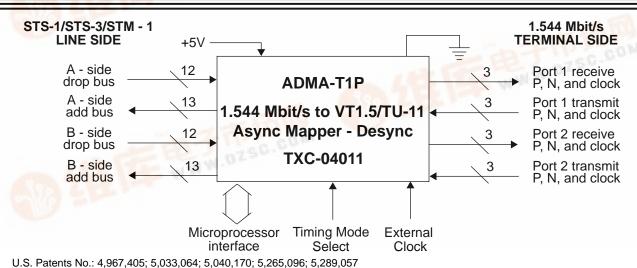

# ADMA-T1P Device 1.544 Mbit/s to VT1.5/TU-11 Async Mapper-Desync TXC-04011

## **DATA SHEET**

Preliminary

#### FEATURES:

- Add/drop two 1.544 Mbit/s signals from an STS-1, an STS-3/AU-3, or an STM-1 VC-4

- Independent add and drop bus timing modes

- Selectable AMI or B8ZS positive/negative rail or NRZ T1 interface. Performance counter provided for illegal coding violations

- Digital desynchronizer reduces systemic jitter in the presence of multiple pointer movements. A register is also provided to control the internal FIFO leak rate

- Drop buses are monitored for parity, loss of clock, and H4 multiframe errors

- Performance counters are provided for VT/TU pointer movements, BIP-2 errors and Far End Block Errors (FEBEs)

- VT/TUs are monitored for Loss Of Pointer, New Data Flags (NDFs), AIS, Remote Defect Indication (RDI), and size errors (S-bits)

- V5 byte Signal Label Mismatch and Unequipped detection

- Loopback, generate BIP-2 errors, and send RDI capability

- Intel microprocessor interface

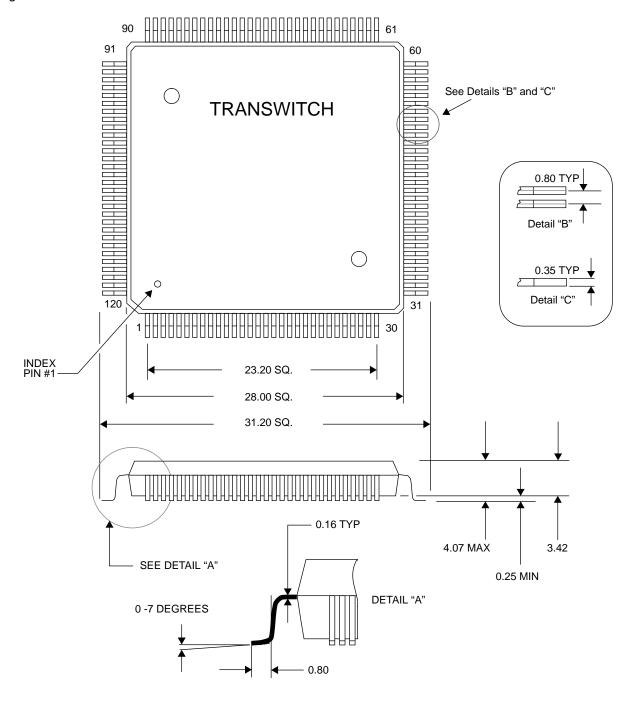

- 120-pin plastic quad flat package

#### DESCRIPTION ==

The ADMA-T1P device is designed for add/drop multiplexer, terminal multiplexer, and dual and single unidirectional ring applications. Two T1 1.544 Mbit/s signals are mapped to and from asynchronous 1.5 Virtual Tributaries (VT1.5s) or Tributary Unit - 11s (TU-11s). The ADMA-T1P interfaces to a multiple-segment, byte-parallel SONET/SDH-formatted bus at the 19.44 Mbit/s byte rate for STM-1/STS-3 operation or at the 6.48 Mbit/s byte rate for STS-1 operation. The T1 1.544 Mbit/s signals can be either AMI/B8ZS positive/negative or NRZ-formatted signals. The ADMA-T1P provides performance counters, alarm detection, and the ability to generate errors and Alarm Indication Signals (AIS). T1 port loopback capability is also provided. The dual timing mode Plus feature increases the I/O signal pin count by 7 from the ADMA-T1 device level so that the ADMA-T1P has a 120-pin package.

The ADMA-T1P bus interface is used to connect to other TranSwitch devices such as the STM-1/STS-3/ STS-3c Overhead Terminator (SOT-3), TXC-03003, to form an STS-3/STM-1 add/drop or terminal system.

#### APPLICATIONS ≡

- STS-1/STS-3/STM-1 to 1.544 Mbit/s add/drop mux/demux

- Unidirectional or bidirectional ring applications

- STS-1/STS-3/STM-1 termination terminal mode multiplexer

- STS-1/STS-3/STM-1 test equipment

**Document Number:**

PRELIMINARY information documents contain information on products in the sampling, pre-production

or early production phases of the product life cycle. Characteristic data and other specifications are subject to change. Contact TranSwitch Applications Engineering for current information on this product.

TXC-04011-MB Ed. 1, September 1995

# **TABLE OF CONTENTS**

| <b>SECTION</b> |                                                                 | <u>PAGE</u> |  |  |  |  |  |  |  |

|----------------|-----------------------------------------------------------------|-------------|--|--|--|--|--|--|--|

| Block Diag     | Block Diagram                                                   |             |  |  |  |  |  |  |  |

| Block Diag     | ram Description                                                 | 3           |  |  |  |  |  |  |  |

| Pin Diagrar    | n                                                               | 6           |  |  |  |  |  |  |  |

| Pin Descrip    | tions                                                           | 6           |  |  |  |  |  |  |  |

| Absolute M     | aximum Ratings                                                  | 14          |  |  |  |  |  |  |  |

| Thermal Ch     | naracteristics                                                  | 14          |  |  |  |  |  |  |  |

| Power Req      | uirements                                                       | 14          |  |  |  |  |  |  |  |

| Input, Outp    | ut and I/O Parameters                                           | 15          |  |  |  |  |  |  |  |

| Timing Cha     | racteristics                                                    | 17          |  |  |  |  |  |  |  |

| Memory Ma      | ap                                                              | 25          |  |  |  |  |  |  |  |

| Memory Ma      | ap Descriptions                                                 | 28          |  |  |  |  |  |  |  |

| Multiplex F    | ormat and Mapping Information                                   | 47          |  |  |  |  |  |  |  |

| Package In     | formation                                                       | 53          |  |  |  |  |  |  |  |

| Ordering In    | formation                                                       | 54          |  |  |  |  |  |  |  |

| Related Pro    | oducts                                                          | 54          |  |  |  |  |  |  |  |

| Standards      | Documentation Sources                                           | 55          |  |  |  |  |  |  |  |

| Document       | ation Update Registration Form                                  | 59          |  |  |  |  |  |  |  |

|                |                                                                 |             |  |  |  |  |  |  |  |

|                | LIGT OF FIGURES                                                 |             |  |  |  |  |  |  |  |

|                | LIST OF FIGURES                                                 |             |  |  |  |  |  |  |  |

|                |                                                                 | PAGE        |  |  |  |  |  |  |  |

| Figure 1.      | ADMA-T1P TXC-04011 Block Diagram                                |             |  |  |  |  |  |  |  |

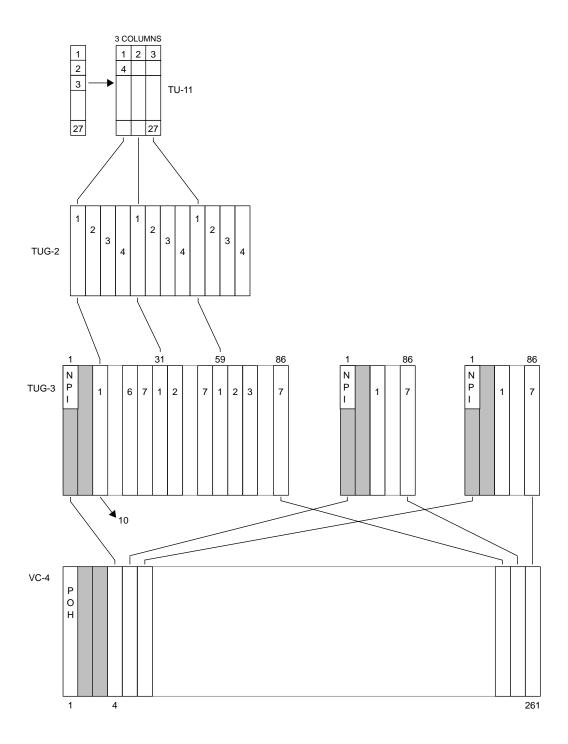

| Figure 2.      | 1.544 Mbit/s Mapping                                            |             |  |  |  |  |  |  |  |

| Figure 3.      | ADMA-T1P TXC-04011 Pin Diagram                                  |             |  |  |  |  |  |  |  |

| Figure 4.      | Ports 1 and 2 DS1 Transmit Timing                               |             |  |  |  |  |  |  |  |

| Figure 5.      | Ports 1 and 2 DS1 Receive Timing                                |             |  |  |  |  |  |  |  |

| Figure 6.      | STS-1 A/B Drop and Add Bus Signals, Timing Derived from Drop Bu | us19        |  |  |  |  |  |  |  |

| Figure 7.      | · · · · · · · · · · · · · · · · · · ·                           |             |  |  |  |  |  |  |  |

| F' 0           | Timing Derived from Drop Bus                                    |             |  |  |  |  |  |  |  |

| Figure 8.      | STS-1 A/B Add Bus Signals, Timing Derived from Add Bus          |             |  |  |  |  |  |  |  |

| Figure 9.      | STS-3/STM-1 A/B Add Bus Signals, Timing Derived from Add Bus .  |             |  |  |  |  |  |  |  |

| Figure 10.     | Microprocessor Read Cycle - Intel Timing                        |             |  |  |  |  |  |  |  |

| Figure 11.     | Microprocessor Write Cycle - Intel Timing                       |             |  |  |  |  |  |  |  |

| Figure 12.     | ADMA-T1P TXC-04011 120-Pin Plastic Quad Flat Package            | 53          |  |  |  |  |  |  |  |

#### **BLOCK DIAGRAM**

Figure 1. ADMA-T1P TXC-04011 Block Diagram

#### **BLOCK DIAGRAM DESCRIPTION**

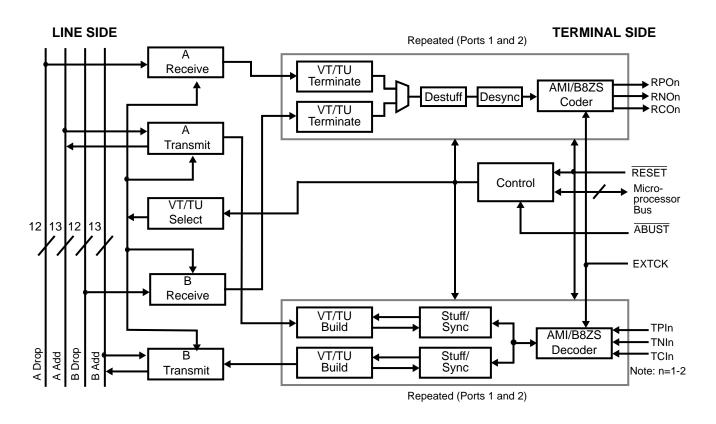

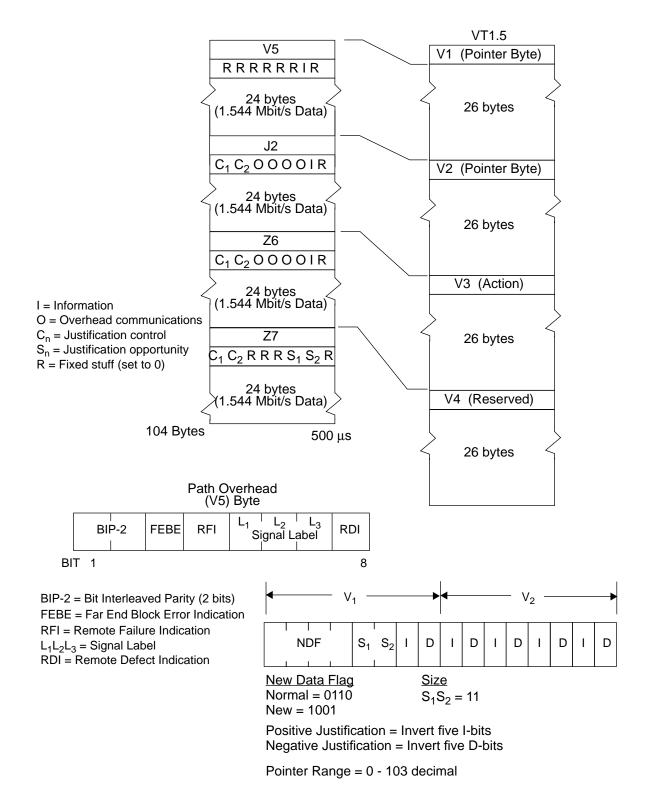

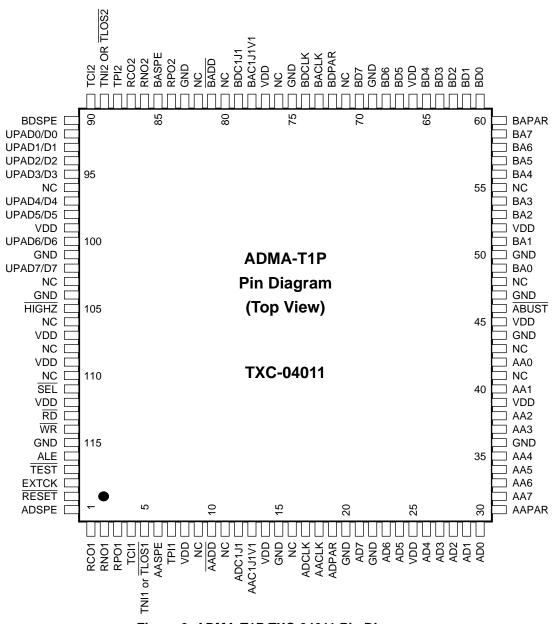

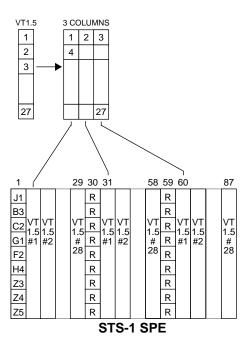

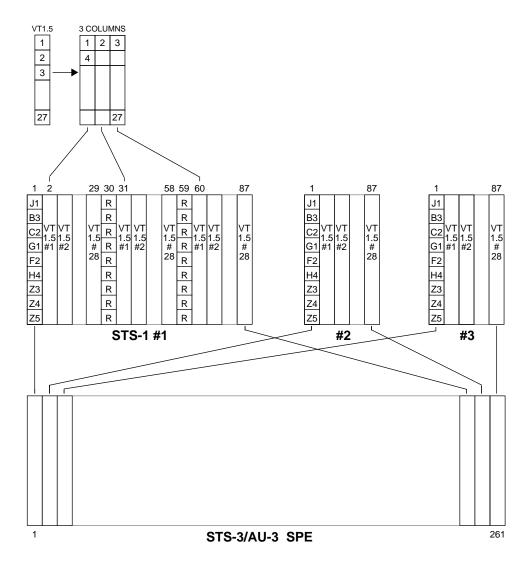

The block diagram for the ADMA-T1P is shown in Figure 1. The ADMA-T1P interfaces to four buses, design nated as A Drop, A Add, B Drop and B Add. The four buses run at the STS-3/STM-1 rate of 19.44 Mbytes/s, or at the STS-1 rate of 6.48 Mbytes/s. For North American applications, the asynchronous T1 signals are carried in floating Virtual Tributary 1.5s (VT1.5s) in a Synchronous Transport Signal -1 (STS-1), or in STS-1s that are carried in the Synchronous Transport Signal - 3 (STS-3). For ITU-T applications, the T1 signals are carried in floating mode Tributary Unit - 11s (TU-11s) in the STM-1 Virtual Container - 4 structure (VC-4) using Tributary Unit Group - 3 (TUG-3), or in the STM-1 Virtual Container - 3 structure (VC-3) using Tributary Unit Group - 2 (TUG-2) mapping schemes. Two T1 signals can be connected (dropped) from one bus (A Drop or B Drop), or both of the drop buses to the T1 lines. Two asynchronous T1 signals are formatted into VT1.5s or TUs and are connected (added) to either of the add buses (or both, depending upon the mode of operation). When the ABUST input is set high to configure the ADMA-T1P for the drop bus timing mode, the add buses are, by definition, byte, frame, and multiframe synchronous with their like-named drop buses, but delayed because of internal processing. For example, if a byte from a VT1.5 or TU-11 is to be added to the A Add bus, the time of its placement on the bus is derived from A Drop bus timing, and from software instructions specifying which VT/TU number is to be dropped. When the device is configured for the add bus timing mode (ABUST set low), the add bus data, parity and add indicator signals are derived from the add clock, C1J1V1 and SPE signals. There will be a delay of either one or two clock cycles for the output signals relative to the add bus C1J1V1 and SPE signals.

The A Receive Block is identical to the B Receive Block. The VT/TU Terminate, Destuff, Desync, and AMI/B8ZS Line Coder Blocks are also repeated for both ports. Twelve leads are connected between a drop bus and the ADMA-T1P A or B Drop bus interface. The interface consists of a byte clock, byte-wide data, a C1J1 indicator signal, a payload identification signal (SPE) and parity. Parity is selectable for odd or even parity, and for data only.

Depending upon the application, buffers and latches may be used between the system buses and an ADMA-T1P. Each bus interface is monitored for parity, loss of clock, and H4 multiframe errors. Under microprocessor control, the two receive blocks extract a VT1.5 or TU-11 from the STS-3 or VC-4 in the VT/TU Terminate Blocks.

Each Terminate Block performs pointer processing (V1 and V2), overhead byte (V5) processing, and provides a bit status of the eight receive overhead communications bits located in the control bytes in the VT/TU (see Figure 2). The pointer bytes are monitored for an NDF indication, and for AIS, and Loss Of Pointer alarms. In addition, the size (S-bits) in the pointer bytes are monitored for the correct value. Overhead byte (V5) processing includes a BIP-2 parity check, along with the count of detected errors, counting the number of received Far End Block Errors (FEBE), the states of the receive signal label, mismatch of the receive signal label against a microprocessor written value, unequipped status detection, and the status of the Remote Defect Indication (RDI) bit, and the Remote Failure Indication (RFI) bit.

Depending on the drop bus selected, the VT/TU is destuffed using majority rule for the two sets of three justification control bits (Cn) which determines whether the two S-bits are data bits or justification bits.

The Desync Block removes the effects on the output of systemic jitter that might occur due to signal mappings and pointer movements. The Desync Block contains two parts, a pointer leak buffer and a T1 loop buffer. The function of the pointer leak buffer is to accept up to five consecutive positive or negative pointer adjustments and to ramp out the effect over a specified period of time. The T1 Loop Buffer consists of a digital loop filter, which is designed to track the frequency of the received T1 signal and to remove both transmission and stuffing jitter.

An option for each port provides either NRZ data and clock or an AMI/B8ZS-coded positive and negative rail signals for the T1 line interface. Transmit data (towards the T1 line) is clocked out of the ADMA-T1P on rising edges of the clock.

Towards the SONET/SDH add buses, the ADMA-T1P accepts either T1 AMI/B8ZS-coded positive and negative rail signals or NRZ data. A 16-bit performance counter is provided that counts illegal AMI or B8ZS coding violations. The T1 line is monitored for AIS, and loss of clock or signal.

The Stuff/Sync Block time buffers the T1 signal for frequency justification by the Stuff Block. The Stuff/Sync Block contains a FIFO and uses threshold modulation for the VT/TU justification process.

This Block also permits tracking of the incoming T1 signal having an average frequency offset as high as 120 ppm, and up to 5 UI of peak-to-peak jitter. The interface between this Block and the VT/TU Build Block is bi-directional. The VT/TU Build Block request bits from the FIFO based on the VT/TU phase. The justification algorithm fixes the first S-bit (S1) to the pattern 1110 every four multiframes. The second S-bit contains either data or a justification bit based on a length measurement. Since the ADMA-T1P supports a ring system architecture, two sets of Blocks are provided for each port.

The VT/TU Block formats the VT/TU into an STS-1, STS-3 or STM-1 structure for asynchronous 1.544 Mbit/s signals, as shown in Figure 2. The pointer value (in the V1 and V2 bytes) is fixed to a value of 78. Access is provided for determining the states of the overhead communications channel (O-bits) located in two justification control bytes in the VT/TU format. Access is also provided for transmitting the signal label and the Remote Defect Indication (RDI) bit, both of which are located in the V5 overhead byte. The Far End Block Error (FEBE) bit state is determined by the BIP-2 detector in the drop side. In addition, a control bit is provided for generating a VT/TU AIS (all ones).

Figure 2. 1.544 Mbit/s Mapping

#### **PIN DIAGRAM**

Figure 3. ADMA-T1P TXC-04011 Pin Diagram

## **PIN DESCRIPTIONS**

#### **POWER SUPPLY AND GROUND**

| Symbol | Pin No.                                               | I/O/P * | Туре | Name/Function                     |

|--------|-------------------------------------------------------|---------|------|-----------------------------------|

| VDD    | 8, 14, 25, 39, 45, 52,<br>66, 77, 99, 107, 109, 112   | Р       | I    | VDD: +5-volt supply voltage, ±5%. |

| GND    | 15, 20, 22, 36, 44, 47, 50, 69, 75, 83, 101, 104, 115 | Р       | I    | Ground: 0 volts reference         |

Note: I = Input; O = Output; P = Power

| Symbol | Pin No.                                                                    | I/O/P | Туре | Name/Function                                                                                                                                                                   |

|--------|----------------------------------------------------------------------------|-------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NC     | 9, 11, 16, 41,<br>43, 48, 55, 71,<br>76, 80, 82, 96,<br>103, 106, 108, 110 |       |      | No Connect: NC pins are not to be connected, not even to another NC pin, but must be left floating. Connection of NC pins may impair performance or cause damage to the device. |

# A DROP AND A ADD BUS I/O

| Symbol  | Pin No.                              | I/O/P | Type * | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------|--------------------------------------|-------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADCLK   | 17                                   | I     | TTL    | A Drop Bus Clock: This clock operates at 19.44 MHz for STS-3/STM-1 operation, and at 6.48 MHz for STS-1 operation. A Drop bus byte-wide data (AD7-AD0), the parity bit (ADPAR), SPE indication (ADSPE), and the C1J1 byte indicator (ADC1J1) inputs are detected on falling edges of this clock. In the drop timing mode (lead ABUST is high) this clock is also used for timing and deriving the like-named add bus byte-wide data (AA7-AA0), add indicator (AADD), and parity bit (AAPAR). These signals are clocked out on rising edges of this clock during the time slots that correspond to the selected VT/TU.        |

| ADPAR   | 19                                   | I     | TTL    | A Drop Bus Parity Bit: Odd parity bit input signal representing the parity calculation for each data byte (AD7-AD0), SPE indication (ADSPE), and the C1J1 byte indicator (ADC1J1) from the drop bus. Control register bits are provided which allow choice of even parity instead, and/or restrict the parity bit detection to the data byte only.                                                                                                                                                                                                                                                                           |

| AD(7-0) | 21, 23, 24,<br>26, 27, 28,<br>29, 30 | I     | TTL    | A Drop Bus Data Byte: Byte-wide data corresponding to the STS-1/STS-3/STM-1 signal from the bus. The first bit received (dropped) from the bus corresponds to bit 7 (pin 21).                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| ADSPE   | 120                                  | I     | TTL    | A Drop Bus SPE Indicator: A signal that is active high during each byte of the STS-1/STS-3/STM-1 payload.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| ADC1J1  | 12                                   | I     | TTL    | A Drop Bus C1/J1 Indications: An active high timing signal that carries STS-1/STS-3/STM-1 frame and SPE information. The C1 pulse identifies the location of the first C1 byte in the STS-3/STM-1 signal and the C1 byte in the STS-1 signal. A J1 pulse, one clock cycle wide, identifies the location of the J1 byte in the STM-1 VC-4 signal. Three J1 pulses are provided to identify the J1 byte locations in the STM-1 AU-3s or STS-3/STS-1 SPEs. One J1 pulse is provided to identify the location of the J1 pulse for STS-1 SPE bus operation. If one or more V1 pulses are present in the signal, they are ignored. |

<sup>\*</sup>See Input, Output and I/O Parameters section below for Type definitions.

| Symbol   | Pin No.                              | I/O/P           | Туре     | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------|--------------------------------------|-----------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AACLK    | 18                                   | I               | TTL      | A Add Bus Clock: When the ABUST lead is low, this clock must be provided for add bus timing. This clock operates at 19.44 MHz for STS-3/STM-1 operation, and at 6.48 MHz for STS-1 operation. The add bus SPE indication and the C1J1 indicators are input into the ADMAT1P on falling edges of this clock. The add bus bytewide data, add indicator, and parity bits are clocked out on rising edges of the clock during the time slots that correspond to the selected VT (TU). When ABUST is high, this input is disabled.                                                                                                              |

| AAPAR    | 31                                   | O<br>(tristate) | CMOS 4mA | A Add Bus Parity Bit: An odd parity output signal calculated over the byte-wide add data. This 3-state lead is only active when there are data being added to the add bus. A control bit is provided that allows even parity to be calculated.                                                                                                                                                                                                                                                                                                                                                                                             |

| AA(7-0)  | 32, 33, 34,<br>35, 37, 38,<br>40, 42 | O<br>(tristate) | CMOS 4mA | A Add Bus Data Byte: 3-state byte-wide data that corresponds to the selected VT (TU). The first bit transmitted (added) to the bus corresponds to bit 7 on pin 32.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| AASPE    | 6                                    | I               | TTL      | A Add Bus SPE Indicator: When the ABUST lead is low, this signal must be provided for add bus timing. This signal is active high during each byte of the STS-1/STS-3/STM-1 payload.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| AAC1J1V1 | 13                                   | ı               | TTL      | A Add Bus C1J1V1 Indication: When the ABUST lead is low, this signal must be provided for add bus timing. This signal carries STS-1/STS-3/STM-1 frame and SPE information. The C1 pulse identifies the first C1 byte time in the STS-3/STM-1 signal and the C1 byte time in the STS-1 signal. A J1 pulse, one clock cycle wide, identifies the location of the J1 byte in the STM-1 VC-4 signal. Three J1 pulses are provided to identify the locations of the STM-1 AU-3s or STS-3 SPEs. One J1 pulse is provided to identify the location of the J1 pulse for STS-1 SPE bus operation. The V1 pulses are used as multiframe indications. |

| ĀADD     | 10                                   | 0               | CMOS 4mA | A Add Bus Add Data Present Indicator: This normally active low signal is present when output data to the A Add bus are valid. It identifies the location of the VT (TU) time slots being selected. A control bit is provided that allows this bit to be active high instead of active low.                                                                                                                                                                                                                                                                                                                                                 |

# **B DROP AND B ADD BUS I/O**

| Symbol  | Pin No.                              | I/O/P | Туре | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------|--------------------------------------|-------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BDCLK   | 74                                   |       | TTL  | B Drop Bus Clock: This clock operates at 19.44 MHz for STS-3/STM-1 operation, and at 6.48 MHz for STS-1 operation. B Drop bus byte-wide data (BD7-BD0), the parity bit (BDPAR), SPE indication (BDSPE), and the C1J1 byte indicator (BDC1J1) inputs are detected on falling edges of this clock. In the drop timing mode (lead ABUST is high) this clock is also used for timing and deriving the like-named add bus byte-wide data (BA7-BA0), add indicator (BADD), and parity bit (BAPAR). These signals are clocked out on rising edges of this clock during the time slots that correspond to the selected VT/TU.             |

| BDPAR   | 72                                   | -     | TTL  | B Drop Bus Parity Bit: Odd parity bit input signal representing the parity calculation for each data byte (BD7-BD0), SPE indication (BDSPE), and the C1J1 byte indicator (BDC1J1) from the drop bus. Control register bits are provided which allow choice of even parity instead, and/or restrict the parity bit detection to the data byte only.                                                                                                                                                                                                                                                                                |

| BD(7-0) | 70, 68, 67,<br>65, 64, 63,<br>62, 61 | I     | TTL  | <b>B Drop Bus Data Byte:</b> Byte-wide data corresponding to the STS-1/STS-3/STM-1 signal from the bus. The first bit received (dropped) from the bus corresponds to bit 7 (pin 70).                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| BDSPE   | 91                                   | I     | TTL  | <b>B Drop Bus SPE Indicator:</b> A signal that is active high during each byte of the STS-1/STS-3/STM-1 payload.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| BDC1J1  | 79                                   | I     | TTL  | B Drop Bus C1/J1 Byte Indicators: An active high timing signal that carries STS-1/STS-3/STM-1 frame and SPE information. The C1 pulse identifies the location of the first C1 byte in the STS-3/STM-1 signal and the C1 byte in the STS-1 signal. A J1 pulse, one clock cycle wide, identifies the location of the J1 byte in the STM-1 VC-4 signal. Three J1 pulses are provided to identify the J1 byte locations in the STM-1 AU-3s or STS-3/STS-1 SPEs. One J1 pulse is provided to identify the location of the J1 pulse for STS-1 SPE bus operation. If one or more V1 pulses are present in this signal, they are ignored. |

| BACLK   | 73                                   | I     | TTL  | B Add Bus Clock: When the ABUST lead is low, this clock must be provided for add bus timing. This clock operates at 19.44 MHz for STS-3/STM-1 operation, and at 6.48 MHz for STS-1 operation. The add bus SPE indication and the C1J1 indicators are input into the ADMAT1P on falling edges of this clock. The add bus bytewide data, add indicator, and parity bits are clocked out on rising edges of the clock during the time slots that correspond to the selected VT (TU). When ABUST is high, this input is disabled.                                                                                                     |

| Symbol   | Pin No.                              | I/O/P           | Туре     | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------|--------------------------------------|-----------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BAPAR    | 60                                   | O<br>(tristate) | CMOS 4mA | <b>B Add Bus Parity Bit:</b> An odd parity output signal calculated over the byte-wide add data. This 3-state lead is only active when there are data being added to the add bus. A control bit is provided that allows even parity to be calculated.                                                                                                                                                                                                                                                                                                                                                                                     |

| BA(7-0)  | 59, 58, 57,<br>56, 54, 53,<br>51, 49 | O<br>(tristate) | CMOS 4mA | <b>B Add Bus Data Byte:</b> 3-state byte-wide data that corresponds to the selected VT (TU). The first bit transmitted (added) to the bus corresponds to bit 7 on pin 59.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| BASPE    | 85                                   | I               | TTL      | B Add Bus SPE Indicator: When the ABUST lead is low, this signal must be provided for add bus timing. This signal is active high during each byte of the STS-1/STS-3/STM-1 payload.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| BAC1J1V1 | 78                                   | I               | TTL      | B Add Bus C1J1 Indications: When the ABUST lead is low, this signal must be provided for add bus timing. This signal carries STS-1/STS-3/STM-1 frame and SPE information. The C1 pulse identifies the first C1 byte time in the STS-3/STM-1 signal and the C1 byte time in the STS-1 signal. A J1 pulse, one clock cycle wide, identifies the location of the J1 byte in the STM-1 VC-4 signal. Three J1 pulses are provided to identify the locations of the STM-1 AU-3s or STS-3 SPEs. One J1 pulse is provided to identify the location of the J1 pulse for STS-1 SPE bus operation. The V1 pulses are used as multiframe indications. |

| BADD     | 81                                   | 0               | CMOS 4mA | B Add Bus Add Data Present Indicator: This normally active low signal is present when output data to the B Add bus are valid. It identifies the location of the VT (TU) time slots being selected. A control bit is provided that allows this bit to be active high instead of active low.                                                                                                                                                                                                                                                                                                                                                |

# **DS1 PORT 1 INTERFACE**

| Symbol | Pin No. | I/O/P           | Туре     | Name/Function                                                                                                                                                                                                                                                                             |

|--------|---------|-----------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RCO1   | 1       | O<br>(tristate) | CMOS 4mA | Receive DS1 Output Clock, Port 1: A 1.544 MHz clock output. Data are clocked out of the ADMA-T1P on rising edges of this clock. Control bits are provided for inverting this clock and for forcing this lead to 3-state.                                                                  |

| RPO1   | 3       | O<br>(tristate) | CMOS 4mA | Receive DS1 Data Positive Rail or NRZ, Port 1: When the ADMA-T1P is operating with a rail interface, positive rail data are provided on this lead. When operating in the bypass mode, an NRZ signal is provided on this lead. A control bit is provided for forcing this lead to 3-state. |

| RNO1   | 2       | O<br>(tristate) | CMOS 4mA | Receive DS1 Data Negative Rail, Port 1: When the ADMA-T1P is operating with a rail interface, negative rail data are provided on this lead. A control bit is provided for forcing this lead to 3-state. In the NRZ mode, this lead is forced to a high impedance state.                   |

| Symbol         | Pin No. | I/O/P | Туре | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------------|---------|-------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TCI1           | 4       | I     | TTLs | <b>Transmit DS1 Input Clock, Port 1:</b> A 1.544 MHz clock input. Data are clocked into the ADMA-T1P on falling edges of this clock. A control bit is provided for inverting this clock.                                                                                                                                                                                                                                    |

| TPI1           | 7       | -     | TTL  | Transmit DS1 Data Positive Rail or NRZ, Port 1: When the ADMA-T1P is operating with a rail interface, positive rail input data are provided on this lead. When operating in the bypass mode, an NRZ signal is provided on this lead.                                                                                                                                                                                        |

| TNI1/<br>TLOS1 | 5       | _     | TTL  | Transmit DS1 Data Negative Rail, Port 1/External Transmit Loss of Signal, Port 1: When the ADMA-T1P is operating with a rail interface, negative rail input data are provided on this lead. When the NRZ interface is selected, this lead can be used to provide an input for an active low external transmit loss of signal indication. If this pin is not used for indicating a loss of signal then it must be held high. |

### **DS1 PORT 2 INTERFACE**

| Symbol | Pin No. | I/O/P           | Туре     | Name/Function                                                                                                                                                                                                                                                                             |

|--------|---------|-----------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RCO2   | 87      | O<br>(tristate) | CMOS 4mA | Receive DS1 Output Clock, Port 2: A 1.544 MHz clock output. Data are clocked out of the ADMA-T1P on rising edges of this clock. Control bits are provided for inverting this clock and for forcing this lead to 3-state.                                                                  |

| RPO2   | 84      | O<br>(tristate) | CMOS 4mA | Receive DS1 Data Positive Rail or NRZ, Port 2: When the ADMA-T1P is operating with a rail interface, positive rail data are provided on this lead. When operating in the bypass mode, an NRZ signal is provided on this lead. A control bit is provided for forcing this lead to 3-state. |

| RNO2   | 86      | O<br>(tristate) | CMOS 4mA | Receive DS1 Data Negative Rail, Port 2: When the ADMA-T1P is operating with a rail interface, negative rail data are provided on this lead. A control bit is provided for forcing this lead to 3-state. In the NRZ mode, this lead is forced to a high impedance state.                   |

| TCI2   | 90      | I               | TTLs     | Transmit DS1 Input Clock, Port 2: A 1.544 MHz clock input. Data are clocked into the ADMA-T1P on falling edges of this clock. A control bit is provided for inverting this clock.                                                                                                         |

| TPI2   | 88      | I               | TTL      | Transmit DS1 Data Positive Rail or NRZ, Port 2: When the ADMA-T1P is operating with a rail interface, positive rail input data are provided on this lead. When operating in the bypass mode, an NRZ signal is provided on this lead.                                                      |

| Symbol         | Pin No. | I/O/P | Туре | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------------|---------|-------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TNI2/<br>TLOS2 | 89      | I     | TTL  | Transmit DS1 Data Negative Rail, Port 2/External Transmit Loss or Signal, Port 2: When the ADMA-T1P is operating with a rail interface, negative rail input data are provided on this lead. When the NRZ interface is selected, this lead can be used to provide an input for an active low external transmit loss of signal indication. If this pin is not used for indicating a loss of signal then it must be held high. |

### **MICROPROCESSOR BUS INTERFACE**

| Symbol                    | Pin No.                                | I/O/P | Туре    | Name/Function                                                                                                                                                                                       |

|---------------------------|----------------------------------------|-------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UPAD(7-0)<br>or<br>D(7-0) | 102, 100,<br>98, 97, 95,<br>94, 93, 92 | I/O   | TTL 8mA | Address/Data Bus: These leads constitute the time multiplexed address and data bus for accessing the registers which reside in the ADMA-T1P. UPAD7/D7 is the most significant bit. High is logic 1. |

| SEL                       | 111                                    | I     | TTLs    | <b>Select:</b> A low enables the microprocessor to access the memory map registers for control, status, and alarm information.                                                                      |

| RD                        | 113                                    | I     | TTLs    | <b>Read:</b> An active low signal generated by the microprocessor for reading the registers which reside in the memory map.                                                                         |

| WR                        | 114                                    | I     | TTLs    | <b>Write:</b> An active low signal generated by the microprocessor for writing to the registers which reside in the memory map.                                                                     |

| ALE                       | 116                                    | I     | TTLs    | Address Latch Enable: An active high signal generated by the microprocessor. Used by the processor for holding an address stable during a read/write cycle.                                         |

# CONTROLS

| Symbol | Pin No. | I/O/P | Туре | Name/Function                                                                                                                                                                                                                                                                                                                                                                                  |

|--------|---------|-------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TEST   | 117     | I     | TTLs | TranSwitch Test Bit: Must be held high.                                                                                                                                                                                                                                                                                                                                                        |

| EXTCK  | 118     | I     | CMOS | External Reference Clock: A 48.6360 MHz (+/- 32 ppm over life) clock that has a duty cycle of 50 +/- 10% must be applied to this pin for operating the desynchronizer, generating line AIS, and driving other internal circuitry.                                                                                                                                                              |

| RESET  | 119     | I     | TTLs | Hardware Reset: An active low pulse that must be applied to this pin for a minimum of 150 nanoseconds after power is first applied. The reset clears all performance counters and alarms, resets the control bits, and initializes the internal FIFO. The microprocessor must initialize the control bits for normal operation.                                                                |

| HIGHZ  | 105     | I     | TTLs | <b>High Impedance Select:</b> A 0 sets all output pins to the high impedance state for testing purposes. Otherwise, this pin must be held high.                                                                                                                                                                                                                                                |

| ABUST  | 46      | I     | TTL  | Add Bus Timing Select: A low selects the add bus timing mode. The add bus clock (AACLK, BACLK), SPE (AASPE, BASPE) and C1J1V1 (AAC1J1V1, BAC1J1V1) input signals are used for deriving data, parity and add indicator signals for the A and B buses. A high selects the drop bus timing mode. The add bus data, parity and add indicator signals are derived from the drop bus timing signals. |

# **ABSOLUTE MAXIMUM RATINGS**

| Parameter                      | Symbol          | Min * | Max *                 | Unit |

|--------------------------------|-----------------|-------|-----------------------|------|

| Supply voltage                 | V <sub>DD</sub> | -0.5  | +6.0                  | V    |

| DC input voltage               | V <sub>IN</sub> | -0.5  | V <sub>DD</sub> + 0.5 | V    |

| Ambient operating temperature  | T <sub>A</sub>  | -40   | 85                    | °C   |

| Operating junction temperature | TJ              |       | 150                   | °C   |

| Storage temperature range      | T <sub>S</sub>  | -55   | 150                   | °C   |

<sup>\*</sup>Note: Operating conditions exceeding those listed in Absolute Maximum Ratings may cause permanent failure. Exposure to absolute maximum ratings for extended periods may impair device reliability.

# THERMAL CHARACTERISTICS

| Parameter                               | Min | Тур | Max | Unit | Test Conditions         |

|-----------------------------------------|-----|-----|-----|------|-------------------------|

| Thermal resistance: junction to ambient |     | 61  |     | °C/W | 0 ft/min linear airflow |

# **POWER REQUIREMENTS**

| Parameter       | Min  | Тур | Max  | Unit | Test Conditions |

|-----------------|------|-----|------|------|-----------------|

| V <sub>DD</sub> | 4.75 | 5.0 | 5.25 | V    |                 |

| I <sub>DD</sub> |      |     | 133  | mA   | STS-1           |

| P <sub>DD</sub> |      |     | 700  | mW   | STS-1           |

| I <sub>DD</sub> |      |     | 175  | mA   | STS-3 or STM-1  |

| P <sub>DD</sub> |      |     | 920  | mW   | STS-3 or STM-1  |

# **INPUT, OUTPUT AND I/O PARAMETERS**

### **INPUT PARAMETERS FOR CMOS**

| Parameter             | Min  | Тур | Max  | Unit | Test Conditions            |

|-----------------------|------|-----|------|------|----------------------------|

| V <sub>IH</sub>       | 3.15 |     |      | V    | $4.75 \le V_{DD} \le 5.25$ |

| V <sub>IL</sub>       |      |     | 1.65 | V    | $4.75 \le V_{DD} \le 5.25$ |

| Input leakage current |      |     | 10   | μΑ   | V <sub>DD</sub> = 5.25     |

| Input capacitance     |      | 3.5 |      | pF   |                            |

### **INPUT PARAMETERS FOR TTL**

| Parameter             | Min | Тур | Max          | Unit | Test Conditions            |

|-----------------------|-----|-----|--------------|------|----------------------------|

| V <sub>IH</sub>       | 2.0 |     |              | V    | $4.75 \le V_{DD} \le 5.25$ |

| V <sub>IL</sub>       |     |     | 0.8          | V    | $4.75 \le V_{DD} \le 5.25$ |

| Input leakage current |     |     | <u>+</u> 1.0 | μΑ   | V <sub>DD</sub> = 5.25     |

| Input capacitance     |     | 3.5 |              | pF   |                            |

### **INPUT PARAMETERS FOR TTLs**

| Parameter                             | Min | Тур | Max | Unit | Test Conditions        |

|---------------------------------------|-----|-----|-----|------|------------------------|

| VT- Negative going, threshold voltage |     |     | 0.8 | V    |                        |

| VT+ Positive going, threshold voltage | 2.0 |     |     | V    |                        |

| Input leakage current                 |     |     | 1.0 | μΑ   | V <sub>DD</sub> = 5.25 |

| Input capacitance                     |     | 3.5 |     | pF   |                        |

| Vhys Hysteresis<br>(VT+ - VT-)        | 0.3 |     | 0.7 | V    |                        |

### **OUTPUT PARAMETERS FOR CMOS 4mA**

| Parameter                              | Min                   | Тур | Max           | Unit | Test Conditions                                |

|----------------------------------------|-----------------------|-----|---------------|------|------------------------------------------------|

| V <sub>OH</sub>                        | V <sub>DD</sub> - 0.8 |     |               | V    | V <sub>DD</sub> = 4.75; I <sub>OH</sub> = -4.0 |

| V <sub>OL</sub>                        |                       |     | 0.5           | V    | $V_{DD} = 4.75; I_{OL} = 4.0$                  |

| I <sub>OL</sub>                        |                       |     | 4.0           | mA   |                                                |

| I <sub>OH</sub>                        |                       |     | -4.0          | mA   |                                                |

| I <sub>OZ</sub> (HIGHZ output current) |                       |     | <u>+</u> 10.0 | μΑ   |                                                |

# **INPUT/OUTPUT PARAMETERS FOR TTL 8mA**

| Parameter             | Min                   | Тур | Max          | Unit  | Test Conditions                                |

|-----------------------|-----------------------|-----|--------------|-------|------------------------------------------------|

|                       | 141111                | тур | IVIGA        | Oilit | Test conditions                                |

| $V_{IH}$              | 2.0                   |     |              | V     | $4.75 \le V_{DD} \le 5.25$                     |

| $V_{IL}$              |                       |     | 0.8          | V     | $4.75 \le V_{DD} \le 5.25$                     |

| Input leakage current |                       |     | <u>+</u> 1.0 | μА    | V <sub>DD</sub> = 5.25                         |

| Input capacitance     |                       | 5.5 |              | pF    |                                                |

| V <sub>OH</sub>       | V <sub>DD</sub> - 0.8 |     |              | V     | V <sub>DD</sub> = 4.75; I <sub>OH</sub> = -8.0 |

| V <sub>OL</sub>       |                       |     | 0.5          | V     | V <sub>DD</sub> = 4.75; I <sub>OL</sub> = 8.0  |

| I <sub>OL</sub>       |                       |     | 8.0          | mA    |                                                |

| I <sub>ОН</sub>       |                       |     | -8.0         | mA    |                                                |

### **TIMING CHARACTERISTICS**

Detailed timing diagrams for the ADMA-T1P device are illustrated in Figures 4 through 11, with values of the timing intervals tabulated below each timing diagram. All output times are measured with a maximum 45 pF load capacitance. Timing parameters are measured at voltage levels of  $(V_{IH} + V_{IL})/2$  for input signals or  $(V_{OH} + V_{OL})/2$  for output signals.

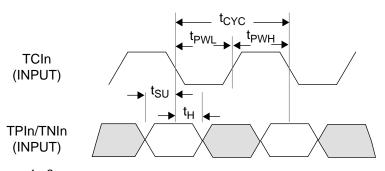

Figure 4. Ports 1 and 2 DS1 Transmit Timing

Note: n = 1 - 2

Note: TCIn is shown for TCLKI = 0, where data are clocked in on falling edges. Data are clocked in on rising edges when TCLKI =1. For NRZ operation, TNIn may be used to input an external loss of signal indication. Otherwise, this pin must be held high.

| Parameter                               | Symbol           | Min   | Тур   | Max | Unit |

|-----------------------------------------|------------------|-------|-------|-----|------|

| TCIn clock period                       | t <sub>CYC</sub> | 560.0 | 647.7 |     | ns   |

| TCIn clock low time                     | t <sub>PWL</sub> | 280.0 |       |     | ns   |

| TCIn clock high time                    | t <sub>PWH</sub> | 280.0 |       |     | ns   |

| TPIn/TNIn data set-up time before TCIn↓ | t <sub>SU</sub>  | 10.0  |       |     | ns   |

| TPIn/TNIn data hold time after TCIn↓    | t <sub>H</sub>   | 2.0   |       |     | ns   |

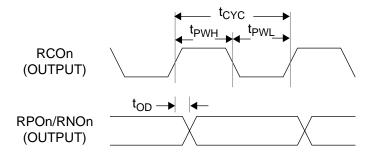

Figure 5. Ports 1 and 2 DS1 Receive Timing

Note: n = 1 - 2

Note: RCOn is shown for RCLKI=0, where data are clocked out on rising edges. Data are clocked out on falling edges when RCLKI=1.

| Parameter                       | Symbol           | Min | Тур | Max | Unit |

|---------------------------------|------------------|-----|-----|-----|------|

| RCOn clock period               | t <sub>CYC</sub> | 637 |     | 658 | ns   |

| RCOn clock low time             | t <sub>PWL</sub> | 318 |     | 329 | ns   |

| RCOn clock high time            | t <sub>PWH</sub> | 318 |     | 329 | ns   |

| RPOn/RNOn data delay from RCOn↑ | t <sub>OD</sub>  | 0.0 |     | 5.0 | ns   |

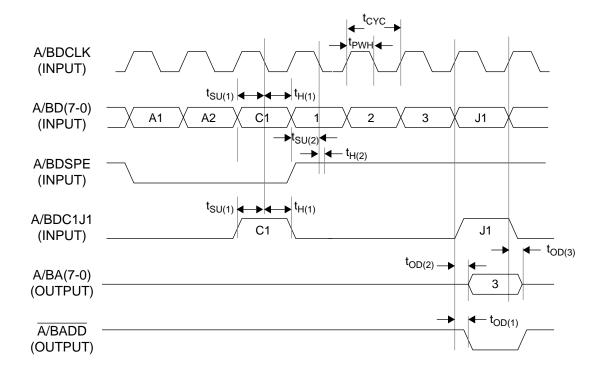

Figure 6. STS-1 A/B Drop and Add Bus Signals, Timing Derived from Drop Bus

| Parameter                                                         | Symbol             | Min | Тур    | Max  | Unit |

|-------------------------------------------------------------------|--------------------|-----|--------|------|------|

| A/BDCLK drop clock period                                         | t <sub>CYC</sub>   |     | 154.32 |      | ns   |

| A/BDCLK drop clock duty cycle, t <sub>PWH</sub> /t <sub>CYC</sub> |                    | 40  | 50     | 60   | %    |

| A/BD(7-0) drop data and A/BDC1J1 set-up time before A/BDCLK↓      | t <sub>SU(1)</sub> | 4.0 |        |      | ns   |

| A/BD(7-0) drop data and A/BDC1J1 hold time after A/BDCLK↓         | t <sub>H(1)</sub>  | 5.0 |        |      | ns   |

| A/BDSPE set-up time before A/BDCLK↓                               | t <sub>SU(2)</sub> | 4.0 |        |      | ns   |

| A/BDSPE hold time after A/BDCLK↓                                  | t <sub>H(2)</sub>  | 5.0 |        |      | ns   |

| A/BA(7-0) add data out (from tri-state) delay from A/BDCLK↑       | t <sub>OD(2)</sub> | 6.0 |        | 18.5 | ns   |

| A/BA(7-0) add data out (to tri-state) delay from A/BDCLK ↑        | t <sub>OD(3)</sub> | 6.0 |        | 20.0 | ns   |

| A/BADD add indicator delay from A/BDCLK↑                          | t <sub>OD(1)</sub> | 6.0 |        | 19.0 | ns   |

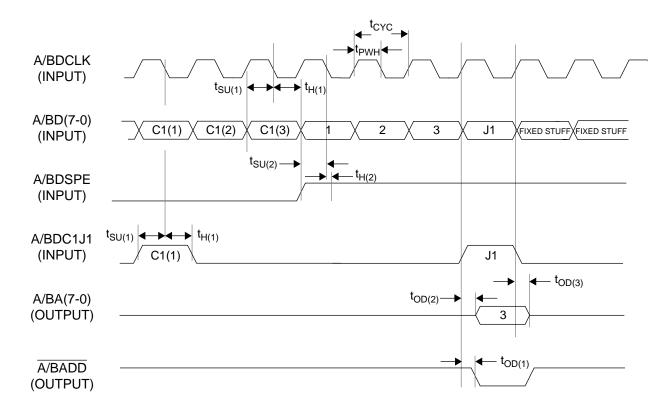

Figure 7. STS-3/STM-1 A/B Drop and Add Bus Signals, Timing Derived from Drop Bus

| Parameter                                                         | Symbol             | Min | Тур   | Max  | Unit |

|-------------------------------------------------------------------|--------------------|-----|-------|------|------|

| A/BDCLK drop clock period                                         | t <sub>CYC</sub>   |     | 51.44 |      | ns   |

| A/BDCLK drop clock duty cycle, t <sub>PWH</sub> /t <sub>CYC</sub> | -                  | 45  | 50    | 55   | %    |

| A/BD(7-0) drop data and A/BDC1J1 set-up time before A/BDCLK↓      | t <sub>SU(1)</sub> | 4.0 |       |      | ns   |

| A/BD(7-0) drop data and A/BDC1J1 hold time after A/BDCLK↓         | t <sub>H(1)</sub>  | 5.0 |       |      | ns   |

| A/BDSPE set-up time before A/BDCLK↓                               | t <sub>SU(2)</sub> | 4.0 |       |      | ns   |

| A/BDSPE hold time after A/BDCLK↓                                  | t <sub>H(2)</sub>  | 5.0 |       |      | ns   |

| A/BA(7-0) add data out (from tri-state) delay from A/BDCLK↑       | t <sub>OD(2)</sub> | 6.0 |       | 18.3 | ns   |

| A/BA(7-0) add data out (to tri-state) delay from A/BDCLK↑         | t <sub>OD(3)</sub> | 6.0 |       | 19.8 | ns   |

| A/BADD add indicator delay from A/BDCLK↑                          | t <sub>OD(1)</sub> | 6.0 |       | 18.8 | ns   |

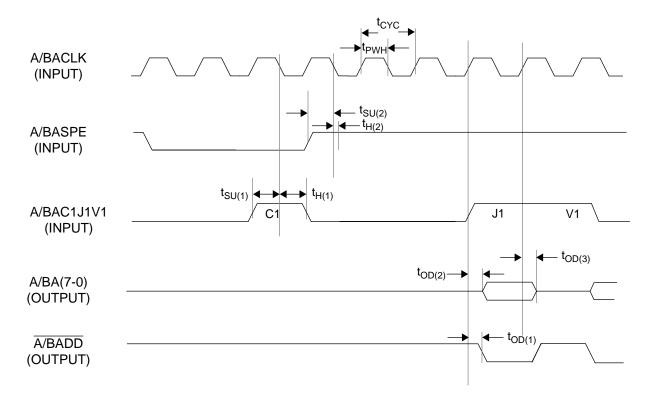

Figure 8. STS-1 A/B Add Bus Signals, Timing Derived from Add Bus

| Parameter                                              | Symbol             | Min | Тур    | Max  | Unit |

|--------------------------------------------------------|--------------------|-----|--------|------|------|

| A/BACLK drop clock period                              | t <sub>CYC</sub>   |     | 154.32 |      | ns   |

| A/BACLK duty cycle, t <sub>PWH</sub> /t <sub>CYC</sub> |                    | 40  | 50     | 60   | %    |

| A/BAC1J1V1 set-up time to A/BACLK↓                     | t <sub>SU(1)</sub> | 4.0 |        |      | ns   |

| A/BAC1J1V1 hold time after A/BACLK↓                    | t <sub>H(1)</sub>  | 5.0 |        |      | ns   |

| A/BASPE set-up time to A/BACLK↓                        | t <sub>SU(2)</sub> | 4.0 |        |      | ns   |

| A/BASPE hold time after A/BACLK↓                       | t <sub>H(2)</sub>  | 5.0 |        |      | ns   |

| A/BA(7-0) data out (from tristate) delay from A/BACLK↑ | t <sub>OD(2)</sub> | 6.0 |        | 18.5 | ns   |

| A/BA(7-0) data to tristate delay from A/BACLK↑         | t <sub>OD(3)</sub> | 6.0 |        | 20.0 | ns   |

| A/BADD add indicator delay from A/BACLK↑               | t <sub>OD(1)</sub> | 6.0 |        | 19.0 | ns   |

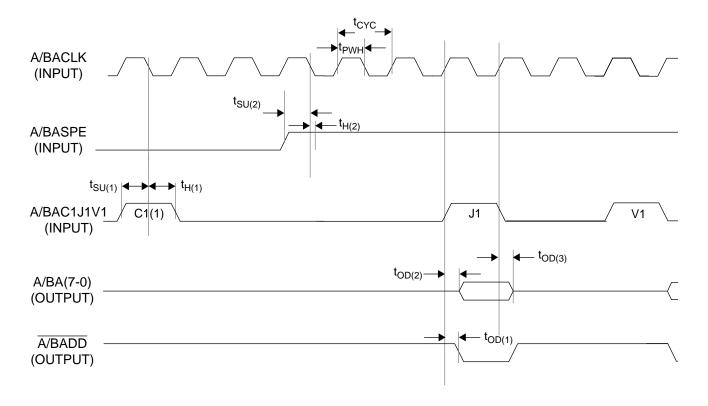

Figure 9. STS-3/STM-1 A/B Add Bus Signals, Timing Derived from Add Bus

| Parameter                                               | Symbol             | Min | Тур   | Max  | Unit |

|---------------------------------------------------------|--------------------|-----|-------|------|------|

| A/BACLK drop clock period                               | t <sub>CYC</sub>   |     | 51.44 |      | ns   |

| A/BACLK duty cycle, t <sub>PWH</sub> /t <sub>CYC</sub>  |                    | 40  | 50    | 60   | %    |

| A/BAC1J1V1 set-up time to A/BACLK ↓                     | t <sub>SU(1)</sub> | 4.0 |       |      | ns   |

| A/BAC1J1V1 hold time after A/BACLK $\downarrow$         | t <sub>H(1)</sub>  | 5.0 |       |      | ns   |

| A/BASPE set-up time to A/BACLK ↓                        | t <sub>SU(2)</sub> | 4.0 |       |      | ns   |

| A/BASPE hold time after A/BACLK ↓                       | t <sub>H(2)</sub>  | 5.0 |       |      | ns   |

| A/BA(7-0) data out (from tristate) delay from A/BACLK ↑ | t <sub>OD(2)</sub> | 6.0 |       | 18.5 | ns   |

| A/BA(7-0) data to tristate delay from A/BACLK ↑         | t <sub>OD(3)</sub> | 6.0 |       | 20.0 | ns   |

| A/BADD add indicator delay from A/BACLK ↑               | t <sub>OD(1)</sub> | 6.0 |       | 19.0 | ns   |

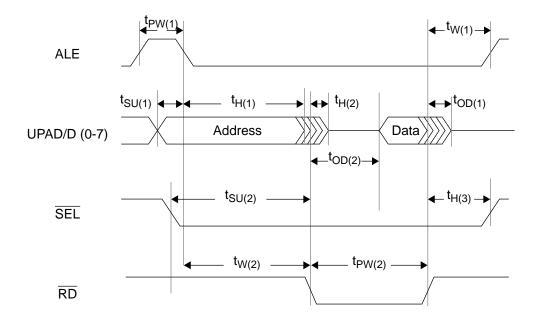

Figure 10. Microprocessor Read Cycle - Intel Timing

| Parameter                                                         | Symbol             | Min  | Тур | Max  | Unit |

|-------------------------------------------------------------------|--------------------|------|-----|------|------|

| ALE pulse width                                                   | t <sub>PW(1)</sub> | 20.0 |     |      | ns   |

| UPAD(0-7) address set-up time before ALE↓                         | t <sub>SU(1)</sub> | 5.0  |     |      | ns   |

| UPAD(0-7) address hold time after ALE↓                            | t <sub>H(1)</sub>  | 3.0  |     |      | ns   |

| UPAD(0-7) address hold time after RD↓                             | t <sub>H(2)</sub>  |      |     | 0.0  | ns   |

| D(0-7) data available delay time after $\overline{RD} \downarrow$ | t <sub>OD(2)</sub> | 5.0  |     | 17.0 | ns   |

| D(0-7) data delay time to tri-state after RD↑                     | t <sub>OD(1)</sub> | 2.0  |     | 8.0  | ns   |

| ALE wait after RD↑                                                | t <sub>W(1)</sub>  | 0.0  |     |      | ns   |

| SEL set-up time before RD↓                                        | t <sub>SU(2)</sub> | 0.0  |     |      | ns   |

| SEL hold time after RD↑                                           | t <sub>H(3)</sub>  | 0.0  |     |      | ns   |

| RD wait after ALE ↓                                               | t <sub>W(2)</sub>  | 20.0 |     |      | ns   |

| RD pulse width                                                    | t <sub>PW(2)</sub> | 45.0 |     |      | ns   |

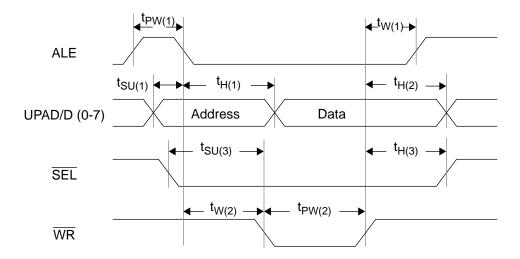

Figure 11. Microprocessor Write Cycle - Intel Timing

| Parameter                                 | Symbol             | Min  | Тур | Max | Unit |

|-------------------------------------------|--------------------|------|-----|-----|------|

| ALE pulse width                           | t <sub>PW(1)</sub> | 20.0 |     |     | ns   |

| ALE wait after WR↑                        | t <sub>W(1)</sub>  | 0.0  |     |     | ns   |

| UPAD(0-7) address set-up time before ALE↓ | t <sub>SU(1)</sub> | 5.0  |     |     | ns   |

| UPAD(0-7) address hold time after ALE↓    | t <sub>H(1)</sub>  | 3.0  |     |     | ns   |

| D(0-7) data input hold time after WR↑     | t <sub>H(2)</sub>  | 16.0 |     |     | ns   |

| SEL set-up time before WR↓                | t <sub>SU(3)</sub> | 0.0  |     |     | ns   |

| SEL hold time after WR↑                   | t <sub>H(3)</sub>  | 0.0  |     |     | ns   |

| WR wait after ALE↓                        | t <sub>W(2)</sub>  | 20.0 |     |     | ns   |

| WR pulse width                            | t <sub>PW(2)</sub> | 45.0 |     |     | ns   |

# **MEMORY MAP**

The ADMA-T1P memory map consists of counters and register bit positions which may be accessed by the microprocessor. Addresses which are shown as TranSwitch test registers or as wholly 'Unused' bytes in the memory map must not be accessed by the microprocessor. No value is specified for the content to be read from an 'Unused' bit position when the address which contains it is selected for a read cycle, but the bit position should be written as 0 when the address is selected for a write cycle (if it is a R/W or W address).

#### **COMMON CONTROL**

| Address<br>(Hex) | Status* | Bit 7  | Bit 6                    | Bit 5  | Bit 4        | Bit 3        | Bit 2  | Bit 1  | Bit 0  |

|------------------|---------|--------|--------------------------|--------|--------------|--------------|--------|--------|--------|

| 00               | W       | RESET  | RESETS                   | RESETC |              |              | Unused |        |        |

| 01               | R/W     | T1SEL1 | T1SEL0                   | BYPAS1 | BYPAS2       | T1LOOP       | T2LOOP | R1EN   | R2EN   |

| 02               | R/W     | MOD1   | MOD0                     | T1B8ZS | T2B8ZS       | T1AIS        | T2AIS  | Unused | TCLKI  |

| 03               | R/W     | TAISE  | UQAE                     | R1AIS  | R2AIS        | RDIEN        | T2SEL1 | T2SEL0 | RCLKI  |

| 40               | R/W     | AAHZE  | BAHZE                    | ADDI   | ABD          | APE          | Unu    | sed    | PTALTE |

| 41               | R/W     |        | NPIA                     | NPIB   | NPIC         | E1AISD       | DPE    | PDDO   | Unused |

| 42               |         |        |                          |        | TranSwitch 7 | est Register | •      |        |        |

| 43               |         |        | TranSwitch Test Register |        |              |              |        |        |        |

| 44               |         |        |                          | •      | TranSwitch 7 | est Register |        |        |        |

<sup>\*</sup> R=Read Only; R(L)=Read Only (Latched); R/W=Read/Write; W=Write only.

#### **A-SIDE DROP BUS STATUS REGISTERS**

| Address<br>(Hex) | Status* | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0 |

|------------------|---------|-------|--------|-------|-------|-------|--------|--------|-------|

| 04               | R(L)    | ADLOC | Unused | AALOC | Unu   | ısed  | A2DH4E | A1DH4E | ADPAR |

| 05               | R       |       |        |       | Unus  | ed    |        |        |       |

| 06               | R       |       |        |       | Unus  | ed    |        |        |       |

| 07               | R       |       | Unused |       |       |       |        |        |       |

### **PORT 1 STATUS/TRANSMIT REGISTERS**

| Address<br>(Hex) | Status* | Bit 7   | Bit 6                                          | Bit 5        | Bit 4      | Bit 3        | Bit 2       | Bit 1      | Bit 0 |

|------------------|---------|---------|------------------------------------------------|--------------|------------|--------------|-------------|------------|-------|

| 08               | R/W     |         | Port 1 Pointer Leak Rate                       |              |            |              |             |            |       |

| 09               | R       |         | Port 1 B8ZS/AMI Coding Errors (low order byte) |              |            |              |             |            |       |

| 0A               | R(L)    |         | Unused R1FFE T1LOCS T1                         |              |            |              |             |            |       |

| 0B               | R       |         |                                                | Port 1 B8ZS/ | AMI Coding | Errors (high | order byte) |            |       |

| 0C               | R       |         |                                                |              | Unus       | sed          |             |            |       |

| 0D               | R/W     | T1VTAIS | T1FB2                                          | T1FFB        | T1RDI      | T1RFI        | A           | 1 TX Label |       |

| 0E               | R/W     |         | Port 1 TX O-Bits                               |              |            |              |             |            |       |

| 0F               | R/W     | R1SEL   |                                                |              | \          | /TN1 (VT#)   |             |            |       |

# PORT 1 A-SIDE DROP BUS RECEIVE REGISTERS

| Address<br>(Hex) | Status* | Bit 7  | Bit 6                                | Bit 5   | Bit 4   | Bit 3  | Bit 2  | Bit 1      | Bit 0 |  |

|------------------|---------|--------|--------------------------------------|---------|---------|--------|--------|------------|-------|--|

| 10               | R       |        | A1BIP2 Error Count                   |         |         |        |        |            |       |  |

| 11               | R       |        | A1FEBE Count                         |         |         |        |        |            |       |  |

| 12               | R(L)    | A1UNEQ | 1UNEQ A1SLER Unused A1NDF Unused TA1 |         |         |        |        |            |       |  |

| 13               | R(L)    | A1AIS  | A1LOP                                | A1SIZE  | A1RDI   | A1RFI  | Δ      | 1 RX Label |       |  |

| 14               | R       |        | A1PJ (                               | Counter |         |        | A1NJ C | ounter     |       |  |

| 15               | R       |        |                                      |         | A1 RX ( | O-Bits |        |            |       |  |

| 16               | R/W     |        | Unused A1UPSL                        |         |         |        |        |            |       |  |

| 17               |         |        | TranSwitch Test Register             |         |         |        |        |            |       |  |

### PORT 1 B-SIDE DROP BUS RECEIVE REGISTERS

| Address<br>(Hex) | Status* | Bit 7  | Bit 6                                | Bit 5   | Bit 4        | Bit 3        | Bit 2   | Bit 1      | Bit 0 |

|------------------|---------|--------|--------------------------------------|---------|--------------|--------------|---------|------------|-------|

| 18               | R       |        |                                      |         | B1BIP2 Err   | or Count     |         |            |       |

| 19               | R       |        |                                      |         | B1FEBE       | Count        |         |            |       |

| 1A               | R(L)    | B1UNEQ | 1UNEQ B1SLER Unused B1NDF Unused TB1 |         |              |              |         |            | TB1FE |

| 1B               | R(L)    | B1AIS  | B1LOP                                | B1SIZE  | B1RDI        | B1RFI        | В       | 1 RX Label |       |

| 1C               | R       |        | B1PJ (                               | Counter |              |              | B1NJ Co | ounter     |       |

| 1D               | R       |        |                                      |         | B1 RX (      | O-Bits       |         |            |       |

| 1E               | R/W     |        | Unused B1UPSL                        |         |              |              |         |            |       |

| 1F               |         |        |                                      | Т       | ranSwitch Te | est Register |         |            |       |

#### **B-SIDE DROP BUS STATUS REGISTERS**

| Address<br>(Hex) | Status* | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0 |

|------------------|---------|-------|--------|-------|-------|-------|--------|--------|-------|

| 24               | R(L)    | BDLOC | Unused | BALOC | Unu   | ısed  | B2DH4E | B1DH4E | BDPAR |

| 25               |         |       | •      |       | Unus  | sed   |        |        |       |

| 26               |         |       | Unused |       |       |       |        |        |       |

| 27               |         |       | Unused |       |       |       |        |        |       |

# PORT 2 STATUS/TRANSMIT REGISTERS

| Address<br>(Hex) | Status* | Bit 7   | Bit 6                                          | Bit 5        | Bit 4      | Bit 3        | Bit 2       | Bit 1       | Bit 0 |

|------------------|---------|---------|------------------------------------------------|--------------|------------|--------------|-------------|-------------|-------|

| 28               | R/W     |         | Port 2 Pointer Leak Rate                       |              |            |              |             |             |       |

| 29               | R       |         | Port 2 B8ZS/AMI Coding Errors (low order byte) |              |            |              |             |             |       |

| 2A               | R(L)    |         |                                                | Unused       |            |              | R2FFE       | T2LOCS      | T2AIS |

| 2B               | R       |         |                                                | Port 2 B8ZS/ | AMI Coding | Errors (high | order byte) | •           |       |

| 2C               |         |         |                                                |              | Unus       | sed          |             |             |       |

| 2D               | R/W     | T2VTAIS | T2FB2                                          | T2FFB        | T2RDI      | T2RFI        | P           | A2 TX Label |       |

| 2E               | R/W     |         | Port 2 TX O-Bits                               |              |            |              |             |             |       |

| 2F               | R/W     | R2SEL   |                                                |              | \          | /TN2 (VT#)   |             |             |       |

### PORT 2 A-SIDE DROP BUS RECEIVE REGISTERS

| Address<br>(Hex) | Status* | Bit 7                     | Bit 6              | Bit 5  | Bit 4        | Bit 3        | Bit 2           | Bit 1 | Bit 0 |

|------------------|---------|---------------------------|--------------------|--------|--------------|--------------|-----------------|-------|-------|

| 30               | R       |                           | A2BIP2 Error Count |        |              |              |                 |       |       |

| 31               | R       |                           | A2FEBE Count       |        |              |              |                 |       |       |

| 32               | R(L)    | A2UNEQ                    | A2SLER             | Unu    | sed          | A2NDF        | Unu             | sed   | TA2FE |

| 33               | R(L)    | A2AIS                     | A2LOP              | A2SIZE | A2RDI        | A2RFI        | RFI A2 RX Label |       |       |

| 34               | R       | A2PJ Counter A2NJ Counter |                    |        |              |              |                 |       |       |

| 35               | R       |                           | A2 RX O-Bits       |        |              |              |                 |       |       |

| 36               | R/W     | Unused A2UPSL             |                    |        |              |              |                 |       |       |

| 37               | R       |                           |                    | Т      | ranSwitch Te | est Register |                 |       |       |

#### PORT 2 B-SIDE DROP BUS RECEIVE REGISTERS

| Address<br>(Hex) | Status* | Bit 7                                      | Bit 6  | Bit 5 | Bit 4        | Bit 3        | Bit 2 | Bit 1 | Bit 0 |

|------------------|---------|--------------------------------------------|--------|-------|--------------|--------------|-------|-------|-------|

| 38               | R       | B2BIP2 Error Count                         |        |       |              |              |       |       |       |

| 39               | R       | B2FEBE Count                               |        |       |              |              |       |       |       |

| 3A               | R(L)    | B2UNEQ                                     | B2SLER | Unu   | sed          | B2NDF        | Unu   | sed   | TB2FE |

| 3B               | R(L)    | B2AIS B2LOP B2SIZE B2RDI B2RFI B2 RX Label |        |       | 2 RX Label   |              |       |       |       |

| 3C               | R       | B2PJ Counter B2NJ Counter                  |        |       | ounter       |              |       |       |       |

| 3D               | R       | B2 RX O-Bits                               |        |       |              |              |       |       |       |

| 3E               | R/W     | Unused B2UPSL                              |        |       |              |              |       |       |       |

| 3F               |         |                                            |        | Т     | ranSwitch Te | est Register | !     |       |       |

# **MEMORY MAP DESCRIPTIONS**

# **CONTROL REGISTERS**