# SWITCH

E123MUX Device E1/E2/E3 MUX/DEMUX TXC-03361

DATA SHEET

### **FEATURES I**

- E1 (2048 kbit/s) multiplexer/demultiplexer for ITU-T Recommendations: G.742 (8448 kbit/s E2 frame format) G.751 (34368 kbit/s E3 frame format)

- Multiplexer/demultiplexer converts: 16 E1s to/from 1 E3 (E13 skip mux), or 16 E1s to/from 4 E2s, or 4 E2s to/from 1 E3 (E12/E23 split mux)

- Counters for bipolar violations, frame errors and loss of frame conditions

- E1 digital phase-locked loop circuits with bypass option

- Test features: PRBS generator and analyzer for E1 channels Local/Remote Loopbacks for E1, E2 or E3 channels Corrupt frame generation for E2 and E3 frames

- E2 and E3 bit error rate indications

- E1 and E3 line side interfaces are selectable as positive and negative rail or NRZ with external loss of signal indication on negative input pin

- · Microprocessor input/output bus provides multiplexed, Intel or Motorola interfaces

- Test access port for boundary scan

- Single +5 volt, ±5 % power supply

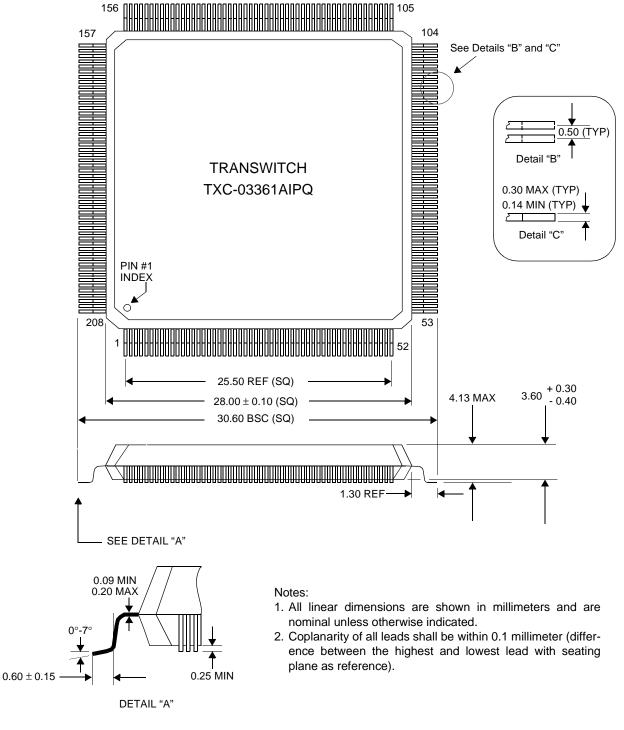

- 208-pin plastic quad flat package

### **DESCRIPTION**

The E123MUX is a CMOS VLSI device that provides the E13 functions needed to multiplex and demultiplex 16 independent E1 signals to and from an E3 signal that conforms to the ITU-T G.751 Recommendation. The E1 and E3 signal interfaces can be either dual unipolar (rail) or NRZ. Digital phase-locked loop circuits are provided for the received E1 signals, but they may be bypassed.

The E123MUX can also be configured to operate as an E12 or E23 multiplexer and demultiplexer. Sixteen E1 signals can be multiplexed and demultiplexed to and from four E2 signals that conform to the ITU-T G.742 Recommendation. Alternatively, four E2 signals can multiplexed and demultiplexed to and from one E3 signal. The E2 signal interfaces are NRZ only. The E123MUX uses memory locations for setting control bits and reporting status information. The status bits have maskable interrupt control bits.

#### **APPLICATIONS**

- Single-board E13 multiplexer

- Compact add/drop multiplexer

- DCS and EDSX systems

- CSU/DSU equipment

Copyright © 2001 TranSwitch Corporation 123MUX sa trademark of TranSwitch Corporation TranSwitch and TXC are registered trademarks of TranSwitch Corporation

**Document Number:** TXC-03361-MB

E123MUX TXC-03361

## **TABLE OF CONTENTS**

| Section                                                | Page |

|--------------------------------------------------------|------|

| List of Figures                                        | 2    |

| Block Diagram                                          |      |

| Block Diagram Description                              |      |

| Pin Diagram                                            | 6    |

| Pin Descriptions                                       | 7    |

| Absolute Maximum Ratings and Environmental Limitations | 16   |

| Thermal Characteristics                                | 16   |

| Power Requirements                                     | 16   |

| Input, Output and I/O Parameters                       | 17   |

| Timing Characteristics                                 | 19   |

| Operation                                              |      |

| Test Access Port                                       | 36   |

| Initialization Sequence                                | 38   |

| Sample Configurations                                  |      |

| Alarm and Interrupt Indications                        |      |

| Throughput Delays                                      |      |

| Memory Map                                             |      |

| Memory Map Descriptions                                |      |

| Package Information                                    |      |

| Ordering Information                                   |      |

| Related Products                                       |      |

| Standards Documentation Sources                        |      |

| List of Data Sheet Changes                             |      |

| Documentation Update Registration Form*                | 85   |

## **LIST OF FIGURES**

| Figure |                                                     | Page |

|--------|-----------------------------------------------------|------|

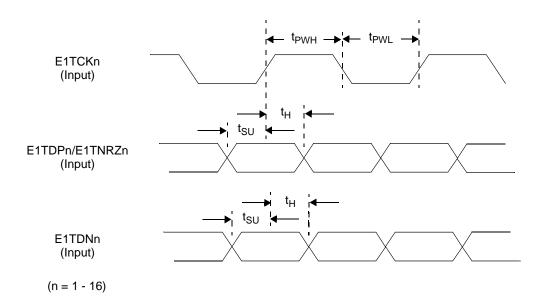

| 1.     | E123MUX TXC-03361 Block Diagram                     | 3    |

| 2.     | E123MUX TXC-03361 Pin Diagram                       |      |

| 3.     | E1 Transmit Input Interface Timing                  | 19   |

| 4.     | E12 Transmit Output Interface Timing                | 20   |

| 5.     | E23 Transmit Input Interface Timing                 | 21   |

| 6.     | E3 Transmit Output Interface Timing                 | 22   |

| 7.     | E3 Receive Input Interface Timing                   | 23   |

| 8.     | E23 Receive Output Interface Timing                 | 24   |

| 9.     | E12 Receive Input Interface Timing                  | 25   |

| 10.    | E1 Receive Output Interface Timing - PLL Enabled    | 26   |

| 11.    | E1 Receive Output Interface Timing - PLL Bypassed   | 27   |

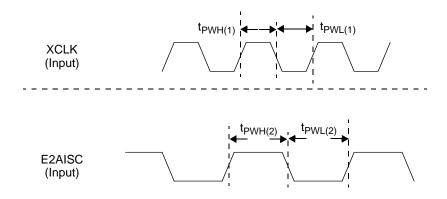

| 12.    | External Clocks Interface Timing                    |      |

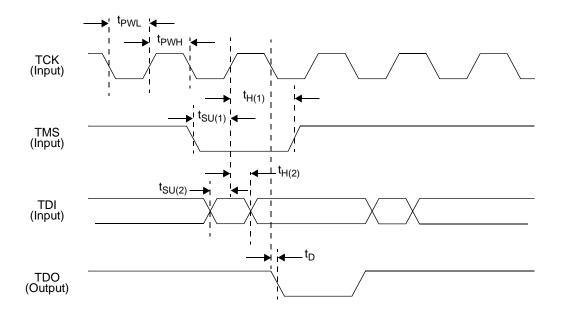

| 13.    | Boundary Scan Timing                                |      |

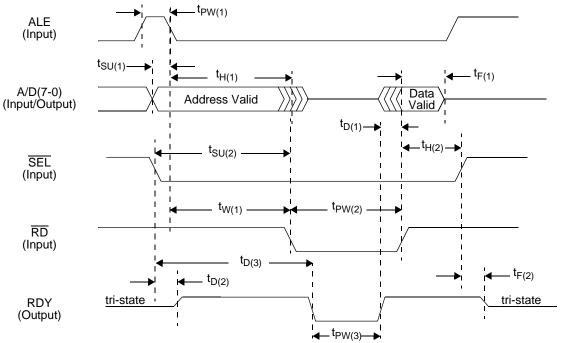

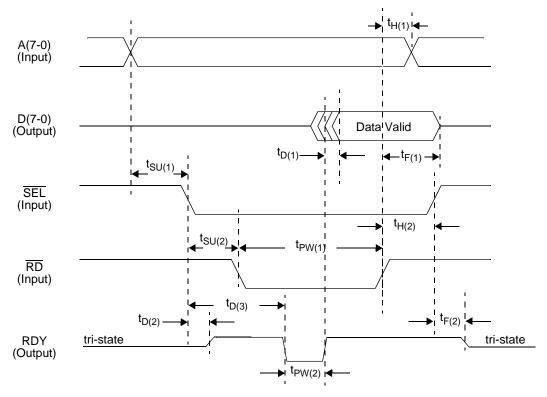

| 14.    | Multiplex Mode - Microprocessor Read Cycle Timing   | 30   |

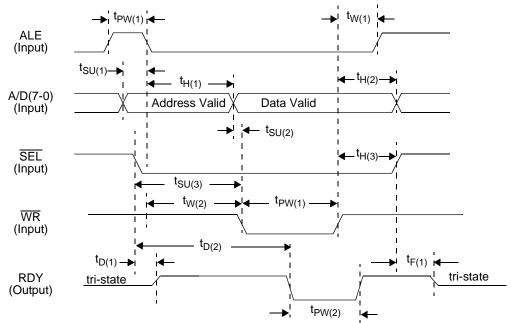

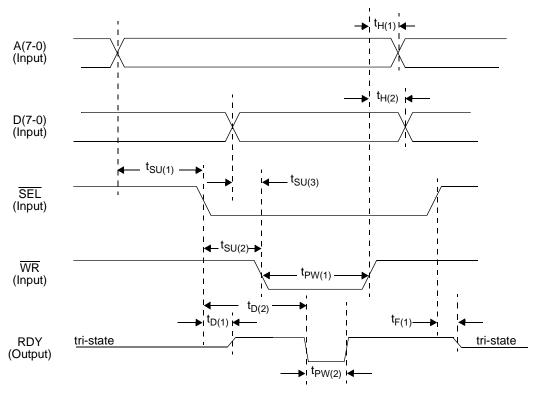

| 15.    | Multiplex Mode - Microprocessor Write Cycle Timing  | 31   |

| 16.    | Intel Mode - Microprocessor Read Cycle Timing       |      |

| 17.    | Intel Mode - Microprocessor Write Cycle Timing      | 33   |

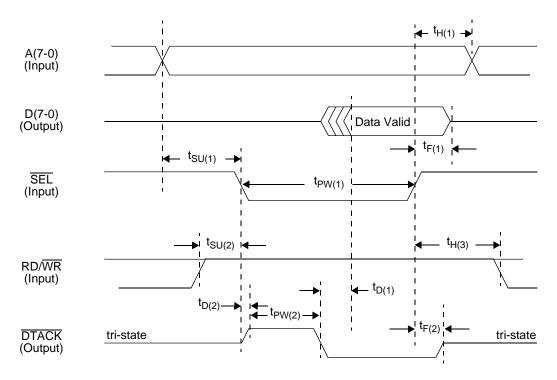

| 18.    | Motorola Mode - Microprocessor Read Cycle Timing    | 34   |

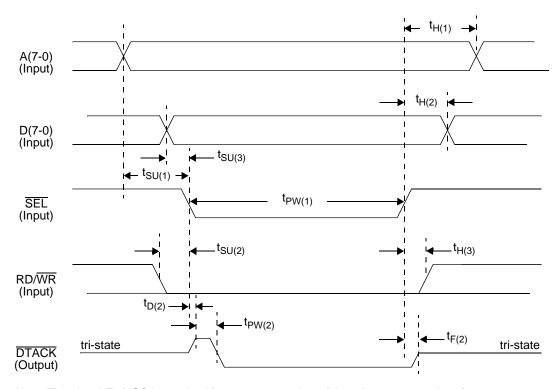

| 19.    | Motorola Mode - Microprocessor Write Cycle Timing   | 35   |

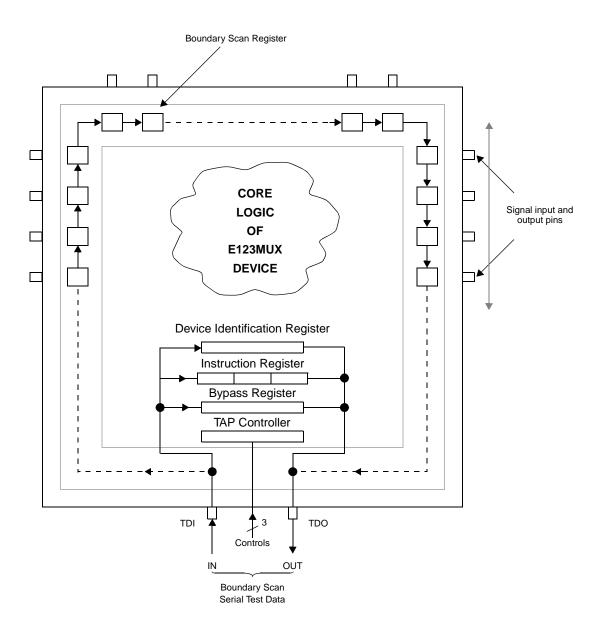

| 20.    | Boundary Scan Schematic                             |      |

| 21.    | E123MUX TXC-03361 208-pin Plastic Quad Flat Package | 77   |

<sup>\*</sup> Please note that TranSwitch provides documentation for all of its products. Current editions of many documents are available from the Products page of the TranSwitch Web site at www.transwitch.com. Customers who are using a TranSwitch Product, or planning to do so, should register with the TranSwitch Marketing Department to receive relevant updated and supplemental documentation as it is issued. They should also contact the Applications Engineering Department to ensure that they are provided with the latest available information about the product, especially before undertaking development of new designs incorporating the product.

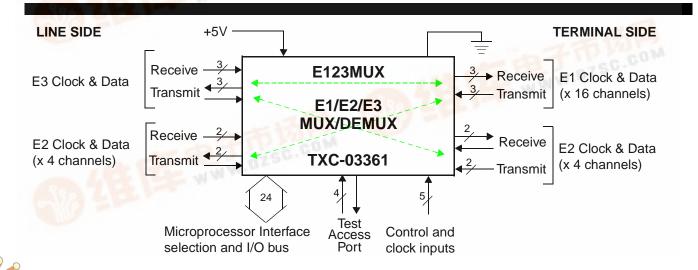

## **BLOCK DIAGRAM**

Note: Test Access Port block and Microprocessor Interface lead details are not shown. Please refer to Pin Descriptions section.

Figure 1. E123MUX TXC-03361 Block Diagram

E123MUX TXC-03361

#### **BLOCK DIAGRAM DESCRIPTION**

Figure 1 shows a simplified block diagram of the E123MUX and its signal leads. In the transmit direction (multiplexer direction), the E123MUX multiplexes 16 independent asynchronous E1 signals operating at 2048 kbit/s into four separate E2 signals operating at 8448 kbit/s. The E1 transmit signal inputs can be in either the dual rail unipolar HDB3 format (E1TDPn and E1TDNn) or in the NRZ format (E1TNRZn). The rail/NRZ interface selection is common to both the multiplexer and demultiplexer sections of the chip. The clock edge for clocking in the data is programmable for either clock (E1TCKn) edge. When the rail interface is selected, the E1 rail signal interface is monitored for loss of signal using the detect and recovery requirements specified in ITU-T Recommendation G.775. Loss of signal status information is provided along with a maskable interrupt. In addition, bipolar violations (BPVs) are counted in 16-bit counters provided for each of the E1 channels. When the NRZ interface is selected for an E1 channel, an external loss of signal indication from the external line interface unit can also be provided as an input to the E123MUX on the lead designated as E1TDNn/E1LOSn, to provide status information and a maskable interrupt for the microprocessor.

Four E1 framed or unframed asynchronous channels operating at 2048 kbit/s are multiplexed into one E2 signal, using the frame format specified in ITU-T recommendation G.742. The G.742 format consists of the 848 bits, starting with bit 1 in the frame alignment. The frame alignment pattern is defined as 1111010000. Bit 11 is defined as a remote alarm, and bit 12 is defined as a spare bit. The remaining bits carry tributary bits and justification control bits.

The four E12 multiplexers are numbered 1 through 4. Microprocessor access is provided in the transmit direction in each of the four E1 frame formats for controlling the states of the remote alarm indication bit (bit 11) and the spare bit (bit 12). Continuous framing errors may also be inserted into each of four frame formats.

The output of the four E12 multiplexers is connected internally to the E23 multiplexer section when the device is configured for E13 operation. The E2 multiplexed data and clock for the four E12 channels is not provided as an interface in this mode. However, an external 8448 kHz clock is required to be connected to the E12TCKIm input for clocking data out from the E12 multiplexer. The E23 section multiplexes each of the four E2 frames into a single E3 signal using the format specified in ITU-T recommendation G.751. The G.751 format consists of the 1536 bits, starting with bit 1 in the frame alignment. The frame alignment pattern is defined as 1111010000. Bit 11 is defined as a remote alarm, and bit 12 is defined as a spare bit. The remaining bits carry tributary bits and justification control bits. A 34368 kHz input clock (E3TCKI) is used to derive the output E3 clock (E3TCKO), which is used to clock out the E3 data. Microprocessor access is provided for controlling the states of the remote alarm indication bit (bit 11) and the spare bit (bit 12) in the E3 frame format. Continuous framing errors may also be inserted into the frame format. The output of the E23 multiplexer can be configured to be either a dual unipolar HDB3 signal or an NRZ signal. The control bit for selecting the HDB3 or NRZ format is common to the demultiplexer (receive direction). Data (E3TDP/E3TNRZ and E3TDN) is clocked out of the E123MUX using the E3 clock (E3TCKO) signal, which is derived from the E3 input clock (E3TCKI). A control bit is provided for clocking out the data on either clock edge.

In the receive direction (demultiplexed direction) from the E3 line, HDB3 or NRZ data (E3RDP/E3RNRZ and E3RDN/E3LOS) is clocked into the E123MUX using the E3 clock (E3RCKI) signal. The clock edge employed can be programmed using the microprocessor. The E23 demultiplexer monitors the incoming signal for loss of signal using the requirements specified in ITU-T recommendation G.775. Bipolar violations are counted in a 16-bit counter. In addition, the E123MUX detects frame alignment using the requirements specified in the G.751 recommendation, and monitors the line signal for AIS. Besides providing status bits for LOS, AIS, and LOF, both framing errors and loss of frame events are counted in 8-bit counters. The status bits have maskable interrupt control bits for enabling and disabling the interrupt for the microprocessor. The remote alarm bit (bit 11), and the national bit (bit 12) in the frame format are monitored for status. A threshold detector is provided for a bit error rate (BER) measurement. The E3 signal is demultiplexed into four E2 signals, which pass through 32-bit FIFOs at the output.

When the device is configured as an E13 multiplexer/demultiplexer, the four E2 signals are connected internally to the four E12 demultiplexers. However, the four E23RGCm Clock outputs must be physically connected

## TRANSWITCH'

## **DATA SHEET**

E123MUX TXC-03361

to E23RCKm clock inputs for proper operation in E13 mode. The E2 signals are available for monitoring using the data lead E23RDm and gapped clock lead.

Each of the four E2 signals is monitored for frame alignment and AIS, which are provided with status bits and maskable interrupt control bits. The states of the remote alarm bit (bit 11) and national bit (bit 12) in each of the four E2 frames are provided as status bits with associated maskable interrupts. A threshold detector is provided for a bit error rate (BER) measurement. Each of the E12s demultiplexes the E2 frame into four E1 signals. The data is written into 32-bit FIFOs using the internal gapped clock. Each E1 channel has an internal digital phase-locked loop circuit (DPLL). The receive gapped clock is connected to the digital phase-locked loop circuit as the reference frequency, along with the 34368 kHz external system clock (XCLK). The output of the DPLL is used to clock the data from the E1 receive FIFO, and is also provided as an output (E1RCKn). The E1 DPLLs require approximately 1 second of settling time after they are enabled to ensure proper operation of E1 FIFOs. Under microprocessor control, either clock edge may be used to clock out the data (E1RDPn/E1RNRZn and E1RDNn).

The E123MUX can also be configured into hybrid configurations. That is, the device can be configured to provide four E12 multiplexers and demultiplexers (16 E1 channels to/from four E2 channels), and one E23 multiplexer and demultiplexer (four E2 channels to/from one E3 channel). In this configuration, the format of the data from the four multiplexers and demultiplexers at the E2 level is NRZ only. In the multiplex direction, the data (E12TDm) from the four sections is clocked out by the E2 clocks (E12TCKOm). The NRZ data input (E23TDn) to the E23 multiplexer is clocked in by the E2 clocks (E23TCKm). The clock edges used for clocking in and out data from the E23 section are programmable.

In the demultiplex direction, four E23 gapped output clocks are provided on leads E23RGCm. E2 data (E23RDm) is clocked out of the internal FIFO by the receive input clock (E23RCKm). It is assumed that external DPLLs will be used in this configuration to provide a symmetrical clock, and that the outputs of the DPLLs are connected to the E23RCKm leads for E2 operation. The receive data input to the four E12 demultiplexers consists of data (E12RDm) and clock (E12RCKm).

If an E23 demultiplexer is connected to the E12 demultiplexer to provide E3 to E1 demultiplexing, the E23 receive gapped clock lead (E23RGCm) is connected to the E23 receive input clock (E23RCKm) and the E12 receive input clock (E12RCKm). The E23 data leads (E23RDm) are connected to the E12 receive data leads (E12RDm). The clock edges used for clocking data into and out of the E12 sections are programmable.

The E123MUX provides a number of testing features, including an E1 PRBS generator and analyzer. The PRBS sequence is a 2<sup>15</sup>-1 polynomial, and the sequence corresponds to the sequence specified in the ITU-T O-151 recommendation. The E1 transmit channel to be used for inserting the PRBS pattern is programmable. The E1 receive channel to be analyzed is also programmable, and is independent of the channel selected in the transmit direction. Only one channel at a time is programmable for PRBS testing in each direction.

The E123MUX also supports individual E1 remote loopbacks, E2 local and remote loopbacks, and E3 local and remote loopbacks. Remote loopback enables the receive clock and data leads to be looped back as transmit clock and data in the upstream direction.

For device testing, both boundary scan and an option to force all bidirectional outputs to a high impedance state for board testing are provided.

The microprocessor interface supports a multiplexed 8-bit address/data bus, an Intel-compatible split bus or a Motorola-compatible split bus. The split bus has 8 address bits and 8 data bits. Interrupt capability is also provided, with the ability to mask an active alarm status from causing an interrupt.

E123MUX TXC-03361

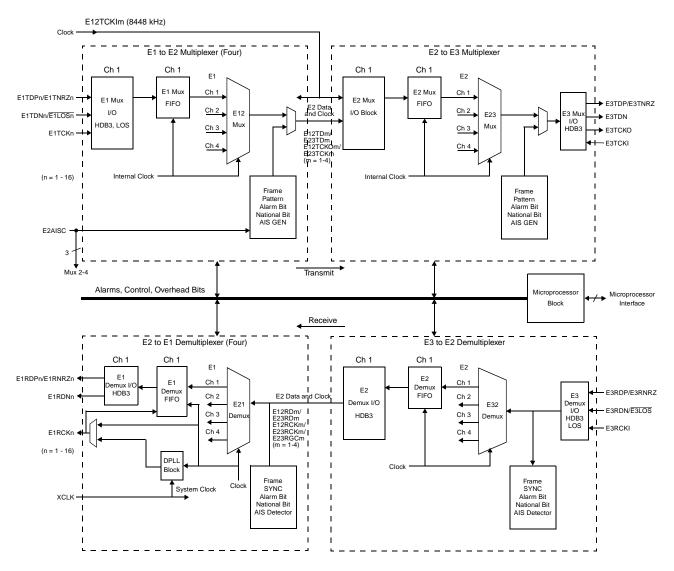

#### **PIN DIAGRAM**

#### Notes:

- 1. An X(Y/Z) format is used for symbol names of microprocessor interface signal pins to identify pin functions in the Multiplexed Address/Data [X] and (Intel [Y] / Motorola [Z]) modes of operation, where these functions are different.

- 2. Active low (inverted) signals are indicated by '-' at end of symbol (e.g., RESET- is equivalent to RESET).

- 3. Some pin symbols have been abbreviated due to space limitations (see Pin Descriptions section for complete symbols).

Figure 2. E123MUX TXC-03361 Pin Diagram

## TRANSWITCH'

## **DATA SHEET**

## **PIN DESCRIPTIONS**

## **POWER SUPPLY AND GROUND**

| Symbol | Pin No.                                                                              | I/O/P* | Туре | Name/Function                                   |

|--------|--------------------------------------------------------------------------------------|--------|------|-------------------------------------------------|

| VDD    | 14, 27, 64, 73, 74, 87,<br>121, 135, 136, 174,<br>181, 182                           | Р      |      | V <sub>DD</sub> : +5 volt supply voltage, ± 5%. |

| GND    | 13, 26, 32, 63, 75, 76,<br>85, 86, 122, 137, 138,<br>142, 143, 173, 183,<br>184, 193 | Р      |      | Ground: 0 volts reference                       |

<sup>\*</sup>Note: I = Input; O = Output; P = Power; T = Tri-state; D = Open Drain Tri-state

## **E1 RECEIVE AND TRANSMIT INTERFACES**

| Symbol                                             | Pin No.                                                                                               | I/O/P | Type *       | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------------------------------------------|-------------------------------------------------------------------------------------------------------|-------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| E1RDPn/<br>E1RNRZn<br>(n = 1 - 16)<br>n=4><br>n=8> | 145<br>148<br>151<br>154<br>107<br>110<br>113<br>116<br>159<br>162<br>165<br>168<br>175<br>178<br>185 | 0     | CMOS<br>2 mA | Receive Positive Rail/NRZ Output, E1 Channels 1 - 16: These pins are used for output of the receive positive rail HDB3 signal, or the receive NRZ signal, for E1 channels 1 through 16. Dual rail unipolar or NRZ mode may be selected for each channel independently, by setting 16 control bits. Pin 145 represents the output signal for E1 channel 1, while pin 188 represents channel 16. The positive rail or NRZ signals for all 16 ports are clocked out of the E123MUX on rising edges of the receive clocks E1RCKn when control bit RE1CS is a 1, and on falling edges of the clocks when the control bit is set to 0. |

| E1RDNn<br>(n = 1 - 16)<br>n=4>                     | 146<br>149<br>152<br>155<br>108<br>111<br>114<br>117<br>160<br>163<br>166                             | 0     | CMOS<br>2 mA | Receive Negative Rail Output, E1 Channels 1 - 16: These pins are used for the receive negative rail HDB3 signal outputs for E1 channels 1 through 16. Pin 146 represents the negative rail signal for E1 channel 1, while pin 189 represents channel 16. The negative rail signals for all 16 ports are clocked out of the E123MUX on rising edges of the receive clocks E1RCKn when control bit RE1CS is a 1, and on falling edges of the clocks when this control bit is set to 0. This pin is disabled when the NRZ mode is selected for a channel.                                                                           |

| n=12><br>n=16>                                     | 169<br>176<br>179<br>186<br>189                                                                       |       |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

<sup>\*</sup>See Input, Output and I/O Parameters section below for Type definitions.

# TRANSWITCH DATA SHEET

| Symbol                                     | Pin No.                       | I/O/P | Туре         | Name/Function                                                                                                                                                                                                                                                                                                                                         |

|--------------------------------------------|-------------------------------|-------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| E1RCKn<br>(n = 1 - 16)                     | 147<br>150<br>153             | 0     | CMOS<br>2 mA | Receive Output Clock, E1 Channels 1 - 16: These pins provide receive output clocks for E1 channels 1 through 16. These clocks are derived from internal DPLLs using                                                                                                                                                                                   |

| n=4>                                       | 156<br>109<br>112             |       |              | the system clock (XCLK) and the internal E1 receive gapped clock. When control bit BPPLLm is a 1 (m = 1 to 4, for n = 1-4, 5-8, 9-12 and 13-16), the DPLL is bypassed                                                                                                                                                                                 |

| n=8>                                       | 115<br>118<br>161             |       |              | and the output is the receive gapped clock. Pin 147 represents channel 1, while pin 190 represents channel 16.                                                                                                                                                                                                                                        |

| n=12>                                      | 164<br>167<br>170<br>177      |       |              |                                                                                                                                                                                                                                                                                                                                                       |

| n=16>                                      | 180<br>187<br>190             |       |              |                                                                                                                                                                                                                                                                                                                                                       |

| E1TDPn/<br>E1TNRZn<br>(n = 1 - 16)<br>n=4> | 1<br>4<br>7<br>10             | ı     | TTL          | Transmit Positive Rail/NRZ Input, E1 Channels 1 - 16:<br>These pins are used for the transmit positive rail HDB3 signal inputs, or the transmit NRZ signal inputs, for E1 channels 1 through 16. Dual rail unipolar or NRZ mode may be                                                                                                                |

| 11=4>                                      | 33<br>36<br>39                |       |              | selected for each channel independently by setting 16 control bits. Pin 1 represents the input signal for E1 channel 1, while pin 203 represents channel 16. The positive rail or NRZ signal input for channel n is clocked into the                                                                                                                  |

| n=8>                                       | 42<br>48<br>51<br>54          |       |              | E123MUX on rising edges of the transmit clock E1TCKn when control bit TE1CS is a 0, and on falling edges of this clock when this control bit is set to 1.                                                                                                                                                                                             |

| n=12>                                      | 57<br>194<br>197<br>200       |       |              |                                                                                                                                                                                                                                                                                                                                                       |

| n=16>                                      | 203                           |       |              |                                                                                                                                                                                                                                                                                                                                                       |

| E1TDNn/<br>E1LOSn<br>(n = 1 - 16)<br>n=4>  | 2<br>5<br>8<br>11<br>34<br>37 | 1     | TTL          | Transmit Negative Rail Input or Loss of Signal Input, E1 Channels 1 - 16: In the dual rail unipolar operating mode, these pins are used for the transmit negative rail HDB3 signal inputs for E1 channels 1 through 16. Pin 2 represents the input negative rail signal for E1 channel 1, while pin 204 represents channel 16. The negative rail sig- |

| n=8>                                       | 40<br>43<br>49<br>52          |       |              | nal for channel n is clocked into the E123MUX on rising edges of the transmit clock E1TCKn when control bit TE1CS is a 0, and on falling edges of this clock when this control bit is set to 1.                                                                                                                                                       |

| n=12>                                      | 55<br>58<br>195<br>198        |       |              | When the NRZ operating mode is selected for a channel, this pin may be used as the input for an external E1 loss of signal (LOS) indication from an external line interface unit. E1LOSn is active low. Any of these pins that are not used                                                                                                           |

| n=16>                                      | 201<br>204                    |       |              | for LOS inputs must be held high.                                                                                                                                                                                                                                                                                                                     |

E123MUX TXC-03361

| Symbol       | Pin No. | I/O/P | Туре | Name/Function                                               |

|--------------|---------|-------|------|-------------------------------------------------------------|

| E1TCKn       | 3       | ļ     | CMOS | Transmit Input Clock, E1 Channels 1 - 16: These pins        |

| (n = 1 - 16) | 6       |       |      | provide the transmit input clocks for E1 channels 1 through |

|              | 9       |       |      | 16. Pin 3 represents channel 1, while pin 205 represents    |

| n=4>         | 12      |       |      | channel 16. The clock frequency must be 2048 kHz ± 50       |

|              | 35      |       |      | ppm and the duty cycle must be (50 $\pm$ 10) %.             |

|              | 38      |       |      |                                                             |

|              | 41      |       |      |                                                             |

| n=8>         | 44      |       |      |                                                             |

|              | 50      |       |      |                                                             |

|              | 53      |       |      |                                                             |

|              | 56      |       |      |                                                             |

| n=12>        | 59      |       |      |                                                             |

|              | 196     |       |      |                                                             |

|              | 199     |       |      |                                                             |

| 40           | 202     |       |      |                                                             |

| n=16>        | 205     |       |      |                                                             |

## E2 RECEIVE AND TRANSMIT INTERFACES (E12 MULTIPLEXERS/DEMULTIPLEXERS 1-4)

| Symbol                  | Pin No.                  | I/O/P | Туре         | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------------------|--------------------------|-------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| E12RDm<br>(m = 1 - 4)   | 157<br>119<br>171<br>191 | ı     | TTL          | Receive E12 Data: These four pins are used for the receive E2 NRZ data input signals when the E123MUX is configured as a separate E12 multiplexer/demultiplexer. Pin 157 corresponds to the E12 multiplexer/demultiplexer number 1, which is associated with E1 channels 1 - 4. In the E13 mode of operation these pins are connected internally to the corresponding E23RDm output pins.                            |

| E12RCKm<br>(m = 1 - 4)  | 158<br>120<br>172<br>192 | I     | CMOS         | Receive E12 Clock: These four pins are used to clock in the receive E2 NRZ data signals. Pin 158 corresponds to the E12 multiplexer/demultiplexer number 1. Receive data is clocked into the E123MUX on rising edges of this clock. In the E13 mode of operation these pins are connected internally to the corresponding E23RGCm output pins.                                                                       |

| E12TDm<br>(m = 1 - 4)   | 16<br>46<br>61<br>207    | 0     | CMOS<br>2 mA | Transmit E12 Data: These four pins are used to output the transmit E2 NRZ data signal when the E123MUX is configured as a separate E12 multiplexer/demultiplexer. Pin 16 corresponds to the E12 multiplexer number 1, which is associated with E1 channels 1 - 4. In the E13 mode of operation these pins are connected internally to the corresponding E23TDm pins.                                                 |

| E12TCKIm<br>(m = 1 - 4) | 15<br>45<br>60<br>206    | ı     | CMOS         | <b>Transmit E12 Clock Input:</b> These four pins are used to provide input clocks for clocking out the transmit E2 NRZ data output signals E12TDm and clock signal E12TCKOm. Pin 15 corresponds to the E12 multiplexer/demultiplexer number 1. Please note that an 8448 kHz clock with a $\pm$ 30 ppm tolerance and a duty cycle of (50 $\pm$ 10) % must be connected to these pins for proper E12 to E23 operation. |

E123MUX TXC-03361

| Symbol                  | Pin No.               | I/O/P | Туре         | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------------------|-----------------------|-------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| E12TCKOm<br>(m = 1 - 4) | 17<br>47<br>62<br>208 | 0     | CMOS<br>2 mA | Transmit E12 Clock Output: These four pins are used to provide output clocks for clocking out the transmit E2 NRZ data output signals (E12TDm). Pin 17 corresponds to the E12 multiplexer/demultiplexer number 1. Transmit data is clocked out of the E12 on rising edges of this clock in E13 mode. In E12 skip mux mode this is programmable by control bit T12CSm. In the E13 mode of operation the E12TCKOm signals are connected internally to the corresponding E23TCKm signals. |

## E2 RECEIVE AND TRANSMIT INTERFACES (E23 MULTIPLEXER/DEMULTIPLEXER)

| Symbol                 | Pin No.                  | I/O/P | Туре         | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------------------|--------------------------|-------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| E23RDm<br>(m = 1 - 4)  | 123<br>126<br>129<br>132 | 0     | CMOS<br>2 mA | Receive E23 Data: These four pins are used to output the receive E2 NRZ data signals when the E123MUX is configured as a separate E23 multiplexer/demultiplexer. Pin 123 corresponds to the E23 demultiplexer E2 output channel number 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| E23RGCm<br>(m = 1 - 4) | 125<br>128<br>131<br>134 | 0     | CMOS<br>2 mA | Receive Gapped E23 Clock: These four pins provide the receive gapped clock outputs for the E23 demultiplexer when the E123MUX is configured for E23 operation. These clocks are the write clocks of an internal FIFO. These clocks may be connected to an external digital PLL if the E123MUX is used in hybrid configurations (E12 and E23 sections). The dejittered clock from the digital PLL is connected to the E23RCKm input clocks. This clock is derived from the received E3 34368 kHz clock. Pin 125 represents the output gapped clock for E2 channel 1. Please note that, for E13 operation, the E23RGCm output receive gapped clock leads must be connected to the corresponding E23RCKm input clock leads.                                                                                                                          |

| E23RCKm<br>(m = 1 - 4) | 124<br>127<br>130<br>133 | -     | CMOS         | Receive Input Clock: These four pins provide the input clocks for clocking out the receive data from the E23 demultiplexer when the E123MUX is configured for E23 operation. The receive data is clocked out of an internal FIFO. For hybrid configurations these clocks may be connected to digital PLLs. The NRZ signal for channel m is clocked out of the E23 on rising edges of the E23RCKm clocks when control bit R23CSm is a 1, and on falling edges of this clock when the control bit is set to 0. Pin 124 represents the input clock for E2 channel 1. Please note that, for E13 operation, the E23RCKm input clock leads must be connected to the corresponding E23RGCm output receive gapped clock leads. For the E23 remote loopback function, it is required that the E23RGCm output be dejittered prior to connecting to E23RCKm. |

E123MUX TXC-03361

| Symbol                 | Pin No.              | I/O/P | Туре | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------------------|----------------------|-------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| E23TDm<br>(m = 1 - 4)  | 18<br>20<br>22<br>24 | ı     | TTL  | Transmit E2 Data: These four pins are used for the transmit E2 NRZ data input signals when the E123MUX is configured as an E23 multiplexer/demultiplexer. Pin 18 corresponds to the E23 multiplexer/demultiplexer E2 input channel number 1. When in E13 skip mux mode these input pins are ignored by the internal logic. For E13 operation these unused pins should be attached to a common pull-up resistor.                                                                                                                                                                                                                                                                                                                                                                     |

| E23TCKm<br>(m = 1 - 4) | 19<br>21<br>23<br>25 | I     | CMOS | Transmit E2 Clock: These four pins are used to provide input clocks for clocking in the transmit E2 NRZ data input signals when the E123MUX is configured for E23 operation. Pin 19 represents the input clock for E23 multiplexer/demultiplexer E2 input channel number 1. Transmit data is clocked into the E123MUX on rising edges of this clock when control bit T23CSm is a 0, and on falling edges of this clock when the control bit is set to 1 for each E23 multiplexer. When in E13 Mode, these input pins are ignored and the clocking is done by internal logic. For E13 Mode, these pins should be attached to a common pull-up resistor. When in E23 Mode, the input clock frequency must be 8448 kHz with $\pm$ 30 ppm accuracy and a duty cycle of (50 $\pm$ 10) %. |

## **E3 RECEIVE AND TRANSMIT INTERFACES**

| Symbol           | Pin No. | I/O/P | Туре         | Name/Function                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|------------------|---------|-------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| E3RDP/<br>E3RNRZ | 140     | I     | TTL          | Receive E3 Positive Rail/NRZ Input: This pin is used for the receive E3 positive rail HDB3 signal input, or the receive E3 NRZ signal input.                                                                                                                                                                                                                                       |  |  |

| E3RDN/<br>E3LOS  | 141     | I     | TTL          | Receive E3 Negative Rail Input/E3 LOS Input: In dual rail unipolar mode, this pin is used for the receive E3 negative rail HDB3 signal input. When the NRZ operating mode is selected, this pin may be used as the input for an active low external E3 loss of signal (LOS) indication from an external line interface unit. If this pin is not used for LOS it must be tied high. |  |  |

| E3RCKI           | 139     | I     | CMOS         | Receive E3 Clock In: The E3 positive and negative rail signals or the E3 NRZ signal are clocked into the E123MUX on rising edges of this clock input signal when control bit RE3CS is a 0, and on falling edges when this control bit is a 1.                                                                                                                                      |  |  |

| E3TDP/<br>E3TNRZ | 28      | 0     | CMOS<br>2 mA | <b>Transmit E3 Positive Rail/NRZ Output:</b> This pin is used for the transmit E3 positive rail HDB3 signal output, or the transmit NRZ signal output.                                                                                                                                                                                                                             |  |  |

| E3TDN            | 29      | 0     | CMOS<br>2 mA | <b>Transmit E3 Negative Rail Output:</b> This pin is used for the transmit E3 negative rail HDB3 signal output. This lead is disabled when the NRZ mode is selected.                                                                                                                                                                                                               |  |  |

E123MUX TXC-03361

| Symbol | Pin No. | I/O/P | Туре         | Name/Function                                                                                                                                                                                                                                                          |

|--------|---------|-------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ЕЗТСКО | 31      | 0     | CMOS<br>2 mA | Transmit E3 Clock Output: The E3 positive and negative rail signals or the E3 NRZ signal are clocked out of the E123MUX on rising edges of this clock when control bit TE3CS is a 1, and on falling edges when this control bit is a 0. E3TCKO is derived from E3TCKI. |

| E3TCKI | 30      | I     | CMOS         | <b>Transmit E3 Clock Input:</b> This input clock frequency must be 34368 kHz $\pm$ 20 ppm and the duty cycle must be (50 $\pm$ 5) %.                                                                                                                                   |

## **EXTERNAL CLOCK INPUTS**

| Symbol | Pin No. | I/O/P | Туре | Name/Function                                                                                                                                                                                                                                                                                                                                                                            |

|--------|---------|-------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| XCLK   | 72      | I     | CMOS | <b>External Clock:</b> A 34368 kHz clock with $\pm$ 20 ppm accuracy and a duty cycle of (50 $\pm$ 5) % must be connected to this pin. It is used by the E123MUX as a reference for the internal E1 digital PLLs.                                                                                                                                                                         |

| E2AISC | 144     | I     | CMOS | <b>E2 AIS External Clock:</b> An 8448 kHz clock with ± 30 ppm accuracy and a duty cycle of (50 ± 10) % must be connected to this pin. It is used by the E123MUX for E2 AIS generation during fault conditions. This clock may also be connected to the Transmit E12 Clock Input pins (E12TCKIm).  Note: This clock is required for the proper operation of the microprocessor interface. |

## **CONTROL LEADS**

| Symbol | Pin No. | I/O/P | Туре | Name/Function                                                                                                                                                                                                                                               |

|--------|---------|-------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HIGHZ  | 68      | I     | TTL  | High Impedance Enable: A low forces all E123MUX output and bidirectional leads (except TDO) to a high impedance state for board level testing. For normal operation this pin must be held high.                                                             |

| TEST   | 69      | I     | TTL  | TranSwitch Test Mode: For normal operation this pin must be held high.                                                                                                                                                                                      |

| RESET  | 70      | I     | TTL  | <b>Reset:</b> An active low on this lead resets the internal state machines, counters and control registers to their default states. The reset signal should be held low for a minimum of 150 nanoseconds. It should be applied after power becomes stable. |

E123MUX TXC-03361

## **TEST ACCESS PORT FOR BOUNDARY SCAN**

| Symbol | Pin No. | I/O/P | Туре         | Name/Function                                                                                                                                                                                                                                                                                                                                                                       |

|--------|---------|-------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TCK    | 100     | I     | TTL          | <b>Test Clock:</b> This is the input clock for boundary scan testing. The TDI and TMS states are clocked into the E123MUX on rising edges of this clock.                                                                                                                                                                                                                            |

| TDI    | 99      | Ι     | TTLp         | <b>Test Data Input:</b> Serial data input for boundary scan test messages. This lead has an internal pull-up resistor.                                                                                                                                                                                                                                                              |

| TDO    | 102     | O(T)  | CMOS<br>4 mA | <b>Test Boundary Data Output:</b> Serial data output whose information is clocked out on falling edges of TCK.                                                                                                                                                                                                                                                                      |

| TMS    | 98      | I     | TTLp         | <b>Test Boundary Mode Select:</b> This input signal is used to control test operations. This lead has an internal pull-up resistor.                                                                                                                                                                                                                                                 |

| TRS    | 101     | _     | TTLp         | Test Boundary Scan Reset: This pin must be either held low or asserted low, then high (pulsed low) for a minimum of 500 ns to asynchronously reset the Test Access Port (TAP) controller. Failure to perform this reset may cause the TAP controller to take over control of the output pins. See Test Access Port Section for details. This lead has an internal pull-up resistor. |

#### **TEST PINS**

| Symbol   | Pin No. | I/O/P | Туре         | Name/Function                                                          |

|----------|---------|-------|--------------|------------------------------------------------------------------------|

| TESTCK   | 96      | 0     | CMOS<br>2 mA | <b>Test Scan Clock:</b> Provided for TranSwitch testing purposes only. |

| TESTDATA | 97      | 0     | CMOS<br>2 mA | <b>Test Scan Data:</b> Provided for TranSwitch testing purposes only.  |

## **MICROPROCESSOR SELECTION**

| Symbol     | Pin No.  | I/O/P | Туре | Name/Function |            |                                                                                                                                                                                                        |  |

|------------|----------|-------|------|---------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| MP0<br>MP1 | 66<br>67 | _     | TTL  | micropr       | ocessor ir | Selection Control Bits: The type of nterface bus is selected according to the e table below:  Selection Motorola-compatible bus I/O Reserved. Do not use. Intel-compatible bus I/O Multiplexed bus I/O |  |

E123MUX TXC-03361

## MICROPROCESSOR INTERFACE - MULTIPLEXED BUS

| Symbol   | Pin No. | I/O/P | Туре         | Name/Function                                                                                                                                                                                                                                                                       |  |  |

|----------|---------|-------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| A/D(7-0) | 77 - 84 | I/O   | TTL<br>4 mA  | Address/Data Bus: Address input leads and bidirectional data leads used for selecting the address and transferring data between the E123MUX and the microprocessor. High is logic one. A/D0 (pin 84) is the least significant bit.                                                  |  |  |

| ALE      | 105     | I     | TTL          | Address Latch Enable: An active high signal generated by the microprocessor. It is used for holding an address stable during a read/write cycle when in multiplexed mic processor mode. This pin should be held high in Motoro Intel modes.                                         |  |  |

| SEL      | 71      | I     | TTL          | <b>Select:</b> A low enables data transfers between the microprocessor and the E123MUX during a read/write cycle.                                                                                                                                                                   |  |  |

| RD       | 104     | I     | TTL          | <b>Read:</b> An active low signal generated by the microprocessor for reading the E123MUX memory map locations.                                                                                                                                                                     |  |  |

| WR       | 103     | I     | TTL          | <b>Write:</b> An active low signal generated by the microprocessor for writing to the E123MUX memory map locations.                                                                                                                                                                 |  |  |

| RDY      | 106     | O(T)  | CMOS<br>4 mA | <b>Ready</b> : A high is an acknowledgment from the addressed memory location that the transfer can be completed. A low indicates that the transfer cannot be completed and that microprocessor wait states must be generated. This lead is tri-stated when not driven high or low. |  |  |

| INT      | 65      | O(D)  | CMOS<br>2 mA | Interrupt: A high on this output pin signals an interrupt request to the microprocessor when an alarm occurs while the interrupt mask bit for that alarm is disabled (set to 0). This pin is open drain and requires a 4.7 kilohm pull-up resistor for proper operation.            |  |  |

E123MUX TXC-03361

## MICROPROCESSOR INTERFACE - SPLIT BUS

| Symbol           | Pin No. | I/O/P | Туре         | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------------------|---------|-------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A(7-0)           | 88 - 95 | I     | TTL          | Address Bus (Intel/Motorola Interfaces): These are address line inputs that are used for accessing a memory location for a read/write cycle. High is logic one. A0 (pin 95) is the least significant bit.                                                                                                                                                                                                                                                                                                                                                                                    |

| D(7-0)           | 77 - 84 | I/O   | TTL<br>4 mA  | <b>Data Bus (Intel/Motorola Interfaces):</b> These are bidirectional data lines used for transferring data between the memory and the microprocessor. High is logic one. D0 (pin 84) is the least significant bit.                                                                                                                                                                                                                                                                                                                                                                           |

| SEL              | 71      | I     | TTL          | <b>Select (Intel/Motorola Interfaces):</b> A low enables data transfers between the microprocessor and the E123MUX during a read/write cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| RD<br>/<br>RD/WR | 104     | I     | TTL          | Read (Intel Interface) or Read/Write (Motorola): Intel Interface - An active low signal generated by the microprocessor for reading the E123MUX memory map locations. Motorola Interface - An active high signal is generated by the microprocessor for reading the E123MUX memory map locations. An active low signal is used to write to E123MUX memory map locations.                                                                                                                                                                                                                     |

| WR/DS            | 103     | I     | TTL          | Write (Intel Interface) or Data Select (Motorola): Intel Interface - An active low signal generated by the microprocessor for writing to the E123MUX memory map locations. Motorola Interface - An active low signal generated by the microprocessor to select the data to be read or written. Connect to the $\overline{\rm DS}$ signal at the microprocessor.                                                                                                                                                                                                                              |

| RDY/<br>DTACK    | 106     | O(T)  | CMOS<br>4 mA | Ready (Intel Interface) or Data Transfer Acknowledge (Motorola Interface): Intel Interface - A high is an acknowledgment from the addressed memory map location that the transfer can be completed. A low indicates that the E123MUX cannot complete the transfer cycle and that microprocessor wait states must be generated.  Motorola Interface - During a read bus cycle, a low signal indicates that the information on the data bus is valid.  During a write bus cycle, a low signal acknowledges the acceptance of data.  This lead is tri-stated when it is not driven high or low. |

| INT/ĪRQ          | 65      | O(D)  | CMOS<br>2 mA | Interrupt (Intel Interface) or Interrupt Request (Motorola Interface): Intel Interface - A high on this output pin signals an interrupt to the microprocessor when an alarm occurs while the interrupt mask bit for that alarm is disabled (set to 0). Motorola Interface - A low on this output pin signals an interrupt request to the microprocessor when an alarm occurs while the interrupt mask bit for that alarm is disabled (set to 0). This pin is open drain tri-state and requires a 4.7 kilohm pull-up resistor for proper operation in both Intel and Motorola Modes.          |

E123MUX TXC-03361

## ABSOLUTE MAXIMUM RATINGS AND ENVIRONMENTAL LIMITATIONS

| Parameter                          | Symbol          | Min                    | Max                   | Unit   | Conditions                     |

|------------------------------------|-----------------|------------------------|-----------------------|--------|--------------------------------|

| Supply voltage                     | V <sub>DD</sub> | -0.3                   | +7.0                  | V      | Note 1                         |

| DC input voltage                   | V <sub>IN</sub> | -0.5                   | V <sub>DD</sub> + 0.5 | V      | Note 1                         |

| Storage temperature range          | T <sub>S</sub>  | -55                    | 150                   | °С     | Note 1                         |

| Ambient operating temperature      | T <sub>A</sub>  | -40                    | 85                    | °С     | 0 ft/min linear airflow        |

| Component Temperature x Time       | TI              |                        | 270 x 5               | °C x s | Note 1                         |

| Moisture Exposure Level            | ME              | 5                      |                       | Level  | per EIA/JEDEC<br>JESD22-A112-A |

| Relative Humidity, during assembly | RH              | 30                     | 60                    | %      | Note 2                         |

| Relative Humidity, in-circuit      | RH              | 0                      | 100                   | %      | non-condensing                 |

| ESD Classification                 | ESD             | SD absolute value 2000 |                       | V      | Note 3                         |

#### Notes:

- 1. Conditions exceeding the Min or Max values may cause permanent failure. Exposure to conditions near the Min or Max values for extended periods may impair device reliability.

- 2. Pre-assembly storage in non-drypack conditions is not recommended. Please refer to the instructions on the "CAUTION" label on the drypack bag in which devices are supplied.

- 3. Test method for ESD per MIL-STD-883D, Method 3015.7.

## THERMAL CHARACTERISTICS

| Parameter                                | Min | Тур  | Max | Unit | Test Conditions         |

|------------------------------------------|-----|------|-----|------|-------------------------|

| Thermal resistance - junction to ambient |     | 26.0 |     | °C/W | 0 ft/min linear airflow |

## **POWER REQUIREMENTS**

| Parameter       | Min  | Тур | Max  | Unit | Test Conditions  |

|-----------------|------|-----|------|------|------------------|

| $V_{DD}$        | 4.75 | 5.0 | 5.25 | V    |                  |

| I <sub>DD</sub> |      |     | 285  | mA   |                  |

| P <sub>DD</sub> |      |     | 1500 | mW   | Inputs switching |

E123MUX TXC-03361

## **INPUT, OUTPUT AND I/O PARAMETERS**

## **Input Parameters For TTL**

| Parameter             | Min | Тур | Max | Unit | Test Conditions                                   |

|-----------------------|-----|-----|-----|------|---------------------------------------------------|

| V <sub>IH</sub>       | 2.0 |     |     | V    | 4.75 <u>&lt;</u> V <sub>DD</sub> ≤ 5.25           |

| V <sub>IL</sub>       |     |     | 0.8 | V    | 4.75 <u>&lt;</u> V <sub>DD</sub> <u>&lt;</u> 5.25 |

| Input leakage current |     |     | 10  | μΑ   | V <sub>DD</sub> =5.25                             |

| Input capacitance     |     | 5.0 |     | pF   |                                                   |

## **Input Parameters For TTLp**

| Parameter             | Min | Тур | Max | Unit | Test Conditions                                   |

|-----------------------|-----|-----|-----|------|---------------------------------------------------|

| V <sub>IH</sub>       | 2.0 |     |     | V    | 4.75 <u>&lt;</u> V <sub>DD</sub> <u>≤</u> 5.25    |

| V <sub>IL</sub>       |     |     | 0.8 | V    | 4.75 <u>&lt;</u> V <sub>DD</sub> <u>&lt;</u> 5.25 |

| Input leakage current |     |     | 550 | μΑ   | $V_{DD}$ =5.25; Input = 0 volts                   |

| Input capacitance     |     | 5.5 |     | pF   |                                                   |

#### **Input Parameters For CMOS**

| Parameter             | Min  | Тур | Max  | Unit | Test Conditions                                   |

|-----------------------|------|-----|------|------|---------------------------------------------------|

| V <sub>IH</sub>       | 3.15 |     |      | V    | 4.75 <u>&lt;</u> V <sub>DD</sub> <u>≤</u> 5.25    |

| V <sub>IL</sub>       |      |     | 1.65 | V    | 4.75 <u>&lt;</u> V <sub>DD</sub> <u>&lt;</u> 5.25 |

| Input leakage current |      |     | 10   | μΑ   | V <sub>DD</sub> =5.25                             |

| Input capacitance     |      | 5.0 |      | pF   |                                                   |

## Output Parameters For CMOS 2 mA (Open Drain)

| Parameter       | Min | Тур | Max | Unit | Test Conditions               |

|-----------------|-----|-----|-----|------|-------------------------------|

| V <sub>OL</sub> |     |     | 0.4 | V    | $V_{DD} = 4.75; I_{OL} = 2.0$ |

| I <sub>OL</sub> |     |     | 2.0 | mA   |                               |

Note: Open Drain requires use of an external 4.7 kilohm pull-up resistor for proper operation.

E123MUX TXC-03361

## **Output Parameters For CMOS 2 mA**

| Parameter         | Min                   | Тур | Max   | Unit | Test Conditions                                |

|-------------------|-----------------------|-----|-------|------|------------------------------------------------|

| V <sub>OH</sub>   | V <sub>DD</sub> - 0.5 |     |       | V    | V <sub>DD</sub> = 4.75; I <sub>OH</sub> = -2.0 |

| V <sub>OL</sub>   |                       |     | 0.4   | V    | $V_{DD} = 4.75; I_{OL} = 2.0$                  |

| I <sub>OL</sub>   |                       |     | 2.0   | mA   |                                                |

| I <sub>OH</sub>   |                       |     | -2.0  | mA   |                                                |

| t <sub>RISE</sub> |                       |     | 10    | ns   | C <sub>LOAD</sub> = 15 pF                      |

| t <sub>FALL</sub> |                       |     | 10    | ns   | C <sub>LOAD</sub> = 15 pF                      |

| Leakage Tri-state |                       |     | +/-10 | μΑ   | 0 to 5.25 V input                              |

## **Output Parameters For CMOS 4mA**

| Parameter                              | Min                   | Тур | Max           | Unit | Test Conditions                                |

|----------------------------------------|-----------------------|-----|---------------|------|------------------------------------------------|

| V <sub>OH</sub>                        | V <sub>DD</sub> - 0.8 |     |               | V    | V <sub>DD</sub> = 4.75; I <sub>OH</sub> = -4.0 |

| V <sub>OL</sub>                        |                       |     | 0.5           | ٧    | $V_{DD} = 4.75; I_{OL} = 4.0$                  |

| I <sub>OL</sub>                        |                       |     | 4.0           | mA   |                                                |

| I <sub>OH</sub>                        |                       |     | -4.0          | mA   |                                                |

| I <sub>OZ</sub> (HIGHZ output current) |                       |     | <u>+</u> 10.0 | μΑ   |                                                |

## Input/Output Parameters For TTL 4 mA (slew rate controlled)

| Parameter             | Min | Тур | Max  | Unit | Test Conditions                                   |

|-----------------------|-----|-----|------|------|---------------------------------------------------|

| V <sub>IH</sub>       | 2.0 |     |      | V    | 4.75 <u>&lt;</u> V <sub>DD</sub> <u>&lt;</u> 5.25 |

| V <sub>IL</sub>       |     |     | 0.8  | V    | 4.75 ≤V <sub>DD</sub> ≤ 5.25                      |

| Input leakage current |     |     | 10   | μΑ   | V <sub>DD</sub> = 5.25                            |

| Input capacitance     |     | 7.0 |      | pF   |                                                   |

| V <sub>OH</sub>       | 2.4 |     |      | V    | V <sub>DD</sub> = 4.75; I <sub>OH</sub> = -2.0    |

| V <sub>OL</sub>       |     |     | 0.4  | V    | V <sub>DD</sub> = 4.75; I <sub>OL</sub> = 4.0     |

| I <sub>OL</sub>       |     |     | 4.0  | mA   |                                                   |

| Гон                   |     |     | -2.0 | mA   |                                                   |

| t <sub>RISE</sub>     |     |     | 10   | ns   | C <sub>LOAD</sub> = 25 pF                         |

| t <sub>FALL</sub>     |     |     | 5    | ns   | C <sub>LOAD</sub> = 25 pF                         |

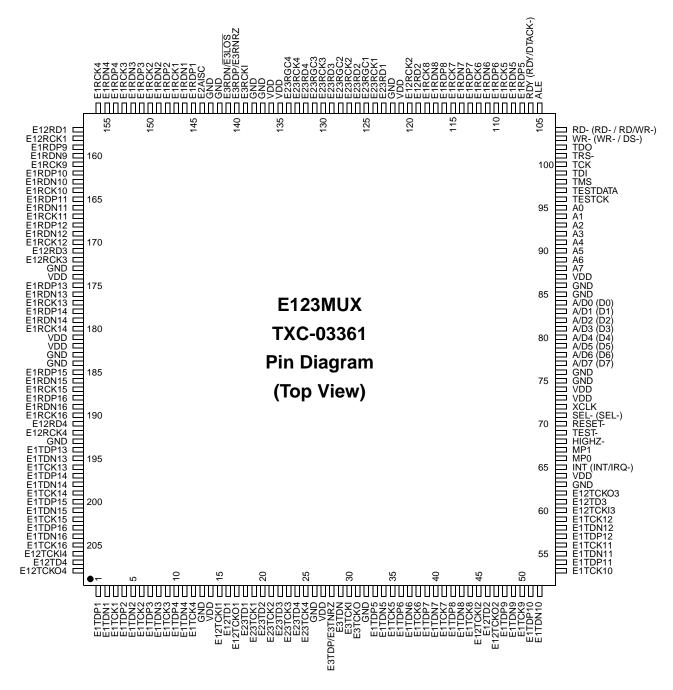

#### **TIMING CHARACTERISTICS**

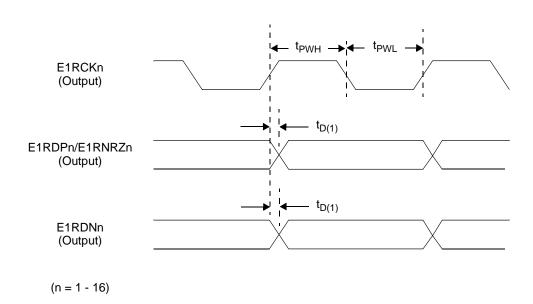

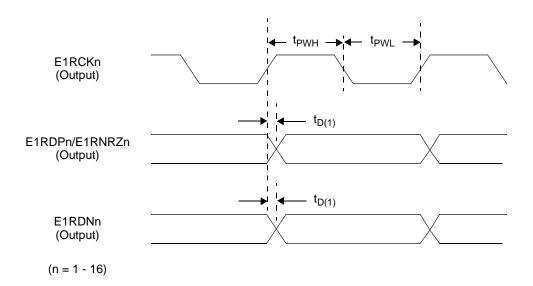

Detailed timing diagrams for the E123MUX are illustrated in Figures 3 through 19, with values of the timing intervals tabulated below each diagram. All output times are measured with a maximum 25 pF load capacitance. Timing parameters are measured at voltage levels of  $(V_{IH} + V_{IL})/2$  for input signals or  $(V_{OH} + V_{OL})/2$  for output signals.

Figure 3. E1 Transmit Input Interface Timing

Note: Shown for control bit TE1CS equal to 0 (Bit 6 in address 04H)

| Parameter                                            | Symbol           | Min                    | Тур | Max | Unit |

|------------------------------------------------------|------------------|------------------------|-----|-----|------|

| E1TCKn clock frequency                               |                  | 2048 ± 50 ppm (Note 1) |     |     | kHz  |

| E1TCKn high time                                     | t <sub>PWH</sub> | 40                     | 50  | 60  | %    |

| E1TCKn low time                                      | t <sub>PWL</sub> | 40                     | 50  | 60  | %    |

| E1TDPn/E1TNRZn and E1TDNn set-up time before E1TCKn↑ | t <sub>SU</sub>  | 10                     |     |     | ns   |

| E1TDPn/E1TNRZn and E1TDNn hold time after E1TCKn↑    | t <sub>H</sub>   | 10                     |     |     | ns   |

Note 1: Meets the G.823 E1 jitter tolerance curve.

E123MUX TXC-03361

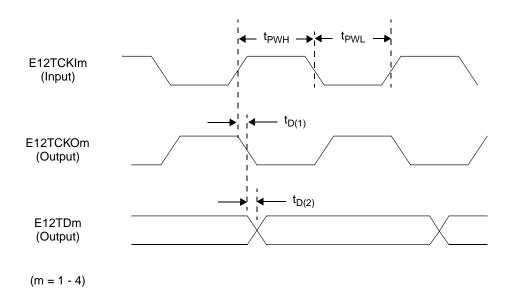

Figure 4. E12 Transmit Output Interface Timing

Note: Shown for control bit T12CSm Parameter equal to 0 (bit 5 in addresses 2AH, 3AH, 4AH, and 5AH, for m = 1-4) and configuration bit E13M equal to 0 (bit 7 address B9H).

| Parameter                                      | Symbol            | Min | Тур | Max | Unit |

|------------------------------------------------|-------------------|-----|-----|-----|------|

| E12TCKIm clock frequency                       |                   |     | kHz |     |      |

| E12TCKIm high time                             | t <sub>PWH</sub>  | 40  | 50  | 60  | %    |

| E12TCKIm low time                              | t <sub>PWL</sub>  | 40  | 50  | 60  | %    |

| E12TCKOm↓ output delay after E12TCKIm↑         | t <sub>D(1)</sub> | 5.0 |     | 93  | ns   |

| E12TDm (NRZ Data) output delay after E12TCKOm↓ | t <sub>D(2)</sub> | 5.0 |     | 10  | ns   |

E123MUX TXC-03361

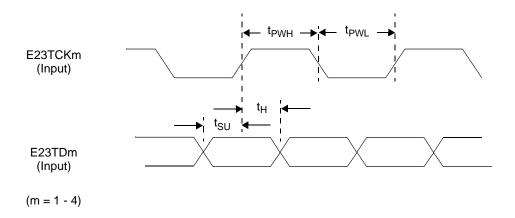

Figure 5. E23 Transmit Input Interface Timing

Note: Shown for control bit T23CSm equal to 0 (bits 7, 5, 3, 1 in address B7H, for m = 4-1)

| Parameter                          | Symbol           | Min | Тур | Max | Unit |

|------------------------------------|------------------|-----|-----|-----|------|

| E23TCKm clock frequency            |                  | 1   | kHz |     |      |

| E23TCKm high time                  | t <sub>PWH</sub> | 40  | 50  | 60  | %    |

| E23TCKm low time                   | t <sub>PWL</sub> | 40  | 50  | 60  | %    |

| E23TDm set-up time before E23TCKm↑ | t <sub>SU</sub>  | 10  |     |     | ns   |

| E23TDm hold time after E23TCKm↑    | t <sub>H</sub>   | 10  |     |     | ns   |

E123MUX TXC-03361

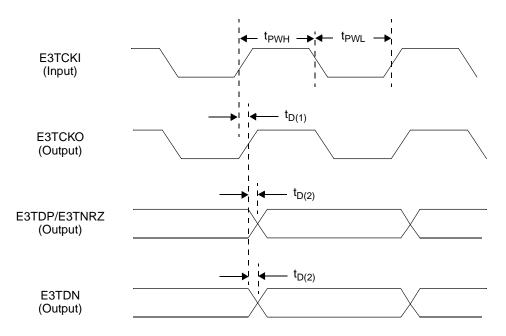

Figure 6. E3 Transmit Output Interface Timing

Note: Shown for control bit TE3CS equal to 1 (Bit 0 in address B0H)

| Parameter                                         | Symbol            | Min | Тур | Max | Unit |

|---------------------------------------------------|-------------------|-----|-----|-----|------|

| E3TCKI clock frequency                            |                   | 3   | kHz |     |      |

| E3TCKI high time                                  | t <sub>PWH</sub>  | 45  | 50  | 55  | %    |

| E3TCKI low time                                   | t <sub>PWL</sub>  | 45  | 50  | 55  | %    |

| E3TCKO↑ output delay after E3TCKI↑                | t <sub>D(1)</sub> | 3.0 |     | 14  | ns   |

| E3TDP/E3TNRZ and E3TDN output delay after E3TCKO↑ | t <sub>D(2)</sub> | 3.0 |     | 8.0 | ns   |

E123MUX TXC-03361

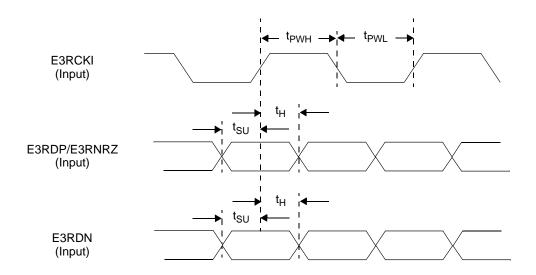

Figure 7. E3 Receive Input Interface Timing

Note: Shown for control bit RE3CS equal to 0 (Bit 1 in address B0H)

| Parameter                                         | Symbol           | Min | Тур | Max | Unit |

|---------------------------------------------------|------------------|-----|-----|-----|------|

| E3RCKI clock frequency                            |                  | 3   | kHz |     |      |

| E3RCKI high time                                  | t <sub>PWH</sub> | 45  | 50  | 55  | %    |

| E3RCKI low time                                   | $t_{PWL}$        | 45  | 50  | 55  | %    |

| E3RDP/E3RNRZ and E3RDN set-up time before E3RCKI↑ | t <sub>SU</sub>  | 7.0 |     |     | ns   |

| E3RDP/E3RNRZ and E3RDN hold time after E3RCKI↑    | t <sub>H</sub>   | 5.0 |     |     | ns   |

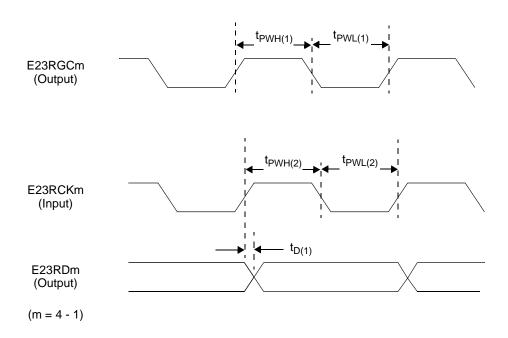

Figure 8. E23 Receive Output Interface Timing

Note: Shown for control bit R23CSm equal to 1 (bits 6, 4, 2, 0 in address B7H, for m = 4 - 1)

| Parameter                              | Symbol              | Min | Тур | Max | Unit |

|----------------------------------------|---------------------|-----|-----|-----|------|

| E23RGCm receive gapped clock frequency |                     |     | kHz |     |      |

| E23RGCm receive gapped clock high time | t <sub>PWH(1)</sub> | 40  | 50  | 60  | %    |

| E23RGCm receive gapped clock low time  | t <sub>PWL(1)</sub> | 40  | 50  | 60  | %    |

| E23RCKm clock frequency                |                     |     | kHz |     |      |

| E23RCKm high time                      | t <sub>PWH(2)</sub> | 40  | 50  | 60  | %    |

| E23RCKm low time                       | t <sub>PWL(2)</sub> | 40  | 50  | 60  | %    |

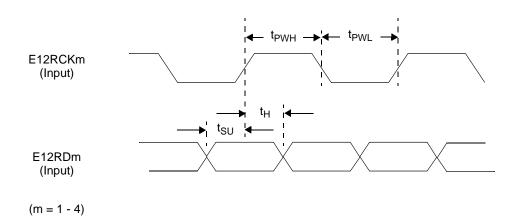

| E23RDm output delay after E23RCKm ↑    | t <sub>D(1)</sub>   | 10  |     |     | ns   |