- Differential ECL Clock Generation

- Divide by 3, 4, 5, or 8 of the Clock

- Divide by 2 and 4 of the Load

- Resets Pipeline Delay of the TLC34058

- 1.235-V Voltage Reference Output

- 5-V Single Power-Supply Operation

- 28-Pin PLCC (FN) Package

- Low Power Consumption . . . 400 mW Max

- Designed to Be Interchangeable With **Brooktree Bt438**

## description

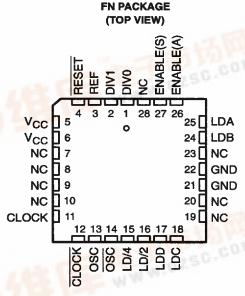

The TVP2002 is a clock driver for the Texas TLC34058 and functionally Instruments equivalent color palettes. It interfaces a 10KH-ECL oscillator operating from a single 5-V supply to the TLC34058, generating the necessary clock and control signals.

NC - No internal connection

The clock output may be divided by 3, 4, 5, or 8 to generate the load signal. The load signal is also divided by 2 and 4 for clocking video timing logic, etc. A second load signal may be synchronously or asynchronously controlled to enable starting and stopping of the VRAM clock.

The TVP2002 also optionally configures the pipeline delay of the TLC34058 to a fixed pipeline delay. An on-chip 1.235-V reference is provided and may be used to provide the reference voltage for the color palette.

### functional block diagram

896672400098206 468

1

### **Terminal Functions**

| TERMINAL            |        | T .                      |                                                                                                                                                                                                                                                                                                                                                                                                                         |

|---------------------|--------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                | NO.    | 1/0                      | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                             |

| CLOCK, CLOCK        | 11, 12 | 0                        | These differential clock outputs connect directly to the CLOCK and CLOCK inputs of the TLC34058. The clock rate is equal to the OSC and OSC rate, and these terminals are capable of driving the TLC34058 directly. The output levels are equivalent to 10KH-ECL logic operating from a single 5-V supply.                                                                                                              |

| DIV0, DIV1          | 1, 2   | (TTL<br>compatible)      | The divide control inputs specify the division factor (3, 4, 5, or 8) for the generation of the LDA and LDB signals as specified in Table 1.                                                                                                                                                                                                                                                                            |

| ENABLE(A)           | 26     | I<br>(TTL<br>compatible) | The asynchronous load-enable control input is used to asynchronously start and stop the LDC and LDD outputs. While ENABLE(A) is low, the LDC and LDD outputs remain in the state they are in when ENABLE(A) goes to a low level. While both ENABLE(A) and ENABLE(S) are low, LDC and LDD are free-running and in phase with the LDA and LDB outputs. Care should be taken to avoid glitches on this asynchronous input. |

| ENABLE(S)           | 27     | (TTL<br>compatible)      | The synchronous load-enable control input is internally synchronized to LDA and is used to synchronously start and stop the LDC and LDD outputs. While ENABLE(S) is low, LDC and LDD are low. While both ENABLE(A) and ENABLE(S) are high, LDC and LDD are free-running and in phase with the LDA and LDB outputs.                                                                                                      |

| GND                 | 21, 22 |                          | Device ground. GND terminals must be connected.                                                                                                                                                                                                                                                                                                                                                                         |

| LDA, LDB            | 25, 24 | O<br>(TTL<br>compatible) | Load outputs LDA and LDB are generated by dividing CLOCK by 3, 4, 5, or 8 as determined by the DIV0 and DIV1 inputs.                                                                                                                                                                                                                                                                                                    |

| LDC, LDD            | 18, 17 | O<br>(TTL<br>compatible) | Load outputs. When both ENABLE inputs are high, these outputs have the same timing as the LDA and LDB outputs.                                                                                                                                                                                                                                                                                                          |

| LD/2                | 16     | O<br>(TTL<br>compatible) | Load output. LD/2 is generated by dividing LDA by two.                                                                                                                                                                                                                                                                                                                                                                  |

| LD/4                | 15     | 0                        | Load output. LD/4 is generated by dividing LDA by four.                                                                                                                                                                                                                                                                                                                                                                 |

| osc, <del>osc</del> | 13, 14 | Ī                        | Differential-ECL oscillator inputs. OSC and OSC are designed to interface to a 10KH-ECL crystal oscillator operating from a single 5-V supply.                                                                                                                                                                                                                                                                          |

| REF                 | 3      | 0                        | Voltage reference output. REF provides a 1.235-V (typical) reference and may be used to drive the REF input of the TLC34058.                                                                                                                                                                                                                                                                                            |

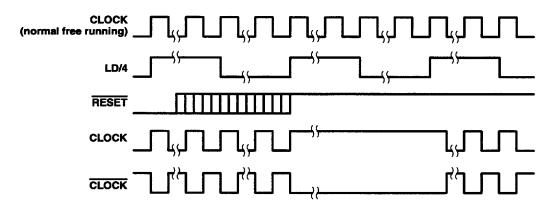

| RESET               | 4      | (TTL<br>compatible)      | Reset control input. Following the first rising edge of LD/4 after the rising edge of RESET, CLOCK and CLOCK are stopped in the high and low states, respectively. At the next rising edge of LD/4, the CLOCK and CLOCK outputs are set to be free running. Care must be taken to avoid glitches on this edge-triggered input.                                                                                          |

| Vcc                 | 5, 6   |                          | Device power. V <sub>CC</sub> terminals must be connected.                                                                                                                                                                                                                                                                                                                                                              |

**Table 1. Selection of Division Factor**

| DIV1 | DIVO | DIVISION | CLOCK CYCLES |          |  |  |

|------|------|----------|--------------|----------|--|--|

|      | DIVO | FACTOR   | LDx LOW      | LDx HIGH |  |  |

| L    | L    | 3        | 1            | 2        |  |  |

| L    | н    | 4        | 2            | 2        |  |  |

| н    | L    | 5        | 2            | 3        |  |  |

| н    | н    | 8        | 4            | 4        |  |  |

# absolute maximum ratings over operating free-air temperature range (unless otherwise noted)†

| Supply voltage, V <sub>CC</sub>                      | 7 V            |

|------------------------------------------------------|----------------|

| Input voltage, V <sub>I</sub>                        |                |

| Operating free-air temperature range, T <sub>A</sub> | 0°C to 70°C    |

| Storage temperature range                            | -65°C to 150°C |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### recommended operating conditions

|                                                                     |                   | MIN                   | NOM  | MAX                   | UNIT |

|---------------------------------------------------------------------|-------------------|-----------------------|------|-----------------------|------|

| Supply voltage, VCC                                                 | 4.75              | 5                     | 5.25 |                       |      |

| High-level input voltage, VIH                                       | TTL               | 2                     |      |                       |      |

| Low-level input voltage, V <sub>IL</sub>                            | ]                 |                       |      | 0.8                   | V    |

| High-level input voltage, VIH                                       | prout             | V <sub>CC</sub> - 1.1 |      | V <sub>CC</sub> - 0.8 |      |

| Low-level input voltage, V <sub>IL</sub>                            | PECL <sup>‡</sup> |                       |      | V <sub>CC</sub> - 1.5 |      |

| High-level output current, IOH                                      | TTL               |                       |      | -2                    |      |

| Low-level output current, IOL                                       | ]''-              |                       |      | 12                    | mA   |

| Output current, IO                                                  | PECL              |                       |      | 30                    |      |

| Input frequency, fOSC                                               |                   | 0                     |      | 135                   | MHz  |

| Pulse duration, RESET low, tw(RL)                                   |                   | 15                    |      |                       |      |

| Setup time, RESET↑ before LD/4↑, t <sub>su(R)</sub>                 |                   | 10                    |      |                       |      |

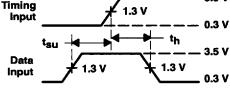

| Setup time, ENABLE(S) before LDA <sup>↑</sup> , t <sub>SU(ES)</sub> | See Figure 1      | 10                    |      |                       |      |

| Hold time, ENABLE(S) after LDA↑, th(ES)                             |                   | 0                     |      |                       | ns   |

| Setup time, ENABLE(A) before LDA↑, t <sub>SU(EA)</sub>              |                   | 10                    |      |                       | ĺ    |

| Hold time, ENABLE(A) after LDA↑, th(EA)                             |                   | 0                     |      |                       | 1    |

| Input duty ratio                                                    |                   | 40%                   | 50%  | 60%                   |      |

| Operating free-air temperature, TA                                  |                   | 0                     |      | 70                    | °C   |

<sup>‡</sup>Pseudo-ECL

# electrical characteristics $V_{CC} = 5 \text{ V}$ , $T_A = 25^{\circ}\text{C}$ (unless otherwise noted)

| PARAMETER                     |                                          |      | TEST CO                                     | MIN                         | TYP                | MAX   | UNIT                  |    |

|-------------------------------|------------------------------------------|------|---------------------------------------------|-----------------------------|--------------------|-------|-----------------------|----|

| ٧ <sub>IK</sub>               | Input clamp voltage                      |      | V <sub>CC</sub> = 4.75 V,                   | l <sub>l</sub> = -18 mA     |                    |       | -1.2                  |    |

| Vон                           | High-level output voltage                | TTL  | $V_{CC} = 5 V \pm 5\%,$                     | l <sub>OH</sub> = -2 mA     | 2.4                |       |                       |    |

| VOL                           | Low-level output voltage                 | 7    | V <sub>CC</sub> = 4.75 V,                   | I <sub>OL</sub> = 12 mA     |                    | 0.3   | 0.5                   | V  |

| VOH High-level output voltage |                                          | PECL |                                             |                             | V <sub>CC</sub> -1 |       | V <sub>CC</sub> - 0.8 |    |

| VOL                           | Low-level output voltage                 | TECL | Connected V <sub>CC</sub> -2 V through 50 Ω |                             | V <sub>CC</sub> -2 |       | V <sub>CC</sub> - 1.6 |    |

| Ŋ                             | Input current                            |      | V <sub>CC</sub> = 5.25 V,                   | V <sub>I</sub> = 7 V        |                    |       | 0.1                   | mA |

| ΊΗ                            | High-level input current                 | ]TTL | V <sub>CC</sub> = 5.25 V,                   | V <sub>I(TTL)</sub> = 2.7 V |                    |       | 20                    | μΑ |

| I <sub>I</sub> L              | Low-level input current                  | 1    | V <sub>CC</sub> = 5.25 V,                   | V <sub>I(TTL)</sub> = 0.4 V |                    |       | -0.2                  | mA |

| ΊΗ                            | I <sub>IH</sub> High-level input current |      | VI(PECL) = 4 V                              | I(PECL) = 4 V               |                    |       | 15                    |    |

| I <sub>I</sub> ը              |                                          |      | V <sub>I(PECL)</sub> = 0.4 V                |                             |                    |       | 15                    | μΑ |

| los                           | Short-circuit output current             | TTL  | V <sub>CC</sub> = 5.25 V,                   | V <sub>O</sub> = 0 V        | -40                | -65   | -100                  | mA |

| V <sub>ref</sub>              | Reference voltage                        |      | I <sub>ref</sub> = -100 μA                  |                             | 1.2                | 1.235 | 1.26                  | ٧  |

| ICC                           | Supply current (see Note 1)              |      |                                             |                             |                    | 60    | 80                    | mA |

NOTE 1: Does not include output part

# TVP2002 CLOCK DRIVER

SLAS083 - JANUARY 1994

# switching characteristics, $V_{CC} = 5 \text{ V}$ , $T_A = 25^{\circ}\text{C}$ (unless otherwise noted)

|                 | PARAMETER                                | TEST CONDITIONS | MIN<br>135 | ТҮР | MAX | UNIT<br>MHz |

|-----------------|------------------------------------------|-----------------|------------|-----|-----|-------------|

| fclock(max)     | Maximum clock frequency                  |                 |            |     |     |             |

| tpd(OH-LDALH)   | Propagation delay time, OSC high to LDA↑ | See Figure 1    |            | 9   | 15  |             |

|                 |                                          | LDA to LDB      | -2         | 0   | 2   |             |

|                 |                                          | LDA to LDC      | -1         | 1.5 | 4   |             |

| t <sub>sk</sub> | Skew time                                | LDA to LD/2     | 0          | 1.5 | 5   | ns          |

|                 |                                          | LDA to LD/4     | 0          | 2   | 6   |             |

|                 |                                          | LDC to LDD      | -2         | 0   | 2   |             |

# PARAMETER MEASUREMENT INFORMATION OSC | total content of the con

Figure 1. Timing Diagram

### PARAMETER MEASUREMENT INFORMATION

NOTE A: CL includes fixture capacitance.

Figure 2. TTL Output Load Circuit

Figure 3. PECL Output Load Circuit

Figure 4. Setup Time and Hold Time

### PRINCIPLES OF OPERATION

The TVP2002 is designed to interface to a 10KH-ECL crystal oscillator and generate the clock signals required by the TLC34058. The OSC and OSC inputs are designed to interface to a 10KH-ECL oscillator operating from a single 5-V power supply.

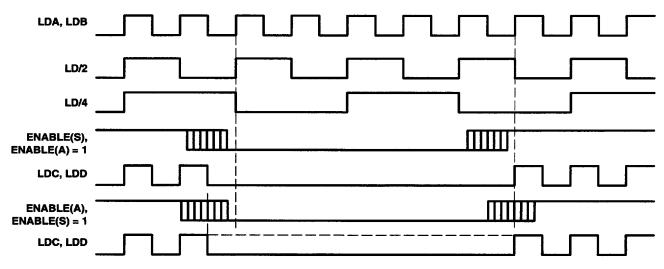

The CLOCK and CLOCK outputs are designed to interface directly to the CLOCK and CLOCK inputs of the TLC34058. The output levels are compatible with 10KH-ECL logic operating from a single 5-V power supply. DIV0 and DIV1 are used to specify whether the pixel clock is to be divided by 3, 4, 5, or 8 to generate the LDA and LDB signals. LDA is also divided by 2 and 4 to generate the LD/2 and LD/4 signals, respectively.

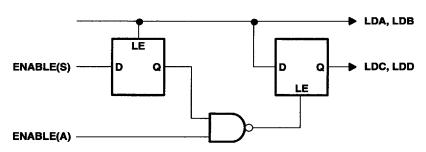

ENABLE(S) is internally synchronized to LDA and may be used to synchronously start and stop the LDC and LDD outputs. When ENABLE(S) is low, LDC and LDD are low. ENABLE(A) is used to asynchronously start and stop the LDC and LDD outputs. When ENABLE(A) is low, the LDC and LDD outputs remain in the state they are when the ENABLE(A) input goes low.

Both ENABLE(A) and ENABLE(S) should not be low simultaneously. If this occurs, synchronous control of LDC and LDD, via ENABLE(S), is not ensured.

When both ENABLE(S) and ENABLE(A) are high, LDC and LDD are free running and in phase with LDA and LDB. This architecture allows the shift registers of the VRAMs to be optionally nonclocked during the retrace intervals. Figure 5 illustrates the ENABLE implementation with the TVP2002, while Figure 6 shows the load output timing.

RESET is designed to enable the TVP2002 to set the pipeline delay of the TLC34058 to a specified number of clock cycles (the exact number is dependent on the TLC34058). Following the first rising edge of LD/4 after the rising edge of RESET, the CLOCK and CLOCK outputs are stopped in the high and low states, respectively. At the next rising edge of LD4, the CLOCK and CLOCK outputs are restarted. Figure 7 shows the operation of the RESET input. The TVP2002 also generates a 1.235-V (typical) reference that may be used to drive the REF input of the TLC34058.

### **PRINCIPLES OF OPERATION**

Figure 5. ENABLE Control

Figure 6. Load Output Timing

Figure 7. RESET Timing

### PRINCIPLES OF OPERATION

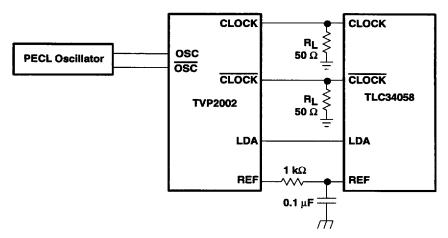

### interfacing to the TLC34058 color palette

Figure 8 illustrates interfacing the TVP2002 to the TLC34058 when using a PECL oscillator. The TVP2002 should be located as close as possible to the TLC34058. The termination resistors for the CLOCK and CLOCK lines should be located as close as possible to the TLC34058.

The TVP2002 may drive the CLOCK and CLOCK inputs of the TLC34058 if they are located as close as possible to each other. Due to the inability to ensure proper synchronization between TVP2002s, multiple devices should not be used in applications where multiple color palettes drive the same monitor.

A 1-k $\Omega$  (typical) resistor must be used to isolate the REF output of the TVP2002 from the REF input of the TLC34058. This prevents noise from the TVP2002 voltage reference from being coupled onto the TLC34058 REF terminal. The REF input of the color palette must still have a decoupling capacitor connected to V<sub>CC</sub> as specified in the TLC34058 data sheet.

Figure 8. Interfacing the TVP2002 to a PECL Oscillator

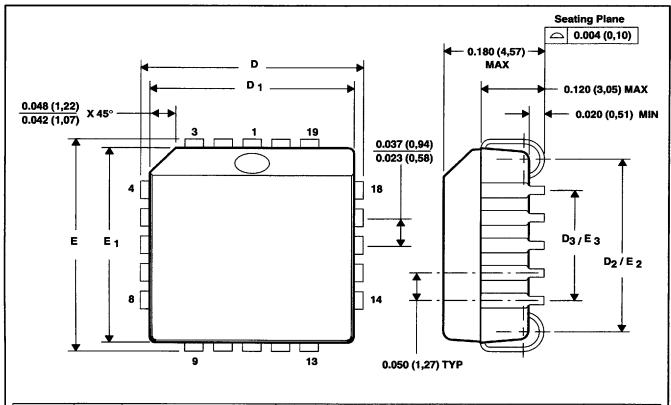

### **MECHANICAL DATA**

# FN/S-PQCC-J\*\* 20-PIN SHOWN

### **PLASTIC J-LEADED CHIP CARRIER**

| JEDEC<br>OUTLINE | NO. OF | D/E           |               | D <sub>1</sub> / E <sub>1</sub> |               | D <sub>2</sub> / | D <sub>3</sub> / E <sub>3</sub> |               |

|------------------|--------|---------------|---------------|---------------------------------|---------------|------------------|---------------------------------|---------------|

|                  | PINS** | MIN           | MAX           | MIN                             | MAX           | MIN              | MAX                             | ТҮР           |

| 1O-047AA         | 20     | 0.385 (9,78)  | 0.395 (10,03) | 0.350 (8,89)                    | 0.356 (9,04)  | 0.290 (7,34)     | 0.330 (8,38)                    | 0.200 (5,08)  |

| 1O-047AB         | 28     | 0.485 (12,32) | 0.495 (12,57) | 0.450 (11,43)                   | 0.456 (11,58) | 0.390 (9,91)     | 0.430 (10,92)                   | 0.300 (7,62)  |

| 1O-047AC         | 44     | 0.685 (17,40) | 0.695 (17,65) | 0.650 (16,51)                   | 0.656 (16,66) | 0.590 (14,99)    | 0.630 (16,00)                   | 0.500 (12,70) |

| 10-047AD         | 52     | 0.785 (19,94) | 0.795 (20,19) | 0.750 (19,05)                   | 0.756 (19,20) | 0.690 (17,53)    | 0.730 (18,54)                   | 0.600 (15,24) |

| 10-047AE         | 68     | 0.985 (25,02) | 0.995 (25,27) | 0.950 (24,13)                   | 0.956 (24,28) | 0.890 (22,61)    | 0.930 (23,62)                   | 0.800 (20,32) |

| 10-047AF         | 84     | 1.185 (30,10) | 1.195 (30,35) | 1.150 (29,21)                   | 1.158 (29,41) | 1.090 (27,69)    | 1.130 (28,70)                   | 1.000 (25,40) |

NOTES: A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. Falls within JEDEC MO-047.