S E M I C O N D U C T O R . I N C .

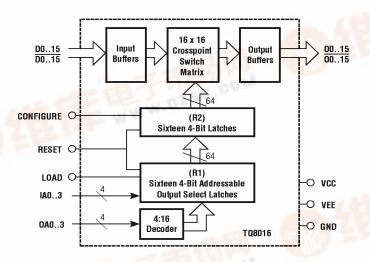

The TQ8016 is a 16 x 16 differential digital crosspoint switch capable of handling 1.3 Gbit/s data rate. The high data rate and exceptional signal fidelity is made possible with TriQuint's fully differential Source-Coupled FET Logic (SCFL) standard cells. The symmetrical switching characteristic inherent in differential logic results in low signal skew and crosstalk for maximum signal fidelity.

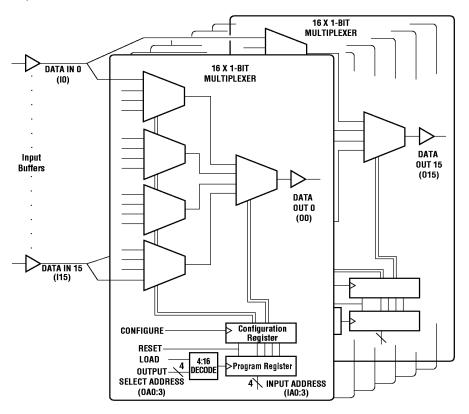

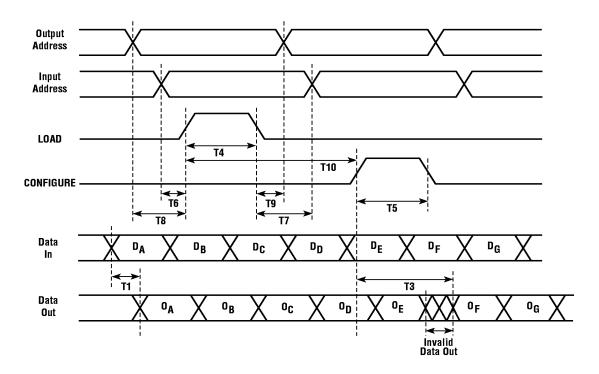

The user can independently configure any switch output to any input, including an input chosen by another output. To configure the switch, the 4-bit output address (OAO..3) is decoded to enable the loading of the 4-bit input selection data (IAO..3) on the rising edge of the LOAD signal. The process is repeated until all desired connections are programmed. By bringing the CONFIGURE signal high, the contents of the Output Select Latches are transferred in parallel to a second row of 4-bit latches (R2), causing the switch reconfiguration.

This double row architecture minimizes the time to completely reconfigure the switch since a new set of addresses can be loaded to the Output Select Latches (R1) while the switch is active (transmitting). At the time of reconfiguration, no data drop-out occurs for any output whose input connection does not change.

For applications which do not require synchronous configuration of the switch, the LOAD and CONFIGURE inputs may be tied together.

# TQ8016

# 1.3 Gigabit/sec 16x16 Digital ECL Crosspoint Switch

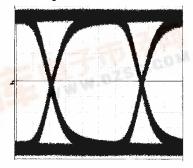

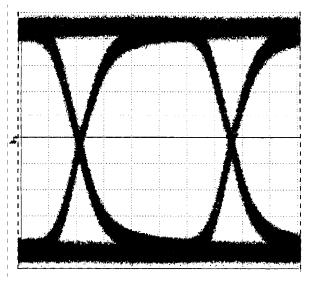

Typical output waveform with all channels driven

#### **Features**

- >1.3 Gigabit/sec data rate

- Non-blocking architecture

- ±200 ps delay match (one input to all outputs)

- ECL-level data inputs/outputs; CMOS-level control inputs

- · Low crosstalk

- Fully differential data path

- Double row of output select latches minimizes reconfiguration time

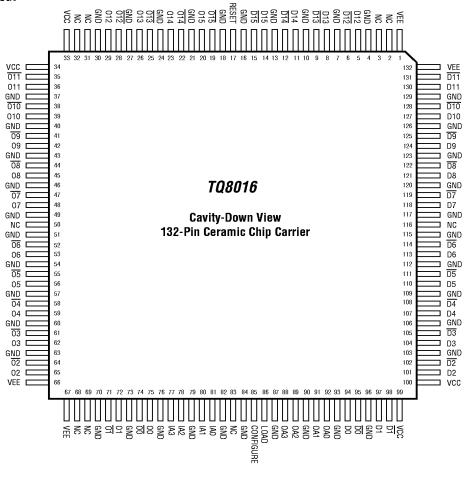

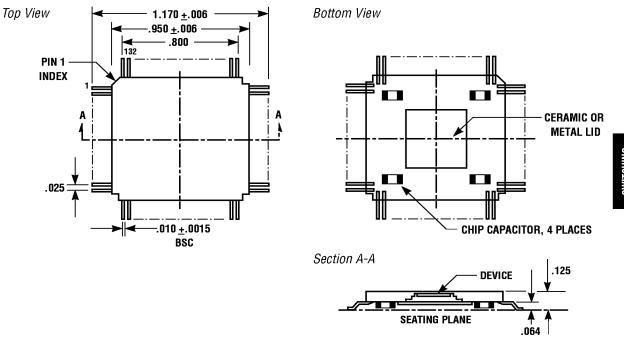

- Available in 132-pin leaded chip carrier

Figure 1. TQ8016 Architecture

Table 1. Pin Descriptions

| Pin Name  | Levels | Description               |

|-----------|--------|---------------------------|

| D0-D15    | ECL    | Differential Data Inputs  |

| D0-D15    | ECL    | Differential Data Inputs  |

| D0-D15    | ECL    | Differential Data Inputs  |

| 00–015    | ECL    | Differential Data Outputs |

| 00–015    | ECL    | Differential Data Outputs |

| IA0-IA3   | CMOS   | Input Address             |

| OA0-OA3   | CMOS   | Output Address            |

| CONFIGURE | CMOS   | Switch Reconfiguration    |

Figure 2. Pinout

Table 1. Pin Descriptions (continued)

| Pin Name | Levels | Description                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

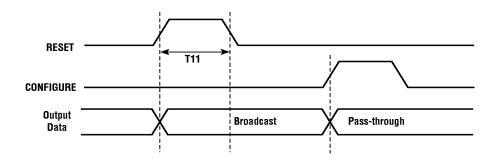

| RESET    | cmos   | Configures the switch to <i>Broadcast</i> or <i>Pass-Through</i> modes, overwriting existing configurations. <b>Broadcast mode:</b> All output ports are connected to data input port 0. This mode is selected by applying a RESET "high" pulse with CONFIGURE held "low." <b>Pass-through mode:</b> 10 is connected to 00, 11 to 01, and so on. This mode is selected by applying a RESET "high" pulse with CONFIGURE held "high." |

| LOAD     | CMOS   | Loads Input Address                                                                                                                                                                                                                                                                                                                                                                                                                 |

| GND      | 0 V.   | Ground Reference                                                                                                                                                                                                                                                                                                                                                                                                                    |

| VEE      | −5 V   | Power Supply                                                                                                                                                                                                                                                                                                                                                                                                                        |

| VCC      | +5 V   | Power Supply                                                                                                                                                                                                                                                                                                                                                                                                                        |

### TQ8016

Table 2. Absolute Maximum Ratings<sup>4</sup>

| Symbol            | Parameter                                                               | Absolute Max. Rating             | Notes |

|-------------------|-------------------------------------------------------------------------|----------------------------------|-------|

| T <sub>STOR</sub> | Storage Temperature                                                     | −65° C to +150° C                |       |

| TJ                | Junction Temperature                                                    | −55° C to +150° C                |       |

| T <sub>C</sub>    | Case Temperature Under Bias                                             | –55° C to +125° C                | 1     |

| V <sub>CC</sub>   | Supply Voltage                                                          | 0 V to +7 V                      | 2     |

| V <sub>EE</sub>   | Supply Voltage                                                          | –7 V to 0 V                      | 2     |

| V <sub>TT</sub>   | Load Termination Supply Voltage                                         | V <sub>EE</sub> to 0 V           | 3     |

| V <sub>IN</sub>   | Voltage Applied to Any ECL Input; Continuous                            | V <sub>EE</sub> −0.5 V to +0.5 V |       |

| I <sub>IN</sub>   | Current Into Any ECL Input; Continuous                                  | –1.0 mA to +1.0 mA               |       |

| V <sub>IN</sub>   | Voltage Applied to Any TTL/CMOS Input; Continuous                       | –0.5 V to V <sub>CC</sub> +0.5 V |       |

| I <sub>IN</sub>   | Current Into Any TTL/CMOS Input; Continuous                             | -1.0 mA to +1.0 mA               |       |

| V <sub>OUT</sub>  | Voltage Applied to Any ECL Output                                       | V <sub>EE</sub> −0.5 V to +0.5 V | 3     |

| I <sub>out</sub>  | Current From Any ECL Output; Continuous                                 | –40 mA                           |       |

| P <sub>D</sub>    | Power Dissipation per Output $P_{OUT} = (GND - V_{OUT}) \times I_{OUT}$ | 50 mW                            |       |

Notes: 1.  $T_C$  is measured at case top.

- 2. All voltages specified with respect to GND, defined as OV.

- 3. Subject to I<sub>OUT</sub> and power dissipation limitations.

- 4. Absolute maximum ratings, as detailed in this table, are the ratings beyond which the device's performance may be impaired and/or permanent damage to the device may occur. Functionality and/or adherence to electrical specifications is not implied when the device is subjected to conditions that exceed, singularly or in combination, the operating range specified in the Recommended Operating Conditions table, below.

Table 3. Recommended Operating Conditions<sup>3</sup>

| Symbol              | Parameter                          | Min. | Тур. | Max. | Units | Notes |

|---------------------|------------------------------------|------|------|------|-------|-------|

| T <sub>C</sub>      | Case Operating Temperature         | 0    | 25   | 85   | °C    | 1     |

| GND                 | Ground Reference Voltage           |      | 0    |      | V     |       |

| V <sub>CC</sub>     | Supply Voltage                     | 4.5  |      | 5.5  | V     |       |

| V <sub>EE</sub>     | Supply Voltage                     | -5.5 |      | -4.5 | V     |       |

| $\overline{V_{TT}}$ | Load Termination Supply Voltage    |      | -2.0 |      | V     | 2     |

| R <sub>LOAD</sub>   | Output Termination Load Resistance |      | 50   |      | Ω     | 2     |

Notes: 1.  $T_C$  measured at case top. Use of adequate heatsink is required.

- 2. The  $V_{TT}$  and  $R_{LOAD}$  combination is subject to maximum output current and power restrictions.

- 3. Functionality and/or adherence to electrical specifications is not implied whenthe device is subjected to conditions that exceed, singularly or in combination, the operating ranges specified.

**Table 4. DC Characteristics**<sup>1</sup>  $T_C = 0$  °C to 85 °C,  $V_{CC} = 4.5$  V to 5.5 V,  $V_{EE} = -5.5$  V to -4.5 V, GND = 0 V, unless otherwise indicated.

| Symbol            | Parameter                            | Min             | Тур | Max             | Units | Test Cond.                        | Notes |

|-------------------|--------------------------------------|-----------------|-----|-----------------|-------|-----------------------------------|-------|

| V <sub>IH</sub>   | ECL Input Voltage High               | -1100           |     | -500            | mV    |                                   |       |

| V <sub>IL</sub>   | ECL Input Voltage Low                | V <sub>TT</sub> |     | -1500           | mV    |                                   |       |

| I <sub>IH</sub>   | ECL Input Current High               |                 |     | +30             | uA    | V <sub>IH</sub> = 0.7 V           |       |

| I <sub>IL</sub>   | ECL Input Current Low                | -30             |     |                 | uA    | V <sub>IL</sub> = -2.0 V          |       |

| V <sub>ICM</sub>  | ECL Input Common Mode Voltage        | -1500           |     | -1100           | mV    |                                   |       |

| V <sub>IDIF</sub> | ECL Input Differential Voltage (P-P) | 400             |     | 1200            | mV    |                                   |       |

| V <sub>IH</sub>   | CMOS Input Voltage High              | 3.5             |     | V <sub>CC</sub> | V     |                                   |       |

| V <sub>IL</sub>   | CMOS Input Voltage Low               | 0               |     | 1.5             | V     |                                   |       |

| I <sub>IH</sub>   | CMOS Input Current High              |                 |     | +100            | uA    | V <sub>IH</sub> = V <sub>CC</sub> |       |

| I <sub>IL</sub>   | CMOS Input Current Low               | -100            |     |                 | uA    | V <sub>IL</sub> = 0 V             |       |

| V <sub>OCM</sub>  | ECL Output Common Mode               | -1500           |     | -1100           | mV    |                                   |       |

| V <sub>ODIF</sub> | ECL Output Differential Voltage      | 600             |     |                 | mV    |                                   |       |

| V <sub>OH</sub>   | ECL Output Voltage High              | -1000           |     | -600            | mV    |                                   |       |

| V <sub>OL</sub>   | ECL Output Voltage Low               | V <sub>TT</sub> |     | -1600           | mV    |                                   |       |

| I <sub>OH</sub>   | ECL Output Current High              | 20              | 23  | 27              | mA    |                                   |       |

| I <sub>OL</sub>   | ECL Output Current Low               | 0               | 5   | 8               | mA    |                                   |       |

| I <sub>CC</sub>   | Power Supply Current                 |                 | 15  | 20              | mA    |                                   | 2     |

| I <sub>EE</sub>   | Power Supply Current                 |                 | 730 | 950             | mA    |                                   | 2     |

Notes: 1. Test conditions unless otherwise indicated:  $V_{TT} = -2.0 \text{ V}$ ,  $R_{LOAD} = 50 \Omega$  to  $V_{TT}$ .

Table 5. AC Characteristics<sup>1</sup> – Within recommended operating conditions, unless otherwise indicated.

| Symbol          | Parameter                       | Min | Тур  | Max  | Units    | Notes |

|-----------------|---------------------------------|-----|------|------|----------|-------|

|                 | Maximum Data Rate/Port          |     |      | 1.3  | Gb/s     | 1,2   |

|                 | Jitter                          |     |      | 150  | ps pk–pk | 1     |

| T <sub>1</sub>  | Channel Propagation Delay       |     | 1200 | 2000 | ps       |       |

| T <sub>2</sub>  | Ch-to-Ch Propagation Delay Skew |     | 400  | 500  | ps       |       |

| T <sub>3</sub>  | CONFIG to Data Out (Oi) Delay   |     |      | 5    | ns       |       |

| T <sub>4</sub>  | LOAD Pulse Width                | 7   |      |      | ns       |       |

| T <sub>5</sub>  | CONFIG Pulse Width              | 7   |      |      | ns       |       |

| T <sub>6</sub>  | IAi to LOAD High Setup Time     | 0   |      |      | ns       |       |

| T <sub>7</sub>  | LOAD to IAi Low Hold Time       | 3   |      |      | ns       |       |

| T <sub>8</sub>  | OAi to LOAD High Setup Time     | 0   |      |      | ns       |       |

| T <sub>9</sub>  | LOAD to OAi Low Hold Time       | 3   |      |      | ns       |       |

| T <sub>10</sub> | Load ↑ to CONFIG ↑              | 0   |      |      | ns       |       |

| T <sub>11</sub> | RESET Pulse Width               | 10  |      |      | ns       |       |

| $T_{R,F}$       | Output Rise or Fall Time        |     | 250  | 400  | ps       | 3     |

Notes: 1. Test conditions:  $V_{TT} = -2.0 \text{ V}$ ,  $R_{LOAD} = 50 \Omega$  to  $V_{TT}$ ; ECL inputs:  $V_{IH} = -1.1 \text{ V}$ ;  $V_{IL} = -1.5 \text{ V}$ ; CMOS inputs:  $V_{IH} = 3.5 \text{ V}$ ,  $V_{IL} = 1.5 \text{ V}$ ; ECL outputs:  $V_{OH} \ge -1.0 \text{ V}$ ,  $V_{OL} \le -1.6 \text{ V}$ ; ECL inputs rise and fall times  $\le 1 \text{ ns}$ ; CMOS inputs rise and fall times  $\le 20 \text{ ns}$ . A bit error rate of 1E - 13 BER or better for  $2^{23} - 1$  PRBS pattern, jitter and rise/fall times are guaranteed through characterization.

<sup>3.</sup> Rise and fall times are measured at the 20% and 80% points of the transition from  $V_{OL}$  max to  $V_{OL}$  min.

<sup>2.</sup> Positive current is defined as flowing into the device and negative current as flowing out of the device.  $I_{CC}$  typically flows into the device and  $I_{EE}$  flows out of the device.

<sup>2. 1.2</sup> Gb/s Non-Return-Zero (NRZ) data equivalent to 600 MHz clock signal.

Figure 3. Timing Diagram — Switch Configuration

Figure 4. Timing Diagram — Reset

- Notes: 1. LOAD input must remain LOW to insure correct programming of the switch

2. "Broadcast" is defined as data input 0 to all data outputs (0..15).

3. "Pass-through" is defined as data input 0 to data output 0, data input 1 to data output 1, etc.

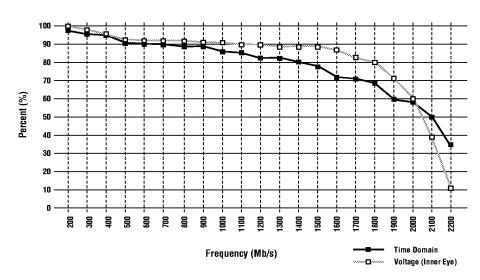

Figure 5. AC Performance Measurements

(Percent Recoverable "Eye" vs. Frequency 16 x 16)

## Typical Error-Free Area

The graph in Figure 5 shows the typical error-free area of a 2<sup>23</sup> – 1 Pseudo-Random Bit Stream (PRBS) "eye" pattern. Data is provided for both time and voltage domains of the differential DINO to DOUTO data path for various data rates. An interference pattern was applied to all other inputs in parallel to induce worst-case cross talk.

For the time domain, Peak-to-Peak Jitter was measured at the eye crossing.

An error-free percentage value was computed using the following formula:

(Data\_Period - PPJitter) x 100 / Data\_Period

Voltage values are referenced to an initial inner eye measurement at 400 MBs. Subsequent percentage values were computed using the following formula:

$V_{INNER} \times 100 / V_{INNER} @ 400 MBs$

Table 6. Typical Differential Waveform Characteristics  $(OUT - \overline{OUT})$

| Frequency             | 1200 Mb/s |

|-----------------------|-----------|

| Fall Time (20% – 80%) | 195 ps    |

| Rise Time (20% – 80%) | 1200 Mb/s |

| Jitter (peak-to-peak) | 40 ps     |

| Time/division         | 125 ps    |

| Volts/division        | 250 mV    |

Figure 5. 1200 Mb/s Data "Eye" Pattern

Time/Div: 150 ps

Figure 6. Mechanical Dimensions

### **Ordering Information**

# **TQ8016-M** 1.3 Gb/s 16x16 ECL Crosspoint Switch

### Additional Information

For latest specifications, additional product information, worldwide sales and distribution locations, and information about TriQuint:

Web: www.triquint.com Tel: (503) 615-9000 Email: sales@tqs.com Fax: (503) 615-8900

For technical questions and additional information on specific applications:

Email: applications@tqs.com

The information provided herein is believed to be reliable; TriQuint assumes no liability for inaccuracies or omissions. TriQuint assumes no responsibility for the use of this information, and all such information shall be entirely at the user's own risk. Prices and specifications are subject to change without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. TriQuint does not authorize or warrant any TriQuint product for use in life-support devices and/or systems.

Copyright © 1997 TriQuint Semiconductor, Inc. All rights reserved.

Revision 1.1.A November 1997