SPWS026 - OCTOBER 1996

- Single-Chip Ethernet™ Controller for the Peripheral Component Interconnect (PCI) **Local Bus**

- 32-Bit PCI<sup>†</sup> Glueless Host Interface

- Compliant With PCI Local-Bus Specification (Revision 2.1)

- 0-MHz to 33-MHz Operation

- 3-V or 5-V I/O Operation

- Adaptive Performance Optimization™ (APO) by Texas Instruments (TI™) for Highest Available PCI Bandwidth

- **High-Performance Bus Master Architecture With Byte-Aligning Direct** Memory Access (DMA) Controller for Low Host CPU and Bus Utilization

- Plug-and-Play Compatible

- Supports 32-Bit Data Streaming on PCI Bus

- Time-Division Multiplexed Static Random-Access Memory (SRAM)

- 2-Gbps Internal Bandwidth

- **Driver Compatible With All Previous** ThunderLAN™ Components

- Switched-Ethernet Compatible

- Full-Duplex Compatible

- Independent Transmit and Receive Channels

- Two Transmit Channels for Demand Priority

- Supports Multiple Protocols With a Single **Driver Suite Optimized Shared Interrupts**

- No On-Board Memory Required

- Auto-Negotiation (N-Way) Compatible

- Multimedia-Ready Architecture

- Supports the Card-Bus Card Information Structure (CIS) Pointer Register

- Early-Receive-Interrupt Count Register

- **EEPROM Interface Supports Jumperless Design and Autoconfiguration**

- **Hardware Statistics Registers for** Management-Information Base (MIB)

- Desktop Management Task Force (DMTF) Compatible

- Integrated 10 Base-T, and 10 Base-5 Attachment Unit Interface (AUI) Physical Layer Interface

- Single-Chip IEEE 802.3 and Blue Book Ethernet-Compliant Solution

- **DSP-Based Digital Phase-Locked Loop**

- **Smart Squeich Allows for Transparent Link Testing**

- Transmission Waveshaping

- Autopolarity (Reverse Polarity) Correction)

- External/Internal Loopback Including Twisted Pair and AUI

- 10 Base-2 Supported Through AUI

- Media-Independent Interface (MII) for Connecting 100-Mbps External **Transceivers**

- Compliant MII for IEEE 802.3u Transceivers

- Supports 100 Base-TX, 100 Base-T4, 100 Base-FX

- Super Set Supports IEEE 802.12 **Transceivers**

- Supports Ethernet and Token-Ring Framing Formats for 100VG-AnyLAN

- Link-Pulse Detection for Determining Wire Rate

- Low-Power CMOS Technology Green PC Compatible

- Magic Packet™ Remote Wake-Up Scheme

- Microsoft™ Advanced Power Management

- PCI Specification Compatible for Low Power/Sleep Mode

- **Advanced Configuration and Power** Interface (ACPI)

- IEEE Standard 1149.1‡ Test-Access Port (JTAG)

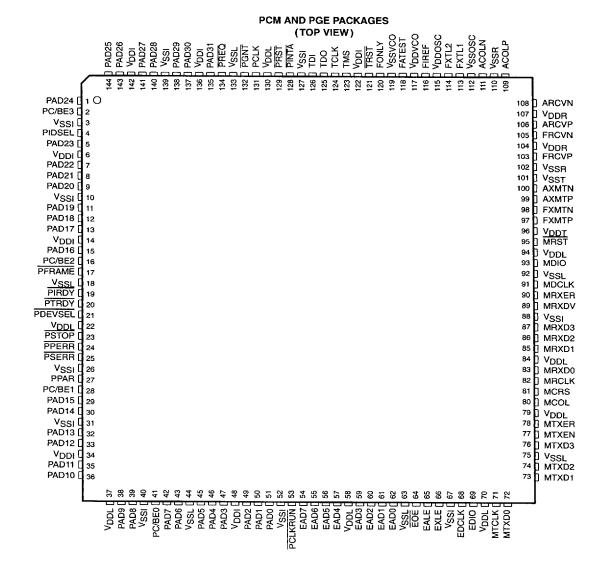

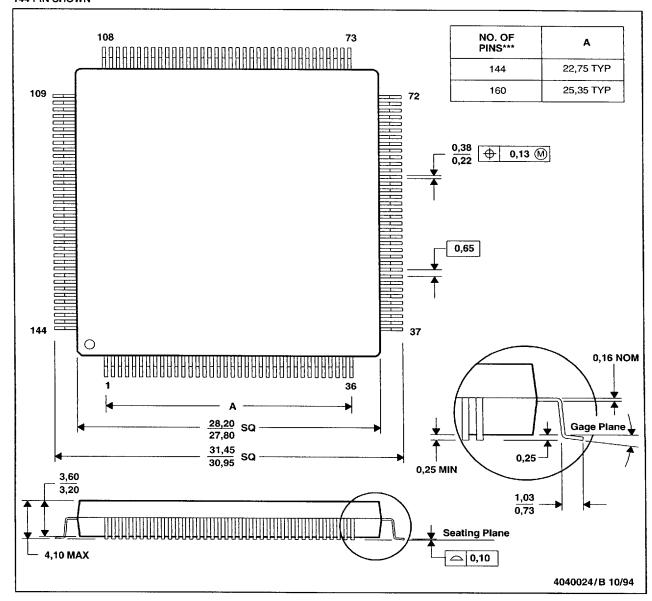

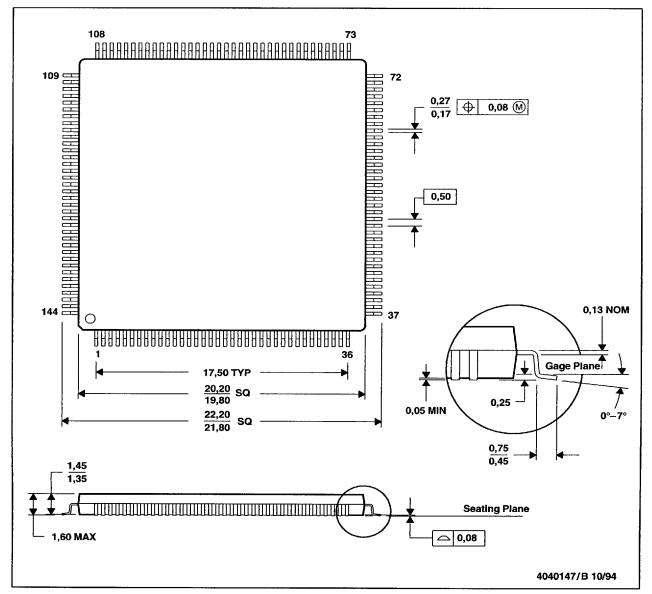

- 144-Pin Thin Quad Flat Packages and Quad Flat Packages (PCM and PGE)

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

† The PCI Local-Bus Specification, Revision 2.1 should be used as a reference with this document. FIEEE Standard 1149.1-1990, IEEE Standard Test-Access Port and Boundary-Scan Architecture

Ethernet is a registered trademark of Xerox Corporation.

Magic Packet is a trademark of Advanced Micro Devices (AMD).

Microsoft is a registered trademark of Microsoft Corp.

ThunderLAN, Adaptive Performance Optimization, and TI are trademarks of Texas Instruments Incorporated.

ADVANCE INFORMATION concerns new products in the sampling or preproduction phase of development. Characteristic data and other specifications are subject to change without notice.

Copyright © 1996, Texas Instruments Incorporated

### ThunderLAN<sup>TM</sup> TNETE100PM PCI ETHERNET<sup>TM</sup> CONTROLLER WITH POWER MANAGEMENT SINGLE-CHIP 10 BASE-T WITH MII FOR 100 BASE-T/100VG-AnyLAN

SPWS026 – OCTOBER 1996

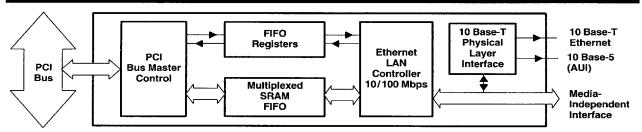

Figure 1. ThunderLAN Architecture

#### description

ThunderLAN is a high-speed networking architecture that provides a complete PCI-to-10 Base-T/AUI Ethernet solution with the flexibility to handle 100-Mbps Ethernet protocols as networking demands grow.

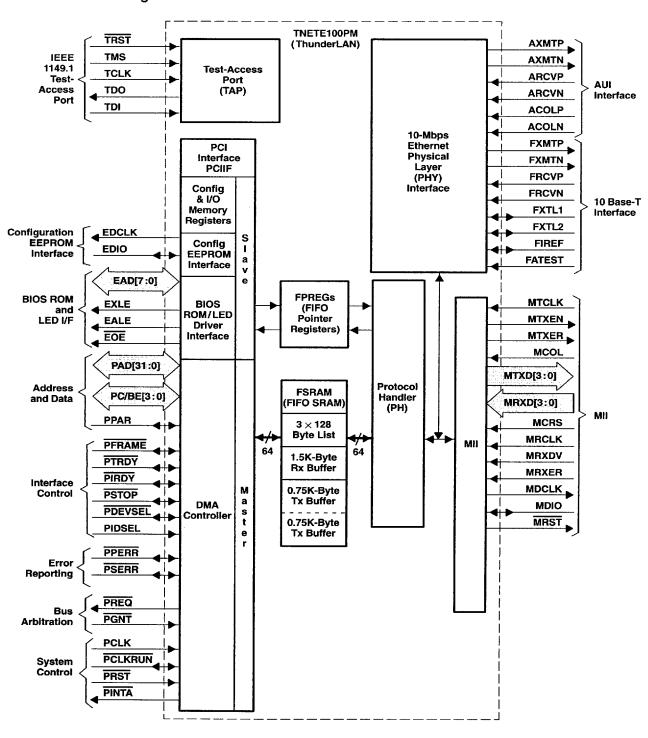

The TNETE100PM, an implementation of the ThunderLAN architecture (see Figure 1), is an intelligent-protocol network interface. The ThunderLAN SRAM FIFO-based architecture eliminates the need for external memory and offers a single-chip glueless PCI-to-10 Base-T/AUI (IEEE 802.3) solution with an on-board physical layer interface. Modular support for 100 Base-T (IEEE 802.3u) and 100VG-AnyLAN (IEEE 802.12) is provided by a superset of the industry-standard media-independent interface (MII). ThunderLAN uses a single driver suite to support multiple networking protocols.

The glueless PCI interface supports 32-bit streaming, operates at speeds up to 33 MHz, and is capable of internal data-transfer rates up to 2 Gbps, taking full advantage of all available PCI bandwidth. The TNETE100PM offers jumperless autoconfiguration using PCI configuration read/write cycles. Customizable configuration registers, which can be autoloaded from an external serial EEPROM, allow designers of TNETE100PM-based systems to give their systems a unique identification code. The TNETE100PM PCI interface, developed in conjunction with other leaders in the semiconductor and computer industries, has been tested vigorously on multiple platforms to ensure compatibility across a wide array of available PCI products. In addition, the ThunderLAN drivers and ThunderLAN architecture use Tl's patented Adaptive Performance Optimization (APO) technology to adjust critical parameters for minimum latency dynamically, minimum host CPU utilization, and maximum system performance. This technology ensures that the maximum capabilities of the PCI interface are used by automatically tuning the controller to the specific system in which it is operating.

The MII, an industry-standard interface for connecting a variety of external IEEE 802.3u physical layer interfaces, is supported fully by the TNETE100PM. In addition, the TNETE100PM features an IEEE 802.12-compliant superset of the MII to allow for support of 100VG-AnyLAN physical layer interfaces. This allows TNETE100PM-based systems to support 100 Base-TX, 100 Base-TX, 100 Base-T4, and 100VG-AnyLAN cabling schemes for maximum flexibility as each new physical layer interface becomes available in the marketplace.

An intelligent protocol handler (PH) implements the serial protocols of the network. The PH is designed for minimum overhead related to multiple protocols, using common state machines to implement 95% of the total protocol handler. On transmit, the PH serializes data, adds framing and cyclic redundancy check (CRC) fields, and interfaces to the network physical layer (PHY) chip. On receive, it provides address recognition, CRC and error-checking, frame disassembly, and deserialization. Data for multiple channels is passed to and from the PH by way of circular-buffer FIFOs in the FIFO SRAM.

ThunderLAN is the first multimedia-ready architecture and is capable of prioritizing data regardless of the selected protocol. The demand-priority protocol supports two priorities of frames: normal and priority. The two transmit channels provide independent host channels for these two frame types. Carrier-sense multiple access with collision detection (CSMA/CD) protocols only support a single priority of frame, but the two channels can be used to prioritize network access. All received frames pass through the single receive channel.

SPWS026 - OCTOBER 1996

#### description (continued)

Compliant with IEEE Standard 1149.1 (JTAG), the TNETE100PM provides a five-pin test-access port that is used for boundary-scan testing.

The TNETE100PM is available in a 144-pin thin quad flat package (TQFP) and quad flat package (QFP).

#### differences between TNETE100A and TNETE100PM

The TNETE100PM implements additional power management features such as Magic Packet and PCI specification 2.1 compatibility for low power/sleep mode, advanced configuration and power interface (ACPI).

#### pin assignments

SPWS026 - OCTOBER 1996

#### functional block diagram

#### **Pin Functions**

| PIN<br>NAME | NO. | TYPET    | DESCRIPTION                                                                                                                         |  |  |  |  |

|-------------|-----|----------|-------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| INAME       | NO. | <u> </u> |                                                                                                                                     |  |  |  |  |

|             |     |          | TEST PORT                                                                                                                           |  |  |  |  |

| TCLK        | 124 | l        | Test clock. TCLK is used to clock state information and test data into and out of the device durin operation of the test port.      |  |  |  |  |

| TDI         | 126 | I        | Test data input. TDI is used to shift test data and test instructions serially into the device durin operation of the test port.    |  |  |  |  |

| TDO         | 125 | 0        | Test data output. TDO is used to shift test data and test instructions serially out of the device durin operation of the test port. |  |  |  |  |

| TMS         | 123 |          | Test mode select. TMS is used to control the state of the test port controller within TNETE100PM.                                   |  |  |  |  |

| TRST        | 121 | I        | Test reset. TRST is used for asynchronous reset of the test port controller.                                                        |  |  |  |  |

|             |     |          | PCI INTERFACE                                                                                                                       |  |  |  |  |

| PAD31       | 135 |          |                                                                                                                                     |  |  |  |  |

| PAD30       | 137 |          |                                                                                                                                     |  |  |  |  |

| PAD29       | 138 |          |                                                                                                                                     |  |  |  |  |

| PAD28       | 140 |          |                                                                                                                                     |  |  |  |  |

| PAD27       | 141 | 1/0      | PCI address/data bus. Byte 3 (most significant) of the PCI address/data bus                                                         |  |  |  |  |

| PAD26       | 143 |          |                                                                                                                                     |  |  |  |  |

| PAD25       | 144 |          |                                                                                                                                     |  |  |  |  |

| PAD24       | 1   |          |                                                                                                                                     |  |  |  |  |

| PAD23       | 5   |          |                                                                                                                                     |  |  |  |  |

| PAD22       | 7   |          |                                                                                                                                     |  |  |  |  |

| PAD21       | 8   |          |                                                                                                                                     |  |  |  |  |

| PAD20       | 9   | 1/0      | DCI address /data has Data Battha DCI address /data h                                                                               |  |  |  |  |

| PAD19       | 11  | "        | PCI address/data bus. Byte 2 of the PCI address/data bus                                                                            |  |  |  |  |

| PAD18       | 12  |          |                                                                                                                                     |  |  |  |  |

| PAD17       | 13  |          |                                                                                                                                     |  |  |  |  |

| PAD16       | 15  |          |                                                                                                                                     |  |  |  |  |

| PAD15       | 29  |          |                                                                                                                                     |  |  |  |  |

| PAD14       | 30  |          |                                                                                                                                     |  |  |  |  |

| PAD13       | 32  |          |                                                                                                                                     |  |  |  |  |

| PAD12       | 33  | 1/0      | PCI address/data bus. Byte 1 of the PCI address/data bus                                                                            |  |  |  |  |

| PAD11       | 35  | "        | 1 or address/data bus. Dyte 1 of the Pol address/data bus                                                                           |  |  |  |  |

| PAD10       | 36  |          |                                                                                                                                     |  |  |  |  |

| PAD9        | 38  |          |                                                                                                                                     |  |  |  |  |

| PAD8        | 39  |          |                                                                                                                                     |  |  |  |  |

| PAD7        | 42  |          |                                                                                                                                     |  |  |  |  |

| PAD6        | 43  |          |                                                                                                                                     |  |  |  |  |

| PAD5        | 45  |          |                                                                                                                                     |  |  |  |  |

| PAD4        | 46  | 1/0      | PCI address/data bus. Byte 0 (least significant) of the PCI address/data bus                                                        |  |  |  |  |

| PAD3        | 47  |          |                                                                                                                                     |  |  |  |  |

| PAD2        | 49  |          |                                                                                                                                     |  |  |  |  |

| PAD1        | 50  |          |                                                                                                                                     |  |  |  |  |

| PAD0        | 51  | 1        |                                                                                                                                     |  |  |  |  |

PADO 51 | The state input of the

### ThunderLAN™ TNETE100PM PCI ETHERNET<sup>TM</sup> CONTROLLER WITH POWER MANAGEMENT SINGLE-CHIP 10 BASE-T WITH MII FOR 100 BASE-T/100VG-AnyLAN SPWS026 - OCTOBER 1996

#### Pin Functions (Continued)

| PIN<br>NAME                          | NO.                 | TYPET | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------------------------------|---------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                      |                     |       | PCI INTERFACE (CONTINUED)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| PCLK                                 | 131                 | I     | PCI clock. PCLK is the clock reference for all PCI bus operations. All other PCI pins except PRSTand PINTA are sampled on the rising edge of PCLK. All PCI bus timing parameters are defined with respect to this edge.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| PCLKRUN                              | 53                  | I/O‡  | Clock run control. Powerdown-enable-configuration. The PCLKRUN pin must be connected to the PRST signal for the system. This reset is generated by the VDDI supply and, therefore, is used to put the TNETE100PM into D3off mode when SOPD = 1. When the PCLKRUN pin is asserted low, the TNETE100PM performs the following internal functions:  • Disables PCLK during sleep state  • Puts all PCI outputs in high impedance mode asynchonously  • Disables PFRAME# to ensure that the TNETE100PM is signaled that it is doing a PCII/O cycle  • Resets all TNETE100PM internal state machines  • Disables all interrupts  • Sets PowerState = 11b (only if SOPD = 1)  • Stops the transmitter and receiver (destructive)  NOTE: Ten PCLK cycles are required for the TNETE100PM to terminate PCI operations and reset all state machines after PCLKRUN goes low.  Clock run control. Clock-run-enable configuration. The PCLKRUN pin must be connected to the PCLKRUN signal of the system. PCLKRUN is the active-low PCI clock request/grant signal that allows the TNETE100PM to indicate when an active PCI clock is required. (This is an open drain.) |

| PC/BE3<br>PC/BE2<br>PC/BE1<br>PC/BE0 | 2<br>16<br>28<br>41 | 1/0   | PCI bus command and byte enables: PC/BE3 enables byte 3 (MSbyte) of the PCI address/data bus. PC/BE2 enables byte 2 of PCI address/data bus. PC/BE1 enables byte 1 of PCI address/data bus. PC/BE0 enables byte 0 (LSbyte) of PCI address/data bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| PDEVSEL                              | 21                  | 1/0   | PCI device select. PDEVSEL indicates that the driving device has decoded one of its addresses as the target of the current access. The TNETE100PM drives PDEVSELwhen it decodes an access to one of its registers. As a bus master, the TNETE100PM monitors PDEVSEL to detect accesses to illegal memory addresses.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| PFRAME                               | 17                  | 1/0   | PCI cycle frame. PFRAME is driven by the active bus master to indicate the beginning and duration of an access. PFRAME is asserted to indicate the start of a bus transaction and remains asserted during the transaction, only being deasserted in the final data phase.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| PGNT                                 | 132                 | ı     | PCI bus grant. PGNT is asserted by the system arbiter to indicate that the TNETE100PM has been granted control of the PCI bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| PIDSEL                               | 4                   | 1     | PCI initialization device select. PIDSEL is the chip select for access to PCI configuration registers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| PINTA                                | 128                 | O/D   | PCI interrupt. PINTA is the interrupt request from the TNETE100PM. PCI interrupts are shared, so this is an open-drain (wired-OR) output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| PIRDY                                | 19                  | 1/0   | PCI initiator ready. PIRDY is driven by the active bus master to indicate that it is ready to complete the current data phase of a transaction. A data phase is not completed until both PIRDY and PTRDY are sampled asserted. When the TNETE100PM is a bus master, it uses PIRDY to align incoming data on reads or outgoing data on writes with its internal RAM-access synchronization (maximum one cycle at the beginning of burst). When the TNETE100PM is a bus slave, it extends the access appropriately until both PIRDY and PTRDY are asserted.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| PTRDY                                | 20                  | 1/0   | PCI target ready. PTRDY is driven by the selected device (bus slave or target) to indicate that it is ready to complete the current data phase of a transaction. A data phase is not completed until both PIRDY and PTRDY are sampled asserted.  ThunderLAN uses PTRDY to ensure every direct I/O (DIO) operation is correctly interlocked.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| PPAR                                 | 27                  | 1/0   | PCI parity. PPAR carries even parity across PAD[31:0] and PC/BE[3:0]. It is driven by the TNETE100PM during all address and write cycles as a bus master and during all read cycles as a bus slave.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

<sup>†</sup> I = input, I/O = 3-state input/output, O/D = open-drain output ‡ Open drain

#### Pin Functions (Continued)

| PIN                                                          |                                                                    |            | Pin Functions (Continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------------------------------------------------------------|--------------------------------------------------------------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                                                         | NO.                                                                | TYPET      | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                              |                                                                    |            | PCI INTERFACE (CONTINUED)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| PPERR                                                        | 24                                                                 | 1/0        | PCI parity error. PPERR indicates a data parity error on all PCI transactions except special cycles.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| PREQ                                                         | 134                                                                | 1/0        | PCI bus request. PREQ is asserted by the TNETE100PM to request control of the PCI bus. This is not a shared signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| PRST                                                         | 129                                                                | ł          | PCI reset signal. Power-down-enable configuration. The PRST pin must be connected to a reset signal (VAUXGOOD) by the auxiliary power supply. This pin resets the TNETE100PM on initial power up only. When PRST is asserted low, the TNETE100PM performs the following internal functions:  • Resets all TNETE100PM registers and state machines  • Puts all PCI outputs (and IEEE standard JTAG pins) in high impedance mode asynchronously PCI reset signal. Clock-run-enable configuration. The PRST pin should be connected to the PRST signal for the system. When PRST is asserted low, the TNETE100PM performs the following internal functions:  • Resets TNETE100PM registers and state machines  • Puts all PCI outputs (and IEEE standard JTAG pins) in high impedance mode asynchronously |

| PSERR                                                        | 25                                                                 | Q/D        | PCI system error. PSERR indicates parity errors or special cycle data parity errors.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| PSTOP                                                        | 23                                                                 | I/O        | PCI stop. PSTOP indicates the current target is requesting the master to stop the current transaction.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                              |                                                                    |            | BIOS ROM/LED DRIVER INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

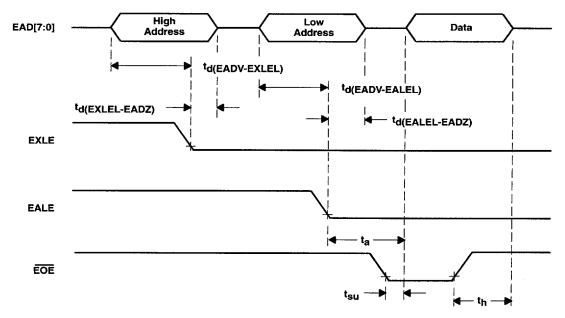

| EAD7<br>EAD6<br>EAD5<br>EAD4<br>EAD3<br>EAD2<br>EAD1<br>EAD0 | AD7 54<br>AD6 55<br>AD5 56<br>AD4 57<br>AD3 59<br>AD2 60<br>AD1 61 |            | <ul> <li>EPROM address/data. EAD[7:0] is a multiplexed byte-bus that is used to address and read data from an external BIOS ROM.</li> <li>On the cycle when EXLE is asserted low, EAD[7:0] is driven with the high byte of the address.</li> <li>On the cycle when EALE is asserted low, EAD[7:0] is driven with the low byte of the address.</li> <li>When EOE is asserted, BIOS ROM data should be placed on the bus.</li> <li>These pins also can be used to drive external-status LEDs. Low-current (2–5 mA) LEDs can be connected directly (through appropriate resistors). High-current LEDs can be driven through buffers or from the BIOS ROM address latches.</li> </ul>                                                                                                                      |

| EALE                                                         | 65                                                                 | 0          | EPROM address latch enable. EALE is driven low to latch the low (least significant) byte of the BIOS ROM address from EAD[0:7].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| EOE                                                          | 64                                                                 | 0          | EPROM output enable. When EOE is active (low), EAD[0:7] is in the high-impedance mode and the output of the BIOS ROM should be placed on EAD[0:7].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| EXLE                                                         | 66                                                                 | 0          | EPROM extended address latch enable. EXLE is driven low to latch the high (most significant) byte of the BIOS ROM address from EAD[0:7].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                              |                                                                    |            | CONFIGURATION EEPROM INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

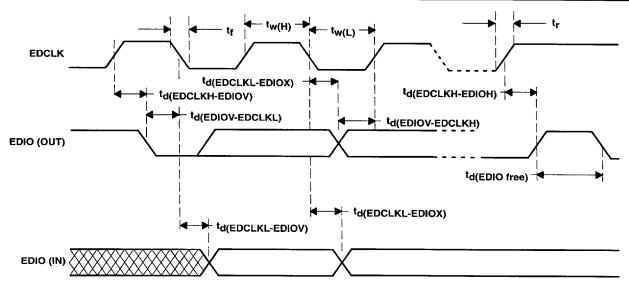

| EDCLK                                                        | 68                                                                 | 0          | EEPROM data clock. EDCLK transfers serial clocked data to the 2K-bit serial EEPROMs (24C02) (see Note 1). EDCLK requires an external pullup for EEPROM operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| EDIO                                                         | 69                                                                 | 1/0        | EEPROM data I/O. EDIO is the bidirectional serial data/address line to the 2K-bit serial EEPROM (24C02). EDIO requires an external pullup for EEPROM operation. Tying EDIO to ground disables the EEPROM interface and prevents autoconfiguration of the PCI configuration register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                              | N.                                                                 | IEDIA-INDE | PENDENT INTERFACE (100-Mbps CSMA/CD AND DEMAND PRIORITY)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| MCOL                                                         | 80                                                                 | l          | Collision sense In CSMA/CD mode, assertion of MCOL indicates a network collision. In demand-priority mode, MCOL (active low) is used to acknowledge a transmission request. The TNETE100PM begins frame transmission 50 MTCLK cycles after the assertion (low) of MCOL.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

<sup>†</sup> I = input, O = output, I/O = 3-state input/output, O/D = open-drain output

### ThunderLAN™ TNETE100PM PCI ETHERNET<sup>TM</sup> CONTROLLER WITH POWER MANAGEMENT SINGLE-CHIP 10 BASE-T WITH MII FOR 100 BASE-T/100VG-AnyLAN SPWS026 – OCTOBER 1996

#### Pin Functions (Continued)

| PIN                              |                      | TYPET                                 | PEGODINTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------------------------------|----------------------|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                             | NO.                  | TYPE†                                 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                  | MEDIA-II             | NDEPENDE                              | NT INTERFACE (100-Mbps CSMA/CD AND DEMAND PRIORITY) (CONTINUED)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| MCRS                             | 81                   | 1                                     | Carrier sense. MCRS indicates a frame-carrier signal is being received.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

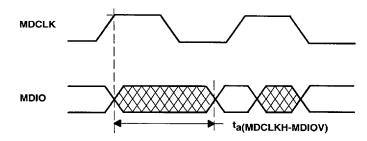

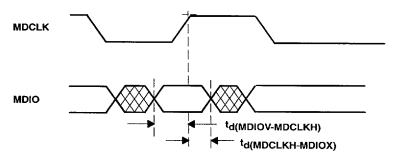

| MDCLK                            | 91                   | 0                                     | Management data clock. MDCLK is part of the serial management interface to physical-media independent (PMI)/PHY chip.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| MDIO                             | 93                   | 1/0                                   | Management data I/O. MDIO is part of the serial management interface to PMI/PHY chip.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

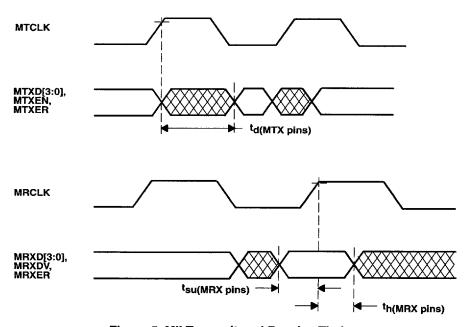

| MRCLK                            | 82                   | 1                                     | Receive clock. MRCLK is the receive clock source from the attached PHY and PMI device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| MRST                             | 95                   | 0                                     | MII reset. MRST is the reset signal to the PMI/PHY front-end (active low).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| MRXD0<br>MRXD1<br>MRXD2<br>MRXD3 | 83<br>85<br>86<br>87 | I                                     | Receive data. MRXD[3:0] is the nibble-receive data from the physical-media dependent (PMD) front end. In demand-priority mode, ThunderLAN reads the frame priority of incoming frames on these pins on the cycle before assertion of MRXDV (the cycle before frame reception begins).  • MRXD1 indicates the transmission priority of the received frame. A value of zero indicates normal transmission, and a value of one indicates priority transmission.  Data on these pins is always synchronous to MRCLK.                                                                                |

| MRXDV                            | 89                   | ı                                     | Receive data valid. MRXDV indicates data on MRXD[3:0] is valid.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| MRXER                            | 90                   | ı                                     | Receive error. MRXER indicates reception of a coding error on received data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| MTCLK                            | 71                   | l                                     | Transmit clock. MTCLK is the transmit clock source from the attached PHY and PMI device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| MTXD0<br>MTXD1<br>MTXD2<br>MTXD3 | 72<br>73<br>74<br>76 | 0                                     | Transmit data. MTXD[3:0] is the nibble-transmit data from TNETE100PM. When MTXEN is asserted, these pins carry transmit data. In demand-priority mode, the TNETE100PM drives the request state of the controller on these pins when MTXEN is not asserted (frame transmission not in progress).  • MTXD0 asserted indicates the TNETE100PM is requesting frame transmission.  • MTXD1 indicates the transmission priority required. A value of zero indicates normal transmission, and a value of one indicates high-priority transmission.  Data on these pins is always synchronous to MTCLK. |

| MTXER                            | 78                   | 0                                     | Transmit error. MTXER allows coding errors to be propagated across the MII.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| MTXEN                            | 77                   | 0                                     | Transmit enable. MTXEN indicates valid transmit data on MTXD[3:0].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                  |                      | · · · · · · · · · · · · · · · · · · · | NETWORK INTERFACE (10 Base-T AND AUI)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

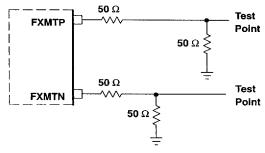

| ACOLN<br>ACOLP                   | 111<br>109           | А                                     | AUI-receive pair. ACOLN and ACOLP are differential line receiver inputs and connect to receive pair through transformer isolation, etc.                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| ARCVN<br>ARCVP                   | 108<br>106           | Α                                     | AUI-receive pair. ARCVN and ARCVP are differential line receiver inputs and connect to receive pair through transformer isolation, etc.                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

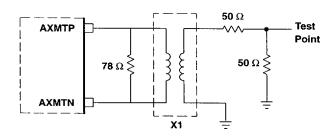

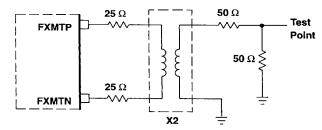

| AXMTP<br>AXMTN                   | 99<br>100            | А                                     | AUI-transmit pair. AXMTP and AXMTN are differential line-transmitter outputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| FATEST                           | 118                  | Α                                     | Analog test pin. FATEST provides access to the filter of the reference PLL. This pin must be left as a "no connect".                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

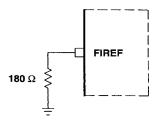

| FIREF                            | 116                  | Α                                     | Current reference. FIREF is used to set a current reference for the analog circuitry.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| FONLY                            | 120                  | Α                                     | Front-end only pin. The FONLY pin should be tied low for systems not requiring the power management capabilities of the TNETE100PM.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

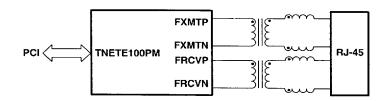

| FRCVN<br>FRCVP                   | 105<br>103           | Α                                     | 10 Base-T receive pair. FRCVN and FRCVP are differential line-receiver inputs and connect to receive pair through transformer isolation, etc.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

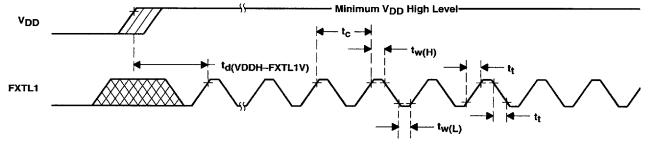

| FXTL1<br>FXTL2                   | 113<br>114           | A                                     | Crystal oscillator pins. FXTL1 is driven from a 20-MHz crystal oscillator module.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| FXMTP<br>FXMTN                   | 97<br>98             | Α                                     | 10 Base-T transmit pair. FXMTP and FXMTN are differential line-transmitter outputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

† I = input, O = output, A = Analog

NOTE 1: This pin should be tied to VDD with a 4.7-k $\Omega$  – 10-k $\Omega$  pullup resistor.

SPWS026 - OCTOBER 1996

#### Pin Functions (Continued)

| PIN<br>NAME        | NO.                                                 | TYPET | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------------|-----------------------------------------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                    |                                                     |       | POWER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| VDDI               | 6, 14,<br>34, 48,<br>122, 136,<br>142               | PWR   | PCI V <sub>DD</sub> pins. Power-down-enable configuration V <sub>DDI</sub> pins provide power for the PCI I/O pin drivers. Connect V <sub>DDI</sub> pins to a 5-V power supply when using 5-V signals on the PCI bus. Connect V <sub>DDI</sub> pins to a 3-V power supply when using 3-V signals on the PCI bus. Pin #122 should be connected to a power supply that is not powered down during SLEEP mode. This supply must be the same voltage as V <sub>DDI</sub> when the PCI bus is fully functional. PCI V <sub>DD</sub> pins. Clock-run-enable configuration V <sub>DDI</sub> pins provide power for the PCI I/O pin drivers. Connect V <sub>DDI</sub> pins to a 5-V power supply when using 5-V signals on the PCI bus. Connect V <sub>DDI</sub> pins to a 3-V power supply when using 3-V signals on the PCI bus. |

| V <sub>DDL</sub>   | 22, 37,<br>58, 70,<br>79, 84,<br>94, 130            | PWR   | Logic V <sub>DD</sub> pins (5 V). Power-down-enable configuration V <sub>DDL</sub> pins provide power for internal TNETE100PM logic and must be connected to an auxiliary power source (5 V).  Logic V <sub>DD</sub> pins (5 V). Clock-run-enable configuration V <sub>DDL</sub> pins provide power for internal TNETE100PM logic and always must be connected to 5 V.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| V <sub>DDOSC</sub> | 115                                                 | PWR   | Analog power pin. VDDOSC is the 5-V power for the crystal oscillator circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| V <sub>DDR</sub>   | 104<br>107                                          | PWR   | Analog power pin. V <sub>DDR</sub> is the 5-V power for the receiver circuitry.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| V <sub>DDT</sub>   | 96                                                  | PWR   | Analog power pin. VDDT is the 5-V power for the transmitter circuitry.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| V <sub>DDVCO</sub> | 117                                                 | PWR   | Analog power pin. VDDVCO is the 5-V power for the voltage controller oscillator (VCO) and filter input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| V <sub>SSI</sub>   | 3, 10, 26,<br>31, 40,<br>52, 67,<br>88, 127,<br>139 | PWR   | PCI I/O ground pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| V <sub>SSL</sub>   | 18, 44,<br>63, 75,<br>92, 133                       | PWR   | Logic ground pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Vssosc             | 112                                                 | PWR   | Analog power pin. Ground for crystal oscillator circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |