### 查询TNETA1600供应商

# 捷多邦,专业PCB打样工厂,24小时加急出资NETA1600 SONET/SDH ATM RECEIVER/TRANSMITTER FOR 622.08-MBIT/S OR 155.52-MBIT/S OPERATION

SDNS036 - FEBRUARY 1996

- Termination/Generation of 155.52-Mbit/s or 622.08-Mbit/s SONET/SDH Frames Carrying ATM Cells; Including:

- Frame Scrambling/Descrambling

- Pointer Processing

- ATM-Cell Delineation

- ATM-Cell Extraction/Insertion

- ATM-Cell Payload Scrambling/Descrambling

- Cell-Rate Decoupling

- Access to Receive and Transmit Transport-Overhead (TOH) and Path-Overhead (POH) Bytes Through the Controller Interface

- Detects Multiple-Bit Errors and Corrects Single-Bit Errors in the 5-Byte ATM Headers of Incoming ATM Cells

- Separate Serial Receive- and Transmit-Data Communication Ports Allow Access to Data Communications and Orderwire-Overhead Bytes

- Alarm Generation/Checking in Accordance With BellCore, ANSI, and ITU-T Specifications

- Performance Monitors/Counters Provide Statistics on B1/B2/B3 Coding Violations, B1/B2/B3 Block Errors, Line and Path Far-End Block Errors (Line FEBEs and Path FEBEs) and Other Status Data

- Supports Boundary Scan Through a 5-Wire JTAG Interface in Accordance With IEEE Std 1149.1-1990 (Includes IEEE Std 1149.1a-1993) IEEE Standard Test-Access Port and Boundary-Scan Architecture

### description

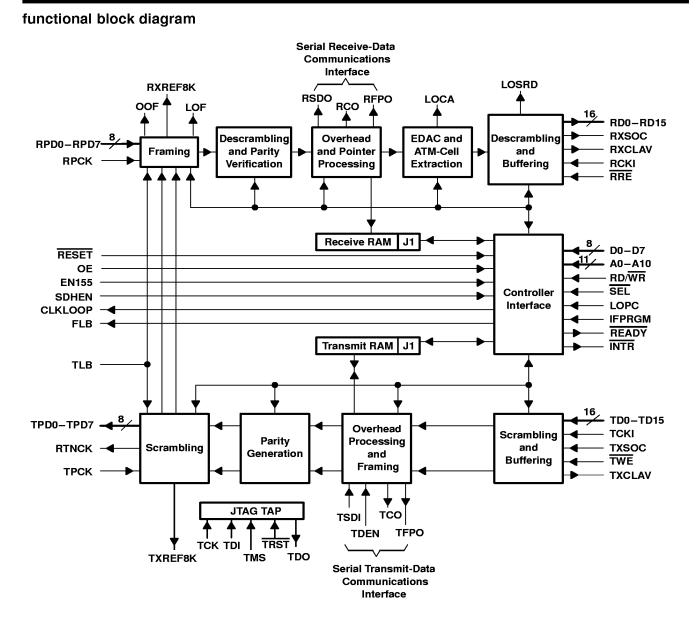

The synchronous optical network (SONET)/synchronous digital hierarchy (SDH) asynchronous transport mode (ATM) line-interface receiver/transmitter provides a versatile solution for transporting ATM cells over the SONET/SDH network at 155.52 Mbit/s or 622.08 Mbit/s.

On the receive side, the TNETA1600 accepts byte-wide data aligned to proper SONET-/SDH-byte boundaries, performs frame alignment and descrambling, and extracts SONET/SDH payload and overhead. The overhead is placed in the receive-overhead RAM where each byte can be accessed through the controller interface. Cell boundaries are established in the payload and ATM cells are extracted, descrambled, and passed to the receive output FIFO for output to the ATM-layer device (i.e., a reassembly device).

On the transmit side, complete ATM cells are scrambled and placed in a SONET/SDH synchronous payload envelope (SPE). Transport- and path- overhead bytes are programmable through the transmit-overhead RAM. The overhead and payload are scrambled and sent out as a byte-wide data stream.

The TNETA1600 is characterized for operation over a temperature range of -40°C to 85°C.

dzsc.com

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCT PREVIEW information concerns products in the formative or design phase of development. Characteristic data and other specifications are design goals. Texas Instruments reserves the right to change or discontinue these products without notice.

Copyright © 1996, Texas Instruments Incorporated

SDNS036 - FEBRUARY 1996

PQFP PACKAGE (TOP VIEW)

|          | п  |    | п  |     |     |     | _ | ר ר | _  |    |     | <b>،</b> ר | _   | _   | 1 г | - | _   | ור | _ | _   |   | _   | _   | <b>.</b> . |     | г   | <b>,</b> , |     | г |   | _   | _   |    |          | _   |     |   | <b>.</b> . |    |    | г  | . – | י ר |        |     | г | - I |     |     | _  | ۲ | יר  | 7        |    |           |

|----------|----|----|----|-----|-----|-----|---|-----|----|----|-----|------------|-----|-----|-----|---|-----|----|---|-----|---|-----|-----|------------|-----|-----|------------|-----|---|---|-----|-----|----|----------|-----|-----|---|------------|----|----|----|-----|-----|--------|-----|---|-----|-----|-----|----|---|-----|----------|----|-----------|

| /        |    |    |    | _   | 156 | 155 |   |     |    |    |     | _          | 150 | 149 |     | - | -   | _  |   | 145 |   | 4   | 113 | ?          | Ņ   | +   | _          | 140 | _ |   | 138 |     |    | 0        | 135 | 134 |   | 55         | N  | ě  | 00 |     |     | 128    |     |   |     | 125 |     |    |   |     |          |    | 1         |

| 1        | 16 | 12 | 42 | 157 | ÷   | 5   | ÷ | 2 ; | -  | ÷  | 151 | 2          | -   | 7   |     | 4 | 147 |    | 4 | 77  | - | 144 | ÷   | 1          | 142 | *** | 1          | 4   | ÷ | 2 | ÷   | 137 |    | <u>-</u> | ÷   | 5   |   | -          | ę  | 5  | ÷  |     | 2   | ₽<br>P | 127 |   |     | Ę.  | 124 | ÷. |   |     |          |    | L.        |

| 2        |    |    |    |     |     |     |   |     |    |    |     |            |     |     |     |   |     |    |   |     |   |     |     |            |     |     |            |     |   |   |     |     |    |          |     |     |   |            |    |    |    |     |     |        |     |   |     |     |     |    |   |     | 12<br>11 |    | H         |

| 3        |    |    |    |     |     |     |   |     |    |    |     |            |     |     |     |   |     |    |   |     |   |     |     |            |     |     |            |     |   |   |     |     |    |          |     |     |   |            |    |    |    |     |     |        |     |   |     |     |     |    |   |     | 11       |    | F.        |

| 4        |    |    |    |     |     |     |   |     |    |    |     |            |     |     |     |   |     |    |   |     |   |     |     |            |     |     |            |     |   |   |     |     |    |          |     |     |   |            |    |    |    |     |     |        |     |   |     |     |     |    |   |     | 11       |    | F.        |

| 5        |    |    |    |     |     |     |   |     |    |    |     |            |     |     |     |   |     |    |   |     |   |     |     |            |     |     |            |     |   |   |     |     |    |          |     |     |   |            |    |    |    |     |     |        |     |   |     |     |     |    |   |     | 11       |    | Б         |

| 6        |    |    |    |     |     |     |   |     |    |    |     |            |     |     |     |   |     |    |   |     |   |     |     |            |     |     |            |     |   |   |     |     |    |          |     |     |   |            |    |    |    |     |     |        |     |   |     |     |     |    |   |     | 11       |    | Б         |

| 7        |    |    |    |     |     |     |   |     |    |    |     |            |     |     |     |   |     |    |   |     |   |     |     |            |     |     |            |     |   |   |     |     |    |          |     |     |   |            |    |    |    |     |     |        |     |   |     |     |     |    |   |     | 11       |    | Б         |

| 8        |    |    |    |     |     |     |   |     |    |    |     |            |     |     |     |   |     |    |   |     |   |     |     |            |     |     |            |     |   |   |     |     |    |          |     |     |   |            |    |    |    |     |     |        |     |   |     |     |     |    |   |     | 11       |    |           |

| 9        |    |    |    |     |     |     |   |     |    |    |     |            |     |     |     |   |     |    |   |     |   |     |     |            |     |     |            |     |   |   |     |     |    |          |     |     |   |            |    |    |    |     |     |        |     |   |     |     |     |    |   |     | 11       |    |           |

| 10       |    |    |    |     |     |     |   |     |    |    |     |            |     |     |     |   |     |    |   |     |   |     |     |            |     |     |            |     |   |   |     |     |    |          |     |     |   |            |    |    |    |     |     |        |     |   |     |     |     |    |   |     | 11       |    | Þ         |

| 11       |    |    |    |     |     |     |   |     |    |    |     |            |     |     |     |   |     |    |   |     |   |     |     |            |     |     |            |     |   |   |     |     |    |          |     |     |   |            |    |    |    |     |     |        |     |   |     |     |     |    |   |     | 11       | 0  | Þ         |

| 12       |    |    |    |     |     |     |   |     |    |    |     |            |     |     |     |   |     |    |   |     |   |     |     |            |     |     |            |     |   |   |     |     |    |          |     |     |   |            |    |    |    |     |     |        |     |   |     |     |     |    |   |     | 10       | 9  | Þ         |

| 13       |    |    |    |     |     |     |   |     |    |    |     |            |     |     |     |   |     |    |   |     |   |     |     |            |     |     |            |     |   |   |     |     |    |          |     |     |   |            |    |    |    |     |     |        |     |   |     |     |     |    |   |     | 10       | 8  | $\square$ |

| 14       |    |    |    |     |     |     |   |     |    |    |     |            |     |     |     |   |     |    |   |     |   |     |     |            |     |     |            |     |   |   |     |     |    |          |     |     |   |            |    |    |    |     |     |        |     |   |     |     |     |    |   |     | 10       |    | $\square$ |

| 15       |    |    |    |     |     |     |   |     |    |    |     |            |     |     |     |   |     |    |   |     |   |     |     |            |     |     |            |     |   |   |     |     |    |          |     |     |   |            |    |    |    |     |     |        |     |   |     |     |     |    |   |     | 10       |    | 2         |

| 16       |    |    |    |     |     |     |   |     |    |    |     |            |     |     |     |   |     |    |   |     |   |     |     |            |     |     |            |     |   |   |     |     |    |          |     |     |   |            |    |    |    |     |     |        |     |   |     |     |     |    |   |     | 10       |    | Ľ.        |

| 17       |    |    |    |     |     |     |   |     |    |    |     |            |     |     |     |   |     |    |   |     |   |     |     |            |     |     |            |     |   |   |     |     |    |          |     |     |   |            |    |    |    |     |     |        |     |   |     |     |     |    |   |     | 10       |    | E.        |

| 18<br>19 |    |    |    |     |     |     |   |     |    |    |     |            |     |     |     |   |     |    |   |     |   |     |     |            |     |     |            |     |   |   |     |     |    |          |     |     |   |            |    |    |    |     |     |        |     |   |     |     |     |    |   |     | 10       |    | E.        |

| 20       |    |    |    |     |     |     |   |     |    |    |     |            |     |     |     |   |     |    |   |     |   |     |     |            |     |     |            |     |   |   |     |     |    |          |     |     |   |            |    |    |    |     |     |        |     |   |     |     |     |    |   |     | 10       |    | H         |

| 20       |    |    |    |     |     |     |   |     |    |    |     |            |     |     |     |   |     |    |   |     |   |     |     |            |     |     |            |     |   |   |     |     |    |          |     |     |   |            |    |    |    |     |     |        |     |   |     |     |     |    |   |     | 10<br>10 |    | F.        |

| 22       |    |    |    |     |     |     |   |     |    |    |     |            |     |     |     |   |     |    |   |     |   |     |     |            |     |     |            |     |   |   |     |     |    |          |     |     |   |            |    |    |    |     |     |        |     |   |     |     |     |    |   |     |          | 19 | Б         |

| 23       |    |    |    |     |     |     |   |     |    |    |     |            |     |     |     |   |     |    |   |     |   |     |     |            |     |     |            |     |   |   |     |     |    |          |     |     |   |            |    |    |    |     |     |        |     |   |     |     |     |    |   |     |          | 18 | Б         |

| 24       |    |    |    |     |     |     |   |     |    |    |     |            |     |     |     |   |     |    |   |     |   |     |     |            |     |     |            |     |   |   |     |     |    |          |     |     |   |            |    |    |    |     |     |        |     |   |     |     |     |    |   |     |          | 17 | Б         |

| 25       |    |    |    |     |     |     |   |     |    |    |     |            |     |     |     |   |     |    |   |     |   |     |     |            |     |     |            |     |   |   |     |     |    |          |     |     |   |            |    |    |    |     |     |        |     |   |     |     |     |    |   |     |          | 6  | Б         |

| 26       |    |    |    |     |     |     |   |     |    |    |     |            |     |     |     |   |     |    |   |     |   |     |     |            |     |     |            |     |   |   |     |     |    |          |     |     |   |            |    |    |    |     |     |        |     |   |     |     |     |    |   |     |          | 5  | Б         |

| 27       |    |    |    |     |     |     |   |     |    |    |     |            |     |     |     |   |     |    |   |     |   |     |     |            |     |     |            |     |   |   |     |     |    |          |     |     |   |            |    |    |    |     |     |        |     |   |     |     |     |    |   |     |          | 4  | Þ         |

| 28       |    |    |    |     |     |     |   |     |    |    |     |            |     |     |     |   |     |    |   |     |   |     |     |            |     |     |            |     |   |   |     |     |    |          |     |     |   |            |    |    |    |     |     |        |     |   |     |     |     |    |   |     | g        | з  | 白         |

| 29       |    |    |    |     |     |     |   |     |    |    |     |            |     |     |     |   |     |    |   |     |   |     |     |            |     |     |            |     |   |   |     |     |    |          |     |     |   |            |    |    |    |     |     |        |     |   |     |     |     |    |   |     | g        | 2  | Þ         |

| 30       |    |    |    |     |     |     |   |     |    |    |     |            |     |     |     |   |     |    |   |     |   |     |     |            |     |     |            |     |   |   |     |     |    |          |     |     |   |            |    |    |    |     |     |        |     |   |     |     |     |    |   |     | g        | 1  | Þ         |

| 31       |    |    |    |     |     |     |   |     |    |    |     |            |     |     |     |   |     |    |   |     |   |     |     |            |     |     |            |     |   |   |     |     |    |          |     |     |   |            |    |    |    |     |     |        |     |   |     |     |     |    |   |     | g        | 0  | Þ         |

| 32       |    |    |    |     |     |     |   |     |    |    |     |            |     |     |     |   |     |    |   |     |   |     |     |            |     |     |            |     |   |   |     |     |    |          |     |     |   |            |    |    |    |     |     |        |     |   |     |     |     |    |   |     | 8        | 9  | Þ         |

| 33       |    |    |    |     |     |     |   |     |    |    |     |            |     |     |     |   |     |    |   |     |   |     |     |            |     |     |            |     |   |   |     |     |    |          |     |     |   |            |    |    |    |     |     |        |     |   |     |     |     |    |   |     | 8        | 8  | P.        |

| 34       |    |    |    |     |     |     |   |     |    |    |     |            |     |     |     |   |     |    |   |     |   |     |     |            |     |     |            |     |   |   |     |     |    |          |     |     |   |            |    |    |    |     |     |        |     |   |     |     |     |    |   |     | 8        | 7  | 2         |

| 35       |    |    |    |     |     |     |   |     |    |    |     |            |     |     |     |   |     |    |   |     |   |     |     |            |     |     |            |     |   |   |     |     |    |          |     |     |   |            |    |    |    |     |     |        |     |   |     |     |     |    |   |     |          | 6  | Ľ.        |

| 36       |    |    |    |     |     |     |   |     |    |    |     |            |     |     |     |   |     |    |   |     |   |     |     |            |     |     |            |     |   |   |     |     |    |          |     |     |   |            |    |    |    |     |     |        |     |   |     |     |     |    |   |     |          | 5  | Ľ.        |

| 37       |    |    |    |     |     |     |   |     |    |    |     |            |     |     |     |   |     |    |   |     |   |     |     |            |     |     |            |     |   |   |     |     |    |          |     |     |   |            |    |    |    |     |     |        |     |   |     |     |     |    |   |     |          | 4  | E.        |

| 38       |    |    |    |     |     |     |   |     |    |    |     |            |     |     |     |   |     |    |   |     |   |     |     |            |     |     |            |     |   |   |     |     |    |          |     |     |   |            |    |    |    |     |     |        |     |   |     |     |     |    |   |     |          | 3  | E.        |

| 39       |    |    |    |     |     |     |   |     |    |    |     |            |     |     |     |   |     |    |   |     |   |     |     |            |     |     |            |     |   |   |     |     |    |          |     |     |   |            |    |    |    |     |     |        |     |   |     |     |     |    |   |     |          | 2  | Ľ.        |

| 40       |    |    |    |     |     |     |   |     |    | -  |     | _          |     |     |     |   |     |    | - |     | _ |     |     | _          | _   |     | _          |     | _ |   |     |     |    | _        |     |     |   |            | _  | _  |    | ~   |     |        |     |   | _   |     |     |    | _ |     |          | 1  | Ľ         |

|          | 41 | 42 | 43 | 44  | 45  |     |   |     | 48 | 49 |     | 20         |     |     | 2 1 |   | 54  |    |   |     |   | 57  |     |            |     |     |            |     | ŝ |   |     |     |    |          |     | 67  |   |            | 69 | 70 |    |     |     |        | 74  |   |     |     |     |    |   | 508 |          |    |           |

|          |    |    |    |     |     |     | L | Л   | _  |    | L   | Л          | _   |     | JТ  | 1 | Ľ   | J  | J |     | Л |     |     | Л          |     | L   | Л          |     | Γ | Л |     |     | IT | Л        | J   |     | L | Л          |    | П  | Ľ  | IT  | П   |        | П   |   | Л   |     |     |    |   |     |          |    |           |

**PRODUCT PREVIEW**

SDNS036 - FEBRUARY 1996

SDNS036 – FEBRUARY 1996

# **Terminal Functions**

# line-side parallel interface

| TERMINAL  | 1/0 | DESCRIPTION                                                                                                                                                                                                                                             |

|-----------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME NO.  |     |                                                                                                                                                                                                                                                         |

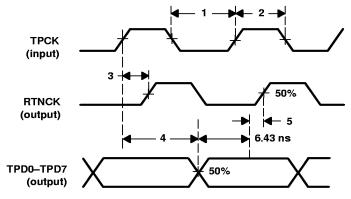

| RPD0-RPD7 | I   | Receive parallel data. This byte-wide data is clocked into the TNETA1600 on low-to-high transitions of RPCK. Bit 7 is the most-significant bit.                                                                                                         |

| RPCK      | I   | Receive parallel clock. Data on RPD0–RPD7 is clocked into the TNETA1600 on low-to-high transitions of RPCK. The frequency of RPCK is nominally 77.76 MHz for 622.08-Mbit/s operation or 19.44 MHz for 155.52-Mbit/s operation.                          |

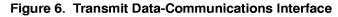

| трск      | I   | Transmit-parallel clock. Data is clocked out of the TNETA1600 on TPD0–TPD7 on low-to-high transitions of TPCK. The frequency of TPCK is 77.76 MHz for 622.08-Mbit/s operation or 19.44 MHz for 155.52-Mbit/s operation.                                 |

| TPD0-TPD7 | 0   | Transmit-parallel data. This byte-wide data is clocked out of the TNETA1600 on low-to-high transitions of TPCK and is accompanied by a return clock (RTNCK). TPD0–TPD7 is valid on low-to-high transitions of RTNCK. Bit 7 is the most-significant bit. |

| RTNCK     | 0   | Return clock. RTNCK is a retimed version of TPCK that accompanies data output on TPD0–TPD7. TPD0–TPD7 is valid on the rising edge of RTNCK.                                                                                                             |

# alarm indicators

| TERMINAL<br>NAME NO | D. 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |  |  |

|---------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|

| LOCA                | 0      | Loss-of-cell alignment. LOCA goes high when seven consecutive ATM cell slots occur with a mismatch between the calculated header-error check (HEC) byte and the fifth byte of the ATM header, indicating invalid ATM headers. LOCA goes low when valid ATM headers are detected in seven consecutive cell slots.                  |  |  |  |  |  |  |  |  |  |  |

| LOF                 | 0      | Loss of frame. LOF goes high when an out-of-frame (OOF) condition persists for 3 ms. LOF goes low when the OOF condition is cleared for 1 ms.                                                                                                                                                                                     |  |  |  |  |  |  |  |  |  |  |

| LOSRD               | 0      | Loss-of-receive data. LOSRD goes high when the receive output FIFO overflows, resulting in a loss of data.<br>The receive output FIFO can store a maximum of three complete ATM cells. If a cell is not extracted on the<br>receive output before additional cells arrive on the receive input, the arriving cells are discarded. |  |  |  |  |  |  |  |  |  |  |

| OOF                 | 0      | Out of frame. OOF goes high when four consecutive erred framing patterns are received. OOF goes low when two successive error-free framing patterns are received.                                                                                                                                                                 |  |  |  |  |  |  |  |  |  |  |

# **Terminal Functions (Continued)**

# control signals

| TERMINAL | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME NO  |     | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| EN155    | 1   | 155.52-Mbit/s enable. When EN155 is high, data operations at 155.52 Mbit/s are enabled for both the receiver and transmitter. In 155.52-Mbit/s mode, both the transmit- and receive-cell interfaces are byte wide such that data are transmitted and received on TD0–TD7 and RD0–RD7, respectively. TD8–TD15 and RD8–RD15 are not used. When EN155 is low, operations at 622.08 Mbit/s are enabled and all 16 bits of the transmit-cell and receive-cell interfaces are utilized. Changing the mode between 155.52 Mbit/s and 622.08 Mbit/s during normal operation may result in the loss of data. |

| OE       | 1   | Output enable. When OE is low, all outputs on the TNETA1600 go into the high-impedance state. This feature facilitates board-level testing.                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| RESET    | 1   | Device reset. When RESET goes low, the device is reset. This reset causes the receive side to restart the frame search and forces OOF, LOF, and LOCA high. The reset also flushes any ATM cells stored in the input and output FIFOs and causes the transmit side to begin building SONET frames from the A1 byte. A valid clock must be present on TPCK when RESET transitions from low to high because this transition starts the initialization of the transmit-overhead RAM.                                                                                                                    |

| SDHEN    | 1   | SDH enable. When SDHEN is high, frames are transmitted with SDH overhead. SDHEN is logically ORed with a bit in the control register such that both the bit and SDHEN must be low to transmit frames with SONET overhead. A change in the logically ORed combination of SDHEN and the associated control bit causes the transmit-RAM overhead to be overwritten with new SONET or SDH values, depending on the logically ORed combination of SDHEN and the overhead is altered, this could result in the loss of data being processed in the transmitter.                                           |

| TLB      | I   | Terminal loopback. TLB is logically ORed with a bit in the control register. If either or both are high, the data received at the transmit-cell interface flows normally through the transmit path to the scrambling function, where it is passed to the receive-framing function. The data is then processed through the receive path and output on RD0–RD15. Data being received on RPD0–RPD7 is blocked. However, transmit operation is not affected and output data is available on TPD0–TPD7.                                                                                                  |

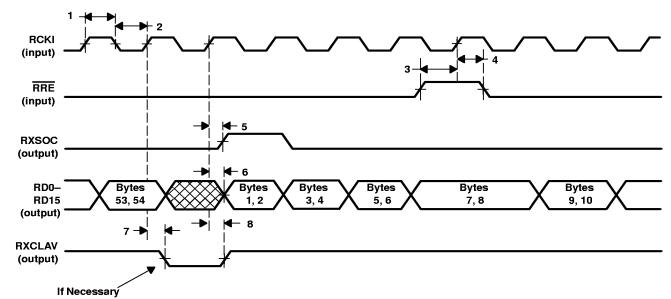

# receive-cell interface

| TERMINA  | ۱L  |     | DECORIDEION                                                                                                                                                                                                                                                                                                                                                       |

|----------|-----|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME     | NO. | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                       |

| RCKI     |     | I   | Receive clock input. Output data is valid on the receive-cell interface on positive transitions of RCKI when $\overline{\text{RRE}}$ is low.                                                                                                                                                                                                                      |

| RD0-RD15 |     | 0   | Receive output data. When EN155 is low (622.08-Mbit/s operation), ATM cell data is clocked out of the TNETA1600 through RD0–RD15 on positive transitions of RCKI, beginning with the first two bytes of the ATM header. When EN155 is high (155.52-Mbit/s operation), cells are clocked out on RD0–RD7 (RD8–RD15 are not used). RD0 is the least-significant bit. |

| RRE      |     | Ι   | Receive read enable. A low level on RRE enables the reading of data from the receive-cell interface.                                                                                                                                                                                                                                                              |

| RXSOC    |     | 0   | Receive start of ATM-cell indicator. RXSOC goes high identifying the first byte (or first two bytes in 622.08-Mbit/s operation) of an ATM cell on the receive-cell interface. RXSOC is low during the remainder of that cell's output.                                                                                                                            |

| RXCLAV   |     | 0   | Receive-cell available. RXCLAV goes high denoting that the receive output FIFO is capable of transferring<br>a complete ATM cell. RXCLAV goes low when the receive output FIFO is empty and the current output data<br>on RD0–RD15 is invalid.                                                                                                                    |

SDNS036 - FEBRUARY 1996

# **Terminal Functions (Continued)**

### transmit-cell interface

| TERMINAL |     | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                     |

|----------|-----|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME     | NO. | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                     |

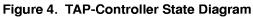

| тскі     |     | Ι   | Transmit clock input. Input signals are clocked into the transmit-cell interface and output signals are valid at the transmit-cell interface on positive transitions of TCKI, when TWE is low.                                                                                                                                                                                                  |

| TD0-TD15 |     | Ι   | Transmit input data. When EN155 is low (622.08-Mbit/s operation), <u>ATM</u> cells are clocked into the <u>TNE</u> TA1600 through TD0–TD15 on positive transitions of TCKI, provided TWE is low. If EN155 is high and TWE is low (155.52-Mbit/s operation), cells are clocked in on TD0–TD7 (TD8–TD15 are not used). TD0 is the least-significant bit.                                          |

| TWE      |     | Ι   | Transmit write enable. A low level on TWE enables the writing of ATM cells into the transmit-cell interface.                                                                                                                                                                                                                                                                                    |

| TXCLAV   |     | 0   | Transmit-cell available. TXCLAV goes high when the transmit input FIFO is capable of accepting the transfer of a complete ATM cell. TXCLAV goes low when the TNETA1600 can accept only four more write cycles (four bytes during 155.52-Mbit/s operation or eight bytes during 622.08-Mbit/s operation) from the ATM-layer device without overflowing the transmit input FIFO.                  |

| TXSOC    |     | Ι   | Transmit start-of-cell indicator. A high level on TXSOC identifies the first byte (or first two bytes in 622.08-Mbit/s operation) of an incoming ATM cell on the transmit-cell interface. TXSOC is held low during the remainder of that cell's input. Once a valid TXSOC indication is detected, subsequent TXSOC indications are ignored until the full 53 bytes of an ATM cell are received. |

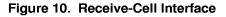

# controller interface

| TERMINAL |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME NO  | э.   <sup>I/C</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| A0–A10   | 1                   | Address lines. A0-A10 provide the address for accessing the internal registers and RAM. A10 is the most-significant bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| D0–D7    | 1/0                 | Data I/O. D0–D7 provides access to the contents of the device's internal registers and RAM. D7 is the most-significant bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| INTR     | C                   | Interrupt (open drain). INTR goes low to indicate that an unmasked condition has occurred.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

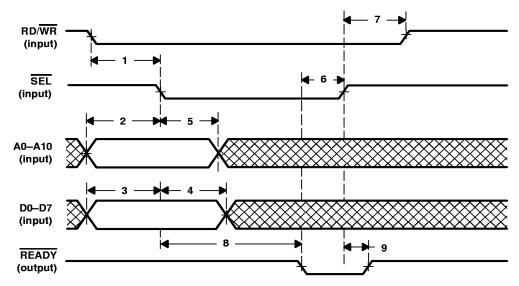

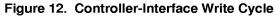

| RD/WR    |                     | Read/write control. A high-level input on RD/WR indicates a read operation and a low-level input indicates a write operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| READY    | С                   | Ready. READY goes low to indicate that the device is ready to complete the requested transaction.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| SEL      |                     | Device select. A low-level input on SEL enables the access of the device's internal registers and RAM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| IFPRGM   | I                   | Interface program mode. IFPRGM is logically ORed with a bit (place TX O/H RAM in program mode) in the control register. If either or both are high, the automatic write operations to transmit overhead by the TNETA1600 are disabled. During this condition, overhead values can be written into the TNETA1600 via the controller interface. Since these values are not automatically overwritten, the user is given the capability to transmit any value in any overhead-byte location. Overhead RAM addresses, which are not written to, retain their values. While in the program mode, the transmit data-communications port is disabled (TFPO is held low). When both IFPRGM and the associated control bit are low, specified overhead bytes are automatically overwritten each frame after the first row's overhead has been transmitted. |

| LOPC     | I                   | Loss of optical carrier. When LOPC goes high, a bit is set in the status register, and if not masked, an interrupt is generated on INTR. This provides an interrupt through the controller interface to the host indicating that the incoming optical signal has been lost. When LOPC goes low, the bit in the status register goes low and an interrupt is (again) generated on INTR.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| CLKLOOP  | С                   | Clock loopback. CLKLOOP is at a high level when the corresponding bit in the control register is at a high level. Similarly, if the control register bit is low, CLKLOOP is low. This allows a clock-loopback function on a line-side device (i.e., a TNETA1510, TNETA1610, or TNETA1611) to be controlled through the controller interface of the TNETA1600.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| FLB      | С                   | Facility loopback. FLB is at a high level when the corresponding bit in the control register is at a high level.<br>Similarly, if the control register bit is low, FLB is low. This allows a facility-loopback function on a line-side<br>device (i.e., a TNETA1510, TNETA1610, or TNETA1611) to be controlled through the controller interface<br>of the TNETA1600.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

# **Terminal Functions (Continued)**

## serial-receive data-communications interface

| TERMINAL | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME NO  |     | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

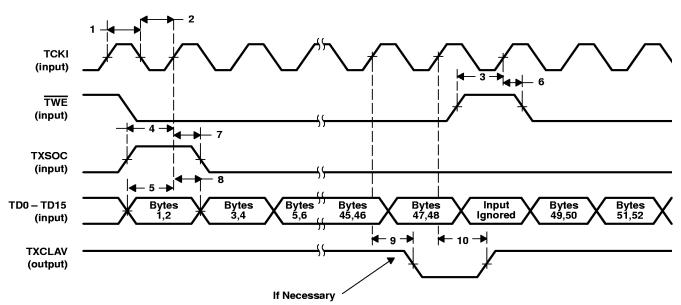

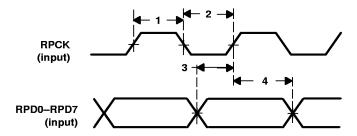

| RSDO     | 0   | Receive serial-data output. The 14 data-communications and orderwire bytes are output serially on RSDO in the following order: E1, D1 – D12, and E2. The most-significant bit (MSB) of each byte is sent out first. Data is valid on the rising edge of RCO. RFPO goes high to identify the concurrent output of the first bit (MSB) of E1. The remaining seven bits of E1 and the 13 other data-communications and orderwire bytes are then shifted out on consecutive clock cycles. |

| RCO      | 0   | Receive clock output. RSDO and RFPO are valid on the rising edge of RCO. RCO is a continuous clock with a frequency of 1.215 MHz. Once the first A1 byte of a frame is received, all 14 orderwire and data-communications bytes from the previous frame are serially transmitted in a burst, such that traffic is not always present on the interface.                                                                                                                                |

| RFPO     | 0   | Receive framing-pulse output. RFPO identifies the presence of the first output bit (MSB) of the E1 byte.<br>When a high signal is clocked out on RFPO, the MSB of E1 is simultaneously clocked out on RSDO.                                                                                                                                                                                                                                                                           |

### serial-transmit data-communications interface

| TERMINAL |     | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------|-----|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME N   | NO. | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| TSDI     |     | Ι   | Transmit serial-data input. When TDEN is high at the time that the first bit of a given byte is to be input, all eight bits of that byte are input serially on TSDI. Bytes are read in the following order: E1, D1 – D12, and E2. The MSB of each byte is input first. Data is clocked into the device on the rising edge of TCO. TFPO goes high to identify the subsequent input of the first bit (MSB) of E1. The remaining seven bits of E1 and the 13 other data-communications and orderwire bytes are then input on consecutive clock cycles, provided TDEN is high for the MSB of each byte. |

| TDEN     |     | -   | Transmit data-communications enable. If TDEN is low when the MSB of a given byte is to be input, the TNETA1600 does not read that byte on TSDI. If TDEN is high when the MSB of a given byte is to be input, all eight bits of that byte are read on contiguous clock cycles. TDEN is examined for the MSB of E1 on the first rising edge of TCO, following the rising edge that clocks out a high signal on TFPO.                                                                                                                                                                                  |

| тсо      |     | 0   | Transmit clock output. TSDI is clocked in and TFPO is valid on the rising edge of TCO. TCO is a continuous 1.215-MHz clock signal. However, the data is input in a burst, such that traffic is not always present on the interface.                                                                                                                                                                                                                                                                                                                                                                 |

| TFPO     |     | 0   | Transmit framing-pulse output. TFPO identifies the subsequent input of the first bit (MSB) of the E1 byte.<br>When a high signal is clocked out on TFPO, the MSB of E1 is clocked in on the next rising edge of TCO,<br>provided TDEN is high. TFPO is valid on the rising edge of TCO.                                                                                                                                                                                                                                                                                                             |

SDNS036 – FEBRUARY 1996

# **Terminal Functions (Continued)**

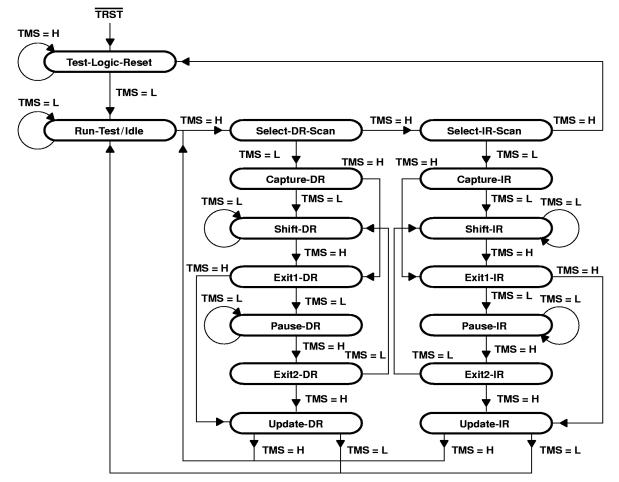

### JTAG test access port

| TERMINAL | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME NO. |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

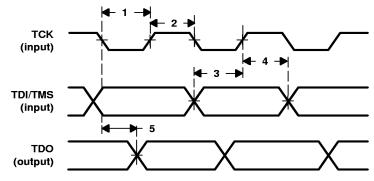

| тск      | I   | Test clock. TCK is one of four terminals required by IEEE Standard 1149.1. TCK samples data on TDI,<br>outputs data on TDO, and clocks the test-access-port (TAP) controller. Data on the device inputs is captured<br>on the rising edge of TCK, and outputs change on the falling edge of TCK.                                                                                                                                                  |

| וסד      | I   | Test-data input. TDI is one of four terminals required by IEEE Standard 1149.1. TDI is the serial input for<br>shifting information into the instruction register or selected data register. TDI is captured on the rising edge<br>of TCK.                                                                                                                                                                                                        |

| TDO      | 0   | Test-data output. TDO is one of four terminals required by IEEE standard 1149.1. TDO is the serial output for shifting information out of the instruction register or selected data register. TDO is updated on the falling edge of TCK.                                                                                                                                                                                                          |

| тмѕ      | I   | Test-mode select. TMS is one of four terminals required by IEEE Standard 11.49.1. TMS directs the TAP controller through its states. TMS is captured on the rising edge of TCK.                                                                                                                                                                                                                                                                   |

| TRST     | I   | Test reset. TRST is the <u>active</u> -low input that implements the optional reset terminal of IEEE Standard 1149.1.<br>When asserted (low), TRST causes the TAP controller to asynchronously enter the test-logic-reset <u>state</u><br>and configure the instruction register and test data registers to their default values. A high-level on TRST<br>allows normal TAP controller operation. TRST should be held low during device power up. |

# miscellaneous signals<sup>†</sup>

| TERMIN             | TERMINAL |     | DECODIDETON                                                                       |

|--------------------|----------|-----|-----------------------------------------------------------------------------------|

| NAME               | NO.      | I/O | DESCRIPTION                                                                       |

| GND                |          |     | Ground. GND1 is the 0-V reference for TTL circuits.                               |

| Vcc                |          |     | Supply voltage. V <sub>CC1</sub> is the 5 V $\pm$ 5% supply for the TTL circuits. |

| RXREF8K            |          | 0   | Receive-side 8-kHz reference. Pulse duration is approximately 450 ns.             |

| TXREF8K            |          | 0   | Transmit-side 8-kHz reference. Pulse duration is approximately 450 ns.            |

| NC                 |          |     | No connection. These terminals are left open.                                     |

| TESTO <sup>†</sup> |          | I   | Test mode 0. TEST0 activates the short-frame test mode.                           |

| TEST1 <sup>†</sup> |          | 1   | Test mode 1. TEST1 disables the TX SONET scrambler.                               |

| TEST2 <sup>†</sup> |          | 1   | Test mode 2. TEST2 disables the RX SONET descrambler.                             |

| TEST3 <sup>†</sup> |          | 1   | Test mode 3. TEST3 disables the TX ATM cell scrambler.                            |

| TEST4 <sup>†</sup> |          | 1   | Test mode 4. TEST4 disables the RX ATM cell descrambler.                          |

| TEST5 <sup>†</sup> |          | 1   | Test mode 5. TEST5 activates the UTOPIA loopback mode.                            |

<sup>†</sup> All test mode inputs are mirrored by bits in the control registers. A logical OR function provides the resulting control signal. For example, the TX SONET scrambler is disabled when a high-level signal is applied to TEST1 terminal or when the associated control register bit is set high for the TX SONET scrambler.

### detailed description

### transmit operation

The TNETA1600 operates at either 155.52 Mbit/s or 622.08 Mbit/s. The choice of operation is made through the EN155 input. When the device is programmed to operate at 155.52 Mbit/s, the device transmits a STS-3c/STM-1 frame. When the device is programmed to operate at 622.08 Mbit/s, the device transmits a STS-12c/STM-4c frame. Both the STS-3c/STM-1 and STS-12c/STM-4c outputs are byte wide.

### transmit-cell interface

The transmit-cell interface consists of an 8-/16-bit-wide input data (TD0-TD15), input clock (TCKI), start of ATM cell input (TXSOC), transmit write-enable input (TWE), and transmit cell-available output (TXCLAV). Input data is clocked into the TNETA1600 on low-to-high transitions of TCKI when TWE is low. TXCLAV goes active when the transmit input FIFO is capable of accepting the transfer of a complete ATM cell. TXCLAV goes inactive when the transmit input FIFO is within four write cycles (four bytes during 155.52-Mbit/s operation or eight bytes during 622.08-Mbit/s operation) of being full. The FIFO holds three complete ATM cells. The reception of a high signal on TXSOC indicates the first byte (or first two bytes in a 16-bit cell interface) of an ATM cell. Once the input FIFO receives a high TXSOC signal indicating the start of an ATM cell, the interface ignores subsequent TXSOC indications until each byte of the incoming ATM cell is received. Receiving a TXSOC indication in the middle of a cell does not reset the input-byte counters and the device groups the first 53 bytes (54 bytes for 622-Mbit/s operation) received after the initial TXSOC indication into a single ATM cell. The transmit-cell interface is fully synchronous. All signals associated with the interface are either sampled or valid on the rising edge of TCKI. The design goal for the interface is to operate at frequencies up to 50 MHz over worst-case supply voltage, process control, and temperature. The data input on the transmit-cell interface is 16 bits wide for 622.08-Mbit/s operation and 8 bits wide for 155.52-Mbit/s operation. The width of the datapath is set when the user chooses either 155.52-Mbit/s or 622.08-Mbit/s operation through the EN155 input. For the 16-bit data input, the device can be configured to accept data in two different input formats. For the first format, data is input as 54 bytes per ATM cell with two user-defined bytes (UDBs) separating the four bytes of the ATM header from the cell payload. The second format has one UDB separating the four bytes of the ATM header from the cell payload and a second UDB at the end of the cell payload. These two formats are illustrated in Figure 1. In each format, the second UBD is discarded so that the 53-byte ATM cell can be mapped into a SONET/SDH frame. The selection of the data format is made via the control register, which is accessible through the controller interface. When a hardware or software reset occurs, the device is set to accept format 1. For the 8-bit data interface, data is input as a 53-byte ATM cell with one UDB separating the four bytes of the ATM header from the 48-byte cell payload.

| - | - | - | - | - |   |   |   |   |   |   | - |   | _ | _  |    |   | Ĩ |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|----|----|---|---|

|   |   |   |   |   | F | • | C | R | R | Л | A | Т | ľ | 10 | Э. | 1 | I |

| MSB BITS 15         | LSB BIT 0           |

|---------------------|---------------------|

| Header Byte No. 1   | Header Byte No. 2   |

| Header Byte No. 3   | Header Byte No. 4   |

| UDB No. 1           | UDB No. 2           |

| Payload Byte No. 1  | Payload Byte No. 2  |

| :                   | :                   |

| :                   | :                   |

| Payload Byte No. 47 | Payload Byte No. 48 |

| FORMAT | NO. 2 |

|--------|-------|

|--------|-------|

| MSB BIT 15          | LSB BIT 0          |

|---------------------|--------------------|

| Header Byte No. 1   | Header Byte No. 2  |

| Header Byte No. 3   | Header Byte No. 4  |

| UDB No. 1           | Payload Byte No. 1 |

| Payload Byte No. 2  | Payload Byte No. 3 |

| :                   | :                  |

| :                   | :                  |

| Payload Byte No. 48 | UDB No. 2          |

Figure 1. Transmit-Cell Interface Formats for 16-Bit Input Data

SDNS036 - FEBRUARY 1996

### transmit-cell interface (continued)

The 48-byte information field of the ATM cell is scrambled using a self-synchronizing scrambler polynomial of  $x^{43} + 1$  to improve the efficiency of the cell-delineation procedure. At startup, the scrambler is initialized to an all-ones state. The 5-byte ATM header is not scrambled. TXSOC identifies the first byte of the ATM cell and disables the scrambler. The input data is stored in the transmit input FIFO and multiplexer into the SONET payload after all 53 bytes of the ATM cell are received. If the FIFO does not contain 53 bytes of information at the start of a cell-insertion cycle, an idle or unassigned cell is sent depending upon the configuration of the control register. An idle cell is defined as an ATM cell with the 5-byte header set to 00 00 00 1 52 (hex) and all 48 bytes of the payload set to a hex value of 6A.

The transmit section is initialized on reset to calculate the header-error-check (HEC) byte in the ATM header. When this feature is active, the fifth byte of the ATM cell that is input through the transmit-cell interface is ignored. The HEC byte is calculated in accordance with the appropriate ANSI, CCITT, and ATM Forum specifications and placed in the fifth byte of the ATM cell. This feature can be disabled for test purposes by setting a bit in the control register.

### transmit overhead

The transmit operation can be controlled to send either a SONET frame or an SDH frame. When both SDHEN and the enable SDH frames bit in the control register are low, a SONET frame is transmitted. When either SDHEN or the enable SDH frames bit (or both) are high, an SDH frame is transmitted. A valid clock must be present at TPCK when the framing mode is changed, as this clock is used to change the overhead-RAM contents. Because overhead contents are altered, toggling the mode during operation can result in the loss of transmit-frame alignment and loss of any data being processed in the TNETA1600 transmitter. A hardware or software reset also causes the overhead RAM to be rewritten with SONET or SDH values, depending on the status of SDHEN.

For both SONET and SDH transmitted frames, the location of the J1 byte in the path overhead is fixed. The J1 byte always comes after the last C1 byte of the transport overhead. This results in a fixed value for the first H1 byte of 0110 0010 for SONET frames or 0110 1010 for SDH frames. The first H2 byte has a fixed value of 0000 1010 (10 0000 1010 binary is equal to 522 decimal) for both SONET and SDH frames. The H3 bytes are set to zero. The transport- and path-overhead bytes are multiplexed into the output-byte stream from the transmit-overhead RAM. All transmit-overhead bytes with values that must be calculated by the TNETA1600 are placed in the transmit-overhead RAM prior to being added to the output data stream. The user has access to the transmit-overhead RAM through the controller interface and can preset the values of many overhead bytes. The user can also insert the D1–D12, E1, and E2 bytes into the transmit-data stream through the serial transmit data-communications port.

The values of the transmit-overhead bytes are initialized at reset or upon a framing-mode change (SONET/SDH) to the values given in Table 1. Overhead bytes not shown in the table are initialized to all zeroes (0000 0000). Although the user can program the value of any overhead byte by writing to the transmit-overhead RAM, several of the values will be automatically overwritten by the TNETA1600. This overwrite occurs after the first row's overhead is transmitted (e.g., after J1 at 155.52 Mbit/s). Table 1 denotes the bytes to which this applies. For example, the B2-byte values are calculated by the TNETA1600 and written into RAM regardless of whether or not a value was written to B2 via the controller interface. These automatic write operations by the TNETA1600 are disabled when the transmit-overhead RAM is placed in program mode (accomplished by setting a bit in the control register or by taking the interface programming mode (IFPRGM) input high). While in the program mode, overhead values can be written into the TNETA1600 via the controller interface. Since no values are automatically overwritten, this gives the user the capability to transmit any value in any overhead-byte location. Specified bytes are automatically overwritten when the program mode is exited.

SDNS036 - FEBRUARY 1996

| OVERHEAD<br>BYTE        | SONET-FRAME<br>VALUE INITIALIZED AT RESET<br>OR FRAME-MODE CHANGE          | SDH-FRAME<br>VALUE INITIALIZED AT RESET<br>OR FRAME-MODE CHANGE            | VALUE<br>OVER-<br>WRITTEN<br>EACH<br>FRAME? |

|-------------------------|----------------------------------------------------------------------------|----------------------------------------------------------------------------|---------------------------------------------|

| A1                      | 1111 0110 (F6 hex)                                                         | 1111 0110 (F6 hex)                                                         | Y                                           |

| A2                      | 0010 1000 (28 hex)                                                         | 0010 1000 (28 hex)                                                         | Y                                           |

| C1/1                    | 0000 0001                                                                  | 0000 0001                                                                  | N                                           |

| C1/2                    | 0000 0010                                                                  | 0000 0010 (0000 0000 for 155.52-Mbit/s mode)                               | N                                           |

| C1/3                    | 0000 0011                                                                  | 0000 0011 (0000 0000 for 155.52-Mbit/s mode)                               | N                                           |

| C1/4 <sup>†</sup>       | 0000 0100                                                                  | 0000 0000                                                                  | N                                           |

| C1/5 <sup>†</sup>       | 0000 0101                                                                  | 0000 0000                                                                  | N                                           |

| C1/6 <sup>†</sup>       | 0000 0110                                                                  | 0000 0000                                                                  | N                                           |

| C1/7†                   | 0000 0111                                                                  | 0000 0000                                                                  | N                                           |

| C1/8 <sup>†</sup>       | 0000 1000                                                                  | 0000 0000                                                                  | N                                           |

| C1/9†                   | 0000 1001                                                                  | 0000 0000                                                                  | N                                           |

| C1/10 <sup>†</sup>      | 0000 1010                                                                  | 0000 0000                                                                  | N                                           |

| C1/11 <sup>†</sup>      | 0000 1011                                                                  | 0000 0000                                                                  | N                                           |

| C1/12 <sup>†</sup>      | 0000 1100                                                                  | 0000 0000                                                                  | N                                           |

| B1                      | Calculated from previous frame                                             | Calculated from previous frame                                             | Y                                           |

| E1                      | 0111 1111                                                                  | 0111 1111                                                                  | N                                           |

| F1                      | 0000 0000                                                                  | 0000 0000                                                                  | N                                           |

| D1–D3                   | 0111 1111                                                                  | 0111 1111                                                                  | N                                           |

| First H1                | Normal operation: 0110 0010<br>Path AIS: 1111 1111‡                        | Normal operation: 0110 1010<br>Path AIS: 1111 1111‡                        | Y                                           |

| H1                      | Normal operation: 1001 0011<br>Path AIS: 1111 1111‡                        | Normal operation: 1001 1011<br>Path AIS: 1111 1111‡                        | N                                           |

| First H2                | Normal operation: 0000 1010<br>Path AIS: 1111 1111 <sup>‡</sup>            | Normal operation: 0000 1010<br>Path AIS: 1111 1111 <sup>‡</sup>            | Y                                           |

| H2                      | Normal operation: 1111 1111<br>Path AIS: 1111 1111‡                        | Normal operation: 1111 1111<br>Path AIS: 1111 1111‡                        | N                                           |

| H3                      | Normal operation: 0000 0000<br>Path AIS: 1111 1111‡                        | Normal operation: 0000 0000<br>Path AIS: 1111 1111 <sup>‡</sup>            | N                                           |

| B2                      | Calculated from previous frame                                             | Calculated from previous frame                                             | Y                                           |

| K1                      | 0000 0000                                                                  | 0000 0000                                                                  | N                                           |

| First K2                | Normal operation: 0000 0000<br>Line AIS: 1111 1111<br>Line FERF: 0000 0110 | Normal operation: 0000 0000<br>Line AIS: 1111 1111<br>Line FERF: 0000 0110 | Bits 1–5: N<br>Bits 6–8: Y§                 |

| D4-D12                  | 0111 1111                                                                  | 0111 1111                                                                  | N                                           |

| Z1/1-Z1/3               | 0000 0000                                                                  | 0000 0000                                                                  | N                                           |

| Z1/4-Z1/12 <sup>†</sup> | 0000 0000                                                                  | 0000 0000                                                                  | N                                           |

| Third Z2                | B2 error count; range of legal values for Z2 is:<br>0000 0000 – 0110 0000  | B2 error count; range of legal values for Z2 is:<br>0000 0000 – 0110 0000  | Y                                           |

| E2                      | 0111 1111                                                                  | 0111 1111                                                                  | N                                           |

### Table 1. Transmit Overhead

<sup>†</sup> These bytes are used only in 622.08-Mbit/s applications.

<sup>‡</sup> For the transmission of a line AIS or path AIS, an all-ones pattern is put in the data stream in place of certain overhead bytes. The all-ones pattern is not, however, written to or reflected in the transmit-overhead RAM. Upon deactivation of the AIS condition, the original values (still in the RAM) are returned to the data stream.

§ For the transmission of a line FERF, a 110 is put in the data stream in place of bits 6–8 of the K2 byte. These values are not, however, written to or reflected in the transmit-overhead RAM. Upon deactivation of the line FERF condition, the original values (still in the RAM) are returned to the data stream.

SDNS036 – FEBRUARY 1996

| OVERHEAD<br>BYTE           | SONET-FRAME<br>VALUE INITIALIZED AT RESET<br>OR FRAME-MODE CHANGE                              | SDH-FRAME<br>VALUE INITIALIZED AT RESET<br>OR FRAME-MODE CHANGE                               | VALUE<br>OVER<br>WRITTEN<br>EACH<br>FRAME? |

|----------------------------|------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|--------------------------------------------|

| J1 (64 bytes)              | Default value: 0000 0000<br>J1 can be modified via controller interface.                       | Default value: 0000 0000<br>J1 can be modified via controller interface.                      | Ν                                          |

| B3                         | Calculated from previous SPE                                                                   | Calculated from previous SPE                                                                  | Y                                          |

| C2                         | 0001 0011                                                                                      | 0001 0011                                                                                     | Y                                          |

| G1 bits 1–4<br>G1 bits 5–6 | B3 error count ( 0000 – 1000); Path FERF: 1001<br>PRDI: 01 PLM; 10 PAIS, LOP, LOCA;<br>11 UNEQ | B3 error count (0000 – 1000); Path FERF: 1001<br>PRDI: 01 PLM; 10 PAIS, LOP, LOCA;<br>11 UNEQ | Y                                          |

| G1 bits 7–8                | 00                                                                                             | 00                                                                                            |                                            |

### Table 1. Transmit Overhead (Continued)

Calculation of parity bytes B1, B2 (twelve bytes), and B3 are as follows:

- B1. B1 is a bit-interleaved parity 8 (BIP-8) code using even parity. B1 is calculated over all bits of the

previous frame after scrambling. The calculated value of B1 is placed in the frame before the frame is

scrambled.