# 捷多邦,专业PCB打样工厂,24小时加急出货NETA1561 ATM SEGMENTATION AND REASSEMBLY DEVICE WITH PCI HOST INTERFACE

SDNS028D - OCTOBER 1994 - REVISED JANUARY 1998

- Peripheral Component Interconnect (PCI) **Device That Provides Asynchronous** Transfer-Mode (ATM) Interface

- Single-Chip Segmentation and Reassembly (SAR) for Full-Duplex ATM Adaptation-Layer (AAL) Processing

- On-Chip PCI Host Interface Allows Use of **Host Memory for Packet SAR**

- 53-Byte ATM Cells Are Transparent to the

- **Provides Complete Encapsulation and** Termination of AAL5 and Limited AAL3/4

- Features a Null AAL That Provides Functions for Constant-Bit-Rate Services

- **Supports 1023 Unique Virtual Circuits** (VCs) on Receive Side

- **Explicit Cell-Level Interleaving Between Groups of VCs**

- Packet Interface Is Managed by Efficient **Descriptor Rings**

- Physical (PHY)-Layer Interface Is Full **Duplex and Compliant to the ATM Forum UTOPIA Contribution**

- Supports PHY-Layer Data Rates in the Range of 25.6 Mbit/s to 155.52 Mbit/s

- Interfaces Directly to the TNETA1500 SONET ATM BICMOS Receiver/Transmitter (SABRE)

- **Recognizes ATM-Layer Operation and** Maintenance (OAM) Cells

- No External Logic Required for Host or Local Buses to Ensure Simple Design

- Supports an External EPROM for System **Configuration Code**

- Packaged in 240-Pin Plastic Quad Flatpack

### description

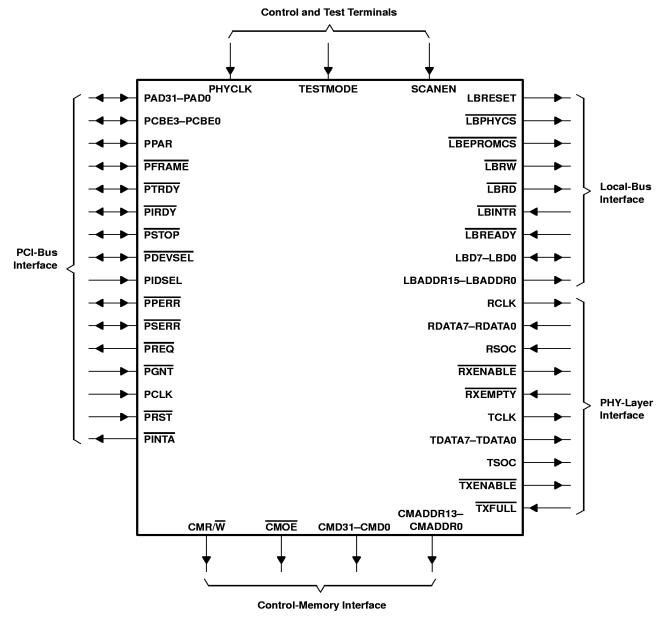

The TNETA1561 (PCI SAR) is an asynchronous transfer mode (ATM) segmentation and reassembly (SAR) device with a peripheral component interconnect (PCI)-bus interface. This device incorporates ATM adaptation-layer (AAL) processing, ATM SAR processing for full-duplex operation up to STS-3c rate of 155.52 Mbit/s, and the controls for the register interface on the physical (PHY) layer. The TNETA1561 provides a packet interface that is managed by descriptor rings, making the 53-byte ATM-framing format transparent to the user. The device passes the payload of 48 bytes, constituting the payload of each cell, across the PCI-host interface. All packets are segmented and reassembled in host memory and accessed by the chip via the descriptor-ring mechanism. The device reduces the memory requirements for network-interface cards (NICs). The TNETA1561 requires no local processor on the card, which enables very compact solutions.

The applications for the TNETA1561 include NICs for client workstations and servers, embedded applications like LAN emulation, and multiprotocol systems like video servers. The TNETA1561 provides complete AAL5 encapsulation and termination in hardware. In addition, limited support is provided for AAL 3/4 and a null AAL is provided to facilitate real-time data transfer. The TNETA1561 recognizes ATM-layer operation and maintenance (OAM) cells.

In the transmit direction, the TNETA1561 generates data via a special bit-rate control table that provides explicit cell-level interleaving between groups of virtual circuits (VCs). This mechanism brings a higher degree of flexibility when specifying peak rates for each group (up to 155.52 Mbit/s at a resolution greater than 32 kbit/s). The VCs within a group are serviced via a first-in, first-out (FIFO) discipline on a per-packet basis.

In the receive direction, the TNETA1561 allows multiple virtual paths (VPs) with the condition that each VC is unique. The device is primarily intended for AAL5 encapsulation and termination that is supported in hardware.

The TNETA1561 has four interfaces that include the following: the PCI-bus interface with a 32-bit-wide data bus, the cell interface based on the universal test and operations interface for ATM (UTOPIA specification), a control-memory interface to access the local SRAM, and the local-bus interface to access the PHY-layer registers. The UTOPIA interface to the PHY layer consists of an 8-bit-wide datapath and associated control signals in both the transmit and receive directions. The 53-byte ATM cells pass between the ATM and PHY layers through the UTOPIA interface.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

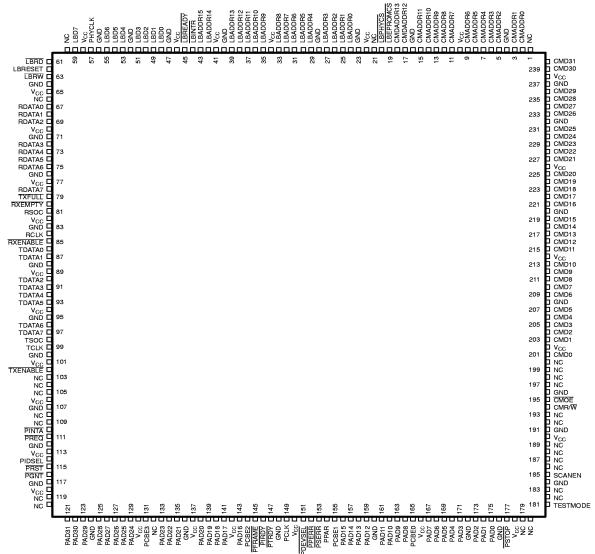

#### PGC PACKAGE (TOP VIEW)

#### NC - No internal connection

#### description (continued)

The native clock for the TNETA1561 is the PCI clock, which operates up to 33 MHz. The native-word size for the device is 32 bits, corresponding to the data width for the PCI bus. The TNETA1561 host interface implements the bus protocol defined in the PCI local-bus specification (revision 2.0). The control-memory interface is 32 bits wide. This interface allows the device to access the local memory to obtain the control information on the packets being segmented and reassembled and to obtain their locations in host memory. Each packet queued for transmission can be distributed across multiple buffers in host memory, with each starting at any byte boundary. This is supported in hardware by the device. Every received package is placed in a single buffer in the host memory and is aligned to a 16-byte boundary. The TNETA1561 operation is explained in detail in the *Principles of Operation* section.

# **TNETA1561** ATM SEGMENTATION AND REASSEMBLY DEVICE WITH PCI HOST INTERFACE SDNS028D - OCTOBER 1994 - REVISED JANUARY 1998

### **Terminal Functions**

# **PCI-bus interface**

| TERMINA     | AL                                                                                                          | 1/0                    | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|-------------|-------------------------------------------------------------------------------------------------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME        | NO.                                                                                                         | 1/0                    | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| PINTA       | 110                                                                                                         | O<br>(open<br>drain)   | PCI interrupt. PINTA is an interrupt request from PCI SAR.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| PAD31–PAD0  | 121–123,<br>125–129,<br>133–135,<br>138–141,<br>143,<br>156–159,<br>161–164,<br>167–170,<br>171,<br>173–175 | I/O<br>(3 state)       | PCI address bus and data bus. PAD31–PAD0 are multiplexed on the same PCI terminals. During the first phase of a transaction (address phase), PAD31–PAD0 contains a 32-bit physical address. This phase is the clock cycle when PFRAME is asserted.  During the data phase, PAD7–PAD0 contain the least significant byte and PAD31–PAD24 contain the most significant byte. Write data is stable when PIRDY is asserted. Read data is stable when PTRDY is asserted. Data is transferred during those clock cycles when both PIRDY and PTRDY are asserted. |  |  |  |

| PCBE3-PCBE0 | 131, 144,<br>155, 165                                                                                       | I/O<br>(3 state)       | PCI-bus command and byte enable. PCBE3-PCBE0 lines are multiplexed on the same PCI terminals. During the address phase of a transaction, PCBE3-PCBE0 lines define the bus command. During the data phase, PCBE3-PCBE0 lines define which bytes are valid.                                                                                                                                                                                                                                                                                                 |  |  |  |

| PCLK        | 149                                                                                                         | I                      | PCI clock. PCLK provides timing for all transactions on PCI.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| PDEVSEL     | 151                                                                                                         | I/O<br>(3 state)       | PCI device select. PDEVSEL, when actively driven, indicates that the driving device has decoded its address as the target of the current access. As an input, PDEVSEL indicates whether any device on the bus is selected.                                                                                                                                                                                                                                                                                                                                |  |  |  |

| PFRAME      | 145                                                                                                         | I/O<br>(3 state)       | PCI frame. PFRAME is driven by the current master to indicate the beginning and duration of an access. PFRAME is asserted at the beginning of the bus transaction and remains asserted during data transfer. When PFRAME is deasserted, the transaction is in the final data phase.                                                                                                                                                                                                                                                                       |  |  |  |

| PGNT        | 116                                                                                                         | I                      | PCI bus grant. PGNT indicates to the agent that the arbiter has granted access to the bus. PGNT is a point-to-point signal and every master has its own.                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| PIDSEL      | 114                                                                                                         | I                      | PCI initialization and device select. PIDSEL is used as a chip select during configuration read and write transactions.                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| PIRDY       | 146                                                                                                         | I/O<br>(3 state)       | PCI initiator ready. PIRDY indicates the initiating agent's (bus master) ability to complete the current data phase of the transaction. During a write, PIRDY indicates valid data on PAD31-PAD0. During a read, PIRDY indicates that the master is prepared to accept the data. PIRDY is used with PTRDY when wait cycles are inserted until both PIRDY and PTRDY are asserted.                                                                                                                                                                          |  |  |  |

| PPAR        | 154                                                                                                         | I/O<br>(3 state)       | PCI parity. PPAR is even across PAD31-PAD0 and PCBE3-PCBE0. For data phases, PPAR is valid one clock after either PIRDY is asserted on a write or PTRDY is asserted on a read. Once asserted, PPAR remains valid until one clock after the completion of the current data phase. The master drives the PPAR for the address and write-data phases. The target drives PPAR for the read-data phase.                                                                                                                                                        |  |  |  |

| PPERR       | 152                                                                                                         | I/O<br>(3 state)       | PCI parity error. PPERR reports a data-parity error on all commands except special cycle. An agent cannot report a PPERR until it has claimed the access by PDEVSEL and completed a data phase.                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| PREQ        | 111                                                                                                         | 0                      | PCI request. PREQ indicates to the arbiter that this agent desires use of the bus. Every master has its own PREQ.                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| PRST        | 115                                                                                                         | I                      | PCI reset. PRST forces the PCI sequence of each device to a known state.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| PSERR       | 153                                                                                                         | I/O<br>(open<br>drain) | PCI system error. PSERR reports address-parity errors and data-parity errors on special-cycle commands.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| PSTOP       | 177                                                                                                         | I/O<br>(3 state)       | PCI stop. PSTOP indicates the current target is requesting the master to stop the current transaction.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| PTRDY       | 147                                                                                                         | I/O<br>(3 state)       | PCI target ready. PTRDY indicates the target agent's (selected device) ability to complete the current data phase of the transaction. During a read, PTRDY indicates that valid data is present on PAD31–PAD0. During a write, PTRDY indicates that the target is prepared to accept data.                                                                                                                                                                                                                                                                |  |  |  |

# **TNETA1561** ATM SEGMENTATION AND REASSEMBLY DEVICE WITH PCI HOST INTERFACE SDNS028D - OCTOBER 1994 - REVISED JANUARY 1998

# **Terminal Functions (Continued)**

### PCI SAR and local-bus interface

| TERMINAL         |                        | I/O | DESCRIPTION                                                                                                                                                                                                                   |  |  |  |

|------------------|------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME             | NO.                    | 1/0 | DESCRIPTION                                                                                                                                                                                                                   |  |  |  |

| LBRESET          | 62                     | 0   | cal-bus reset. LBRESET is an active-high signal that is driven by the PCI SAR.                                                                                                                                                |  |  |  |

| <b>LBPHYCS</b>   | 20                     | 0   | Local-bus PHY-layer chip select. LBPHYCS is used to interface with PHY-layer devices and is driven by PCI SAR.                                                                                                                |  |  |  |

| LBEPROMCS        | 19                     | 0   | Local-bus EPROM chip select. LBEPROMCS is an active-low signal that is driven by PCI SAR.                                                                                                                                     |  |  |  |

| LBRW             | 63                     | 0   | Local-bus write. LBRW is an active-low write signal that indicates a write operation and is driven by PCI SAR.                                                                                                                |  |  |  |

| LBRD             | 61                     | 0   | Local-bus read. LBRD is an active-low read signal that indicates a read operation and is do by PCI SAR.                                                                                                                       |  |  |  |

| LBINTR           | 44                     | 1   | Local-bus interrupt. LBINTR is generated and driven by a local-bus device.                                                                                                                                                    |  |  |  |

| LBREADY          | 45                     | I   | Local-bus ready. LBREADY is driven by local-slave devices. The bus transaction is completed after eight PCI bus cycles, regardless of LBREADY. LBREADY is accepted by the SAR as a handshake from the devices on the bus.     |  |  |  |

| LBD7-LBD0        | 59,<br>55–53,<br>51–48 | 1/0 | Local-bus data. LBD7-LBD0 are used to transfer data to and from local-slave devices and are driven by PCI SAR or local-slave devices.                                                                                         |  |  |  |

| LBADDR15-LBADDR0 | 30_35                  |     | Local-bus address. LBADDR15-LBADDR0 are driven by the PCI SAR and are used to address the PHY-layer registers and the EPROM. LBADDR15-LBADDR2 are received from the PCI bus and LBADDR1-LBADDR0 are generated by the PCI SAR. |  |  |  |

# PHY-layer receive interface

| TERMINAL      |                        | 1/0 | DECORIDEION                                                                                                                                         |  |  |  |

|---------------|------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME          | NO.                    | I/O | DESCRIPTION                                                                                                                                         |  |  |  |

| RCLK          | 84                     | 0   | Receive clock. RCLK is equivalent to the internal clock at 19.44 MHz. RCLK is sent to the PHY layer.                                                |  |  |  |

| RDATA7-RDATA0 | 78,<br>75–72,<br>69–67 | I   | Receive data. RDATA7-RDATA0 are connected to the PHY-layer receive interface and are driven by the PHY-layer device.                                |  |  |  |

| RSOC          | 81                     | ı   | Receive start of cell. RSOC is a signal from the PHY layer indicating that the first byte of an ATM cell was sent to the TNETA1561.                 |  |  |  |

| RXEMPTY       | 80                     | I   | Receive buffer empty in the PHY layer. RXEMPTY is a signal that acts as an inverted enable signal on this interface and is driven by the PHY layer. |  |  |  |

| RXENABLE      | 85                     | 0   | Receive enable. RXENABLE is active low and is driven by the TNETA1561.                                                                              |  |  |  |

# **TNETA1561** ATM SEGMENTATION AND REASSEMBLY DEVICE WITH PCI HOST INTERFACE SDNS028D - OCTOBER 1994 - REVISED JANUARY 1998

# **Terminal Functions (Continued)**

# PHY-layer transmit interface

| TERMINAL      |                           | I/O | DESCRIPTION                                                                                                                                                                                          |

|---------------|---------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME          | NO.                       | 1/0 | DESCRIPTION                                                                                                                                                                                          |

| TCLK          | 99                        | 0   | Transmit clock. The TNETA1561 generates TCLK at the PCI-clock frequency and sends it to the PHY layer. TCLK is an inverted version of the internal clock.                                            |

| TDATA7-TDATA0 | 97–96,<br>93–90,<br>87–86 | 0   | Transmit data. TDATA7-TDATA0 are sent at the rate of the PCI clock and are driven by the TNETA1561.                                                                                                  |

| TSOC          | 98                        | 0   | Transmit start of cell. TSOC is sent by the PCI SAR to the PHY layer and indicates that the first byte of an ATM cell was transmitted to the PHY layer.                                              |

| TXENABLE      | 102                       | 0   | Transmit enable. The SAR turns off TXENABLE when the PHY layer sends the TXFULL signal.                                                                                                              |

| TXFULL        | 79                        | ı   | Transmit buffer full in the PHY layer. The PHY layer asserts TXFULL at least four cycles before any internal buffers are full. This makes the TNETA1561 stop the data transmission to the PHY layer. |

# PCI SAR and control-memory interface

| TERMINAL         |                                                                                         |     |                                                                                                                                                                                                                                    |  |  |  |

|------------------|-----------------------------------------------------------------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME             | NO.                                                                                     | I/O | DESCRIPTION                                                                                                                                                                                                                        |  |  |  |

| CMADDR13-CMADDR0 | 18–17,<br>15–11,<br>9–5,<br>3–2                                                         | 0   | Control-memory address. CMADDR13-CMADDR0 is a 14-bit address bus and is driven by the PCI SAR.                                                                                                                                     |  |  |  |

| CMD31-CMD0       | 240–239,<br>236–233,<br>231–227,<br>225–221,<br>219–215,<br>213–209,<br>207–203,<br>201 | I/O | Control-memory data. The control-memory interface has a 32-bit data bus. CMD31-CMD0 are designed for 20-ns asynchronous SRAMs. The TNETA1561 uses this interface to access the data structures and pointers in the control memory. |  |  |  |

| CMOE             | 195                                                                                     | 0   | Control-memory output enable. CMOE is an active-low signal and is driven by the PCI SAR.                                                                                                                                           |  |  |  |

| CMR/W            | 194                                                                                     | 0   | Control-memory read/write. CMR/W determines a read or write operation. If the output is low, it is a write operation. If the output is high, it is a read operation. CMR/W is driven by the PCI SAR.                               |  |  |  |

# **TNETA1561** ATM SEGMENTATION AND REASSEMBLY DEVICE WITH PCI HOST INTERFACE SDNS028D - OCTOBER 1994 - REVISED JANUARY 1998

# **Terminal Functions (Continued)**

# PCI SAR and test/control interface

|          | TERMINAL                                                                                                 | I/O | DESCRIPTION                                                                              |  |  |

|----------|----------------------------------------------------------------------------------------------------------|-----|------------------------------------------------------------------------------------------|--|--|

| NAME     | NO.                                                                                                      | 1/0 | DESCRIPTION                                                                              |  |  |

| NC       | 1, 21, 60, 66, 103–105, 108,<br>109, 119, 120, 132, 179,<br>180, 182, 183, 186–189,<br>192, 193, 197–200 | 0   | No connection. Leave open.                                                               |  |  |

| PHYCLK   | 57                                                                                                       | I   | PHY-layer clock. PHYCLK is a 19.44-MHz clock signal driven by a PHY-layer clock crystal. |  |  |

| SCANEN   | 185                                                                                                      | I   | SCAN enable. Connect to ground for normal operation.                                     |  |  |

| TESTMODE | 181                                                                                                      | ı   | Test mode. TESTMODE is driven by the test system. Leave grounded for normal operation.   |  |  |

# power and ground

|      | TERMINAL                                                                                                                                   | DESCRIPTION    |  |  |  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------|----------------|--|--|--|

| NAME | NO.                                                                                                                                        | DESCRIPTION    |  |  |  |

| GND  | 4, 16, 23, 28, 40, 47, 52, 56, 64, 71, 76, 83, 88, 95, 100, 107, 112, 117, 124, 136, 148, 160, 172, 176, 184, 191, 196, 208, 220, 232, 237 | Ground         |  |  |  |

| vcc  | 10, 22, 34, 41, 46, 58, 65, 70, 77, 82, 89, 94, 101, 106, 113, 118, 130, 137, 142, 150, 166, 178, 190, 202, 214, 226, 238                  | Supply voltage |  |  |  |

SDNS028D - OCTOBER 1994 - REVISED JANUARY 1998

## absolute maximum ratings over operating free-air temperature range (unless otherwise noted)†

| Supply voltage range, V <sub>CC</sub> (see Note 1)                          |                                            |

|-----------------------------------------------------------------------------|--------------------------------------------|

| Input voltage range, V <sub>1</sub>                                         | 0.5 V to V <sub>CC</sub> + 0.5 V           |

| Output voltage range, V <sub>O</sub>                                        | $-0.5 \text{ V to V}_{CC} + 0.5 \text{ V}$ |

| Input clamp current, $I_{IK}$ ( $V_I < 0$ or $V_I > V_{CC}$ ) (see Note 2)  | ±20 mA                                     |

| Output clamp current, $I_{OK}$ ( $V_O < 0$ or $V_O > V_{CC}$ ) (see Note 3) | ±20 mA                                     |

| Operating free-air temperature range, T <sub>A</sub>                        | 0°C to 70°C                                |

| Storage temperature range, T <sub>stq</sub>                                 |                                            |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES: 1. All voltage values are with respect to the GND terminals.

- 2. Applies for external input and bidirectional buffers

- 3. Applies for external output and bidirectional buffers

# recommended operating conditions

|                 |                                |        |                          | MIN   | NOM | MAX  | UNIT |

|-----------------|--------------------------------|--------|--------------------------|-------|-----|------|------|

| Vcc             | Supply voltage                 |        |                          | 4.75  | 5   | 5.25 | V    |

|                 | High-level input voltage       |        | V <sub>CC</sub> = 4.75 V | 3.325 |     |      |      |

| V <sub>IH</sub> |                                |        | V <sub>CC</sub> = 5.25 V | 3.675 |     |      | ] v  |

|                 |                                | TTL    |                          | 2     |     |      |      |

|                 |                                | CMOS   | V <sub>CC</sub> = 4.75 V |       |     | 0.95 |      |

| V <sub>IL</sub> | Low-level input voltage        | CIVIOS | V <sub>CC</sub> = 5.25 V |       |     | 1.05 | V    |

|                 |                                | ΠL     |                          |       |     | 0.8  |      |

| TA              | Operating free-air temperature |        |                          | 0     |     | 70   | °C   |

# electrical characteristics over recommended operating conditions (unless otherwise noted), $T_A = 25^{\circ}C$

|                  | PARAMETER                           | TEST CONDITIONS                                           | MIN                  | TYP | MAX | UNIT |

|------------------|-------------------------------------|-----------------------------------------------------------|----------------------|-----|-----|------|

| Vall             | High-level output voltage           | I <sub>OH</sub> = 8 mA                                    | V <sub>CC</sub> -0.8 |     |     | V    |

| VOH              | nigri-level output voltage          | I <sub>OL</sub> = 4 mA                                    | V <sub>CC</sub> -0.8 |     |     | ٧    |

|                  | Law layel output valtage            | I <sub>OH</sub> = 8 mA                                    |                      |     | 0.5 | V    |

| VOL              | Low-level output voltage            | I <sub>OL</sub> = 4 mA                                    |                      |     | 0.5 | V    |

| loz              | High-impedance-state output current | V <sub>I</sub> = V <sub>CC</sub> or GND                   |                      |     | ±10 | μΑ   |

| ٦L               | Low-level input current             | V <sub>I</sub> = GND                                      |                      |     | -1  | μΑ   |

| ΊΗ               | High-level input current            | VI = VCC                                                  |                      |     | 1   | μА   |

| lcc <sup>‡</sup> | Supply current, dynamic             | $V_{CC} = 5 \text{ V}, \qquad f_{clock} = 33 \text{ MHz}$ |                      | 300 |     | mA   |

<sup>‡</sup> The supply-current (ICC) typical value is given for a full-duplex operation with fclock equal to 33 MHz.

SDNS028D - OCTOBER 1994 - REVISED JANUARY 1998

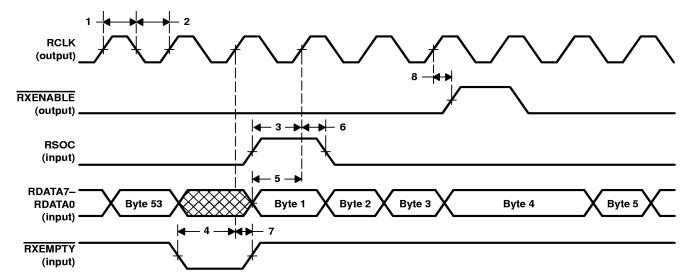

# timing requirements (see Note 4 and Figure 1)

| NO. |                          |                                              | MIN | MAX | UNIT |

|-----|--------------------------|----------------------------------------------|-----|-----|------|

| 1   | tw(RCLKH)                | Pulse duration, RCLK high                    | 12  |     | ns   |

| 2   | tw(RCLKL)                | Pulse duration, RCLK low                     | 12  |     | ns   |

| 3   | t <sub>su(RSOC)</sub>    | Setup time, RSOC high before RCLK↑           | 10  |     | ns   |

| 4   | t <sub>su(RXEMPTY)</sub> | Setup time, RXEMPTY low before RCLK↑         | 10  |     | ns   |

| 5   | t <sub>su(RDATA)</sub>   | Setup time, RDATA7–RDATA0 valid before RCLK↑ | 10  |     | ns   |

| 6   | th(RSOC)                 | Hold time, RSOC high after RCLK↑             | 1   |     | ns   |

| 7   | th(RXEMPTY)              | Hold time, RXEMPTY low after RCLK↑           | 1   |     | ns   |

NOTE 4: All output signals are generated on the rising edge of RCLK.

## operating characteristics (see Note 4 and Figure 1)

| NO. |                                               | MIN | MAX | UNIT |

|-----|-----------------------------------------------|-----|-----|------|

| 8   | td(RXENABLE) Delay time, RCLK ↑ to RXENABLE ↑ | 1   | 20  | ns   |

NOTE 4: All output signals are generated on the rising edge of RCLK.

Figure 1. Receive-Cell Interface

SDNS028D - OCTOBER 1994 - REVISED JANUARY 1998

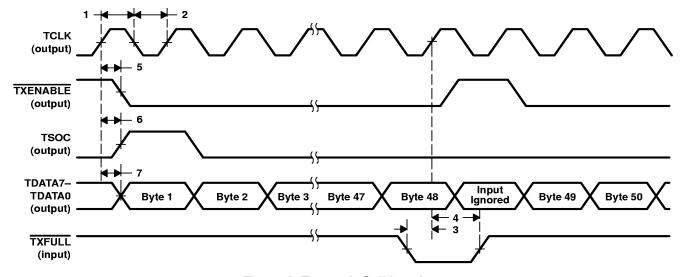

# timing requirements (see Note 5 and Figure 2)

| NO. |                                                             | MIN | MAX | UNIT |

|-----|-------------------------------------------------------------|-----|-----|------|

| 1   | t <sub>w(TCLKH)</sub> Pulse duration, TCLK high             | 12  | 18  | ns   |

| 2   | t <sub>w(TCLKL)</sub> Pulse duration, TCLK low              | 12  | 18  | ns   |

| 3   | t <sub>su(TXFULL)</sub> Setup time, TXFULL low before TCLK↑ | 10  |     | ns   |

| 4   | t <sub>h(TXFULL)</sub> Hold time, TXFULL low after TCLK↑    | 1   |     | ns   |

NOTE 5: All output signals are generated on the rising edge of RCLK. All inputs are sampled on the rising edge of TCLK.

### operating characteristics (see Note 5 and Figure 2)

| NO. |                                                                | MIN | MAX | UNIT |

|-----|----------------------------------------------------------------|-----|-----|------|

| 5   | td(TXENABLE) Delay time, TCLK↑ to TXENABLE↓                    | 1   | 20  | ns   |

| 6   | td(TSOC) Delay time, TCLK↑ to TSOC↑                            | 1   | 20  | ns   |

| 7   | t <sub>d(TDATA)</sub> Delay time, TCLK↑ to TDATA7–TDATA0 valid | 1   | 20  | ns   |

NOTE 5: All output signals are generated on the rising edge of RCLK. All inputs are sampled on the rising edge of TCLK.

Figure 2. Transmit-Cell Interface

SDNS028D - OCTOBER 1994 - REVISED JANUARY 1998

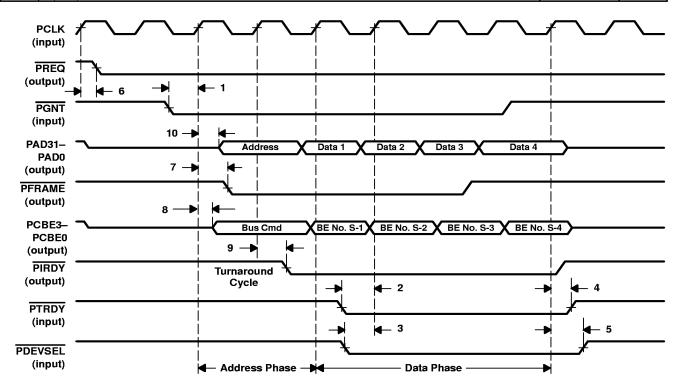

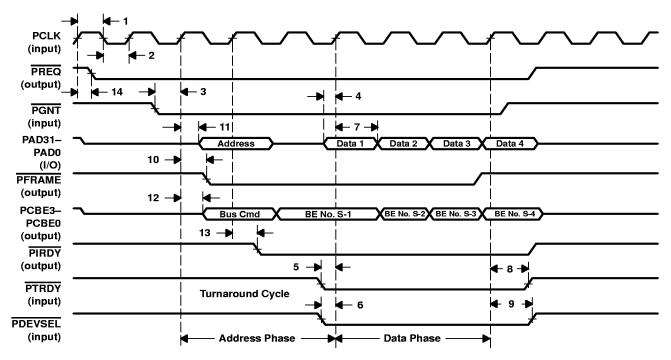

### timing requirements (see Figure 3)

| NO. |                          |                                      | MIN | MAX | UNIT |

|-----|--------------------------|--------------------------------------|-----|-----|------|

| 1   | t <sub>su(PGNT)</sub>    | Setup time, PGNT low before PCLK1    | 10  |     | ns   |

| 2   | t <sub>su(PTRDY)</sub>   | Setup time, PTRDY low before PCLK↑   | 7   |     | ns   |

| 3   | t <sub>su(PDEVSEL)</sub> | Setup time, PDEVSEL low before PCLK↑ | 7   |     | ns   |

| 4   | th(PTRDY)                | Hold time, PTRDY low after PCLK↑     | 3   |     | ns   |

| 5   | th(PDEVSEL)              | Hold time, PDEVSEL low after PCLK↑   | 3   | ·   | ns   |

# operating characteristics (see Figure 3)

| NO. |                        |                                        | MIN | MAX | UNIT |

|-----|------------------------|----------------------------------------|-----|-----|------|

| 6   | td(PREQ)               | Delay time, PCLK↑ to PREQ↓             | 2   | 12  | ns   |

| 7   | <sup>t</sup> d(PFRAME) | Delay time, PCLK↑ to PFRAME↓           | 2   | 11  | ns   |

| 8   | td(PCBE)               | Delay time, PCLK↑ to PCBE3–PCBE0 valid | 2   | 11  | ns   |

| 9   | <sup>t</sup> d(PIRDY)  | Delay time, PCLK↑ to PIRDY↓            | 2   | 11  | ns   |

| 10  | <sup>t</sup> d(PAD)    | Delay time, PCLK↑ to PAD31-PAD0 valid  | 2   | 11  | ns   |

Figure 3. TNETA1561 Write Operation (PCI SAR as Master)

SDNS028D - OCTOBER 1994 - REVISED JANUARY 1998

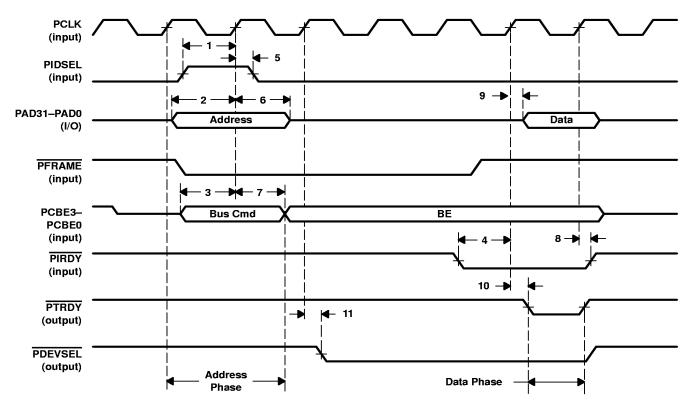

# timing requirements (see Figure 4)

| NO. |                          |                                           | MIN | MAX | UNIT |

|-----|--------------------------|-------------------------------------------|-----|-----|------|

| 1   | <sup>t</sup> w(PCLKH)    | Pulse duration, PCLK high                 | 12  |     | ns   |

| 2   | <sup>t</sup> w(PCLKL)    | Pulse duration, PCLK low                  | 13  |     | ns   |

| 3   | <sup>t</sup> su(PGNT)    | Setup time, PGNT low before PCLK↑         | 10  |     | ns   |

| 4   | <sup>t</sup> su(PAD)     | Setup time, PAD31-PAD0 valid before PCLK↑ | 7   |     | ns   |

| 5   | <sup>t</sup> su(PTRDY)   | Setup time, PTRDY low before PCLK↑        | 7   |     | ns   |

| 6   | <sup>t</sup> su(PDEVSEL) | Setup time, PDEVSEL low before PCLK↑      | 7   |     | ns   |

| 7   | <sup>t</sup> h(PAD)      | Hold time, PAD31–PAD0 valid after PCLK↑   | 2   |     | ns   |

| 8   | <sup>t</sup> h(PTRDY)    | Hold time, PTRDY low after PCLK↑          | 3   |     | ns   |

| 9   | <sup>t</sup> h(PDEVSEL)  | Hold time, PDEVSEL low after PCLK↑        | 3   |     | ns   |

# operating characteristics (see Figure 4)

| NO. |                        |                                        | MIN | MAX | UNIT |

|-----|------------------------|----------------------------------------|-----|-----|------|

| 10  | <sup>t</sup> d(PFRAME) | Delay time, PCLK↑ to PFRAME↓           | 2   | 11  | ns   |

| 11  | <sup>t</sup> d(PAD)    | Delay time, PCLK↑ to PAD31–PAD0 valid  | 2   | 11  | ns   |

| 12  | <sup>t</sup> d(PCBE)   | Delay time, PCLK↑ to PCBE3–PCBE0 valid | 2   | 11  | ns   |

| 13  | <sup>t</sup> d(PIRDY)  | Delay time, PCLK↑ to PIRDY↓            | 2   | 11  | ns   |

| 14  | <sup>t</sup> d(PREQ)   | Delay time, PCLK↑ to PREQ↓             | 2   | 12  | ns   |

Figure 4. TNETA1561 Read Operation (PCI SAR as Master)

SDNS028D - OCTOBER 1994 - REVISED JANUARY 1998

# timing requirements (see Figure 5)

| NO. |                         |                                            | MIN | MAX | UNIT |

|-----|-------------------------|--------------------------------------------|-----|-----|------|

| 1   | t <sub>su(PIDSEL)</sub> | Setup time, PIDSEL high before PCLK↑       | 7   |     | ns   |

| 2   | t <sub>su(PAD)</sub>    | Setup time, PAD31–PAD0 valid before PCLK↑  | 7   |     | ns   |

| 3   | t <sub>su(PCBE)</sub>   | Setup time, PCBE3–PCBE0 valid before PCLK↑ | 7   |     | ns   |

| 4   | t <sub>su(PIRDY)</sub>  | Setup time, PIRDY low before PCLK1         | 7   |     | ns   |

| 5   | th(PIDSEL)              | Hold time, PIDSEL high after PCLK↑         | 1   |     | ns   |

| 6   | th(PAD)                 | Hold time, PAD31-PAD0 valid after PCLK↑    | 0   |     | ns   |

| 7   | th(PCBE)                | Hold time, PCBE3–PCBE0 valid after PCLK↑   | 1   |     | ns   |

| 8   | th(PIRDY)               | Hold time, PIRDY low after PCLK↑           | 1   |     | ns   |

# operating characteristics (see Figure 5)

| NO. |                                        | MIN                     | MAX | UNIT |

|-----|----------------------------------------|-------------------------|-----|------|

| 9   | td(PAD) Delay time, PCLK               | ↑ to PAD31–PAD0 valid 2 | 11  | ns   |

| 10  | t <sub>d(PTRDY)</sub> Delay time, PCLK | ↑ to PTRDY↓ 2           | 11  | ns   |

| 11  | td(PDEVSEL) Delay time, PCLK           | ↑ to PDEVSEL↓ 2         | 11  | ns   |

Figure 5. TNETA1561 Read Operation (PCI SAR as Slave)

SDNS028D - OCTOBER 1994 - REVISED JANUARY 1998

# timing requirements (see Figure 6)

| NO. |                         |                                           | MIN | MAX | UNIT |

|-----|-------------------------|-------------------------------------------|-----|-----|------|

| 1   | t <sub>su(PIDSEL)</sub> | Setup time, PIDSEL high before PCLK↑      | 7   |     | ns   |

| 2   | <sup>t</sup> su(PAD)    | Setup time, PAD31–PAD0 valid before PCLK↑ | 7   |     | ns   |

| 3   | <sup>t</sup> su(PFRAME) | Setup time, PFRAME low before PCLK↑       | 7   |     | ns   |

| 4   | <sup>t</sup> su(PIRDY)  | Setup time, PIRDY low before PCLK↑        | 7   |     | ns   |

| 5   | <sup>t</sup> h(PIDSEL)  | Hold time, PIDSEL high after PCLK↑        | 2   |     | ns   |

| 6   | <sup>t</sup> h(PIRDY)   | Hold time, PIRDY low after PCLK↑          | 1   |     | ns   |

| 7   | <sup>t</sup> h(PFRAME)  | Hold time, PFRAME low after PCLK↑         | 3   |     | ns   |

# operating characteristics (see Figure 6)

| NO. |                                                   | MIN | MAX | UNIT |

|-----|---------------------------------------------------|-----|-----|------|

| 8   | t <sub>d(PTRDY)</sub> Delay time, PCLK↑ to PTRDY↓ | 2   | 11  | ns   |

Figure 6. TNETA1561 Write Operation (PCI SAR as Slave)

SDNS028D - OCTOBER 1994 - REVISED JANUARY 1998

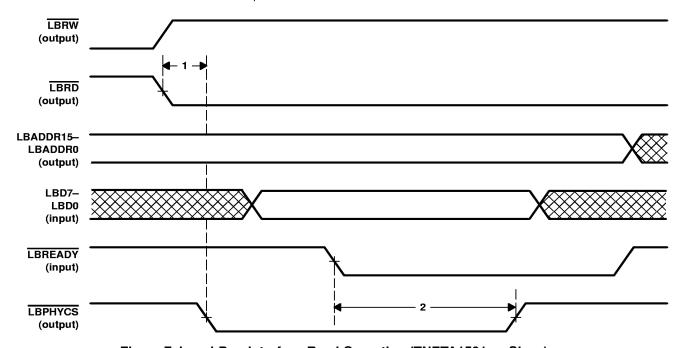

# operating characteristics (see Note 6 and Figure 7)

| NO. |                                               | MIN | TYP | MAX | UNIT |

|-----|-----------------------------------------------|-----|-----|-----|------|

| 1   | td(LBPHYCS)1 Delay time, LBRD↓ to LBPHYCS↓    |     | 30† |     | ns   |

| 2   | td(LBPHYCS)2 Delay time, LBREADY↓ to LBPHYCS↑ |     | 95† |     | ns   |

<sup>†</sup>These values are given for operation with a 33-MHz PCI clock.

NOTE 6: If LBREADY does not go active low within eight PCI clocks after LBPHYCS goes active low, the TNETA1561 latches in the data of the LBD7-LBD0 bus and terminates the read operation.

Figure 7. Local-Bus-Interface Read Operation (TNETA1561 as Slave)

SDNS028D - OCTOBER 1994 - REVISED JANUARY 1998

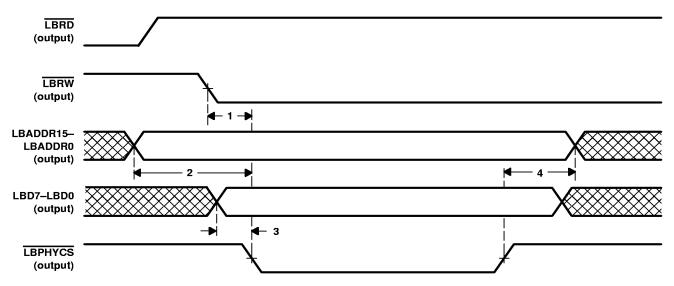

# operating characteristics (see Figure 8)†

| NO. |                          |                                                  | MIN | TYP  | MAX | UNIT |

|-----|--------------------------|--------------------------------------------------|-----|------|-----|------|

| 1   | <sup>t</sup> d(LBPHYCS)1 | Delay time, LBRW↓ to LBPHYCS↓                    |     | зо‡  |     | ns   |

| 2   | <sup>t</sup> d(LBPHYCS)2 | Delay time, LBADDR15–LBADDR0 valid to LBPHYCS↓   |     | 210‡ |     | ns   |

| 3   | <sup>t</sup> d(LBPHYCS)3 | Delay time, LBD7–LBD0 valid to LBPHYCS↓          |     | зо‡  |     | ns   |

| 4   | <sup>t</sup> d(LBADDR)   | Delay time, LBPHYCS↑ to LBADDR15–LBADDR0 invalid |     | 150‡ |     | ns   |

TEPHYCS is asserted low for eight PCI-clock cycles during a write operation to allow access to slow devices.

<sup>‡</sup>These values are given for operation with a 33-MHz PCI clock.

Figure 8. Local-Bus-Interface Write Operation (TNETA1561 as Slave)

SDNS028D - OCTOBER 1994 - REVISED JANUARY 1998

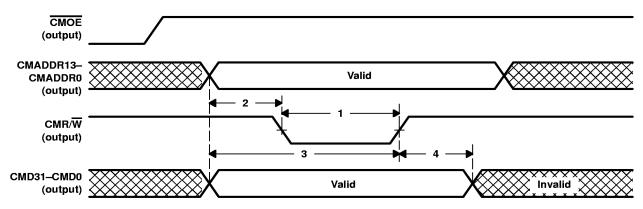

### operating characteristics (see Figure 9)

| NO. |                        |                                              | MIN | TYP | MAX | UNIT |

|-----|------------------------|----------------------------------------------|-----|-----|-----|------|

| 1   | tw(CMR/WL)             | Pulse duration, CMR/W low                    |     | 29† |     | ns   |

| 2   | <sup>t</sup> d(CMR/W)1 | Delay time, CMADDR13–CMADDR0 valid to CMR/W↓ |     | 16† |     | ns   |

| 3   | <sup>t</sup> d(CMR/W)2 | Delay time, CMD31–CMD0 valid to CMR/W↑       |     | 42† |     | ns   |

| 4   | <sup>†</sup> d(CMD)    | Delay time, CMR/W↑ to CMD31–CMD0 invalid     |     | 16† |     | ns   |

<sup>†</sup>These values are given for operation with a 33-MHz PCI clock.

Figure 9. Control-Memory-Interface Write Operation

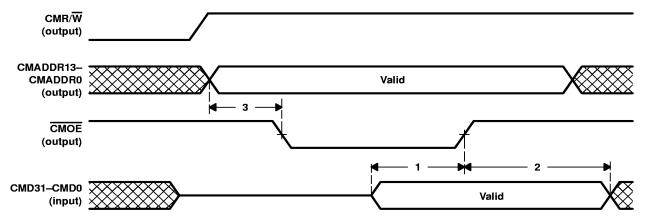

### timing requirements (see Figure 10)

| NO. |                                                                | MIN | MAX | UNIT |

|-----|----------------------------------------------------------------|-----|-----|------|

| 1   | t <sub>su(CMD)</sub> Setup time, CMD31–CMD0 valid before CMOE↑ | 7†  |     | ns   |

| 2   | t <sub>h(CMD)</sub> Hold time, CMD31–CMD0 valid after CMOE↑    | 0†  |     | ns   |

<sup>†</sup>These values are given for operation with a 33-MHz PCI clock.

### operating characteristics (see Figure 10)

| NO. |                                                                  | MIN | TYP | MAX | UNIT |

|-----|------------------------------------------------------------------|-----|-----|-----|------|

| 3   | t <sub>d(CMOE)</sub> Delay time, CMADDR13–CMADDR0 valid to CMOE↓ |     | 1   |     | ns   |

Figure 10. Control-Memory-Interface Read Operation

SDNS028D - OCTOBER 1994 - REVISED JANUARY 1998

#### PRINCIPLES OF OPERATION

| Table of Contents      |                                                                                         |  |  |  |

|------------------------|-----------------------------------------------------------------------------------------|--|--|--|

| Functional Description | Operation         23           Data Structure         29           Registers         41 |  |  |  |

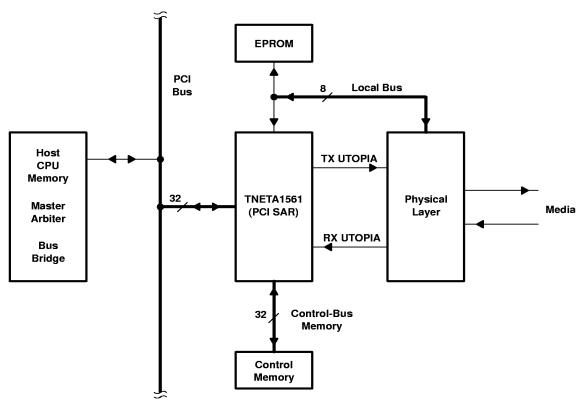

## functional overview (see Figure 11)

The TNETA1561 (PCI SAR) implements the PCI-bus protocols for connecting a peripheral device to a PCI-bus host system (mapped in memory space) and is designed for the PCI plug-in card concept. The central-resource functions, such as PCI-bus arbitration, are implemented by the host processor using the PCI SAR adapter.

The PCI SAR provides the PCI-configuration space to support its configuration and initialization. This configuration space specifies data for initialization software and error-handling software. The PCI SAR supports the mechanism to implement an external-EPROM interface for device-specific initialization and other booting mechanisms.

The PCI bus uses bursts as the basic mechanism to transfer data. The TNETA1561 supports data-burst sizes up to 52 bytes for a PCI-bus access, requiring a total of 13 data-phase transfers. A 13-word data transfer occurs when the payload data is not 32-bit aligned. The typical latency for PCI-bus access is 2  $\mu$ s, but this PCI SAR provides adequate data buffering for a worst-case latency of up to 30  $\mu$ s.

Figure 11. TNETA1561 Architecture

SDNS028D - OCTOBER 1994 - REVISED JANUARY 1998

#### PRINCIPLES OF OPERATION

#### functional overview (see Figure 11) (continued)

The TNETA1561 provides a packet interface that is managed by descriptor rings to make the 53-byte ATM framing format transparent to the user. The PCI SAR passes the 48-byte payload of each cell across the PCI bus. All packets are stored in host memory and accessed by PCI SAR by the descriptor-ring mechanism.

The PCI SAR generates data in the transmit direction via a special bit-rate control table that provides explicit cell-level interleaving between groups of VCs. This mechanism provides a high degree of flexibility in specifying peak rates for each group of up to 155 Mbit/s at a resolution greater than 32 kbit/s. The VCs within a group are serviced via a FIFO discipline on a per-packet basis.

The PCI SAR supports 1023 unique VCs, typically all associated with virtual path identifier (VPI) 0. VPI 0 allows multiple VPs, with the reminder that each VC is unique. Limited support is provided to recognize ATM-layer OAM cells. The PCI SAR is intended primarily for ATM AAL5 encapsulation and termination that is fully supported in hardware. Limited support is provided for AAL3/4 with 48-byte transfers across the PCI-bus interface and hardware recognition of the EOM indicator on the receive side. In addition, a null AAL is supported to facilitate real-time data transfer. The interface to the PHY layer consists of an 8-bit-wide datapath and associated control signals in both the transmit and receive directions. The 53-byte cells pass between the ATM and PHY layers. The native clock for PCI SAR is the PCI-bus clock frequency of 33 MHz. The 8-bit-wide datapath on the receive ATM-PHY interface requires a clock rate of at least 19.44 MHz when interacting with a 155.52-Mbit/s physical layer. The receive interface uses the PHY-layer clock. The native-word size for PCI SAR is 32 bits, corresponding to the data-bus width for the PCI bus.

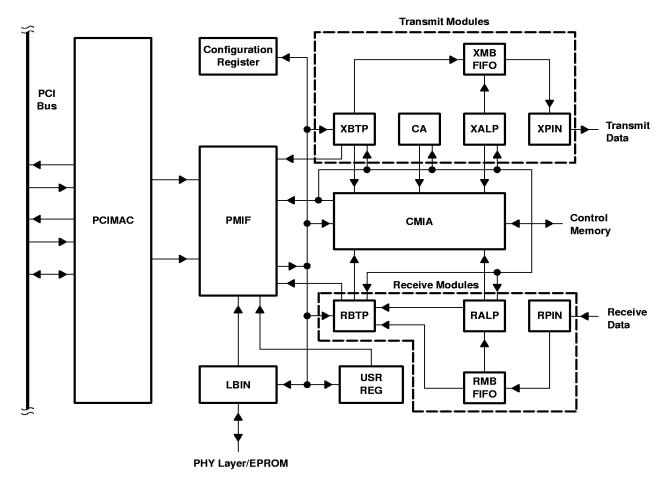

#### functional description

The PCI SAR implements the functions of the transmit and receive modules. The implementation of these modules is described in terms of their functional blocks. The PCI SAR has the following basic blocks: PCIMAC, PMIF, LBIN, USR REG, transmit block (XBTP, CA, XALP, XMB FIFO, XPIN), and receive block (RBTP, RALP, RMB FIFO, RPIN) (see Figure 12).

#### transmit modules

The transmit host and buffer transaction processor (XBTP) is responsible for all host-related functions on the transmit side. It requests 48-byte transfers from the PCI bus-interface block, PCIMAC. The cell actuator (CA) accesses the BWG table and determines the next VC to be serviced. The transmit adaptation-layer processor (XALP) processes all AAL-related functions and adds the four bytes of the ATM header to each cell. The AAL5 cyclic-redundancy check (CRC) is generated by the XBTP module and appended to the packet. The transmit buffer (XMB), a FIFO, is an 8-cell buffer that receives 13 words per cell. Idle cells also are placed in this buffer. The transmit PHY interface (XPIN) does word-to-byte unpacking and interacts with the PHY layer using the PCI-bus clock.

#### receive modules

The receive PHY interface (RPIN) performs byte-to-word packing, filters idle cells, and interacts with the PHY layer using the system PHY-layer clock crystal. The receive buffer (RMB) performs rate synchronization from the PHY-layer clock to the PCI-bus clock and buffers up to 32 cells. The receive ATM processor (RAT) and the receive ATM adaptation-layer processor (RALP) operate in parallel and are part of the same module. The RALP terminates the AAL5 CRC and processes various EOP indicators. The RAT function is responsible for deleting the ATM header and accessing the correct receive direct-memory access (DMA) entry. Finally, the receive host and buffer transaction processor (RBTP) performs all host-specific functions on the receive side.

SDNS028D - OCTOBER 1994 - REVISED JANUARY 1998

#### PRINCIPLES OF OPERATION

#### **PCIMAC**

The PCIMAC block is an interface unit between a PCI-based host system and PMIF block of PCI SAR. It masters the PCI bus in its master mode and allows the host to access the PCI SAR in its slave-mode operation. This block provides the PCI-bus host interface with all the interface signals for master and slave operations. This block implements a 32-bit data buffer to provide a datapath to and from the host. This data buffer has an interface with the XMB FIFO for transmit data and with RMB FIFO for receive data. This module also has a PCI-configuration space implemented as 32-bit registers.

The PMIF has another interface with PMIF (internal to PCI SAR) that provides all the necessary control signals enabling PCI SAR to operate in master mode. The operation in slave mode is controlled by the host system.

#### **PMIF**

The PMIF block provides interfaces to LBIN, CMIA, XBTP, RBTP, and USR REG blocks. The LBIN function provides access to the PHY layer and EPROM. The CMIA interface provides a datapath to access control-memory data. The XBTP and RBTP interfaces provide appropriate signals that make the PCI SAR device a PCI-bus master for the transmit or receive function.

The USR REG interface provides status and control data for PCI SAR functions. This block also has a SAR configuration register that is written by the host to enable transmit or receive operation. This block is only a carrier of data and control signals in either its master- or slave-mode operation. It does not initiate any operation except generating PCI-bus requests.

#### **CMIA**

The CMIA block provides an interface to the control memory using the local memory bus. It performs memory arbitration for all the functions that access control memory. Each access is a one (32-bit) word access. The priority mechanism to service various functions is in the following order: RALP, XALP, CA, RBTP, XBTP, and PMIF.

# **PHY layer**

The PHY-layer interface is serviced by the XPIN and RPIN modules for either reading data from the XMB FIFO in the transmit direction or writing data to RMB FIFO in the receive direction. Figure 12 depicts the data-flow representation of the PCI SAR functional block diagram.

SDNS028D - OCTOBER 1994 - REVISED JANUARY 1998

### **PRINCIPLES OF OPERATION**

Figure 12. PCI SAR Functional Block Diagram

SDNS028D - OCTOBER 1994 - REVISED JANUARY 1998

#### PRINCIPLES OF OPERATION

#### interfaces

The PCI SAR (TNETA1561) has the interfaces shown in Figure 13. The PCI-bus interface communicates with any other host on the PCI bus. The local-bus interface allows PCI SAR to have access to PHY-layer device registers and to an external EPROM. The control-memory interface allows the host and other internal functions of the PCI SAR to access the control memory. The PHY-layer interface allows the PCI SAR to transmit packets to a PHY-layer device or receive cells from it.

Figure 13. PCI SAR Interface to Other Hosts on the PCI Bus

SDNS028D - OCTOBER 1994 - REVISED JANUARY 1998

#### PRINCIPLES OF OPERATION

#### **PCI-bus interface**

The PCI-bus interface is provided by the PCIMAC block of the PCI SAR device. The system terminals are for the PCI-clock and reset function. The address and data terminals are for a 32-bit interface with the least significant byte (LSB) being the bits 7–0 and the most significant byte (MSB) being the bits 31–24. The bus command and byte enable are used to indicate the valid byte of the data. The device fully supports all bus commands (per PCI local-bus specification, rev 2.0, 30 April 1993) except for the interrupt acknowledge, special-cycle command, and I/O commands. In the slave mode, the memory-read multiple and the memory-read lines are treated as the memory-read command. The memory-write and invalidate commands are treated as the memory-write command. In the master mode, it does not support memory-read multiple and memory-read line commands. The device also provides all the interface-control terminals; PFRAME PIRDY, PTRDY, PSTOP, PIDSEL, and PDEVSEL. The PLOCK feature is not supported. For bus-master operation, the PREQ and PGNT terminals are provided. The error reporting terminal PPERR is for reporting parity errors (except on a special cycle) and PSSER is for reporting address-and-data parity errors or any other catastrophic system error. The PCIMAC also generates PSERR when it is self selected as the target.

The PCI SAR keeps track of the number of times it has retried a PCI-master transaction. This feature is externally programmable up to a maximum of 15 retries. Once the number of retries exceeds this count value, the TNETA1561 asserts  $\overline{\text{PSERR}}$  low. The interrupt  $\overline{\text{PINTA}}$  is defined for the PCI SAR. The PCI SAR does not support any JTAG or boundary-scan function. The PCI SAR implements the following functions: the PCI-memory bus master for DMA transfers responds as a PCI slave for local-memory accesses and supports disconnection with retry for PCI. As a PCI-bus master, it supports burst and nonburst data accesses; however, in slave mode it supports only nonburst data transfers. The PCI SAR is designed to meet the worst-case latency of the PCI bus up to 30  $\mu s$ . A minimum bus-grant value ensures the PCI-bus access for a minimum duration that is long enough to transfer a cell (48 bytes). The PCI macro terminates a transaction when the TNETA1561 is acting as a bus master and no device-select return is detected after it has initiated a transaction.

#### local-bus interface

The local-bus interface is between the PMIF and LBIN modules. The local bus allows access to the EPROM and the registers on the PHY-layer device. Since several devices are allowed on the local bus, the PCI SAR accepts a ready signal from devices on the bus as a handshake. This accommodates slow devices such as EPROMs and is used to relax timing constraints on the register interface for PHY-layer devices. The local bus is accessed only via PCI-bus transactions with the PCI SAR as the slave (with the exception of the local-bus interrupt signal). The PCI-bus address must remain stable while the local bus is active.

#### control-memory interface

The control-memory interface is between the control-memory interface and arbitration (CMIA) and all other modules that access the control memory. The control memory is set up in a  $16K \times 32$  configuration with the cycle time given by the PCI-bus clock. The control-memory interface is designed for an asynchronous SRAM with a 32-bit data bus, a 14-bit address bus, a read or write signal, and an output-enable (CMOE) signal.

#### PHY-layer interface

The ATM cell-transfer rate is full-duplex 149.76 Mbit/s, but data may arrive in bursts at 155.52 Mbit/s due to the framing scheme described by the PHY layer. A clock rate of at least 19.44 MHz is essential in the receive direction to prevent cell loss due to buffer overflow in the PHY layer. The PCI SAR decouples the PCI-bus clock from the PHY-layer clock in the receive direction via an asynchronous FIFO, which holds up to 32 cells. The PCI SAR transmits data to the PHY layer at the PCI-bus clock rate.

The PCI SAR sends a transmit clock at the PCI clock frequency and a receive clock at 19.44 MHz to the PHY layer. The transmit clock sent to the PHY layer is an inverted version of the internal clock. This ensures that all setup- and hold-time restrictions are met. The PCI SAR generates output data along with a start-of-cell indicator in the transmit direction.

SDNS028D - OCTOBER 1994 - REVISED JANUARY 1998

#### PRINCIPLES OF OPERATION

#### PHY-layer interface (continued)

This data is sent at the rate of the PCI-bus clock. The PHY layer can respond with a full signal, which is asserted at least four cycles before any internal buffers are full. The PCI SAR then turns off the TXENABLE signal until the full signal is deasserted. The PHY layer sends a start-of-cell indicator with output data. The empty signal acts as an inverted enable signal on this interface.

The PHY-layer interrupt signal is directly connected to the PCI-bus interrupt signal; therefore, PCI-bus interrupt is asserted when the PHY-layer interrupt signal is asserted.

## operation

The memory mapping of the PCI SAR local-memory elements is mapped in the host-memory space. The host memory-block location, which is determined by the host, is not predefined. The host writes the starting address in the base-address register located in the configuration space. The PCI SAR during read-from or write-to host memory uses the little-endian addressing scheme. This requires byte swapping of data into big endian and writing into the XMB FIFO during the transmit operation. The received data bytes from the RMB FIFO also must be changed from big endian into little endian.

#### PCI-bus and data-transfer requirements

The PCI SAR behaves as a PCI-bus DMA master and as a slave. The PCI SAR supports a maximum AAL5-buffer size of 64K bytes, which corresponds to a maximum AAL5-packet length of 64K bytes. In burst mode, the data transfer between the PCI SAR and the host is cell based (48 bytes). This transfer is completed in a single access of the PCI bus, but this depends on the bus latency of the host system. This transfer always is initiated by the PCI SAR as a master. The data transfer across the PCI bus is word based (4 bytes). The PCI SAR also supports nonburst transfers as a master and as a slave for host accesses (as defined in the PCI-bus transaction).

#### PCI-bus interaction and transfer size

| TRANSACTION                                                                                                    | PCI SAR ROLE | TRANSFER SIZE                    |

|----------------------------------------------------------------------------------------------------------------|--------------|----------------------------------|

| Host access – PCI SAR registers, PHY-layer registers and control memory                                        | Slave        | Word                             |

| Host access – PCI-configuration space                                                                          | Slave        | Byte/word                        |

| Host access – EPROM                                                                                            | Slave        | One, two, three<br>or four bytes |

| PCI SAR access – Transmit completion ring, transmit descriptor ring, and receive free-buffer ring transactions | Master       | Word                             |

| PCI SAR access – Posting to host-receive completion-ring entry                                                 | Master       | 4 words                          |

| PCI SAR access – Cell-payload transfers                                                                        | Master       | 1-13 words<br>latency dependent  |

SDNS028D - OCTOBER 1994 - REVISED JANUARY 1998

#### PRINCIPLES OF OPERATION

#### memory-map table

The following memory-map table defines the offset-address range for the various blocks of the control memory as they are mapped into host memory. The host-memory base address of the control-memory block is obtained from the base register 0. This is defined in the paragraph for the PCI SAR configuration-space registers. The host-memory base address of the EPROM-memory block is obtained from the expansion-ROM base-address register. These base addresses are defined in the PCI-SAR configuration-space register section.

#### control-memory block - maximum size of 64K bytes

The first 48K bytes of this block are in the control memory (external to the PCI SAR) and are divided into the first 16K bytes for the transmit-side information and the next 32K bytes for the receive-side information. The remaining 16K bytes are divided into 8K bytes each for the USR register (within the PCI SAR) and PHY-layer register (PHY-layer device external to PCI SAR).

| OFFSET ADDRESS BITS | DESCRIPTION                      | READ/WRITE<br>REGISTER |

|---------------------|----------------------------------|------------------------|

| 00000000h-000003FFh | Initialization block (256 words) | R/W                    |

| 00000400h-000023FFh | Transmit DMA states (2K words)   | R/W                    |

| 00002400h-00003FFFh | BWG table (1.2K words)           | R/W                    |

| 00004000h-0000BFFFh | Receive DMA states (8K words)    | R/W                    |

| 0000C000h-0000DFFFh | PHY-layer register (2K words)    | R/W                    |

| 0000E000h-0000FFFFh | USR register (2K words)          | R/W                    |

#### indirect local-memory block - maximum size of 8K bytes

The indirect control-memory block includes the following registers for addressing, data, and status information:

| REGISTER                                     | SIZE   | DESCRIPTION                                                                |

|----------------------------------------------|--------|----------------------------------------------------------------------------|

| Control-memory address register              | 32 bit | Contains the address of the control-memory block                           |

| Control-memory data register                 | 32 bit | Buffer that provides data read from or written to the control-memory block |

| Control-memory control register 1-register 8 | 32 bit | Display PCI SAR register information                                       |

#### **EPROM** memory block

The TNETA1561 can access an EPROM via the local-bus interface. The maximum-size EPROM that can be accessed by the TNETA1561 is 8K bytes. There are four sizes of data transfers from the EPROM (one, two, three, or four byte). To read data from the EPROM, the host generates a 32-bit PCI address and drives the appropriate byte-enable signals according to the type of transfer being executed.

# PHY-layer registers access

The TNETA1561 uses the local-bus interface to access the PHY-layer registers. The host system must use the PCI interface to address the register in the PHY layer; therefore, a 32-bit address has to be generated from the host and passed to the TNETA1561. To access a byte-wide address offset for the PHY-layer device registers, the host software uses the PCI-bus byte-enable signals to specify which data byte to access on the PHY-layer device. During a write operation to a PHY-layer register, the host uses byte-enable signals to indicate to the TNETA1561 which data byte contains the valid byte. During a read operation to a PHY-layer register, the TNETA1561 copies the byte read from the PHY-layer four times to form a 32-bit word. The 32-bit word containing the PHY-layer data in all four bytes is transferred to the host.

SDNS028D - OCTOBER 1994 - REVISED JANUARY 1998

#### PRINCIPLES OF OPERATION

#### control-memory access

The control memory is accessed by using the offset-address bit of the PCI-bus address. This provides a 14-bit-wide address bus to the control memory. All PCI-bus accesses to control memory are one-word accesses at word boundaries.

#### control-memory address map

The data below specifies the PCI SAR slave-mode PCI-bus physical-address ranges for peripheral devices.

| MEMORY REGIONS                       | CONTROL-MEMORY<br>BASE POINTERS<br>(HEX) |

|--------------------------------------|------------------------------------------|

| Initialization block                 | 0000h                                    |

| Transmit BWG 0-255 - DMA block       | 0100h                                    |

| BWG table (1200 words, 4800 entries) | 0900h                                    |

| Receive BWG/VCI 0-1023 - DMA block   | 1000h                                    |

#### PCI-bus physical addresses for PCI SAR peripheral devices

The data below specifies the PCI SAR slave-mode PCI-bus physical-address ranges for peripheral devices.

| DESCRIPTION                  | ADDRESS<br>BITS | READ/WRITE<br>REGISTER |

|------------------------------|-----------------|------------------------|

| EPROM addresses              | 14              | R                      |

| PHY-layer register addresses | 14              | R/W                    |

| Control-memory addresses     | 14              | R/W                    |

#### packet-interface information

Packet interface, BWG-table mechanism, AAL5 processing, AAL3/4 processing, null-AAL processing, VPI/VCI/GFC processing, OAM processing, and details on the transmit-descriptor rings/DMA, receive free-buffer rings/DMA, and completion rings are described in this section.

The PCI SAR uses host memory to store a packet (48-byte cells) in both transmit and receive directions. The PCI SAR initiates the data transfer for the PCI bus for both transmit and receive operations. The packet does not include AAL5 encapsulation while in host memory. The PCI SAR provides this header data. The buffering of data within the PCI SAR is limited to an 8-cell FIFO for transmit and a 32-cell FIFO for receive.

Each packet queued for transmission can be distributed across multiple buffers in host memory with each starting on a one-byte boundary. Packets that are received over ATM are placed in a single buffer in host memory (either big or small) aligned to a 16-byte boundary.

SDNS028D - OCTOBER 1994 - REVISED JANUARY 1998

#### PRINCIPLES OF OPERATION

#### bandwidth group (BWG) table mechanism

The PCI SAR generates data via a special bit-rate control table known as the BWG table (see Figure 14). The BWG table consists of up to 4800 entries and each entry consists of an 8-bit BWG index. The table is organized with 1200 words in control memory. The size is programmable via the BWG-size register. Each BWG index corresponds to a transmit DMA channel, and the TNETA1561 can support 255 (8-bit index) transmit DMA channels simultaneously. The PCI SAR cycles through the table and sends an ATM cell for the transmit DMA channel for each entry in the table. If a zero value is entered for a BWG index, an idle cell is transmited. The BWG table assigns the transmit-side bandwidth. The total available bandwidth for an OC-3c SONET link is 135.63 Mbit/s (155.52 Mbit/s less SONET and ATM overhead). The granularity is obtained by dividing the SONET-link bit rate (135.63 Mbit/s) by the entries in the BWG table (4800).

$135.63 \text{ Mbit/s} \div 4800 = 28,250 \text{ bit/s per entry}$

An application requiring 500 kbit/s requires 19 entries in the table.

500 kbit/s ÷ 28,250 bit/s per entry = 19 required entries in the table

If the application uses the transmit descriptor ring 5, then there will be 19 entries with 5 as the BWG index (see Figure 14).

| 5 | 5 | 5 | 5 | 0    |

|---|---|---|---|------|

| 5 | 5 | 5 | 5 | 1    |

| 5 | 5 | 5 | 5 | 2    |

| 5 | 5 | 5 | 5 | 3    |

| 5 | 5 | 5 | 0 | 4    |

|   |   | • |   | •    |

|   |   | • |   | •    |

|   |   | • |   | •    |

|   |   | • |   | •    |

|   |   | • |   | •    |

|   |   | • |   | •    |

| 0 | 0 | 0 | 0 | 1199 |

Figure 14. BWG Table

SDNS028D - OCTOBER 1994 - REVISED JANUARY 1998

#### PRINCIPLES OF OPERATION

#### AAL-type processing

The PCI SAR supports various types of AAL processing. AAL5, AAL3/4, null-AAL, OAM, and GFC processing are described in this section.

#### AAL5 processing

The primary support is for AAL5 with encapsulation in the transmit direction and termination in the receive direction. AAL5 packets are converted to cells by the PCI SAR before delivery to the PHY layer. Similarly, the device recovers the 53-byte ATM cells from the PHY layer before it performs AAL5 termination.

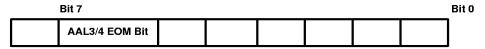

Since 48 bytes are provided across the PCI-bus interface, all AAL3/4 packet data processing is performed by the host in software. AAL5 processing is disabled on VCIs using AAL3/4. The AAL3/4 EOM indicator, which is located in the first byte of the ATM payload (see Figure 15), is recognized in hardware, initiating an interrupt to the host. This is used by the host to retrieve successive 48-byte payload segments from the appropriate buffer.

#### AAL3/4 processing

The PCI SAR adds the pad, the control/length field, and the cyclic-redundancy check (CRC) for transmit packets. The PCI SAR does not interpret the field length in the AAL5 frame in the receive direction; therefore, the entire AAL5 packet is forwarded to host memory, allowing the driver to remove the correct payload. This also allows the host to examine the control field in software, necessary in a time of evolving standards in this area. The PCI SAR performs CRC checks in the receive direction and indicates EOP processing to the host, based on the EOP indication in AAL5.

Figure 15. AAL3/4 Processing

#### null-AAL processing

Null-AAL processing uses the same mechanism as AAL3/4 in the transmit direction to disable AAL5 processing. The control entry associated with each BWG (VCI) in the receive direction has an entry to indicate an interval defined in units of cells received. The PCI SAR then provides an interrupt to the host when the number of cells received on the VCI is equal to that indicated by the table entry. This counter is reset after each interrupt (at the end of each interval). This interval also is referred to as a packet, although it does not encapsulate a well-defined unit of information.

#### OAM processing

ATM-layer OAM processing does not require real-time intervention and is processed in software. OAM cells received on the link are identified by the PCI SAR.

#### high-order VPI/VCI bits and GFC processing

The lower ten bits of the VCI are used to encode the 1023 possible VCIs. VCI 0 is not used since it indicates unassigned cells. The upper-order bits of the VCI and the VPI field are programmable on a per-VC basis on transmit. The generic-flow-control (GFC) field always is set to zero.

The upper-order bits of the VCI, the VPI field, and the GFC field are ignored on all cells that are received. These cells are passed only to the PCI SAR if the header-error-control (HEC) field is correct, the upper-order bits of the header are set intentionally, or the cell is misrouted. The probability of misrouting is small and such an event would be detected via the CRC check in AAL5. The advantage of this scheme is that any VPI/VCI combination is supported if the lower ten bits of the VCI are unique.

SDNS028D - OCTOBER 1994 - REVISED JANUARY 1998

#### PRINCIPLES OF OPERATION

#### ATM-layer OAM encoding

| NO. | ITEM                               | VCI | PTI |

|-----|------------------------------------|-----|-----|

| 1   | VP level: link-associated OAM cell | 3   | _   |

| 2   | VP level: end-to-end OAM cell      | 4   | -   |

| 3   | VC level: link-associated OAM cell | Any | 4   |

| 4   | VC level: end-to-end OAM cell      | Any | 5   |