# STV0116

# PAL/NTSC DIGITAL ENCODER

- BOTH 625 & 525 LINES MULTIPLEXED 8 BIT DIGITAL INPUT ACCORDING TO CCIR 601-2 AND REC 656

- NTSC M, PAL B, D, G, H, I, PAL N (ARGEN-TINA) PROGRAMMABLE OUTPUT

- COMPOSITE OR LINE SYNCHRONISM OUTPUT

- CVBS, Y ANALOG OUTPUTS THROUGH 9 BIT DACs

- RGB AND C ANALOG OUTPUTS THROUGH 8 BIT DACs

- OSD INSERTION WITH CLUT AND 6.75MHz OUTPUT CLOCK REFERENCE

- TRUE 27MHz MODULATOR

- TRUE NTSC ENCODING WITH I, QAXIS

- OVERSAMPLING TO 27MHz FOR EASY OUTPUT FILTERING

- ODD/EVEN SYNCHRONISM INPUT/OUTPUT

- ON CHIP TEST PATTERN GENERATOR

- I<sup>2</sup>C BUS CONTROLLED

- EASY CONFIGURATION TO ANY STAND-ARD WITH ONE REGISTER LOADING

### DESCRIPTION

The STV0116 converts the digital output of a Video MPEG decoder into a standard analog base band NTSC/PAL signal, with a modulated subcarrier. Both composite and SVHS format video signals are simultaneously delivered to 3 analog outputs. The STV0116 includes additionnally three analog RGB outputs to be used for the SCART plug.

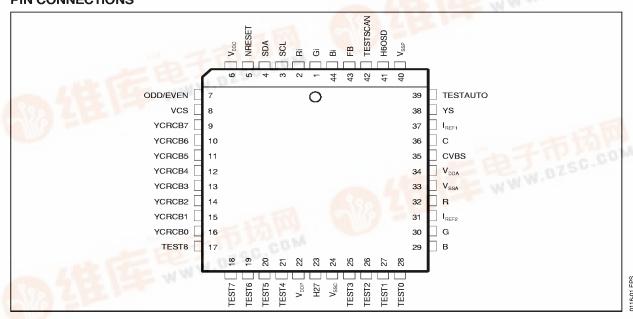

# PIN CONNECTIONS

October 1996 1/21

# **PIN DESCRIPTION**

| Pin N°               | Symbol                              | Туре | Function                                                                                                                                                                                                                                                                       |

|----------------------|-------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2 - 1 - 44           | Ri, Gi, Bi                          | I    | OSD serial inputs. OSD_Pixel minimum width is 148ns (i.e. 6.75MHz). Ri, Gi, Bi transcoded to Y, CR, CB according to CLUT (8 colors among 262144). CLUT tint programmable                                                                                                       |

| 3                    | SCL                                 | l    | Serial interface with microcontroller. Spread of frequency: 0 to 400kbit/s. Level 0 > 200ns.                                                                                                                                                                                   |

| 4                    | SDA                                 | 1/0  | Trigger pads to ensure a low frequency input.  Maximum capacitance for each bus line (400pF).  Chip address (hex): b0 (write mode), b1 (read mode).                                                                                                                            |

| 5                    | NRESET                              | I    | The hard reset is active low. It has priority on software reset. FALL and RISE time of hard NRESET < 20ns. Hold time of hard NRESET > 80ns. No synchronism of hard NRESET is necessary. NRESET Imposes default states.                                                         |

| 24 - 6               | V <sub>SSC</sub> - V <sub>DDC</sub> |      | 0V-5V supply for core.                                                                                                                                                                                                                                                         |

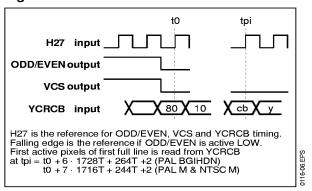

| 7                    | ODD/EVEN                            | I/O  | ODD/EVEN frame input (slave mode by ODD/EVEN), output (master mode or slave mode by EAV).  The synchronism reference is the rising edge of H27.  Default polarity: odd field = LOW level, even field = HIGH level.                                                             |

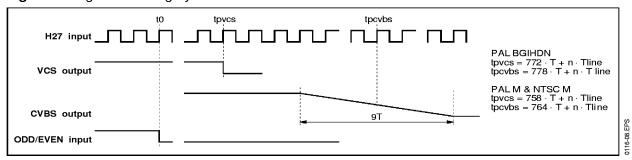

| 8                    | vcs                                 | 0    | Composite synchronization or horizontal line synchronization output. Polarity (default : positive). The synchronism reference is the rising edge of H27.                                                                                                                       |

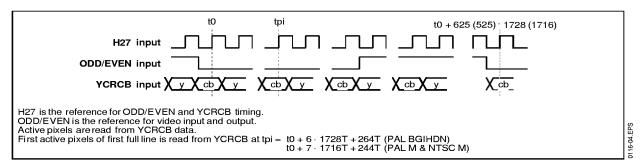

| 9 to 16              | YCRCB [7:0]                         | I    | Time multiplexed 4:2:2 luminance and color difference input as defined in CCIR Rec 601_2 and Rec 656 (TTL levels inputs). 525 lines/60Hz or 625 lines/50Hz. Timing (Rec 656 part II). A line length is 1716 or 1728 periods of 27MHz for 525 or 625 line systems respectively. |

| 17 to 21<br>25 to 28 | TEST [7:0]                          | I/O  | For test purpose only. Input (default mode).                                                                                                                                                                                                                                   |

| 40 - 22              | V <sub>SSP</sub> - V <sub>DDP</sub> |      | 0V-5V supply for pads.                                                                                                                                                                                                                                                         |

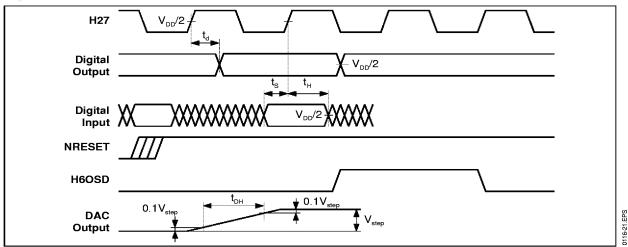

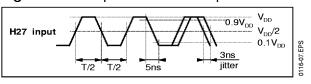

| 23                   | H27                                 | I    | 27MHz input clock reference. LOW/HIGH ratio: 50%. FALL and RISE time: 5ns Max. The rising edge is the reference for HOLD and SETUP time of all inputs. The duration of High/Low level is in accordance with REC656 (18.5ns ±3ns with less than 3ns of jitter).                 |

| 32 - 30 - 29         | R, G, B                             | 0    | Current analog outputs synchrone with CVBS.                                                                                                                                                                                                                                    |

| 31                   | I <sub>REF2</sub>                   | I    | Reference current source of the triple 8 bit DAC for R, G, B. For a reference load of $1.8k\Omega$ : $1.7 < I_{REF2}$ (mA) $< 2.1$ .                                                                                                                                           |

| 33 - 34              | V <sub>SSA</sub> - V <sub>DDA</sub> |      | 0V-5V supply for DACs.                                                                                                                                                                                                                                                         |

| 35                   | CVBS                                | 0    | Current analog video composite output.                                                                                                                                                                                                                                         |

| 36                   | С                                   | 0    | Current analog chrominance output, SVHS compatible.                                                                                                                                                                                                                            |

| 37                   | I <sub>REF1</sub>                   | I    | Reference current source of the triple DAC for CVBS, YS and C. For a reference load of $1.8 k\Omega$ : $1.7 < I_{REF1}$ (mA) $< 2.1$ .                                                                                                                                         |

| 38                   | YS                                  | 0    | Current analog luminance output with composite synchronization, SVHS compatible.                                                                                                                                                                                               |

| 39                   | TESTAUTO                            | l    | Hardware autotest mode control, active HIGH. TESTAUTO input forces the master mode with color bar pattern outputs.                                                                                                                                                             |

| 41                   | H6OSD                               | 0    | 6.75MHz clock output for the reference of an OSD input signal.                                                                                                                                                                                                                 |

| 42                   | TESTSCAN                            | l    | Full scan test mode control, active HIGH.  TESTSCAN must be grounded for normal operation.                                                                                                                                                                                     |

| 43                   | FB                                  | l    | Fast blanking is minimum 1 OSD_pixel large.<br>FB synchronous to H27.<br>OSD active when FB is HIGH.                                                                                                                                                                           |

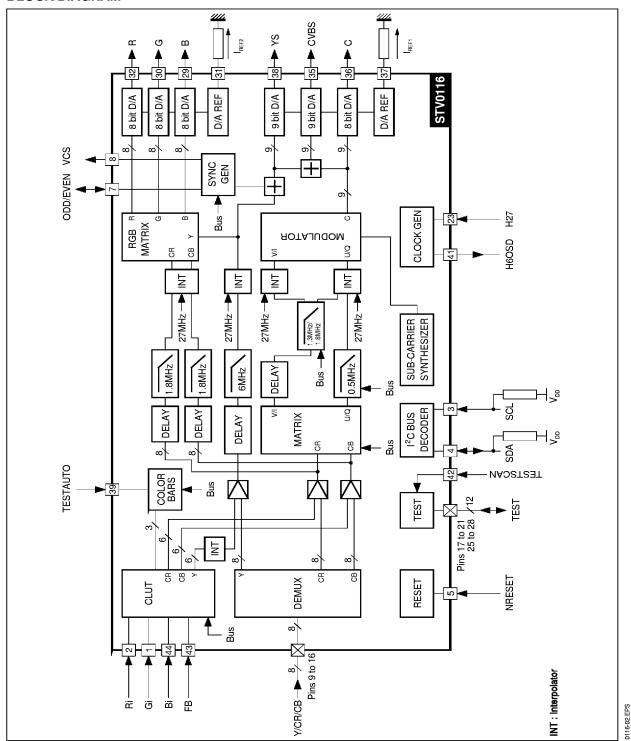

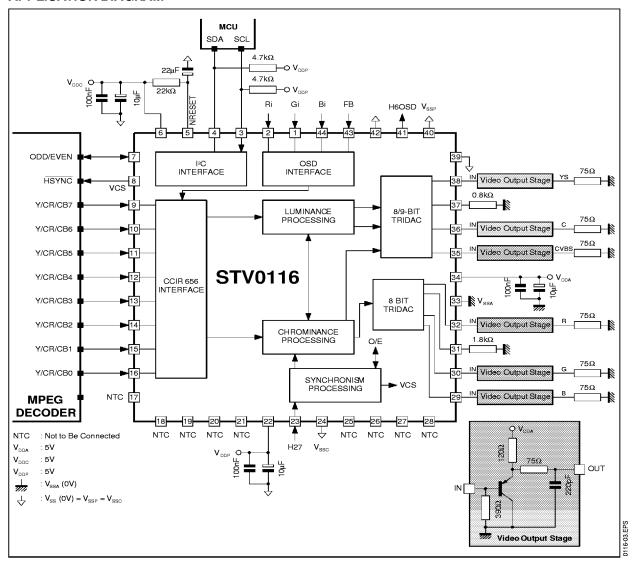

## **BLOCK DIAGRAM**

# **ABSOLUTE MAXIMUM RATINGS**

| Symbol            | Parameter                  | Value                 | Unit |

|-------------------|----------------------------|-----------------------|------|

| $V_{DD}$          | Supply Voltage             | 7                     | V    |

| V <sub>IN</sub>   | Digital Inputs             | V <sub>DD</sub> + 0.3 | ٧    |

| V <sub>OUT</sub>  | Digital and Analog Outputs | 0, V <sub>DD</sub>    | V    |

| T <sub>oper</sub> | Operating Temperature      | 0, +70                | °C   |

| T <sub>stg</sub>  | Storage Temperature        | -20, +150             | °C   |

0116-02.TBL

# **ELECTRICAL CHARACTERISTICS**

| Symbol                              | Parameter                                                                  | Test Conditions                          | Min.                    | Тур. | Max.                          | Unit |

|-------------------------------------|----------------------------------------------------------------------------|------------------------------------------|-------------------------|------|-------------------------------|------|

| OC (V <sub>DDA</sub> =              | $= V_{DDP} = V_{DDC} = 5V$ , $T_{amb} = 25$ to 7                           | 70°C, unless otherwise specified)        |                         |      |                               |      |

| Supply                              |                                                                            |                                          |                         |      |                               |      |

| $V_{DDA}$                           | Analog Supply Voltage                                                      |                                          | 4.75                    | 5    | 5.25                          | >    |

| I <sub>DDA</sub>                    | Analog Supply Current                                                      | $I_{REF1}=I_{REF2}=3mA,\ R_L=400\Omega$  |                         | 30   |                               | mA   |

| $V_{DDP}$                           | Output Buffer Supply Voltage                                               |                                          | 4.75                    | 5    | 5.25                          | ٧    |

| $I_{DDP}$                           | Output Buffer Supply Current                                               | Autotest mode                            |                         | 30   |                               | mA   |

| $V_{DDC}$                           | Core Supply Voltage                                                        |                                          | 4.75                    | 5    | 5.25                          | >    |

| $I_{DDC}$                           | Core Supply Current                                                        | Autotest mode                            |                         | 20   |                               | mA   |

| Digital Inp                         | outs                                                                       |                                          |                         |      |                               |      |

| V <sub>L</sub><br>V <sub>H</sub>    | Low Input Voltage (SDA, SCL)<br>High Input Voltage (SDA, SCL)              |                                          | -0.50<br>3              |      | 1.50<br>7                     | >>   |

| V <sub>IL</sub><br>V <sub>IH</sub>  | (any others are TTL compatible)<br>Low Input Voltage<br>High Input Voltage |                                          | -0.50<br>2              |      | 0.80<br>V <sub>DD</sub> + 0.5 | >>   |

| ال                                  | Input Leakage Current                                                      | V <sub>ILmin</sub> or V <sub>IHmax</sub> |                         |      | 10                            | μΑ   |

| CL                                  | Input Capacitance (all inputs)                                             |                                          |                         |      | 10                            | рF   |

| Digital Ou                          | tputs                                                                      |                                          |                         |      |                               |      |

| $oldsymbol{V}_OL \ oldsymbol{V}_OH$ | Low Output Voltage<br>High Output Voltage                                  | $I_{OL} = 1mA$<br>$I_{OH} = -1mA$        | V <sub>SS</sub><br>2.40 |      | 0.60<br>V <sub>DD</sub>       | >>   |

| DACs                                |                                                                            |                                          |                         |      |                               |      |

| ILE                                 | Integral Linearity Error                                                   | $I_{REF} = 3mA, V_{DDA} = 5V,$           |                         |      | ±2                            | LSB  |

| DLE                                 | Differential Linearity Error                                               | $R_L = 400\Omega$                        |                         |      | ±1                            | LSB  |

| lg                                  | Current Gain                                                               |                                          |                         | 2    |                               |      |

| $G_{E}$                             | Gain Error                                                                 |                                          |                         | 3    |                               | %    |

AC ( $V_{DDA} = V_{DDP} = V_{DDC} = 5V$ ,  $T_{amb} = 25$  to 70 °C,  $C_L = 20$ pF, unless otherwise specified)

| Digital In      | puts                           |                                                                                                        |    |     |    |     |

|-----------------|--------------------------------|--------------------------------------------------------------------------------------------------------|----|-----|----|-----|

| ts              | Input Data Set-up Time         |                                                                                                        | 7  |     |    | ns  |

| t⊢              | Input Data Hold Time           |                                                                                                        | 10 |     |    | ns  |

| Digital Ou      | utputs                         |                                                                                                        |    |     |    |     |

| t <sub>d</sub>  | Output Delay Time              | C <sub>L</sub> = 10pF                                                                                  |    |     | 29 | ns  |

| ph0             | Output Phase of H6OSD after Re | eset                                                                                                   |    | H27 |    |     |

| Fmi             | Frequency of SCL               |                                                                                                        |    |     | 1  | MHz |

| Clock Inp       | out                            |                                                                                                        |    |     |    |     |

| tc              | Clock Cycle Time               |                                                                                                        |    | 27  |    | MHz |

| t <sub>D</sub>  | Clock Duty Factor              |                                                                                                        |    | 50  |    | %   |

| $t_R$           | Clock Rise Time                |                                                                                                        |    |     | 5  | ns  |

| t <sub>F</sub>  | Clock Fall Time                |                                                                                                        |    |     | 5  | ns  |

| DAC Out         | put                            |                                                                                                        |    |     |    |     |

| t <sub>DH</sub> | Output Delay Time              | $I_{REF} = 3mA$ , $R_L = 400\Omega$ , $C_L = 10pF$ 32 LSB max step 9 bit dac 16 LSB max step 8 bit dac |    |     | 29 | ns  |

116-04.TBL

Figure 1

#### CIRCUIT DESCRIPTION

The STV0116 can operate either in master mode or in slave mode receiving a vertical parity synchronism signal from MPEG IC.

An I<sup>2</sup>C Bus allows to control the main functions:

- Selection of the standard,

- Synchronisation mode and polarity,

- Color killing,

- Reset of the synchronism and oscillator,

- Test mode.

- By-pass of the chroma filters,

- Sub-carrier phase and frequency adjustment,

- OSD CLUT.

#### **Pixel Input Format**

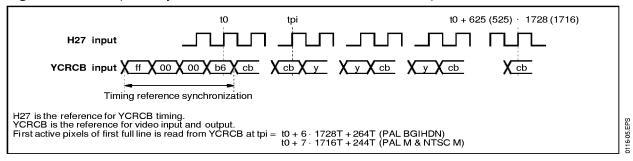

The digital input is a time multiplexed YCBCR 8 bit stream.

The samples represent a succession of CB/Y/CR/Y component values and are latched on the rising edge of H27 (27MHz clock). This input is fully compatible with SGS-THOMSON MPEG decoder IC's outputs.

#### **Video Timing**

The STV0116 outputs interlaced video to conform to the NTSC or PAL timing specifications. Non standard line counts in PAL or NTSC modes are not supported.

The 8 field (for PAL) and 4 field (for NTSC) burst sequences are internally generated, using the 27MHz clock as reference.

Rise and fall times of sync, blanking interval, and the burst envelope are internally controlled according to the composite video specification (see Figures 6 and 7). Only lines 1 to 9, 264 to 272 for 525 and 624 to 5, 311 to 318 for 625 lines system respectively are blanked. The others can be used for data encoding.

#### **Master Mode**

After a software reset, the sync generator starts counting 27MHz clock pulses and provides a complete composite sync pulse sequence of 4 fields to the NTSC encoder.

For PAL, the combination with the ODD/EVEN line sequence gives the 8 field sequence for the color burst insertion. At the end of a sequence the counter is automatically reset and a new sequence can start. In the same time an ODD/EVEN frame pulse is output to control the MPEG decoder.

#### Slave Mode

After a software reset, the sync counter waits for the falling edge of the ODD/EVEN pulse sent to the ODD/EVEN Pin selected as an input. Then a sequence identical to the one in master mode can start and is reset by the next falling edge of the field pulse (see Figure 2).

If no ODD/EVEN pulse is present after a full 3 frames sequence, the IC can either regenerate itself the next sequences in "free running" using the 27MHz clock, or switch on the internal test bar pattern, or blank the outputs, after reading status register.

Alternatively the STV0116 can be set to extract the synchronization directly from the Y/CR/CB input data sequence (see Figure 3).

These different modes are selectable by the I<sup>2</sup>C Bus.

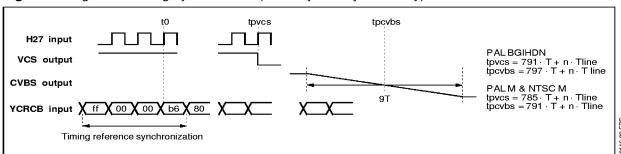

Figure 2: Slave 1 (Slave by ODD/EVEN)

Figure 3: Slave 2 (Slave by EAV, End of Active Video, taken on YCRCB)

### Chrominance Encoding

The demultiplexed CR, CB samples feed a chroma I/Q matrix for NTSC and a U/V matrix for PAL. The U/V or I/Q chroma signals are then band limited according to the CCIR 624 recommendations and interpolated at a 27MHz pixel rate. This process makes easier the filtering for the D/A convertion and allows a more accurate encoding.

A Discrete Time Oscillator, using a 22 bit phase accumulator, generates the color sub-carrier. This signal feeds a quadrature modulator which modulates the baseband chroma signals.

The phase and the frequency of the sub-carrier can be adjusted if needed or reset by software.

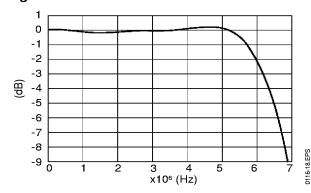

## **Luminance Processing**

The demuxed Y samples are band limited and interpolated at 27MHz samples rate.

Then a gain and offset compensation is applied to the luma signal before inserting the synchronism pulses.

The interpolation filter compensates for the sinX/X attenuation provided by the D/A convertion, and greatly simplifies the output filtering.

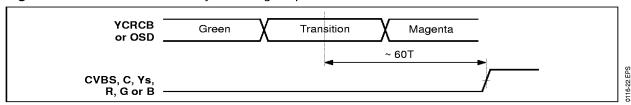

A delay is inserted in the luma path to transmit correctly picture transition.

## **CVBS and SVHS Outputs**

Each digital signal drives a 9-bit D/A converter for Y, CVBS, 8-bit for C, operating at 27MHz.

The outputs are current sources and are proportional to the current reference value. For 3mA reference current and  $400\Omega$  load, the levels are such that a PNP emitter follower is enough to drive the SCART plug (1V from sync tip to white level). The integrated over sampling filters make the external antiliasing low pass filter simpler.

#### **Reset Procedure**

A hard reset is performed by grounding the reset pin. This will set the IC in PAL BDGHI and slave mode.

The "software reset" configure the IC according to the configuration fixed by register 0 (that isn't reseted itself). The sync generator is then ready for a new sequence. This will be initialized either by the next clock pulse in master mode, or by the next field pulse in slave mode.

### R, G, B Outputs

After demux, CR/CB data feed a 4 times interpolation filter at 27MHz sample rate. Then the chroma base-band signal is band limited at 1.8MHz and matrixed with Y. Three 8 bit D/A converters generate R, G, B outputs at 27MHz.

#### **H6OSD Output**

This 6.75Mhz clock signal is intended to trig the OSD input data. It is synchronous with the H27 clock reference.

## R, G, B, FB OSD Inputs

These are logic inputs for OSD insertion. FB (fast blanking) is used to switch from the main video input to the RGB inputs. FB and RGB inputs must be locked to the H27 clock. They are latched on the rising edge of 6.75MHz clock signal.

The RGB inputs allow 8 color combinations. The internal CLUT (color look up table) affects for each of these 8 values a color chosen among 643 preset for Y, CR, CB components. As CLUT performs the matrixing into Y, CR and CB, the resulting signals take benefit of the oversampling filters in the main path. Additionally the Y signal is interpolated. Inserted OSD rate is 6.75Mbit/s.

#### Signal Quality Detector

It is active if the timing reference synchronization data of the input data stream is present.

By use of Hamming decoding in video Y/CR/CB (EAV, SAV), the IC generates a bit (HOK). This bit indicates multiple errors of the hamming decoding. It can be read by the microcontroller.

### Master/Slave Functionality

T = 1 period of H27. Duration of active line is 1440T.

Figure 4: Master Mode

#### Freerun and SLAVE Mode

If freerun is allowed and the vertical synchronism is lost, all the video signals are generated with the picture sampled on YCRCB. VCS is still available. If freerun is not allowed VCS is stopped and YS, C, CVBS, R, G, B are at BLACK level.

#### Synchronization Signals

T = 37.037ns = 1 period of H27 (27MHz).

Figure 5: H27 Input Maximum Acceptance

Figure 6: Logic and Analog Synchronisms

Figure 7: Logic and Analog Synchronisms (Slave by EAV synchro only)

Figure 8: YCRCB and OSD Delay to Analog Output

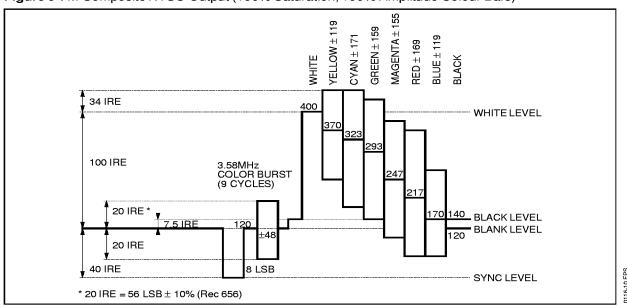

Figure 9: M Composite NTSC Output (100% Saturation, 100% Amplitude Colour Bars)

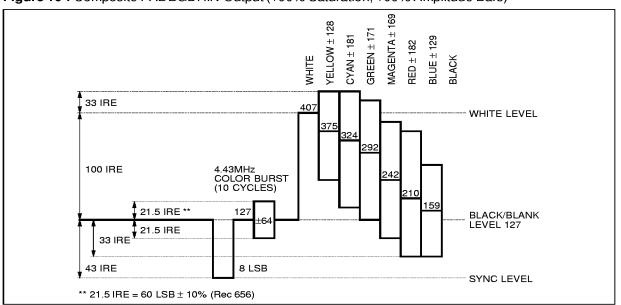

Figure 10: Composite PAL BGDHIN Output (100% Saturation, 100% Amplitude Bars)

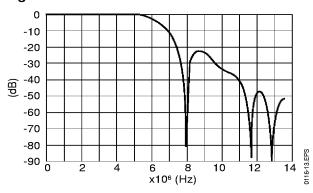

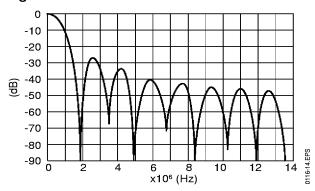

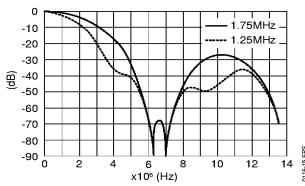

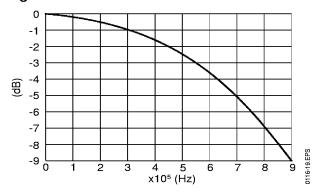

Figure 12: Luma Filter

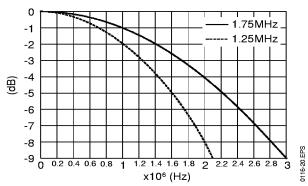

Figure 13 : Chroma Q Filter

Figure 14: Chroma Filters

Note: Those filter curves include the sinx/x attenuation of DACs.

Figure 12a: Luma Filter

Figure 13a: Chroma Q Filter

Figure 14a: Chroma Filters

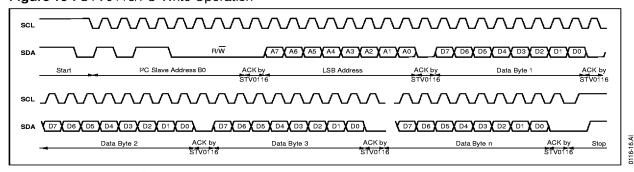

## I<sup>2</sup>C REGISTERS DESCRIPTION

The IC is controlled by an  $I^2$ C Bus and internal registers can be read or written by an external microcontroller.

Encoder addresses are:

- Write 10110000 (b0 hex).

- Read 10110001 (b1 hex).

Registers are organized as follows:

Reg 0 : Sync mode selection, standard selection, sync polarity selection

Reg 1 : Color killer, chroma filter selection, sync output selection

Reg 2, 3 : Sync delay

Reg 4 to 9 : Sub-carrier frequencies

Reg 10 to 17: Y clut for RiGiBi input encoding Reg 18 to 25: CR clut for RiGiBi input encoding Reg 26 to 33: CB clut for RiGiBi input encoding

Reg 34 : Test (not to be used)

Reg 35 : Status Reg 36 to 38 : Line forcing

#### I<sup>2</sup>C FORMAT

#### Write Mode (all registers except STATUS)

| - |   |               |   |   |             |   |        |   |            |   |   |

|---|---|---------------|---|---|-------------|---|--------|---|------------|---|---|

|   | s | Slave address | W | Α | Sub-address | Α | Data 0 | Α | <br>Data N | Α | Р |

S Start condition

Slave address 1011000

W = '0' Write flag

A Acknowledge, generated by slave (STV0116) when OK A = '0' else '1'

Sub-address Sub-address register (content is made of one byte)

Data 0 First data byte

Data N Continued data bytes (address is automatically incremented) and A's

P Stop condition

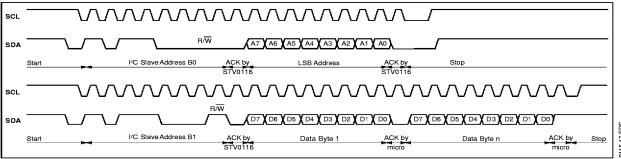

#### Read Mode (all registers)

| S    | Slave address | W | AC | Sub-address N | AC | Р |

|------|---------------|---|----|---------------|----|---|

| Then | i :           | • |    |               |    |   |

| S    | Slave address | R | AC | Data N        | АМ |   |

S Start condition

Slave address 7 bit address for STV0116: 1011000

W = '0' Write flag

AC Acknowledge, generated by slave (STV0116) when OK, AC = '0' else '1'

R = '1' Read flag

Sub-address 8 bit sub-address register

Data N Data byte of register N, sent by STV0116

Data N+1 Data byte of register N+1 (address automatically incremented)

AM Acknowledge, generated by the microcontroller AM = '0' when acknowledge is OK else '1'

P Stop condition (when last AM = '1')

## I<sup>2</sup>C FORMAT (continued)

#### Remarks

### Writing of a register:

Registers 0, 1, ..., 34 can be loaded sequentially with only one start/stop condition followed by the sub-address of the first register desired.

Example: Start followed by address b0 and sub-address 1 and then 3 bytes of data and stop: the cfg register will be loaded with the first byte and delay register will be loaded with the 2 others bytes.

#### Reading of a register:

Example 1: Reading of register 35 (STATUS): start followed by address b0 hex, AC = '0', then sub-address 35, AC = '0' and stop. Then start, address b1, AC = '0' and then data of register 35, AM = '1' and stop condition.

Example 2: Reading of registers 0 to 3: start followed by address b0 hex, AC = '0', and sub-address 0, AC = '0' and stop. Then start, address b1, AC = '0' and then first byte of register 0, AM = '0', second byte from register 1, AM = '0', third byte of register 2, AM = '0', fourth byte from register 3, AM = '1' and stop condition.

Figure 15: STV0116/PC Write Operation

Figure 16: STV0116/PC Read Operation

## **REGISTERS MAPPING AND DESCRIPTION**

- (\*) default mode on hard NRESET. (\*\*) default mode on TESTAUTO.

# Register 0 Control (Read/Write)

|             |                     | M                   | ISB                   |                                            |                                     |              |              |             |              | LSB          |

|-------------|---------------------|---------------------|-----------------------|--------------------------------------------|-------------------------------------|--------------|--------------|-------------|--------------|--------------|

|             |                     |                     | d7                    | d6                                         | d5                                  | d4           | d3           | d2          | d1           | d0           |

| Regis       | ster 0              | S                   | td1                   | std0                                       | sym1                                | sym0         | sys1         | sys0        | mod1         | mod0         |

| (*)         | std1<br>0<br>0<br>1 | std0<br>0<br>1<br>0 | PALI                  | dard select<br>BDGHI<br>N Argentina<br>C M |                                     |              |              |             |              |              |

| (*)         | sym1<br>0<br>1      |                     |                       | ole<br>ole : free-ru                       | n is active e                       |              |              |             | ositionned   | (with a time |

| (*)         | sym0<br>0<br>1      |                     | ODD                   | /EVEN inp                                  | nization sou<br>ut<br>tion of F fro |              | mode         |             |              |              |

| (*)         | sys1<br>0<br>1      |                     | Sync<br>Posit<br>Nega |                                            | oolarity                            |              |              |             |              |              |

|             | sys0                |                     |                       |                                            |                                     | N polarity ( | as input (sl | lave) or as | output (slav | e : synchro  |

| (*)         | 0<br>1              |                     | Sync                  |                                            | .ster))<br>D/EVEN fal<br>D/EVEN ris |              |              |             |              |              |

| (*)         | mod1<br>0<br>1      |                     | No re<br>Softv        | eset<br>vare reset                         |                                     |              |              |             |              |              |

| (*)<br>(**) | mod0<br>0<br>1      |                     | Slave<br>Mast         | e<br>er (freerun                           | forced)                             |              |              |             |              |              |

**Note**: Software reset is automatically disabled at I<sup>2</sup>C stop condition. Reset is active during 4 H27 periods.

## Register 1 Cfg (Read/Write)

|      |                        | MSB                             |                                                                                                        |             |                       |            |                |       | LSB |  |  |

|------|------------------------|---------------------------------|--------------------------------------------------------------------------------------------------------|-------------|-----------------------|------------|----------------|-------|-----|--|--|

|      |                        | d7                              | d6                                                                                                     | d5          | d4                    | d3         | d2             | d1    | d0  |  |  |

| Regi | ster 1                 | hsnvcs rstddfs flt1 syncok coki |                                                                                                        |             |                       |            |                |       |     |  |  |

| (*)  | hsnvcs<br>0<br>1       | Com                             | Output signal selection on VCS<br>Composite synchro<br>Horizontal synchro                              |             |                       |            |                |       |     |  |  |

|      | rstddfs<br>0 to 1<br>0 |                                 | Reset of DDFS (Direct Digital Frequency Synthetizer) Transition generates a pulse reset for oscillator |             |                       |            |                |       |     |  |  |

| (*)  | flt1<br>1<br>0         |                                 | ma pass ba<br>Hz, 0.45MI<br>Hz                                                                         |             | ly                    |            |                |       |     |  |  |

| (*)  | syncok<br>0<br>1       | Sync                            | hro availab<br>hro OFF<br>hro availab                                                                  | -           | e of no free-<br>= 0) | run active |                |       |     |  |  |

| (*)  | coki<br>0<br>1         | Colo<br>Colo<br>Colo            | r ON                                                                                                   | ed on C and | d CVBS (on            | CVBS only  | y in next rele | ease) |     |  |  |

Note: FOUR FILTERS FOR ENCODING NEEDS.

Luma passband filter (6.3MHz (BW = 5.75MHz with sinX/X D/A conversion))

Chroma passband filter (1.3MHz/1.8MHz: U/V and I, 1.8MHz/0.45MHz: Q, 1.8MHz: CR, CB for R, G, B encoding)

(chroma BW becomes 1.2MHz/1.7MHz, 0.45MHz, 1.7MHz with sinX/X DAC).

## Register 2 Delay\_msb (Read/Write)

MSB

|            | MSB |    |    |    |    |    |    | LSB |

|------------|-----|----|----|----|----|----|----|-----|

|            | d7  | d6 | d5 | d4 | d3 | d2 | d1 | d0  |

| Register 2 | d10 | d9 | d8 | d7 | d6 | d5 | d4 | d3  |

## Register 3 Delay Isb

|                        | d7 | d6 | d5 | d4       | d3       | d2       | d1       | d0       |

|------------------------|----|----|----|----------|----------|----------|----------|----------|

| Read Mode :            |    |    |    |          |          |          |          |          |

| Register 3 Write Mode: | d2 | d1 | d0 | Reg2, d4 | Reg2, d3 | Reg2, d2 | Reg2, d1 | Reg2, d0 |

| Register 3             | d2 | d1 | d0 | xx       | xx       | xx       | xx       | xx       |

d[10:0] sample polynomial counter at 27MHz

Sample polynomial counter  $(1 + x^2 + x^{11})$  value on which falling edge of F (ODD/EVEN signal) is detected on YCRCB (F is extracted from EAV word)

LSB

1st byte: 21 (hex 15), 2nd byte: 128 (hex 80) for PAL BDGHIN (625 lines)

1st byte: 201 (hex c9), 2nd byte: 128 (hex 80) for M (525 lines)

Sample polynomial counter value on which falling edge of ODD/EVEN is detected

(\*) 1st byte: 0, 2nd byte: 32 (hex 20) for PAL BDGHIN (625 lines)

1st byte: 0, 2nd byte: 32 (hex 20) for M (525 lines)

Note: Delay register should be loaded before Control register for synchro on YCRCB cross table of sample polynomial counter is given cech.txt

### Register Increment for ddfs (Digital Frequency Synthesizer) (Read/Write)

MSB

LSB (see Note)

d7

d6

d5

d4

d3

d2

d1

d0

|            | d7  | d6  | d5  | d4  | d3  | d2  | d1  | d0  |

|------------|-----|-----|-----|-----|-----|-----|-----|-----|

| Register 4 | xx  | xx  | d21 | d20 | d19 | d18 | d17 | d16 |

| Register 5 | d15 | d14 | d13 | d12 | d11 | d10 | d9  | d8  |

| Register 6 | d7  | d6  | d5  | d4  | d3  | d2  | d1  | d0  |

x x 0 0 1 0 1 0 1 0 0 0 0 0 1 0 0 1 1 0 0 0 1 1 PALBGHI

x x 0 0 1 0 0 0 0 1 1 1 1 1 0 0 1 1 0 1 1 1 1 0 0 PALM

f = 3.5795452MHz error = +0.2Hz

$f_{th} = 3579545 \pm 10 Hz$

f = 4.4336206MHz error = +1.85Hz

$f_{th} = 4433618.75 \pm 5Hz$

f = 3.5820558MHz error = -0.45Hz

$f_{th} = 3582056.25 \pm 5Hz$

f = 3.5756120MHz error = +0.51Hz

$f_{th} = 3575611.49 \pm 5Hz$

Note: 1 LSB = 6.43Hz

## Register Phase Offset for ddfs (Digital Frequency Synthesizer) (Read/Write)

MSB LSB d7 d6 d5 d4 d3 d1 d0 Register 7 o20 017 XXXXo21 019 018 016 Register 8 015 o14 o13 012 011 010 о9 80 Register 9 о5 02 00 ο7 06 о4 о3 01

(\*) Reset value depends on standard chosen in register 0

Register Palety (Read/Write)

|                                | MSB     |             |     |     |     |     |     | LSB |

|--------------------------------|---------|-------------|-----|-----|-----|-----|-----|-----|

|                                | d7      | d6          | d5  | d4  | d3  | d2  | d1  | d0  |

| Read Mode :                    |         |             |     |     |     |     |     |     |

| Register 10                    | Reg10,c | l5 Reg10,d5 | y75 | y74 | y73 | y72 | y71 | y70 |

| Register 11                    |         | l5 Reg11,d5 |     | y64 | y63 | y62 | y61 | y60 |

| Register 12                    |         | l5 Reg12,d5 |     | y54 | y53 | y52 | y51 | y50 |

| Register 13                    |         | l5 Reg13,d5 |     | y44 | y43 | y42 | y41 | y40 |

| Register 14                    |         | l5 Reg14,d5 |     | y34 | y33 | y32 | y31 | y30 |

| Register 15                    |         | l5 Reg15,d5 |     | y24 | y23 | y22 | y21 | y20 |

| Register 16                    |         | l5 Reg16,d5 |     | y14 | y13 | y12 | y11 | y10 |

| Register 17                    | Reg17,c | l5 Reg17,d5 | y05 | y04 | y03 | y02 | y01 | y00 |

| Write Mode :                   |         |             |     |     |     |     |     |     |

| Register 10                    | xx      | xx          | y75 | y74 | y73 | y72 | y71 | y70 |

| Register 11                    | XX      | XX          | y65 | y64 | y63 | y62 | y61 | y60 |

| Register 12                    | XX      | xx          | y55 | y54 | y53 | y52 | y51 | y50 |

| Register 13                    | XX      | XX          | y45 | y44 | y43 | y42 | y41 | y40 |

| Register 14                    | XX      | XX          | y35 | y34 | y33 | y32 | y31 | y30 |

| Register 15                    | XX      | XX          | y25 | y24 | y23 | y22 | y21 | y20 |

| Register 16                    | XX      | XX          | y15 | y14 | y13 | y12 | y11 | y10 |

| Register 17 NTSC               | XX      | XX          | y05 | y04 | y03 | y02 | y01 | y00 |

| Register 17 PAL (to be loaded) | XX      | xx          | 0   | 0   | 0   | 1   | 0   | 0   |

# 8 x 6 bit words for Y component.

| Default Value : |     | Y(hexa) | Color   | (100% white to black) |

|-----------------|-----|---------|---------|-----------------------|

|                 | 111 | 3B      | white   | y7x                   |

|                 | 110 | 28      | yellow  | y6x                   |

|                 | 101 | 14      | magenta | y5x                   |

|                 | 100 | 10      | red     | y4x                   |

|                 | 011 | 21      | cyan    | y3x                   |

|                 | 010 | 1D      | green   | y2x                   |

|                 | 001 | 09      | blue    | y1x                   |

|                 | 000 | 04      | black   | y0x                   |

Register Paletcr (Read/Write)

|              | MSB      |          |      |      |      |      |      | LSB  |

|--------------|----------|----------|------|------|------|------|------|------|

|              | d7       | d6       | d5   | d4   | d3   | d2   | d1   | d0   |

| Read Mode :  |          |          |      |      |      |      |      |      |

| Register 18  | Reg18,d5 | Reg18,d5 | cr75 | cr74 | cr73 | cr72 | cr71 | cr70 |

| Register 19  | Reg19,d5 | Reg19,d5 | cr65 | cr64 | cr63 | cr62 | cr61 | cr60 |

| Register 20  | Reg20,d5 | Reg20,d5 | cr55 | cr54 | cr53 | cr52 | cr51 | cr50 |

| Register 21  | Reg21,d5 | Reg21,d5 | cr45 | cr44 | cr43 | cr42 | cr41 | cr40 |

| Register 22  | Reg22,d5 | Reg22,d5 | cr35 | cr34 | cr33 | cr32 | cr31 | cr30 |

| Register 23  | Reg23,d5 | Reg23,d5 | cr25 | cr24 | cr23 | cr22 | cr21 | cr20 |

| Register 24  | Reg24,d5 | Reg24,d5 | cr15 | cr14 | cr13 | cr12 | cr11 | cr10 |

| Register 25  | Reg25,d5 | Reg25,d5 | cr05 | cr04 | cr03 | cr02 | cr01 | cr00 |

| Write Mode : |          |          |      |      |      |      |      |      |

| Register 18  | xx       | xx       | cr75 | cr74 | cr73 | cr72 | cr71 | cr70 |

| Register 19  | xx       | xx       | cr65 | cr64 | cr63 | cr62 | cr61 | cr60 |

| Register 20  | xx       | xx       | cr55 | cr54 | cr53 | cr52 | cr51 | cr50 |

| Register 21  | xx       | xx       | cr45 | cr44 | cr43 | cr42 | cr41 | cr40 |

| Register 22  | xx       | xx       | cr35 | cr34 | cr33 | cr32 | cr31 | cr30 |

| Register 23  | xx       | xx       | cr25 | cr24 | cr23 | cr22 | cr21 | cr20 |

| Register 24  | xx       | xx       | cr15 | cr14 | cr13 | cr12 | cr11 | cr10 |

| Register 25  | XX       | xx       | cr05 | cr04 | cr03 | cr02 | cr01 | cr00 |

8 x 6 bit words for CR component.

| Default Value : | R0, B0, C0 | CR(hexa) | Color   | (75% white to black) |

|-----------------|------------|----------|---------|----------------------|

|                 | 111        | 20       | white   | cr7x                 |

|                 | 110        | 23       | yellow  | cr6x                 |

|                 | 101        | 31       | magenta | cr5x                 |

|                 | 100        | 35       | red     | cr4x                 |

|                 | 011        | 0B       | cyan    | cr3x                 |

|                 | 010        | 0E       | green   | cr2x                 |

|                 | 001        | 1C       | blue    | cr1x                 |

|                 | 000        | 20       | black   | cr0x                 |

Register Paletcb (Read/Write)

|              | MSB      |          |      |      |      |      |      | LSB  |

|--------------|----------|----------|------|------|------|------|------|------|

|              | d7       | d6       | d5   | d4   | d3   | d2   | d1   | d0   |

| Read Mode :  |          |          |      |      |      |      |      |      |

| Register 26  | Reg26,d5 | Reg26,d5 | cb75 | cb74 | cb73 | cb72 | cb71 | cb70 |

| Register 27  | Reg27,d5 | Reg27,d5 | cb65 | cb64 | cb63 | cb62 | cb61 | cb60 |

| Register 28  | Reg28,d5 | Reg28,d5 | cb55 | cb54 | cb53 | cb52 | cb51 | cb50 |

| Register 29  | Reg29,d5 | Reg29,d5 | cb45 | cb44 | cb43 | cb42 | cb41 | cb40 |

| Register 30  | Reg30,d5 | Reg30,d5 | cb35 | cb34 | cb33 | cb32 | cb31 | cb30 |

| Register 31  | Reg31,d5 | Reg31,d5 | cb25 | cb24 | cb23 | cb22 | cb21 | cb20 |

| Register 32  | Reg32,d5 | Reg32,d5 | cb15 | cb14 | cb13 | cb12 | cb11 | cb10 |

| Register 33  | Reg33,d5 | Reg33,d5 | cb05 | cb04 | cb03 | cb02 | cb01 | cb00 |

| Write Mode : |          |          |      |      |      |      |      |      |

| Register 26  | xx       | xx       | cb75 | cb74 | cb73 | cb72 | cb71 | cb70 |

| Register 27  | xx       | xx       | cb65 | cb64 | cb63 | cb62 | cb61 | cb60 |

| Register 28  | xx       | xx       | cb55 | cb54 | cb53 | cb52 | cb51 | cb50 |

| Register 29  | xx       | xx       | cb45 | cb44 | cb43 | cb42 | cb41 | cb40 |

| Register 30  | xx       | xx       | cb35 | cb34 | cb33 | cb32 | cb31 | cb30 |

| Register 31  | xx       | xx       | cb25 | cb24 | cb23 | cb22 | cb21 | cb20 |

| Register 32  | xx       | xx       | cb15 | cb14 | cb13 | cb12 | cb11 | cb10 |

| Register 33  | XX       | XX       | cb05 | cb04 | cb03 | cb02 | cb01 | cb00 |

# 8 x 6 bit words for CB component.

Default Value: R0, B0, C0 CB(hexa) Color (75% white to black)

| 111 | 20 | white   | cb7x |

|-----|----|---------|------|

| 110 | 0B | yellow  | cb6x |

| 101 | 2E | magenta | cb5x |

| 100 | 19 | red     | cb4x |

| 011 | 27 | cyan    | cb3x |

| 010 | 12 | green   | cb2x |

| 001 | 35 | blue    | cb1x |

| 000 | 20 | black   | cb0x |

# **Register 34 Autotest**

MSB

|              | d7 | d6 | d5 | d4 | d3 | d2 | d1 | d0 |

|--------------|----|----|----|----|----|----|----|----|

| Testauto Off | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| Testauto On  | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

# Register 35 Status (Read)

|       |                     | М                   | SB                    |                                             |                                         |                            |             |            |               | LSB         |

|-------|---------------------|---------------------|-----------------------|---------------------------------------------|-----------------------------------------|----------------------------|-------------|------------|---------------|-------------|

|       |                     |                     | <b>17</b>             | d6                                          | d5                                      | d4                         | d3          | d2         | d1            | d0          |

| Regis | ter 35              | h                   | ok                    | atfr                                        | std1                                    | std0                       | sym1        | sym0       | sys1          | sys0        |

|       | hok<br>0<br>1       |                     | Multi                 | ming decoo<br>ole errors<br>1 error         | ding of ODE                             | D/EVEN sig                 | nal from YC | CRCB       |               |             |

|       | atfr<br>0<br>1      |                     | Enco                  | der not syn                                 |                                         | nchronized                 |             |            |               |             |

| (*)   | std1<br>0<br>0<br>1 | std0<br>0<br>1<br>0 | PAL                   | dard selecti<br>BDGHI<br>N (Argentin<br>C M |                                         |                            |             |            |               |             |

| (*)   | sym1<br>0<br>1      |                     |                       | ole<br>de : free-ru                         |                                         | n case of O<br>ne) and sla |             | suppressio | n (with a tin | ne constant |

| (*)   | sym0<br>0<br>1      |                     | ODD                   | /EVEN inpu                                  |                                         | rce in slave<br>m EAV)     | e mode      |            |               |             |

| (*)   | sys1<br>0<br>1      |                     | Sync<br>Posit<br>Nega |                                             | oolarity                                |                            |             |            |               |             |

| (*)   | sys0<br>0<br>1      |                     | Sync                  | hro on ODI                                  | : ODD/EVE<br>D/EVEN fall<br>D/EVEN risi | ling edge                  |             |            |               |             |

Note: SIGNAL QUALITY DETECTOR by use of hamming decoding on EAV, SAV in YCRCB input.

## Register Compression (Read/Write)

| •            | `   | ,   |     |     |     |     |     |     |

|--------------|-----|-----|-----|-----|-----|-----|-----|-----|

|              | MSB |     |     |     |     |     |     | LSB |

|              | d7  | d6  | d5  | d4  | d3  | d2  | d1  | d0  |

| Read Mode:   |     |     |     |     |     |     |     |     |

| Register 36  | lc9 | lc8 | lc7 | lc6 | lc5 | lc4 | lc3 | lc2 |

| Register 37  | lc1 | lc0 | lf9 | lf8 | lf7 | lf6 | lf5 | lf4 |

| Register 38  | lf3 | lf2 | lf1 | lf0 | 0   | 0   | 0   | 0   |

| Write Mode : |     |     |     |     |     |     |     |     |

| Register 36  | lf9 | lf8 | lf7 | lf6 | lf5 | lf4 | lf3 | lf2 |

| Register 37  | lf1 | IfO | lc9 | lc8 | lc7 | lc6 | lc5 | lc4 |

| Register 38  | lc3 | lc2 | lc1 | lc0 | x   | x   | ×   | ×   |

It is used to compress on line fonctionnal patterns. "Ic" is the line number value\* on which the polynomial line counter  $(1 + x^3 + x^{10})$  is forced (when it occurs) with 'lf' value.

(\*)

On reset 'lf' = 001, 'lc' = 000 (line counter never goes to 000 value) 1st byte : 00, 2nd byte : 00 hex, 3rd byte : 10 (Read) 1st byte: 00, 2nd byte: 40 hex, 3rd byte: 00 (Write)

## **APPLICATION DIAGRAM**

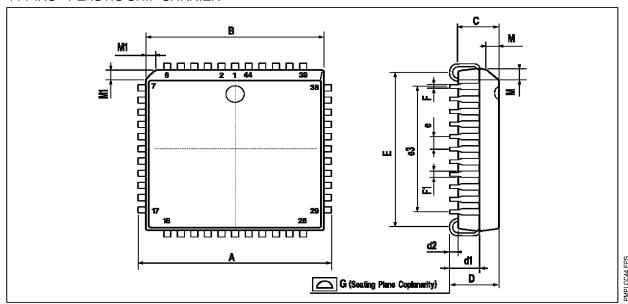

#### **PACKAGE MECHANICAL DATA**

44 PINS - PLASTIC CHIP CARRIER

| Dimensions | Millimeters |      |       | Inches |       |       |

|------------|-------------|------|-------|--------|-------|-------|

| Dimensions | Min.        | Тур. | Max.  | Min.   | Тур.  | Max.  |

| Α          | 17.4        |      | 17.65 | 0.685  |       | 0.695 |

| В          | 16.51       |      | 16.65 | 0.650  |       | 0.656 |

| С          | 3.65        |      | 3.7   | 0.144  |       | 0.146 |

| D          | 4.2         |      | 4.57  | 0.165  |       | 0.180 |

| d1         | 2.59        |      | 2.74  | 0.102  |       | 0.108 |

| d2         |             | 0.68 |       |        | 0.027 |       |

| E          | 14.99       |      | 16    | 0.590  |       | 0.630 |

| е          |             | 1.27 |       |        | 0.050 |       |

| e3         |             | 12.7 |       |        | 0.500 |       |

| F          |             | 0.46 |       |        | 0.018 |       |

| F1         |             | 0.71 |       |        | 0.028 |       |

| G          |             |      | 0.101 |        |       | 0.004 |

| М          |             | 1.16 |       |        | 0.046 |       |

| M1         |             | 1.14 |       |        | 0.045 |       |

Information furnished is believed to be accurate and reliable. However, SGS-THOMSON Microelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No licence is granted by implication or otherwise under any patent or patent rights of SGS-THOMSON Microelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. SGS-THOMSON Microelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of SGS-THOMSON Microelectronics.

#### © 1996 SGS-THOMSON Microelectronics - All Rights Reserved

Purchase of I<sup>2</sup>C Components of SGS-THOMSON Microelectronics, conveys a license under the Philips I<sup>2</sup>C Patent. Rights to use these components in a I<sup>2</sup>C system, is granted provided that the system conforms to the I<sup>2</sup>C Standard Specifications as defined by Philips.

## SGS-THOMSON Microelectronics GROUP OF COMPANIES

Australia - Brazil - Canada - China - France - Germany - Hong Kong - Italy - Japan - Korea - Malaysia - Malta - Morocco The Netherlands - Singapore - Spain - Sweden - Switzerland - Taiwan - Thailand - United Kingdom - U.S.A.