SSP1600

DSP

Samsung is a pioneer in the DSP core approach, which is a high performing and flexible family of DSP core based ASDSP(Application Specifics Digital Signal Processor). The DSP core architecture and instruction set are designed simplicity and flexibility. The DSP core contains only the most essential DSP function blocks. Because all internal buses are accessible externally. The ASDSP is an application specifics integrated circuit that incorporates a programmable digital signal processor core. The ASDSP approach allows the system designer to integrate a programmable dsp core, interface logic, peripheral, extra memory into a single integrated circuit. Typically, the custom circuitry on a ASDSP is implemented either in standard cell or gate array. All methods used samsung process by 0.8um double metal CMOS technology.

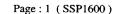

The SSP1600 is based on CD2400 licensed by Clarkspur Inc. It uses 0.8um CMOS(CSP4H) and can perform up to 20 MHz at 5V. The SSP1600 DSP cores have the following on-chip functions: two independent high-speed RAM banks, a 16 x 16 multiply unit, an 24-bit ALU , RAM address pointers, a status register, a program control unit, and an external bus control unit. The SSP1600 can address up to 64K-word of external ROM over an external data bus. The actual size of the external ROM area used depends upon the requirements of the individual application. The SSP1600 has five 16-bit buses and one 24-bit bus; program address (PA) bus, program data (PD) bus, multiplier (M) bus, external (EXT) bus, subsidiary (S) bus, data (D) bus, mpya instructions (add, load, multiply, and modify RAM address pointer) are executed efficiently within one machine cycle. The condition flags in the status register (ST) are set or cleared by the corresponding ALU operations. Values for the status register control bits are loaded by application software or through the I/O pins USR0, USR1, ST5, and ST6.

The system stack has six hardware levels and operates using Push and Pop operations. The pins EA [2:0], ESB, and R/WB are used to control the EXT bus, and the RESB, INTO, INT1, INT2, and SS pins are used to control system functions.

#### **Key Features**

- 16-bit fixed point arithmetic

- ACC + A x B -> ACC; MAC operation in 25 ns using pipelined multiplier

- 16x16-bit pipelined multiply with 24-bit output

- 24-bit ALU operation

- 512-word data RAM; RAM0, RAM1

- Eight 8-bit RAM point register are existed, R0 ~ R3 are for RAM0, R4 ~ R7 are for RAM1.

- RAM pointer registers for easy circular buffer operation

- Simple instruction set

- User defined I/Os

- Up to 64K word Program Memory which can be readable and writable

- SSP1600 EVA Chip has two 256-word SRAM for each RAM banks

- 20 MIPS @ 5.0 Volt

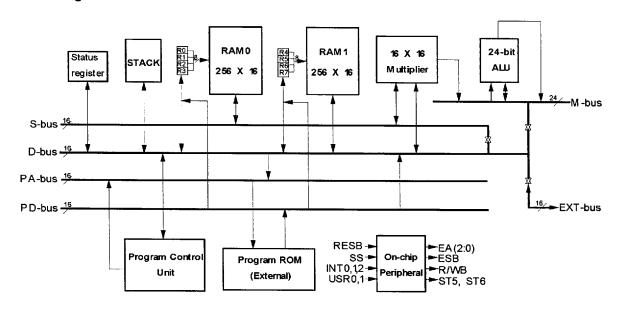

- 68 pin PLCC (evaluation version)

- 0.8um double metal CMOS (CSP4H)

- Excepted core size (except PAD, Data RAM): 3600um x 2400um

#### Design Tools

As part of its total support commitment, SASUNG backs up the SSP1600 with a set of high level software and hardware tools.

- Software Tools : running on PC

- Assembler (ASM1600)

- ► Simulator (SIM1600)

- Hardware Tools : running on PC

- ► Real-time Emulator (SDE1600)

- ► Algorithm Development Board (SDAP1600)

- Design Tools: running on SUN (Unix)

- ► Verilog model

- Macrocells dedicated to the DSP core to build user's applications.

- Standard cell library, I/O library and Data path generator

- Memory Generator (ROM, RAM)

CD-ROM(Edition 3.0) This Data Sheet is subject to change without notice.

(C) 1996 Samsung Electronics Printed in Korea.

### Block Diagram

### Pin Layout

CD-ROM(Edition 3.0) This Data Sheet is subject to change without notice.

(C) 1996 Samsung Electronics Printed in Korea.

Page: 2 (SSP1600)

# Pin Descriptions

| Name Number I/O |                  |     | Description                                                      |

|-----------------|------------------|-----|------------------------------------------------------------------|

| CK1             | 51               | 0   | Clock                                                            |

| PH10B           | 52               | l   | Internal clock output Inverted output of PH1 generated from CK1  |

| RESB            | 50               | l   | Asynchronous step Effective when CK1 is rising                   |

| ss              | 53               | 1   | Asynchronous single step Effective when CK1 of a cycle is rising |

| INT0            | 56               |     | Interrupt request 0                                              |

| INT1            | 57               | 1   | Interrupt request 1                                              |

| INT2            | 58               |     | Interrupt request 2                                              |

| PA0-PA15        | 27-35 &<br>37-43 | 0   | Program address                                                  |

| PAD0-PD15       | 11-26            | I/O | Program data                                                     |

| EXT0-EXT15      | 1-9 &<br>61-68   | 1/0 | External data bus                                                |

| EA0-EA2         | 44-46            | 0   | External register address                                        |

| ESB             | 47               | 0   | External data strobe                                             |

| R/WB            | 48               | 0   | Read/write timing signal for EXT bus                             |

| USR0            | 54               | !   | User input 0                                                     |

| USR1            | 55               | 1   | User input 1                                                     |

| VDD             | 36               | ı   | + 5 Volt                                                         |

| vss             | 10,68            | ı   | GND                                                              |

| ST5<br>ST6      | 59<br>60         | 0   | User output 0 User output 1                                      |

# **Electrical Characteristics**

# Absolute Maximum Ratings

| Characteristics             | Symbol           | Value                         | Unit |  |

|-----------------------------|------------------|-------------------------------|------|--|

| $V_{DD}$ to $V_{SS}$        | V <sub>DD</sub>  | 0.7                           | V    |  |

| Input voltage               | Vı               | $V_{DD}$ + 0.5 to - 0.5       | V    |  |

| Output voltage              | Vo               | V <sub>DD</sub> + 0.5 to -0.5 | V    |  |

| Storage temperature         | T <sub>STG</sub> | -65 to + 150                  | °C   |  |

| Lead temperature(Soldering) | TL               | Less than 300                 | ъ    |  |

# DC Characteristics

| Characteristics                        | Symbol 5        | Condition                 | Min                  | Тур | Max                | Unit |

|----------------------------------------|-----------------|---------------------------|----------------------|-----|--------------------|------|

| Operating current                      | I <sub>DD</sub> | CK = 20 MHz               |                      | 40  |                    | mA   |

| Input voltage high                     | V <sub>IH</sub> |                           | 0.9V <sub>DD</sub>   |     |                    | V    |

| Output voltage low                     | VIL             |                           |                      |     | 0.1V <sub>DD</sub> | V    |

| Input Leakage current                  | h               |                           |                      | 1   |                    | μA   |

| Output voltage high                    | V <sub>OH</sub> | I <sub>OH</sub> = -100 μA | V <sub>00</sub> =0.2 |     |                    | V    |

| Output voltage low                     | Vol             | I <sub>οι</sub> = 0.5 mA  |                      |     | 0.5                | V    |

| Output current in high impedance state | loz             |                           |                      |     | 5                  | μА   |

# **AC Characteristics**

| AC Characteristics             | Symbol            | Min  | Тур | Max | Unit |

|--------------------------------|-------------------|------|-----|-----|------|

| Clock cycle time               | T <sub>CY</sub>   | 1000 | 50  |     |      |

| Clock pulse width              | P <sub>ww</sub>   | 20   |     |     |      |

| EA,R/WB delay from CK1         | E <sub>AD</sub>   |      | 10  |     |      |

| EXT pre-charge delay from CK1  | T <sub>1P</sub>   |      | 13  |     | -    |

| EXT floating delay from CK1    | T <sub>1F</sub>   |      | 13  |     |      |

| EXT data output delay from CK1 | T <sub>RD</sub>   |      | 18  |     |      |

| EXT data output hold from CK1  | Тхн               | 8    |     |     | 1    |

| EXT data input setup time      | Txes              | 5    |     |     | ns   |

| EXT data input hold time       | $T_{xRH}$         | 8    |     |     |      |

| ESB delay time                 | TEWRD             |      | 8   |     |      |

| PA delay from CK1              | T <sub>PAD</sub>  |      | 8   |     | 1    |

| PD input setup time            | T <sub>PDS</sub>  |      | 5   |     |      |

| PD input hold time             | ТРОН              | 8    |     |     |      |

| SS setup time                  | T <sub>CTLS</sub> | 3    |     |     |      |

| SS hold time                   | T <sub>CTLH</sub> | 8    |     |     | 1    |