| TADLE OF OCUTENTS BISC.               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TABLE OF CONTENTS                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 1. GENERAL DESCRIPTION                | 卡场网                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2. FEATURES                           | and the second s |

| 3. ORDERING INFORMATION               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5. FUNCTIONAL BLOCK DESCRIPTIONS      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| LCD Polarity Reverse Signal Generator |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Clock Signal Generator                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| -V1 Discharge Circuit                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Column Driver Voltage Generator       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Row Driver Voltage Generator          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Row Driver Voltage Conversion Circuit |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| VDD_ROW Voltage Generator             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| +V1 Voltage Generator                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 6. PINS ASSIGNMENT                    | A THE WWW.DZSC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 7. PIN DESCRIPTION                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 8. DC CHARACTERISTICS                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Maximum Ratings                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 9. Electrical Characteristics         | <u> </u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

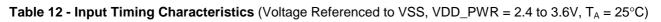

| 10. AC CHARACTERISTICS                | A CEE EL W.DZSG.00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Input Timing Characteristics          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

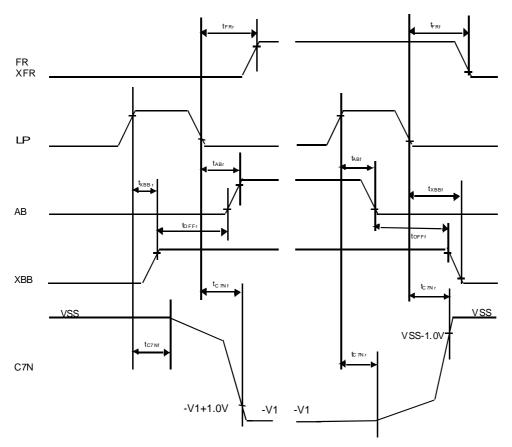

| Output Timing Characteristics         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 11. EXPLANATION OF FUNCTIONS          | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                       | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| LCD Polarity Reverse Signal Generator |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| LCD Polarity Reverse Signal Generator | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Contrast Control Circuit                          | 15 |

|---------------------------------------------------|----|

| +V1 Voltage Generator                             | 15 |

| -V1 and +V1 Discharge Circuit                     | 16 |

| Power Up and Power Down Sequence                  | 16 |

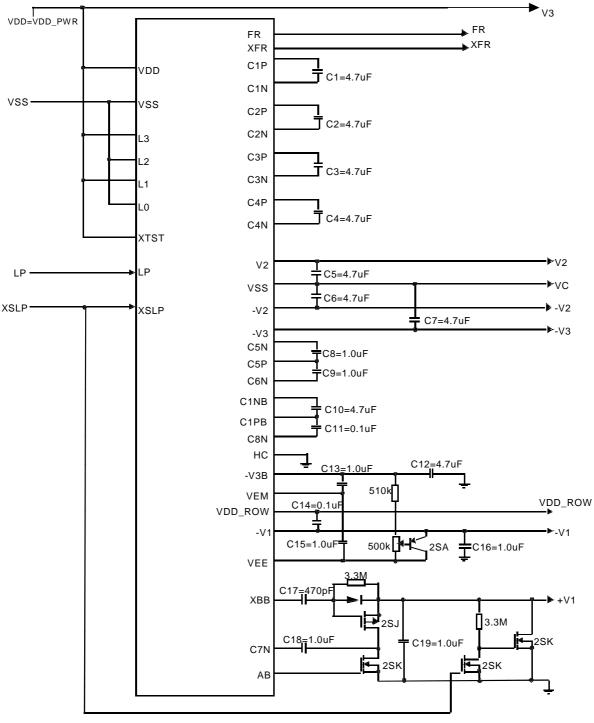

| 12. APPLICATION CIRCUIT (SSD1730 5X STEP-UP MODE) | 17 |

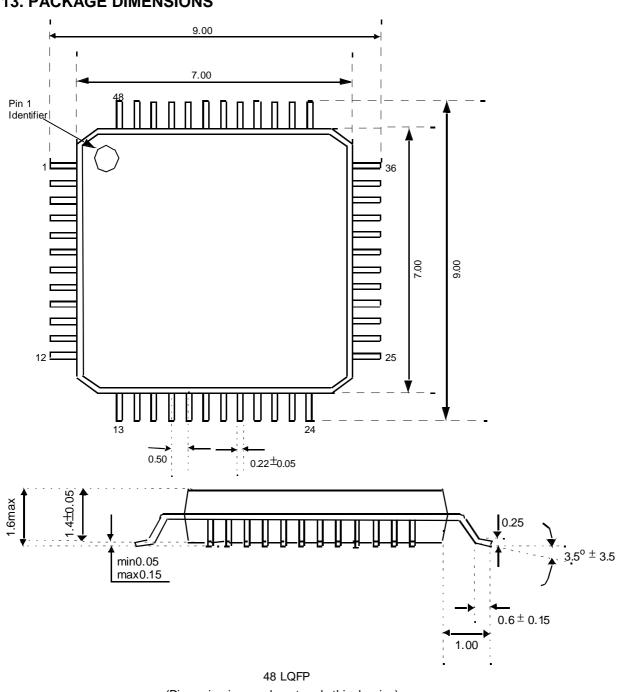

| 13. PACKAGE DIMENSIONS                            | 18 |

# SOLOMON SYSTECH LIMITED SEMICONDUCTOR TECHNICAL DATA

# SSD1730

# Advanced Infomation

# SSD1730 MLA Power Chip CMOS

### **1. GENERAL DESCRIPTION**

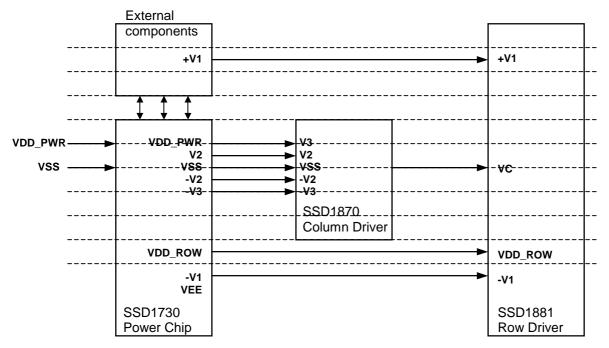

The SSD1730 is a power chip for operating four-line MLA (Multi Line Addressing) LCD drivers. It consists of a CMOS charge pump-type voltage converter that can generate all the bias voltages required for the four-line MLA drive based on a single power supply input.

This can be used for the system that is formed by a column (segment) driver such as SSD1870 and a row (common) driver such as SSD1881. Such type of display system is able to produce a module with lower power consumption when comparing with the conventional driving method.

# 2. FEATURES

- Single Power Supply Operation, +2.4V to +3.6V

- Low current consumption

- Two step-up modes, 5X or 6X step-up by internal charge pump DC/DC converter

- Internal LCD voltage generator to generate all LCD voltages required for 4-line MLA driving

External contrast control

- Internal –V1 discharge circuit to discharge the residual charge at the row driver negative voltage-side power supply voltage terminal –V1

- Internal "power off" function using an external signal

- Equipped internally with a LCD polarity reverse signal generator

- Polarity reversed period in the range of 2P to 17P

- Available in 48 pin QFP package (0.5 mm terminal pitch)

# **3. ORDERING INFORMATION**

| Ordering Part Number | Package Dimension | Package Form |

|----------------------|-------------------|--------------|

| SSD1730QL3           | 7 mm x 7mm        | 48 LQFP      |

#### Table 1 - Ordering Information

This document contains information on a new product. Specifications and information herein are subject to change without notice. IC manufactured under Motif license including U.S. Patent No. 5,420,604

SOLOMON

Rev 2.0

04/2002

Copyright © 2001 SOLOMON Systech Limited

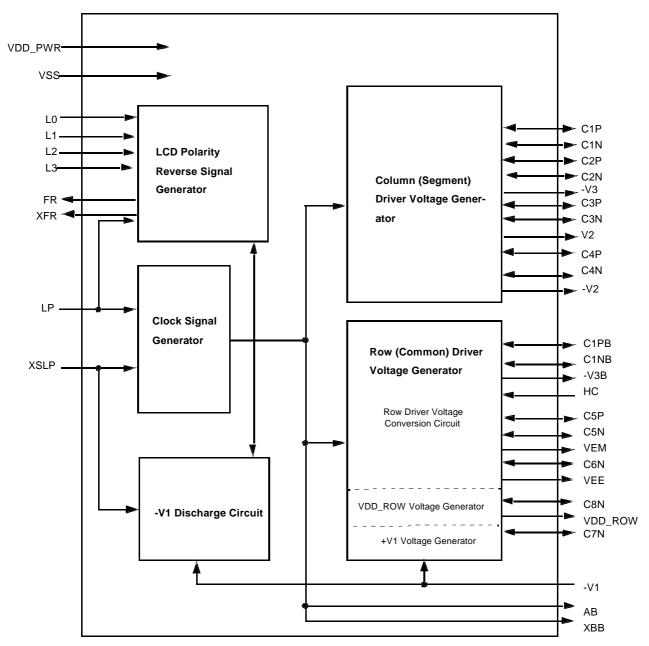

Figure 1 - Block Diagram

# 5. FUNCTIONAL BLOCK DESCRIPTIONS

### LCD Polarity Reverse Signal Generator

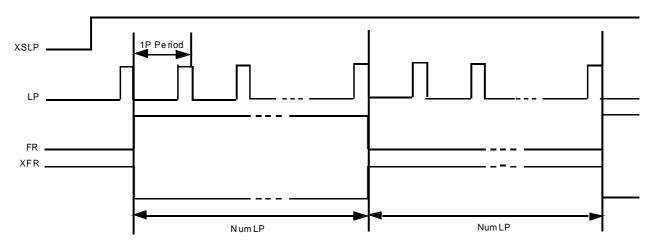

This circuit generates the polarity reverse signals FR and XFR from the pulse signal LP. The polarity reversal interval is controlled by four pins L0, L1, L2 & L3 and the range is from 2P to 17P (1P is equal to one LP period), Table 15 shows their relationship. The polarity of the FR signal and the XFR signal are mutually opposite, so that the upper and lower screens can be driven mutually in opposite phases when a two-screen drive panel is used.

### **Clock Signal Generator**

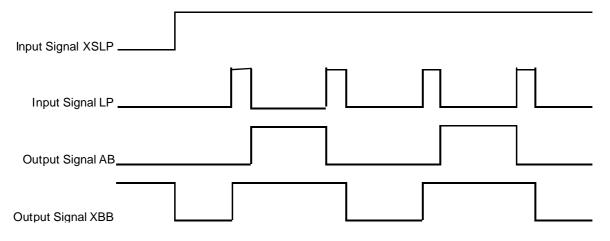

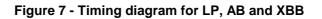

This circuit generates the clock for the charge pump from the pulse signal LP. When the display control signal XSLP is set to VSS, the clock will stop and the voltage converter will halt. For normal display mode, XSLP must be tied to VDD\_PWR. Besides, this circuit also generates the signals AB & XBB which are the clocks for the column driver voltage generator and the row driver voltage generator. Figure 7 shows their timing characteristics.

# -V1 Discharge Circuit

When the display is off or the power is off, this circuit will discharge the residual charges at the negative voltage level-side power supply voltage terminal –V1 of the row driver.

# **Column Driver Voltage Generator**

This circuit accompanying with external components generates voltages for column driver. In SSD1730, three voltage outputs including V2, -V2 and -V3 will be generated and their voltage levels are based on the supply voltage VDD\_PWR. Their relationship is V2 = VDD\_PWR/2, -V2 = -(VDD\_PWR/2) and  $-V3 = -VDD_PWR$ .

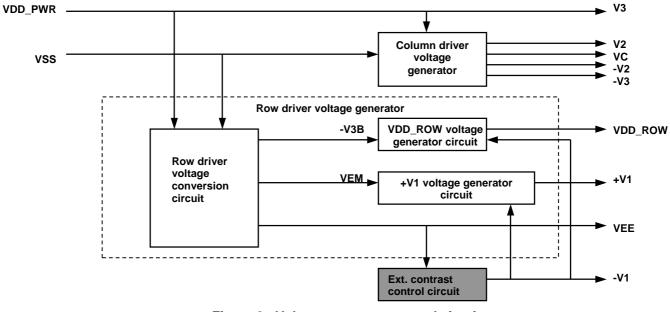

### **Row Driver Voltage Generator**

This voltage generator consists of three circuits (1) Row driver voltage conversion circuit, (2) VDD\_ROW voltage generator and (3) +V1 voltage generator.

#### **Row Driver Voltage Conversion Circuit**

This circuit generates VEE voltage which is used to generate +V1 & -V1 power supply voltages for row driver. There are two step-up modes 5X and 6X which are set by the HC pin. When HC pin is tied to VSS, 5X step-up mode is chosen. When HC pin is tied to -V3B, 6X step-up mode is chosen.

In SSD1730, VDD\_PWR is taken as the reference, VEE is equal to -4 x VDD\_PWR at 5X step-up mode while VEE is equal to -5 x VDD\_PWR at 6X step-up mode.

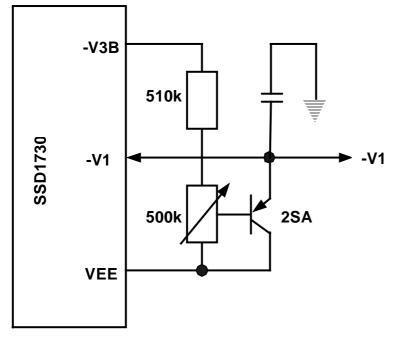

For the contrast adjustment, it is performed through the use of an external emitter follower circuit to adjust VEE to generate –V1, this contrast control circuit is shown in Figure 9.

#### VDD\_ROW Voltage Generator

VDD\_ROW voltage generator is used to generate VDD\_ROW, which is the power supply to the logic circuit of a row driver.

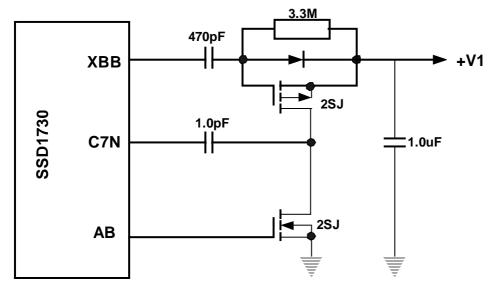

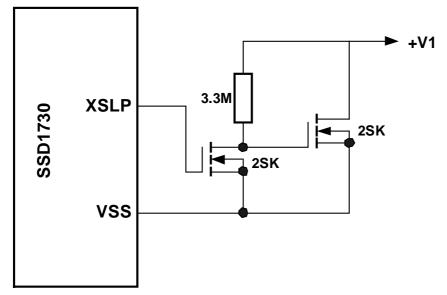

#### +V1 Voltage Generator

+V1 voltage generator accompanies with an external MOS transistor to generate +V1 voltage, which is required for the row driver. Figure 10 shows the accompanying external circuit for generating +V1 voltage.

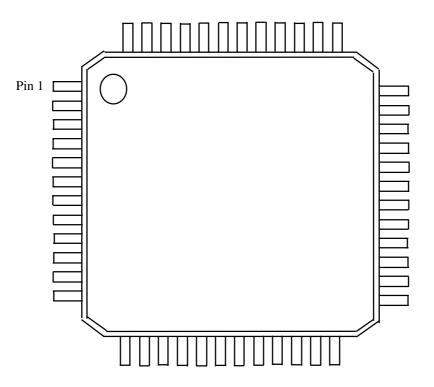

# 6. PINS ASSIGNMENT

The package of SSD1730 is 48 LQFP and Table 2 shows its pin assignment.

# Figure 2 - Pinout Diagram

| Pin# | Signal Name | Pin# | Signal Name | Pin# | Signal Name | Pin# | Signal<br>Name |

|------|-------------|------|-------------|------|-------------|------|----------------|

| 1    | -V1         | 13   | -V3B        | 25   | NC2         | 37   | LO             |

| 2    | C8N         | 14   | C1NB        | 26   | NC 3        | 38   | L1             |

| 3    | VDD_ROW     | 15   | VSS         | 27   | -V3         | 39   | L2             |

| 4    | C7N         | 16   | C1PB        | 28   | C2P         | 40   | L3             |

| 5    | VSS         | 17   | VDD_PWR     | 29   | VDD_PWR     | 41   | VSS            |

| 6    | VEE         | 18   | C4N         | 30   | C1P         | 42   | LP             |

| 7    | C6N         | 19   | -V2         | 31   | VSS         | 43   | FR             |

| 8    | VEM         | 20   | C4P         | 32   | C3N         | 44   | XFR            |

| 9    | C5N         | 21   | -V3         | 33   | V2          | 45   | XSLP           |

| 10   | HC          | 22   | VSS         | 34   | NC4         | 46   | XTST           |

| 11   | NC1         | 23   | C1N         | 35   | C3P         | 47   | AB             |

| 12   | C5P         | 24   | C2N         | 36   | VDD_PWR     | 48   | XBB            |

Table 2 - Pin Assignment Table

SSD1730

4

# 7. PIN DESCRIPTION

# Key:

I =Input O =Output I/O = Bi-Directional (Input/Output) P = Power pin NC = Dummy pin

| Pin Name | Туре | Pin#               | Description      |

|----------|------|--------------------|------------------|

| VDD_PWR  | Р    | 17, 29 &36         | Power supply pin |

| VSS      | Р    | 5, 15, 22, 31 & 41 | Ground pin       |

Table 3 - Power Supply Pins

| Pin Name | Туре | Pin#     | Description                                                                                                                                                        |

|----------|------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| L0 to L3 | I    | 37 to 40 | These input pins are used to set the polarity reversal interval ranging from 2P to 17P.                                                                            |

| FR       | 0    | 43       | This is an output pin and the FR signal is generated from the LCD polarity reverse signal generator.                                                               |

| XFR      | 0    | 44       | This is an output pin and the XFR signal is also<br>generated from the LCD polarity reverse signal<br>generator. This signal is a reverse phase from FR<br>signal. |

Table 4 - Pins for frame signal generator

| Pin Name | Туре | Pin# | Description                                                                                                                                                                                                                                |

|----------|------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LP       | I    | 42   | This input pin is used to generate the charge pump<br>clock and the polarity reverse signal FR and XFR.<br>A pulse signal with a period of 1P should be fed<br>into this pin.                                                              |

| XSLP     | 1    | 45   | This input pin is used to switch on or off the display. When it is set to VSS level, the clock and the operations of the voltage converter will be stop. The display will be off. When it is set to VDD_PWR level, the display will be on. |

Table 5 - Pins for clock signal generator

| Pin Name | Туре | Pin# | Description                                                                                                                                                                                                                                                                            |

|----------|------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -V1      | I/O  | 1    | This is the row driver negative voltage level power<br>supply voltage terminal. The –V1 is an input signal<br>to the contrast adjustment circuit this is used to<br>adjust the display contrast. Besides, this is the<br>power supply to the +V1 voltage generator control<br>circuit. |

Table 6 - Pins for –V1 discharge circuit

| Pin Name | Туре | Pin#   | Description                                                                                                                 |

|----------|------|--------|-----------------------------------------------------------------------------------------------------------------------------|

| C1P      | I/O  | 30     | The positive-side connection terminal for a capacitor C1 to generate -V3 output voltage. (Refer to the application circuit) |

| C1N      | I/O  | 23     | The negative-side connection terminal for a capacitor C1 to generate -V3 output voltage. (Refer to the application circuit) |

| C2P      | I/O  | 28     | The positive-side connection terminal for a capacitor C2 to generate -V3 output voltage. (Refer to the application circuit) |

| C2N      | I/O  | 24     | The negative-side connection terminal for a capacitor C2 to generate -V3 output voltage. (Refer to the application circuit) |

| -V3      | 0    | 21, 27 | This is -V3 output voltage, which is for the power supply of segment driver.                                                |

| C3P      | I/O  | 35     | The positive-side connection terminal for a capacitor C3 to generate V2 output voltage. (Refer to the application circuit)  |

| C3N      | I/O  | 32     | The negative-side connection terminal for a capacitor C3 to generate V2 output voltage. (Refer to the application circuit)  |

| V2       | I/O  | 33     | This is V2 output voltage which is for the power supply of segment driver.                                                  |

| C4P      | I/O  | 20     | The positive-side connection terminal for a capacitor C4 to generate -V2 output voltage. (Refer to the application circuit) |

| C4N      | I/O  | 18     | The negative-side connection terminal for a capacitor C4 to generate -V2 output voltage. (Refer to the application circuit) |

| -V2      | 0    | 19     | This is -V2 output voltage which is for the power supply of segment driver.                                                 |

Table 7 - Pins for column (segment) driver voltage generator

| Pin Name | Туре                               | Pin#         | Description                                                                                                                                                           |  |  |  |  |

|----------|------------------------------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|          | Pins for VDD_ROW voltage generator |              |                                                                                                                                                                       |  |  |  |  |

| C8N      | I/O                                | 2            | The negative-side connection terminal for a<br>capacitor C11 to generate VDD_ROW output<br>voltage. (Refer to the application circuit)                                |  |  |  |  |

| VDD_ROW  | 0                                  | 3            | This is VDD_ROW output voltage which is the power supply to the logic circuit part of row driver.                                                                     |  |  |  |  |

|          | Pins for +V1 voltage generator     |              |                                                                                                                                                                       |  |  |  |  |

| AB       | 0                                  | 47           | This is the clock output for the external n-channel MOS transistor control in the +V1 voltage generator circuit.                                                      |  |  |  |  |

| XBB      | 0                                  | 48           | This is the clock output for the external p-channel MOS transistor control in the +V1 voltage generator circuit.                                                      |  |  |  |  |

| C7N      | I/O                                | 4            | The negative-side connection terminal for a capacitor C18 to generate +V1 output voltage. (Refer to the application circuit)                                          |  |  |  |  |

|          |                                    | Pins for row | driver voltage conversion circuit                                                                                                                                     |  |  |  |  |

| C1PB     | I/O                                | 16           | The positive-side connection terminal for a capacitor C10 and C11 to generate -V3B output voltage. (Refer to the application circuit)                                 |  |  |  |  |

| C1NB     | I/O                                | 14           | The negative-side connection terminal for a capacitor C10 to generate -V3B output voltage. (Refer to the application circuit)                                         |  |  |  |  |

| -V3B     | 0                                  | 13           | This is -V3B output voltage equipped as the middle voltage level for generating VEE output voltage.                                                                   |  |  |  |  |

| HC       | 1                                  | 10           | This pin is used to select 5X or 6X step-up mode.<br>When it is tied to VSS, 5X step-up mode will be<br>set. When it is tied to -V3B, 6X step-up mode will<br>be set. |  |  |  |  |

| C5P      | I/O                                | 12           | The positive-side connection terminal for a capacitor C8 and C9 to generate VEM output voltage. (Refer to the application circuit)                                    |  |  |  |  |

| C5N      | I/O                                | 9            | The negative-side connection terminal for a capacitor C8 to generate VEM output voltage. (Refer to the application circuit)                                           |  |  |  |  |

| VEM      | 0                                  | 8            | This is VEM output voltage equipped as the middle voltage level for generating VEE output voltage.                                                                    |  |  |  |  |