# **RC4153**

# Voltage-to-Frequency Converter

#### **Features**

- 0.1 Hz to 250 kHz dynamic range

- 0.01% F.S. maximum nonlinearity error— 0.1Hz to 10 kHz

- 50 ppm/°C maximum gain temperature coefficient (external reference)

- Few external components required

## Description

The 4153 sets a new standard for ease of application and high frequency performance in monolithic voltage-to-frequency converters. This voltage-to-frequency converter requires only four passive external components for precision operation, making it ideal for many low cost applications such as A/D conversion, frequency-to-voltage conversion,

## **Applications**

- Precision voltage-to-frequency converters

- Serial transmission of analog information

- Pulse width modulators

- Frequency-to-voltage converters

- A/D converters and long term integrators

- · Signal isolation

- · FSK modulation/demodulation

- Frequency scaling

- Motor speed controls

- Phase lock loop stabilization

and serial data transmission. The improved linearity at high frequency makes it comparable to many dual slop A/D converters both in conversion time and accuracy, while retaining the benefits of voltage-to-frequency conversion, i.e., serial output, cost and size. The speed accuracy and temperature performance of the 4153 is achieved by incorporating high speed ECL logic, a high gain, wide bandwidth op amp, and a buried Zener reference on a single monolithic chip.

## **Pin Assignments**

## **Pin Descriptions**

| Pin | Function                          |

|-----|-----------------------------------|

| 1   | -V <sub>S</sub>                   |

| 2   | REF Gnd                           |

| 3   | V <sub>REF</sub> Output           |

| 4   | V <sub>OUT</sub> (Op Amp)         |

| 5   | I <sub>IN</sub> (REF Input)       |

| 6   | C <sub>O</sub> (Pulse Width)      |

| 7   | Trigger Input                     |

| 8   | Circuit Gnd                       |

| 9   | Frequency Output (Open Collector) |

| 10  | +V <sub>S</sub>                   |

| 11  | (+) Op Amp Input                  |

| 12  | (-) Op Amp Input                  |

| 13  | V <sub>OS</sub> Trim              |

| 14  | V <sub>OS</sub> Trim              |

# Absolute Maximum Ratings<sup>(1)</sup>

| Parameter                              | Min.            | Тур. | Max.            | Units |

|----------------------------------------|-----------------|------|-----------------|-------|

| Supply Voltage                         |                 |      | ±18             | ٧     |

| Internal Power Dissipation             |                 |      | 500             | mW    |

| Input Voltage                          | -V <sub>S</sub> |      | +V <sub>S</sub> |       |

| Output Sink Current (Frequency Output) |                 |      | 20              | mA    |

| Storage Temperature Range              | -65             |      | +150            | °C    |

| Operating Temperature Range            |                 |      |                 |       |

| RV4153                                 | -25             |      | +80             |       |

| RC4153                                 | 0°              |      | +70             | °C    |

#### Note

### **Thermal Characteristics**

|                                          | 14-Lead Ceramic DIP | 14-Lead Plastic DIP |

|------------------------------------------|---------------------|---------------------|

| Max. Junction Temp                       | +175°C              | +125°C              |

| Max. P <sub>D</sub> T <sub>A</sub> <50°C | 1042 mW             | 468 mW              |

| Therm Res θ <sub>JC</sub>                | 60°C/W              | _                   |

| Therm Res θ <sub>JA</sub>                | 120°C/W             | 160°C/W             |

| For T <sub>A</sub> >50°C Derate at       | 8.33 mW/°C          | 6.25 mW/°C          |

<sup>&</sup>quot;Absolute maximum ratings" are those beyond which the safety of the device cannot be guaranteed. They are not meant to

imply that the device should be operated at these limits. If the device is subjected to the limits in the absolute maximum ratings

for extended periods, its reliability may be impaired. The tables of Electrical Characteristics provide conditions for actual

device operation.

## **Electrical Characteristics**

$(V_S = \pm 15V \text{ and } T_A = +25^{\circ}C \text{ unless otherwise noted})$

| Parameters                                              | Min.     | Тур.          | Max. | Units      |

|---------------------------------------------------------|----------|---------------|------|------------|

| Power Supply Requirements                               |          |               |      |            |

| Supply Voltage                                          | ±12      | ±15           | ±18  | V          |

| Supply Current (+V <sub>S</sub> , I <sub>OUT</sub> = 0) |          | +4.2          | +7.5 | mA         |

| $(-V_S, I_{OUT} = 0)$                                   |          | -7            | -10  |            |

| Full Scale Frequency                                    | 250      | 500           |      | kHz        |

| Transfer Characteristics                                |          |               |      |            |

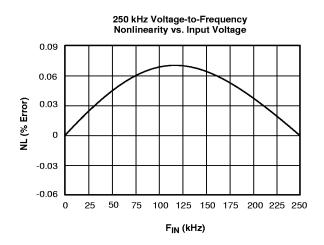

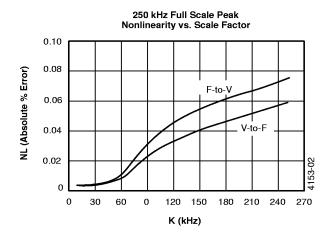

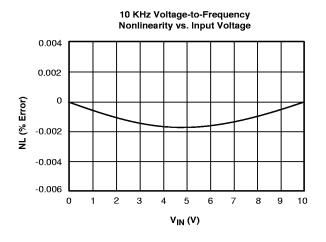

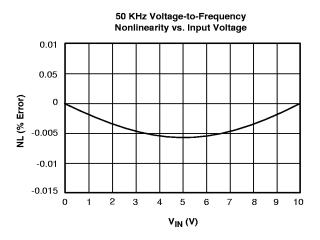

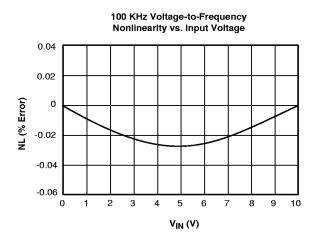

| Nonlinearity Error Voltage-to-Frequency <sup>1</sup>    |          |               |      |            |

| 0.1 Hz ≤ F <sub>OUT</sub> ≤ 10 kHz                      |          | 0.002         | 0.01 | %FS        |

| 1.0 Hz ≤ F <sub>OUT</sub> ≤ 100 kHz                     |          | 0.025         | 0.05 | %FS        |

| 5.0 Hz ≤ F <sub>OUT</sub> ≤ 250 kHz                     |          | 0.06          | 0.1  | %FS        |

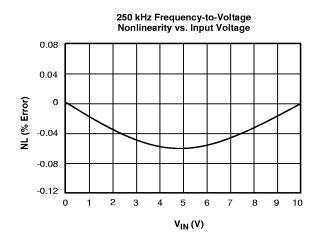

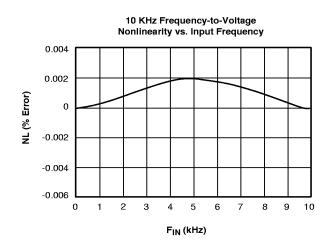

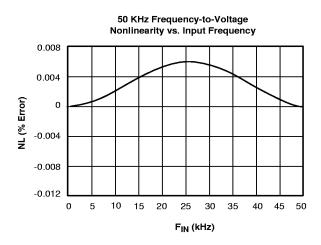

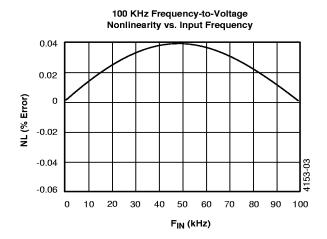

| Nonlinearity Error Frequency-to-Voltage <sup>1</sup>    |          |               |      |            |

| 0.1 Hz ≤ F <sub>IN</sub> ≤ 10 kHz                       |          | 0.002         | 0.01 | %FS        |

| 1.0 Hz ≤ F <sub>IN</sub> ≤ 100 kHz                      |          | 0.05          | 0.1  | %FS        |

| 5.0 Hz ≤ F <sub>IN</sub> ≤ 250 kHz                      |          | 0.07          | 0.12 | %FS        |

| Scale Factor Tolerance, F = 10 = kHz                    |          |               |      |            |

| 1                                                       |          |               |      |            |

| $K = \frac{1}{2V_{REF}R_{IN}C_{O}}$                     |          | ±0.5          |      | %          |

| Change of Scale Factor with Supply                      |          | 0.008         |      | %/V        |

| Reference Voltage (V <sub>REF</sub> )                   |          | 7.3           |      | V          |

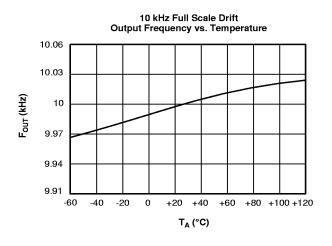

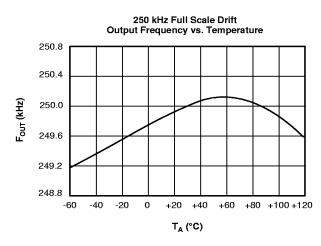

| Temperature Stability (0°C to 70°C) <sup>1, 2, 3</sup>  |          |               |      |            |

| Scale Factor 10 KHz Nominal                             |          | ±75           | ±150 | ppm/°C     |

| Reference Voltage                                       |          | ±50           | ±100 | ppm/°C     |

| Scale Factor (External Ref) 10 KHz FS                   |          | ±25           | ±50  | ppm/°C     |

| Scale Factor (External Ref) 100 KHz FS                  |          | ±50           | ±100 | ppm/°C     |

| Scale Factor (External Ref) 250 KHz FS                  |          | ±100          | ±150 | ppm/°C     |

| Op Amp                                                  |          |               |      | 1 1        |

| Open Loop Output Resistance                             |          | 230           |      | Ω          |

| Short Circuit Current                                   |          | 25            |      | mA         |

| Gain Bandwidth Product <sup>1</sup>                     | 2.5      | 3.0           |      | MHz        |

| Slew Rate                                               | 0.5      | 2.0           |      | V/μs       |

| Output Voltage Swing (R <sub>I</sub> ≥ 2K)              | 0 to +10 | -0.5 to +14.3 |      | V          |

| Input Bias Current                                      |          | 70            | 400  | n <b>A</b> |

| Input Offset Voltage (Adjustable to 0)                  |          | 0.5           | 5.0  | mV         |

| Input Offset Current                                    |          | 30            | 60   | nA         |

| Input Resistance (Differential Mode)                    |          | 1.0           | -    | MΩ         |

| Common Mode Rejection Ratio                             | 75       | 100           |      | dB         |

| Power Supply Rejection Ratio                            | 70       | 106           |      | dB         |

| Large Signal Voltage Gain                               | 25       | 350           |      | V/mV       |

| Parameters                                  | Min. | Тур. | Max. | Units      |

|---------------------------------------------|------|------|------|------------|

| Switched Current Source                     |      |      |      |            |

| Reference Current (External Reference)      |      | 1.0  |      | mA         |

| Digital Input (Frequency-to-Voltage, Pin 7) |      |      |      |            |

| Logic "0"                                   |      |      | 0.5  | V          |

| Logic "1"                                   | 2.0  |      |      | V          |

| Trigger Current                             |      | -50  |      | μΑ         |

| Logic Output (Open Collector)               |      |      |      |            |

| Saturation Voltage (Pin 9)                  |      |      |      |            |

| I <sub>SINK</sub> = 4 mA                    |      | 0.15 | 0.4  | V          |

| I <sub>SINK</sub> = 10 mA                   |      | 0.4  | 1.0  | V          |

| I <sub>LEAK</sub> (Off State)               |      | 150  |      | n <b>A</b> |

#### Notes:

- 1. Guaranteed but not tested.

- 2. V<sub>REF</sub> Range: 6.6V ≤ V<sub>REF</sub> ≤ 8.0V.

3. Over the specified operating temperature range.

# **Typical Performance Characteristics**

# **Typical Performance Characteristics**

## **Typical Application Circuits**

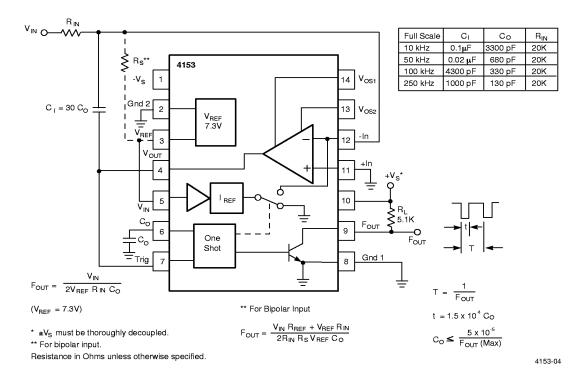

Figure 1. Voltage-to-Frequency Converter Minimum Circuit

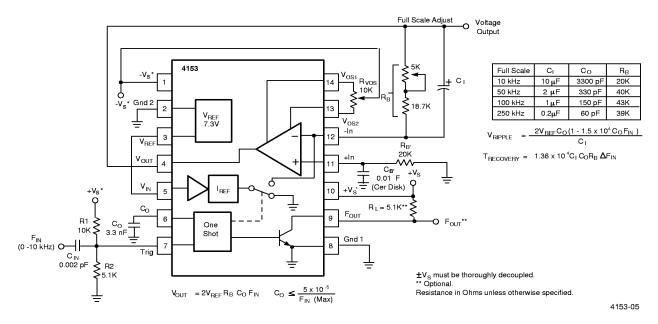

Figure 2. Frequency-to-Voltage Converter

## Typical Application Circuit (Continued)

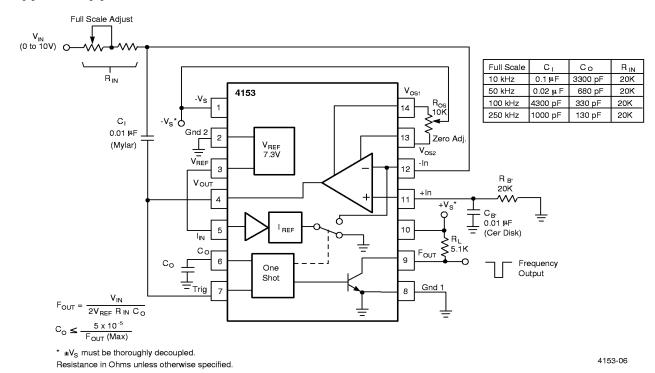

Figure 3. Voltage-to-Frequency Converter with Offset and Gain Adjusts

### **Principles of Operation**

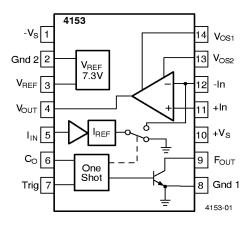

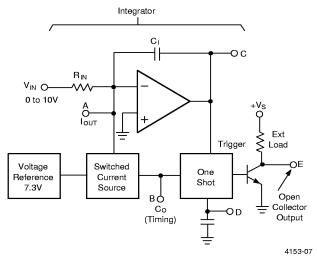

The 4153 consists of several functional blocks which provide either voltage-to-frequency or frequency-to-voltage conversion, depending on how they are connected. The operation is best understood by examining the block diagram as it is powered in a voltage-to-frequency mode (Figure 4).

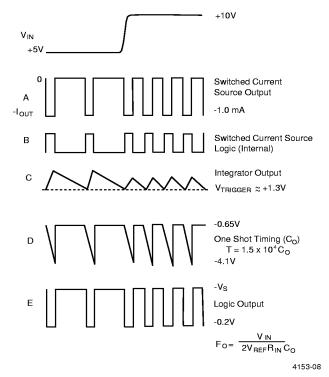

When power is first applied, all capacitors are discharged. The input current,  $V_{\rm IN}/R_{\rm IN}$ , causes  $C_{\rm I}$  to charge, and point C will try to ramp down. The trigger threshold of the one-shot is approximately +1.3V, and if the integrator output is less than +1.3V, the one-shot will fire and pulse the open collector output E and the switched current source A (see Figures 4 and 5). Because the point C is less than +1.3V, the one-shot fires, and the switched current source delivers a negative current pulse to the integrator. This causes  $C_{\rm IN}$  to charge in the opposite direction, and point C will ramp up until the end of the one-shot pulse. At that time, the positive current  $V_{\rm IN}/R_{\rm IN}$  will again make point C ramp down until the trigger threshold is reached.

When power is applied, the one-shot will continuously fire until the integrator output exceeds the trigger threshold. Once this is reached, the one-shot will fire as needed to keep the integrator output above the trigger threshold. If  $V_{\rm IN}$  is increased, the slope of the downward ramp increases, and the one-shot will fire more often in order to keep the integrator output high. Since the one-shot firing frequency is the same as the open collector output frequency, any increase in  $V_{\rm IN}$  will cause an increase in  $F_{\rm OUT}$ . This relationship is very linear because the amount of charge in each  $I_{\rm OUT}$  pulse is carefully defined, both in magnitude and duration. The duration of the pulse is set by the timing capacitor  $C_{\rm O}$  (point D). This feedback system is called a charge-balanced loop.

Figure 4. Voltage-to-Frequency Block Diagram

The scale factor K (the number of pulses per second or a specified  $V_{IN}$ ), is adjusted by changing either  $R_{IN}$  and therefore  $I_{IN}$ , or by changing the amount of charge in each  $I_{OUT}$  pulse. Since the magnitude of  $I_{OUT}$  is fixed at 1 milliamp, the way to change the amount of charge is by adjusting the one-shot duration set by  $C_{O}$  ( $I_{OUT}$  may be adjusted by changing  $V_{REF}$ ). The accuracy of the relationship between  $V_{IN}$  and  $F_{OUT}$  is affected by three major sources of error: temperature drift, nonlinearity and offset.

The total temperature drift is the sum of the individual drift of the components that make up the system. The greatest source of drift in a typical application is in the timing capacitor,  $\mathbf{C}_{\mathrm{O}}$ . Low temperature coefficient capacitors, such as silver mica and polystyrene, should be measured for drift using a capacitance meter. Experimentation has shown that the lowest tempco's are achieved by wiring a parallel capacitor composed of 70% silver mica and 30% polystyrene.

The reference on the chip can be replaced by an external reference with much tighter drift specifications, such as an LM199. The 199's 6.9V output is close to the 4153's 7.3V output, and has less than 10 ppm/°C drift.

Nonlinearity is primarily caused by changes in the precise amount of charge in each  $I_{OUT}$  pulse. As frequency increases, internal stray capacitances and switching problems change the width and amplitude of the  $I_{OUT}$  pulses, causing a nonlinear relationship between  $V_{IN}$  and  $F_{OUT}$ .

Figure 5. Voltage-to-Frequency Timing Waveforms

For this reason, the scale factor you choose should be below 1 KHz/V or as low as the acquisition time of your system will allow.

Nonlinearity is also affected by the rate of  $C_I$  to  $C_O$ . Less error can be achieved by increasing the value of  $C_I$ , but this affects response time and temperature drift. Optimum value for  $C_I$  and  $C_O$  are shown In the tables in Figures 1, 2, and 3. These values represent the best compromise of nonlinearity and temperature drift. Polypropylene, mylar or polystyrene capacitors should be used for  $C_I$ .

The accuracy at low input voltages is limited by the offset and  $V_{\rm OS}$  drift of the op amp. To improve this condition, an offset adjust is provided.

Once your system is running, it may be calibrated as follows: apply a measured full scale input voltage and adjust  $R_{\rm IN}$  until the scale factor is correct. For precise applications, trimming by soldering metal film resistors in parallel is recommended instead of trimpots, which have bad tempco's and are easily taken out of adjustment by mechanical shock. After the scale factor is calibrated, apply a known small input voltage (approximately  $10~{\rm mV}$ ) and adjust the op amp offset until the output frequency equals the input multiplied by the scale factor.

The output E consists of a series of negative going pulses with a pulse width equal to the one-shot time. The open collector pull-up resistor may be connected to a different supply (such as 5V for TTL) as long a it does not exceed the value of  $\pm V_S$  applied to pin 10. The load current should be

kept below 10 mA in order to minimize strain on the device. Pins 2 and 8 must be grounded in all applications, even if the open collector transistor is not used.

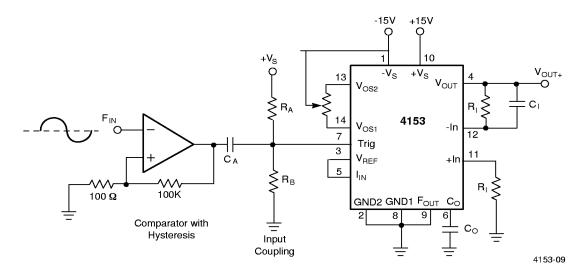

Figure 6 shows the complete circuit for a precision frequency-to-voltage converter. The circuit converts an input frequency to a proportional voltage by integrating the switched current source output. As the input frequency increases, the number of I<sub>OUT</sub> pulses delivered to the integrator increases, thus increasing the average output voltage. Depending on the time constant of the integrator, there will be some ripple on the output. The output may be further filtered, but this will reduce the response time. A second order filter will decrease ripple and improve response time.

The input waveform must meet three conditions for proper frequency-to-voltage operation. First, it must have sufficient amplitude and offset to swing above and below the 1.3V trigger threshold (See Figure 6 for an example of AC coupling and offset bias.) Second, it must be a fast slewing waveform having a quick rise time. A comparator may be used to square it up. Finally, the input pulse width must not exceed the one-shot time, in order to avoid retriggering the one-shot (AC couple the Input).

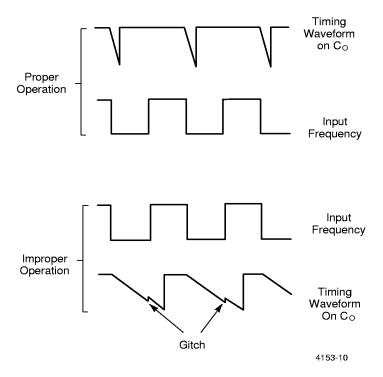

Capacitive coupling between the trigger input and the timing capacitor pin may occur if the input waveform is a square-wave or the input has a short period. This can cause gross nonlinearity due to changes in the one-shot timing waveform (See Figure 7). This problem can be avoided by keeping the value of  $C_{\rm O}$  small, and thereby keeping the timing period less than the input waveform period.

Figure 6. Frequency-to-Voltage Precision Converter

Figure 7. Frequency-to-Voltage Timing Waveforms

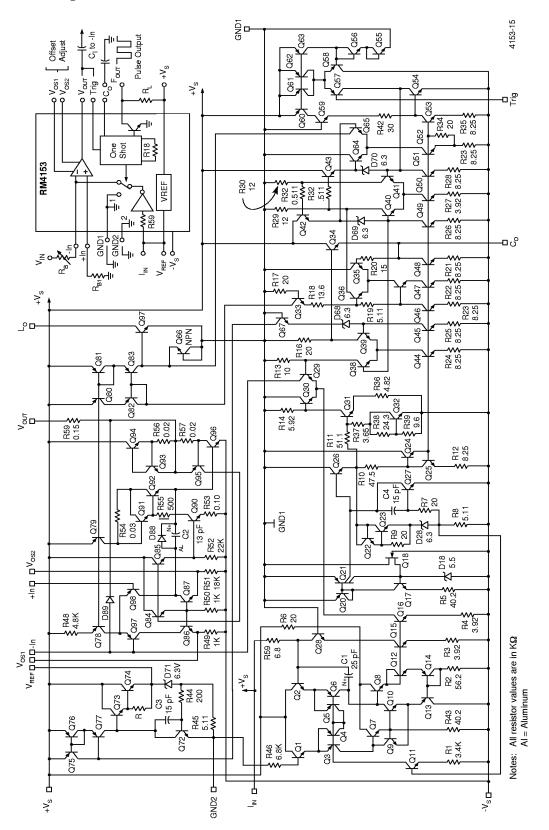

## **Detailed Circuit Operation**

The circuit consists of a buried zener reference (breakdown occurs below the surface of the die, reducing noise and contamination), a high speed one-shot, a high speed switched precision voltage-to-current converter and an open-collector output transistor.

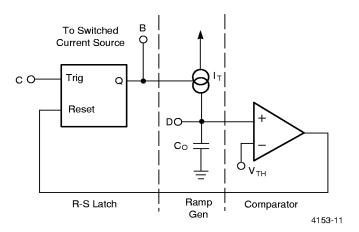

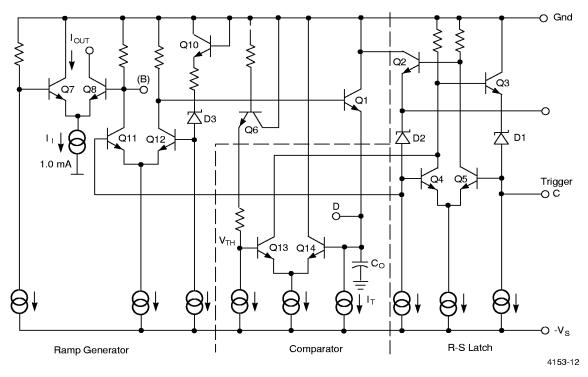

Figure 8 shows a block diagram of the high speed one-shot and Figure 9 shows the monolithic implementation. A trigger pulse sets the R-S latch, which lets  $C_{\rm O}$  charge from  $I_{\rm T}$ . When the voltage on  $C_{\rm O}$  exceeds  $V_{\rm TH}$ . the comparator resets the latch and discharges  $C_{\rm O}$ . Looking at the detailed schematic,

a positive trigger voltage turns on Q5, turns off Q4, and turns on Q3. Q3 provides more drive to Q5 keeping it on and latching the base of Q11 low. This turns on the switched current source and turns off Q1, allowing  $C_{\rm O}$  to charge in a negative direction. When the voltage on  $C_{\rm O}$  exceeds  $V_{\rm TH}$ , Q13's collector pulls Q3's base down, resetting the latch, turning off the switched current source and discharging  $C_{\rm O}$  through Q1. Note that all of the transistors in the signal path are NPNs, and that the voltage swings are minimized ECL fashion to reduce delays. Minimum delay means minimum drift of the resultant VFC scale factor at high frequency.

Figure 8. One-Shot Block Diagram

Figure 9. One-Shot (Detail)

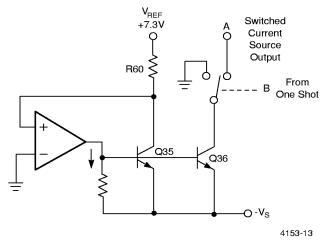

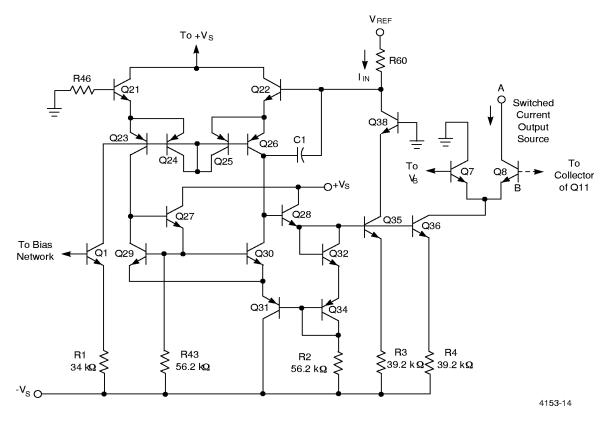

The switched current source is shown as a block diagram in Figure 10 and detailed in Figure 11. The summing node (+ input of the op amp) is held at 0V by the amplifier feedback, causing  $V_{REF}$  to be applied across R60. This current ( $V_{REF}/R60$ ), minus the small amplifier bias current, flows through Q35. Q35 develops a  $V_{BE}$  dependent on that current. This  $V_{BE}$  is developed across Q36. Since Q35 and Q36 are equal in area, the currents are equal. The mirrored current is switched by the one-shot output.

The detail schematic shows the amplifier and load (Q21 through Q34), the mirror transistors (Q35, Q36) and the differential switching transistors (Q7, Q8). The amplifier uses a complementary paraphase input composed of Q21 through Q26 with a current mirror formed by Q27 through Q30, which converts from differential to single-ended output. Level-shift diodes Q32 and Q34 and emitter follower Q31 bootstrap the emitters of the mirror devices Q29 and Q30 to increase gain and lower input offsets, which would otherwise be caused by unbalanced collector voltages on Q23 and Q26.

Figure 10. Switched Current Source Block Diagram

Matching emitter currents in Q35 and Q36 are assured by degeneration resistors R3 and R4. The differential switch allows the current source to remain active continuously, shunting to ground in the off state. This helps stabilize the

output, and again, NPNs reduce switching time, timing errors, and most important, drift of timing errors over temperature.

Figure 11. Switched Current Source (Detail)

## **Schematic Diagram**

## Notes:

## **Ordering Information**

| Part Number | Package | Operating Temperature Range |

|-------------|---------|-----------------------------|

| RC4153N     | N       | 0°C to +70°C                |

| RV4153N     | N       | -25°C to 80°C               |

#### Notes:

N = 14-lead plastic DIP

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user.

- A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.