# 捷多邦,专业PCB打样工厂,24小时加急出货

# RV4141A

Low Power Ground Fault Interrupter

# **Features**

- Powered from the AC line

- Built-in rectifier

- Direct interface to SCR

- 500 µA quiescent current

- Precision sense amplifier

# Description

The RV4141A is a low power controller for AC receptacle ground fault circuit interrupters. These devices detect hazardous current paths to ground and ground to neutral faults. The circuit interrupter then disconnects the load from the line before a harmful or lethal shock occurs.

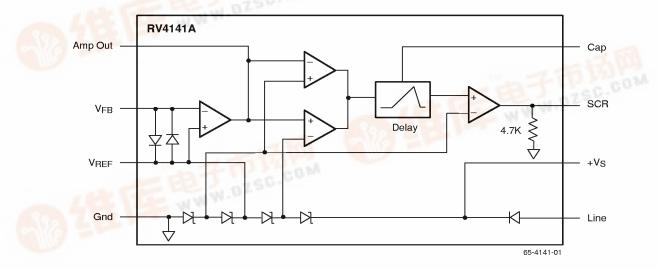

Internally, the RV4141A contains a diode rectifier, shunt regulator, precision sense amplifier, current reference, time delay circuit, and SCR driver.

Two sense transformers, SCR, solenoid, three resistors and four capacitors complete the design of the basic circuit interrupter. The simple layout and minimum component count insure ease of application and long term reliability.

- Adjustable time delay

- Minimum external components

- Meets UL 943 requirements

- For use with 110V or 220V systems

- Available in 8 pin DIP or SOIC package

Features not found in other GFCI controllers include a low offset voltage sense amplifier eliminating the need for a coupling capacitor between the sense transformer and sense amplifier, and an internal rectifier to eliminate high voltage rectifying diodes.

The RV4141A is powered only during the positive half period of the line voltage, but can sense current faults independent of its phase relative to the line voltage. The gate of the SCR is driven only during the positive half cycle of the line voltage.

# **Block Diagram**

# **Absolute Maximum Ratings**

(beyond which the device may be damaged)<sup>1</sup>

| Parameter                   |              |     | Тур | Max   | Units |

|-----------------------------|--------------|-----|-----|-------|-------|

| Supply Current              |              |     |     | 10    | mA    |

| Internal Power Dissipation  |              |     |     | 500   | mW    |

| Storage Temperature Range   |              | -65 |     | +150  | °C    |

| Operating Temperature Range |              | -35 |     | +80   | °C    |

| Junction Temperature        |              |     |     | 125°C |       |

| Lead Soldering Temperature  | 60 Sec, DIP  |     |     | 300   | °C    |

|                             | 10 Sec, SOIC |     |     | 260   | °C    |

Notes:

1. Functional operation under any of these conditions is NOT implied. Performance and reliability are guaranteed only if Operating Conditions are not exceeded.

# **Thermal Characteristics**

| Parameter |                    | Min  | Тур | Max | Units |      |

|-----------|--------------------|------|-----|-----|-------|------|

| θJA       | Thermal resistance | SOIC |     | 240 |       | °C/W |

|           |                    | PDIP |     | 160 |       | °C/W |

| Parameters                      | Test Conditions                        | Min  | Тур  | Max  | Units |

|---------------------------------|----------------------------------------|------|------|------|-------|

| Shunt Regulator (Pins 5 to 4)   | ·                                      |      |      | •    | •     |

| Regulated Voltage               | I <sub>2-3</sub> = 11μA                | 25.0 | 27.0 | 29.0 | V     |

| Regulated Voltage               | ILINE = 750 μA, I <sub>2-3</sub> = 9μA | 25.0 | 27.0 | 29.0 | V     |

| Quiescent Current               | V5-4 = 24V                             | —    | 500  | —    | μΑ    |

| Sense Amplifier (Pins 2 to 3)   |                                        |      |      |      |       |

| Offset Voltage                  |                                        | -200 | 0    | 200  | μV    |

| Gain Bandwidth                  | (Design Value)                         | —    | 1.5  | —    | MHz   |

| Input Bias Current              | (Design Value)                         |      | 30   | 100  | nA    |

| SCR Trigger (Pins 7 to 4)       |                                        |      |      |      |       |

| Output Resistance               | V7-4 = Open, I2-3 = μA                 | 3.8  | 4.7  | 5.6  | kΩ    |

| Output Voltage                  | I <sub>2-3</sub> = 9μA                 | 0    | 0.1  | 10   | mV    |

| Output Voltage                  | I <sub>2-3</sub> = 11µA                | 2.4  | 3.0  | 3.6  | V     |

| Output Current                  | $V_{7-4} = 0V, I_{2-3} = 11\mu A$      | 400  | 600  |      | μΑ    |

| Reference Voltage (Pins 3 to 4) |                                        |      |      |      |       |

| Reference Voltage               | ILINE = 750 μA                         | 12.0 | 13.0 | 14.0 | V     |

| Delay Timer (Pins 8 to 4)       |                                        |      |      |      |       |

| Delay Time (Note 1)             | C <sub>8-4</sub> = 12nF                | —    | 2.0  | —    | ms    |

| Delay Current                   | I <sub>2-3</sub> = 11µA                | 30   | 40   | 50   | μA    |

Note:

1. Delay time is defined as starting when the instantaneous sense current (I<sub>2-3</sub>) exceeds 6.5 V/RSET and ending when the SCR trigger voltage V<sub>7-6</sub> goes high.

# **Circuit Operation**

(Refer to Block Diagram and Figure 1)

The precision op amp connected to Pins 1 through 3 senses the fault current flowing in the secondary of the sense transformer, converting it to a voltage at Pin 1. The ratio of secondary current to output voltage is directly proportional to feedback resistor, RSET.

RSET converts the sense transformer secondary current to a voltage at Pin 1. Due to the virtual ground created at the sense amplifier input by its negative feedback loop, the sense transformer's burden is equal to the value of RIN. From the transformer's point of view, the ideal value for RIN is  $0\Omega$ . This will cause it to operate as a true current transformer with minimal error. However, making RIN equal to zero creates a large offset voltage at Pin 1 due to the sense amplifier's very high DC gain. RIN should be selected as high as possible consistent with preserving the transformer's operation as a true current mode transformer. A typical value for RIN is between 200 and 1000 $\Omega$ .

As seen by the equation below, maximizing RIN minimizes the DC offset error at the sense amplifiers output. The DC offset voltage at Pin 1 contributes directly to the trip current error. The offset voltage at Pin 1 is:

VOS x RSET/(RIN + RSEC)

Where: VOS = Input offset voltage of sense amplifier RSET = Feedback resistor RIN = Input resistor RSEC = Transformer secondary winding resistance

The sense amplifier has a specified maximum offset voltage of  $200 \ \mu V$  to minimize trip current errors.

Two comparators connected to the sense amplifier output are configured as a window detector, whose references are -6.5 volts and +6.5 volts referred to Pin 3. When the sense transformer secondary RMS current exceeds 4.6/RSET the output of the window detector starts the delay circuit. If the secondary current exceeds the predetermined trip current for longer than the delay time a current pulse appears at Pin 7, triggering the SCR.

The SCR anode is directly connected to a solenoid or relay coil. The SCR can be tripped only when its anode is more positive than its cathode.

#### **Supply Current Requirements**

The RV4141A is powered directly from the line through a series limiting resistor called RLINE, its value is between 24 k $\Omega$  and 91 k $\Omega$ . The controller IC has a built-in diode rectifier eliminating the need for external power diodes.

The recommended value for  $R_{LINE}$  is 24 k $\Omega$  to 47 k $\Omega$  for 110V systems and 47 k $\Omega$  to 91 k $\Omega$  for 220V systems. When  $R_{LINE}$  is 47 k $\Omega$  the shunt regulator current is limited to 3.6 mA. The recommended maximum peak line current through  $R_{LINE}$  is 10 mA.

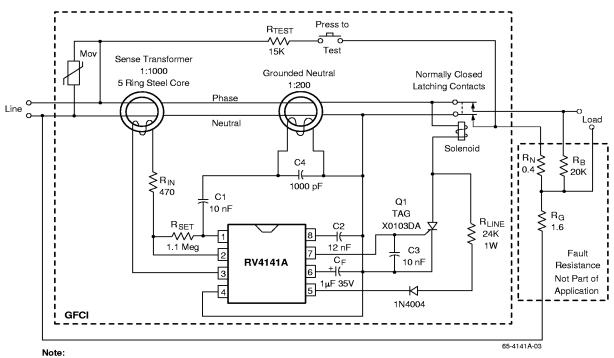

#### GFCI Application (Refer to Figure 1)

The GFCI detects a ground fault by sensing a difference current in the line and neutral wires. The difference current is assumed to be a fault current creating a potentially hazardous path from ine to ground. Since the line and neutral wires pass through the center of the sense transformer, only the differential primary current is transferred to the secondary. Assuming the turns ratio is 1:1000 the secondary current is 1/1000th the fault current. The RV4141A's sense amplifier converts the secondary current to a voltage which is compared with either of the two window detector reference voltages. If the fault current exceeds the design value for the duration of the programmed time delay, the RV4141A will send a current pulse to the gate of the SCR.

Detecting ground to neutral faults is more difficult. RB represents a normal ground fault resistance, RN is the wire resistance of the electrical circuit between load/ neutral and earth ground. RG represents the ground to neutral fault condition. According to UL 943, the GFCI must trip when RN =  $0.4\Omega$ , RG =  $1.6\Omega$  and the normal ground fault is 6 mA.

Assuming the ground fault to be 5 mA, 1 mA and 4 mA will go through RG and RN, respectively, causing an effective 1 mA fault current. This current is detected by the sense transformer and amplified by the sense amplifier. The ground/ neutral and sense transformers are now mutually coupled by RG, RN and the neutral wire ground loop, producing a positive feedback loop around the sense amplifier. The newly created feedback loop causes the sense amplifier to oscillate at a frequency determined by ground/neutral transformer secondary inductance and C4. Typically it occurs at 8 KHz.

C2 is used to program the time required for the fault to be present before the SCR is triggered. Refer to the equation below for calculating the value of C2. Its typical value is 12 nF for a 2 ms delay.

RSET is used to set the fault current at which the GFCI trips. When used with a 1:1000 sense transformer, its typical value is 1 M $\Omega$  for a GFCI designed to trip at 5 mA.

$R_{IN}$  should be the highest value possible which insures a predictable secondary current from the sense transformer. If  $R_{IN}$  is set too high, normal production variations in the transformer permeability will cause unit to unit variations in the secondary current. If it is too low, a large offset voltage error at Pin 1 will be present. This error voltage in turn creates a trip current error proportional to the input offset voltage of the sense amplifier. As an example, if  $R_{IN}$  is 500 $\Omega$ ,

#### RV4141A

RSET is 1 M $\Omega$ , RSEC is 45 $\Omega$  and the VOS of the sense amplifier is its maximum of 200  $\mu$ V, the trip current error is ±5.6%.

The SCR anode is directly connected to a solenoid or relay coil. It can be tripped only when its anode is more positive than its cathode. It must have a high dV/dt rating to ensure that line noise (generated by electrically noisy appliances) does not falsely trigger it. Also the SCR must have a gate drive requirement less than 200  $\mu$ A. C3 is a noise filter that prevents high frequency line pulses from triggering the SCR.

The relay solenoid used should have a response time of 3 ms or less to meet the UL 943 timing requirement.

#### **Sense Transformers and Cores**

The sense and ground/neutral transformer cores are usually fabricated using high permeability laminated steel rings. Their single turn primary is created by passing the line and neutral wires through the center of its core. The secondary is usually from 200 to 1500 turns.

Magnetic Metals Corporation, Camden, NJ 08101, (609) 964-7842 and Magnetics, 900 E. Butler Road, P.O. Box 391, Butler, PA 16003, (412) 282-8282 are full-line suppliers of ring cores and transformers designed specifically for GFCI and related applications.

#### Calculating The Values Of RSET and C2

Determine the nominal ground fault trip current requirement. This will be typically 5 mA in North America (117V AC) and 22 mA in the UK and Europe (220V AC). Determine the minimum delay time required to prevent nuisance tripping. This will typically be 1 to 2 ms. The value of C2 required to provide the desired delay time is:

C2 = 6 x T

where: C2 is in nF T is the desired delay time in ms.

The value of RSET to meet the nominal ground fault trip current specification is:

$$R_{SET} = \frac{4.6 \times N}{I_{FAULT} \times COS \ 180(T/P)}$$

where:

RSET is in  $k\Omega$

T is the time delay in ms P is the period of the line frequency in ms

IFAULT is the desired ground fault trip current in mA RMS N is the number of sense transformer secondary turns.

This formula assumes an ideal sense transformer is used. The calculated value of  $R_{SET}$  may have to be changed up to 30% to when using a non-ideal transformer.

1. Portions of this schematic are subject to U.S. patents 3,878,435 and Re. 30,678.

Figure 1. GFI Application Circuit

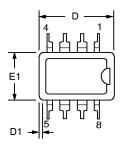

# **Mechanical Dimensions**

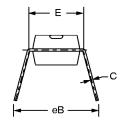

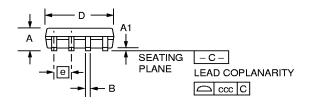

#### 8-Lead Plastic DIP Package

| Symbol | Inc      | hes  | Millimeters |       | Notes |

|--------|----------|------|-------------|-------|-------|

| Symbol | Min.     | Max. | Min.        | Max.  | Notes |

| А      | _        | .210 | _           | 5.33  |       |

| A1     | .015     | _    | .38         | _     |       |

| A2     | .115     | .195 | 2.93        | 4.95  |       |

| В      | .014     | .022 | .36         | .56   |       |

| B1     | .045     | .070 | 1.14        | 1.78  |       |

| С      | .008     | .015 | .20         | .38   | 4     |

| D      | .348     | .430 | 8.84        | 10.92 | 2     |

| D1     | .005     |      | .13         | _     |       |

| E      | .300     | .325 | 7.62        | 8.26  |       |

| E1     | .240     | .280 | 6.10        | 7.11  | 2     |

| е      | .100 BSC |      | 2.54 BSC    |       |       |

| eВ     | _        | .430 | _           | 10.92 |       |

| L      | .115     | .160 | 2.92        | 4.06  |       |

| N      | 8°       |      | 8°          |       | 5     |

# Notes:

- 1. Dimensioning and tolerancing per ANSI Y14.5M-1982.

- 2. "D" and "E1" do not include mold flashing. Mold flash or protrusions shall not exceed .010 inch (0.25mm).

- 3. Terminal numbers are for reference only.

- 4. "C" dimension does not include solder finish thickness.

- 5. Symbol "N" is the maximum number of terminals.

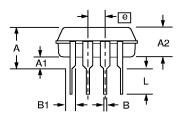

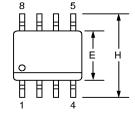

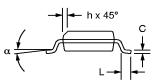

# Mechanical Dimensions (continued)

### 8-Lead SOIC Package

| Symbol | Inc      | hes  | Millimeters |      | Notes |

|--------|----------|------|-------------|------|-------|

| Symbol | Min.     | Max. | Min.        | Max. | Notes |

| Α      | .053     | .069 | 1.35        | 1.75 |       |

| A1     | .004     | .010 | 0.10        | 0.25 |       |

| В      | .013     | .020 | 0.33        | 0.51 |       |

| С      | .008     | .010 | 0.20        | 0.25 | 5     |

| D      | .189     | .197 | 4.80        | 5.00 | 2     |

| Е      | .150     | .158 | 3.81        | 4.01 | 2     |

| е      | .050 BSC |      | 1.27 BSC    |      |       |

| Н      | .228     | .244 | 5.79        | 6.20 |       |

| h      | .010     | .020 | 0.25        | 0.50 |       |

| L      | .016     | .050 | 0.40        | 1.27 | 3     |

| N      | 8        |      | 8           |      | 6     |

| α      | 0°       | 8°   | 0°          | 8°   |       |

| ccc    | _        | .004 | _           | 0.10 |       |

#### Notes:

- 1. Dimensioning and tolerancing per ANSI Y14.5M-1982.

- 2. "D" and "E" do not include mold flash. Mold flash or protrusions shall not exceed .010 inch (0.25mm).

- 3. "L" is the length of terminal for soldering to a substrate.

- 4. Terminal numbers are shown for reference only.

- 5. "C" dimension does not include solder finish thickness.

- 6. Symbol "N" is the maximum number of terminals.

## **Ordering Information**

| Part Number | Package             | Operating Temperature Range |  |  |

|-------------|---------------------|-----------------------------|--|--|

| RV4141AN    | 8-Lead Plastic DIP  | -35°C to +80°C              |  |  |

| RV4141AM    | 8-Lead Plastic SOIC | -35°C to +80°C              |  |  |

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user.

- 2. A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.