# Rockwell Semiconductor Systems

# RF100 902-928 RF Direct Conversion Receiver

## **Product Description**

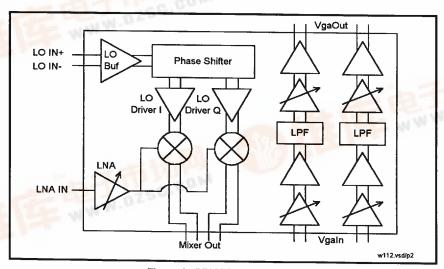

The RF100 Direct-Conversion Receiver is a highly integrated, monolithic device that is based on a direct-conversion quadrature receiver architecture. It includes a low-noise amplifier (LNA), quadrature double-balanced mixers, an on-chip 3-pole baseband low-pass filter, and a variable gain amplifier (VGA), providing the entire RF to baseband I&Q demodulation on a single chip.

Because of its direct-conversion topology, the RF100 requires no RF filtering for image rejection, has low power consumption, and is capable of operating off of a regulated or unregulated three-cell battery pack (2.7 V to 5.0 V).

The RF 100 is packaged in a small, 48-pin TQFP plastic package and is operational in the 900 MHz ISM band (902–928 MHz).

# **Applications**

- Direct Sequence Spread Spectrum Systems

- Frequency Hopping Spread Spectrum Systems

- Digital Cordless Telephones

- Wireless LANs

- Wireless Modems

- Wireless Security

- Inventory Control Systems

### **Features**

- Single-chip Antenna-to-Baseband RF Receiver.

- LNA/Double-Balanced Mixer for RF to Baseband Conversion.

- Quadrature Mix Down to Baseband.

- 22 dB Selectable Attenuator for the Front End.

- LO Input Buffer.

- On-chip 3-pole low pass filter.

- 86 dB of Baseband Gain with 62 dB of Gain Control.

- Differential Baseband Output.

- 3 Battery Cell operation (2.7 V to 5 V).

- 48-Pin TQFP Package.

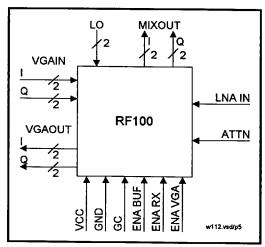

Figure 1. RF100 Block Diagram

Order No. W112 Rev. 1, October 27,1995

### **Technical Description**

The RF100 block diagram, shown on the previous page, is composed of two major sections:

- 1. LNA/Mixer Down-conversion

- VGA/LPF

#### **LNA/Mixer Down-conversion Section**

The low noise amplifier drives two mixers with quadrature local-oscillators. The quadrature LO is generated with a passive 90° network, with a buffer preceding it as well as after it on each port. The LO input buffer is enabled separately.

#### VGA/LPF Section

Four stages of gain are provided in the IF amplifier, with the first and third having variable gain. A single voltage controls the gain for both stages. A three-pole low-pass filter at 850 KHz is provided to add additional system selectivity.

#### **Recommendations on Layout and Implementation**

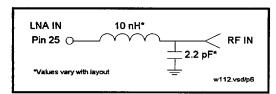

The LNA input pin requires proper matching. A 10 nH series inductor and a 2.2 pF capacitor to GND are recommended (refer to Figure 2 below).

Figure 2. Typical LNA Input Matching Circuit

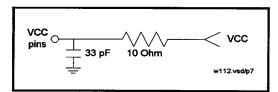

2. All Vccs should have proper decoupling capacitors connected to ensure the cleanness of the DC supply. An RC low-pass network (as shown in Figure 3) is advised. For pin 13 and pin 37, an additional 2.2 μF capacitor in parallel to the 33 pF cap is needed to filter out low-frequency noise.

Figure 3. Recommended VCC Decoupling Circuit

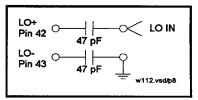

The LO port can be driven differentially or singleended. The LO may be used single-ended by simply connecting the LO- pin (pin 43) to a 47 pF capacitor to GND (refer to Figure 4).

Figure 4. Single-ended LO Input

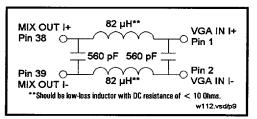

4. For the external baseband filter between the Mixer outputs and VGA inputs, a recommended circuit is shown in Figure 5. This baseband filter has a corner frequency of 750 KHz. For better performance, the I channel filter should be kept away from the Q channel filter to prevent crosstalk. Also, using an orthogonal layout for these two filters will reduce mutual inductance and result in better performance. It is also essential to keep the two filters away from the VGA output pins to prevent potential instability due to the large gain of the VGA.

Figure 5. Recommended External Baseband Filter

5. For the current design, the VGA has a high-corner frequency of around 650 KHz when used with the recommended external baseband filter, and a lowcorner frequency of about 25 KHz when used with the recommended 56 nF servo cap and 22 nF blocking cap of the 2nd VGA stage.

The 650 KHz high corner is determined by the 3-pole off-chip filter which has a corner frequency of 750 KHz, and the on-chip 3-pole LPF whose bandwidth is nominally 850 KHz. The low-corner frequency is the effect of both the servo cap and the blocking cap. The low-corner cutoff frequency can be changed by simply varying the values of these two caps. Note that a change in capacitance will also change the settling time of the VGA.

The following equations should be used to get a rough estimate of the low-corner cutoff frequency, the servo capacitor, the blocking capacitor and the settling time:

$F_{\text{cutoff}}$  =  $K_1/C_{\text{servo}}$   $C_{\text{BL}}$  =  $C_{\text{servo}}/K_2^*$  $t_{\text{settling}}$  =  $K_3 \times C_{\text{servo}}$

where: K<sub>1</sub> is approximately 1400 KHz · nF,

K<sub>2</sub> is approximately 2.55, K<sub>3</sub> is approximately 3.57 μs/nF.

\* C<sub>BL</sub> is the capacitor between pins 5,6 or pins 7,8; C<sub>sevo</sub> is the capacitor between pins 9,10 or pins 11,12.

## Interface Description

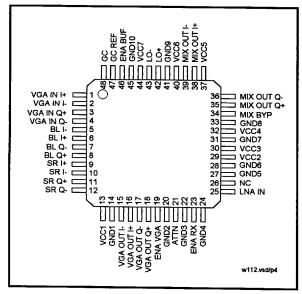

The RF100 interface signal diagram is shown in Figure 6, and the corresponding interface signals are described by functional group in Table 1. The RF100 signal pinout diagram is shown in Figure 7.

Figure 6. RF100 Signal Interface Diagram

Figure 7. RF100 Pin Signals - 48-Pin TQFP

**Table 1. Pin Description**

| Table 1. Pin Description |                                                      |                                                                |  |  |  |  |  |  |

|--------------------------|------------------------------------------------------|----------------------------------------------------------------|--|--|--|--|--|--|

| Pin                      | Name                                                 | Description                                                    |  |  |  |  |  |  |

| 1<br>2<br>3<br>4         | VGA IN I+<br>VGA IN I-<br>VGA IN Q+<br>VGA IN Q-     | Inputs for variable-gain amplifier.                            |  |  |  |  |  |  |

| 5<br>6<br>7<br>8         | BL I-<br>BL I+<br>BL Q-<br>BL Q+                     | Blocking caps for second variable-gain stage.                  |  |  |  |  |  |  |

| 9<br>10<br>11<br>12      | SR I+<br>SR I-<br>SR Q+<br>SR Q-                     | Bypass caps for variable-gain DC servo.                        |  |  |  |  |  |  |

| 13                       | VCC1                                                 | Power Supply for variable-gain amplifier.                      |  |  |  |  |  |  |

| 14                       | GND1                                                 | Ground for variable-gain amplifier.                            |  |  |  |  |  |  |

| 15<br>16<br>17<br>18     | VGA OUT I-<br>VGA OUT I+<br>VGA OUT Q-<br>VGA OUT Q+ | Outputs for variable-gain amplifier.                           |  |  |  |  |  |  |

| 19                       | ENA VGA                                              | Enable variable-gain amplifier.                                |  |  |  |  |  |  |

| 20                       | GND2                                                 | LNA Ground #1.                                                 |  |  |  |  |  |  |

| 21                       | ATTN                                                 | LNA Attenuation Pin.<br>(1 = Low Gain, 0 = High Gain)          |  |  |  |  |  |  |

| 22                       | GND3                                                 | LNA Ground #2.                                                 |  |  |  |  |  |  |

| 23                       | ENA RX                                               | Enable receiver front-end (LNA/Mixer).                         |  |  |  |  |  |  |

| 24                       | GND4                                                 | LNA Ground #3.                                                 |  |  |  |  |  |  |

| 25                       | LNA IN                                               | LNA Input. (Matching circuit required)                         |  |  |  |  |  |  |

| 26                       | NC                                                   | Not Connected.                                                 |  |  |  |  |  |  |

| 27                       | GND5                                                 | Ground.                                                        |  |  |  |  |  |  |

| 28                       | GND6                                                 | LNA substrate. Connected to GND.                               |  |  |  |  |  |  |

| 29<br>30                 | VCC2                                                 | LNA Supply.                                                    |  |  |  |  |  |  |

| 31                       | VCC3<br>GND7                                         | Supply for bias circuitry.                                     |  |  |  |  |  |  |

| 32                       | VCC4                                                 | Ground for bias circuitry.                                     |  |  |  |  |  |  |

| 33                       | GND8                                                 | Mixer Reference. Connected to V <sub>cc</sub> .  Mixer ground. |  |  |  |  |  |  |

| 34                       | MIX BYP                                              | Mixer bias bypass. AC-coupled to ground.                       |  |  |  |  |  |  |

| 35<br>36                 | MIX OUT Q+<br>MIX OUT Q-                             | Mixer Quadrature Outputs.                                      |  |  |  |  |  |  |

| 37                       | VCC5                                                 | Mixer Output Vcc.                                              |  |  |  |  |  |  |

| 38<br>39                 | MIX OUT I+<br>MIX OUT I-                             | Mixer In-phase outputs.                                        |  |  |  |  |  |  |

| 40                       | VCC6                                                 | LO Driver V <sub>cc</sub> .                                    |  |  |  |  |  |  |

| 41                       | GND9                                                 | LO Driver ground.                                              |  |  |  |  |  |  |

| 42<br>43                 | LO+<br>LO-                                           | Local Oscillator Inputs.                                       |  |  |  |  |  |  |

| 44                       | VCC7                                                 | LO Input Buffer Vcc.                                           |  |  |  |  |  |  |

| 45                       | GND10                                                | LO Input Buffer Ground.                                        |  |  |  |  |  |  |

| 46                       | ENA BUF                                              | Enable LO Input Buffer.                                        |  |  |  |  |  |  |

| 47                       | GC REF                                               | VGA Gain Control Reference.<br>AC-coupled to ground.           |  |  |  |  |  |  |

| 48                       | GC                                                   | VGA Gain Control Pin.                                          |  |  |  |  |  |  |

## **Receiver Specifications**

Electrical specifications are given below in Table 2. Absolute maximum ratings are given below in Table 3.

Table 2. Electrical Specifications\*

Test Conditions:  $T_A$  = 25°C,  $V_{CC}$  = 3.6 V,  $f_{LO}$  = 915 MHz

| Pa                                                       | arameter                                      | Min        | Тур        | Max      | Units |

|----------------------------------------------------------|-----------------------------------------------|------------|------------|----------|-------|

| LNA/Mixer Voltage Gain:                                  | High Gain Mode                                | 18         | 20.5       | 22.5     | dB    |

|                                                          | Low Gain Mode                                 |            | -1.5       | 2.5      |       |

| Gain Variation vs. Frequency                             | 902 MHz < f <sub>LO</sub> < 928 MHz           |            | 0.5        | 11       | dB    |

| LNA/Mixer SSB Noise Figure:                              | High Gain Mode                                |            | 6.0        | 8.0      | dB    |

| LNA/Mixer Input IP3:                                     | High Gain Mode<br>Low Gain Mode               |            | -14<br>-8  |          | dBm   |

| LNA/Mixer Input P <sub>1db</sub> :                       | High Gain Mode<br>Low Gain Mode               |            | -21<br>-15 |          | dBm   |

| Required LO Input Power                                  |                                               | -13        | -10        | -7       | dBm   |

| Required LO Total Harmonic Dis                           | Required LO Total Harmonic Distortion:        |            |            | -20      | dBc   |

| LO Input Return Loss (Zo=50) w                           | /match                                        |            |            | -10      | dB    |

| RF Input Return Loss (Zo=50) w                           | /match                                        |            | †          | -9.5     | dB    |

| Mixer IF Port Output Impedance                           | (single-ended)                                | 150        | 190        | 230      | Ω     |

| LO Power at RF Port                                      | `                                             |            | -60        | -47      | dBm   |

| I/Q Phase imbalance                                      |                                               |            | 2          | 5        | deg   |

| I/Q Amplitude Imbalance (entire chain)                   |                                               |            | 0.5        | 3        | dB    |

| I/Q Amplitude Tracking for VGA                           |                                               |            | 0.5        | 2        | dB    |

| V <sub>IH</sub> for Enables and Attn.                    |                                               | 1.9        |            | <u> </u> | V     |

| V <sub>IL</sub> for Enables and Attn.                    |                                               |            |            | 0.8      | V     |

| I <sub>IH</sub> for Enables and Attn. (per control line) |                                               |            | 20         | 60       | μА    |

| I <sub>IL</sub> for Enables and Attn. (per control line) |                                               | -10        | -1         | 0        | μА    |

| VGA Maximum Gain                                         |                                               | 82         | 86         |          | dB    |

| VGA Gain at VGC = 1.70 V                                 |                                               |            | 50         |          | dB    |

| VGA Gain Control Range                                   |                                               | 62         |            |          | dB    |

| Gain Control Voltage Range                               |                                               | 1.2        | 1.7        | 2.0      | V     |

| Gain Control Sensitivity                                 |                                               |            | 0.08       |          | dB/mV |

| VGA Noise Figure:                                        | maximum gain<br>minimum gain                  |            | 6.5<br>33  |          | dB    |

| VGA Input IP3 @ minimum gain                             |                                               |            | -26        |          | dBV   |

| VGA Output IP3 @ maximum ga                              | in (in-band)                                  |            | 6          |          | dBV   |

|                                                          | VGA P <sub>1dB</sub> @ 3.9 MHz (maximum gain) |            |            |          | dBV   |

| VGA Input Impedance (single-ended)                       |                                               | 150        | _56<br>190 | 230      | Ω     |

| VGA Output Impedance (single-ended)                      |                                               |            |            | 1000     | Ω     |

| VGA 3 dB Bandwidth                                       |                                               |            | 0.85       | 1.2      | MHz   |

| VGA Selectivity @ 3.9 MHz                                |                                               | 31         | 40         |          | dB    |

| VGA Output DC Offset                                     |                                               |            |            | 35       | mV    |

| Total Supply Current:                                    | RX Mode                                       | 36         | 50         | 60       | mA    |

|                                                          | LO Buffer enabled only                        | 3          | 4          | 5        | mA    |

|                                                          | Sleep Mode                                    |            | 1          | 100      | μΑ    |

| Power Supply Range                                       |                                               | 2.7        | 3.6        | 5.0      | V     |

| Operating Temperature Range                              |                                               | <b>–10</b> | 25         | 70       | ္နင   |

<sup>\*</sup> These measurements are taken with the recommended LNA input matching and proper decoupling caps for VCC, as described in the Technical Description section.

Table 3. Absolute Maximum Ratings

| Parameter           | Symbol           | Min             | Max | Unit |

|---------------------|------------------|-----------------|-----|------|

| Storage Temperature | T <sub>STG</sub> | <del>-4</del> 0 | 125 | °C   |

| Power Dissipation   | P <sub>D</sub>   | _               | 500 | mW   |

| LNA Input Power     | RF <sub>IN</sub> | _               | +5  | dBm  |

| Supply Voltage      | V <sub>cc</sub>  | 0               | 5.5 | V    |

| Input Voltage Range | _                | GND             | VCC | V    |

| LO Input Power      | PLO              | _               | +5  | dBm  |

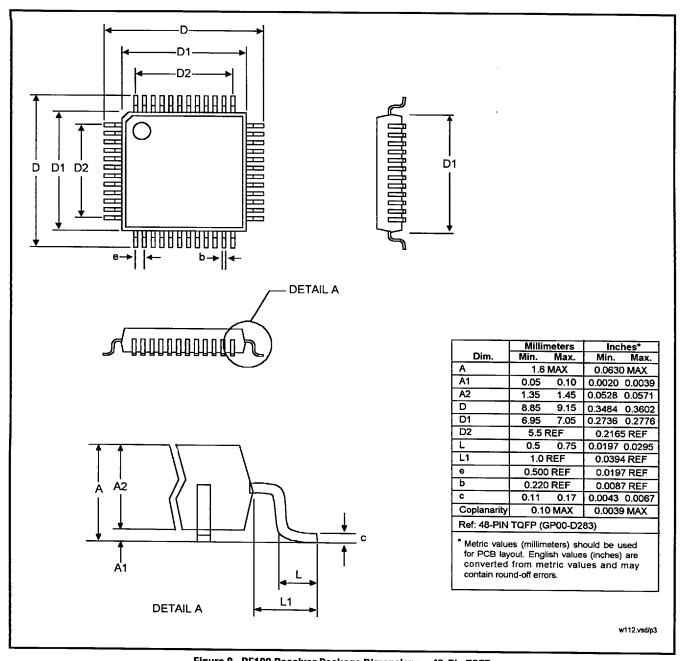

### **Module Dimensions**

RF100 Module dimensions are shown below in Figure 8.

Figure 8. RF100 Receiver Package Dimensions – 48-Pin TQFP

Information provided by Rockwell International Corporation is believed to be accurate and reliable. However, no responsibility is assumed by Rockwell International for its use, nor any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent rights of Rockwell International other than for circuitry embodied in Rockwell products. Rockwell International reserves the right to change circuitry at any time without notice. This document is subject to change without notice.