# QProx™ QT9701B2

## CHARGE-TRANSFER CAPACITANCE SENSOR IC

- Auto calibration on demand

- Multistage internal digital filtering including median filter

- 200µs minimum response time

- 200ns to 1.4µs selectable drive pulse width

- 4-stage charge cancellation for large load capacity

- Pseudorandom burst modes

- Programmable sensitivity, hysteresis, response time, digital filtering, detection mode, drift compensation

- Extensive post-detection processing

- Analog sample gate control line

- LED status indication

- Shorted electrode detection

- Uses cloned eeprom setups from E2SR board

- SPI and UART serial interfaces to 5MHz data rate

- AD7303 SPI DAC drive support for analog output

- 5 volt single supply operation

## APPLICATIONS

- ◆ Fluid level sensing

- ◆ Security sensing

- ◆ Moisture detection

- ◆ Switch replacement

- ◆ Distance gauging

- ◆ Material properties analysis

- ◆ Human presence detection

- ◆ Collision avoidance

- ◆ Transducer drivers

## DESCRIPTION

The QT9701B2 is an enhanced version of the QT9701B. It is both functionally and pin compatible with that device; the additional features of the 'B2' are fully transparent when the device is used in a 'B' circuit. Operation in the 'B' mode is referred to as 'Mode 1'; enhanced B2 functions are referred to as 'Mode 2'.

Enhancements over the QT9701B include an additional median filtering option, a 5MHz SPI serial port output, a bidirectional UART serial port, synthetic analog output capability, Setups cloning capability (both in and out), and reversible output and transfer-switch drives. Data transmitted can include raw or filtered analog, condition codes, reference level, or the detection integrator count. The UART serial port allows all the Setups of the device to be completely reprogrammed from an MCU. The serial protocol is the same as that used in the E2SR board, and the device is fully compatible with QTWinView™ PC software.

The QT9701B2 includes a fast onboard ADC for signal acquisition and incorporates high speed digital signal processing to deliver up to 200µs response times. Virtually all internal processing function can be enabled, disabled, or altered to suit a specific application by the simple addition of an inexpensive 8-pin serial e<sup>2</sup>eprom.

The QT9701B2 can perform a 'learn by example' autocalibration, where the object to be sensed is presented and 'learned' to create the proper threshold point. It is also possible to recalibrate the device remotely on demand via an external control line or over the serial port. The numerous autocal methods eliminate the need for potentiometer adjustments. Sophisticated threshold options allow detection on positive or negative signal swings, or both, and can incorporate preset time delays before final detection confirmation.

Applications include noninvasive continuous level sensing, displacement measurement, human proximity, moisture measurement, Robotic sensors, transducer interfaces, and switch replacement.

The device requires only a single +5 volt regulated supply, for example from a common 78L05 3-terminal regulator.

## AVAILABLE OPTIONS

| T <sub>A</sub>  | SOIC (S)    |

|-----------------|-------------|

| 0°C to +70°C    | QT9701B2-S  |

| -40°C to +85°C  | QT9701B2-IS |

| -40°C to +125°C | QT9701B2-ES |

## 1 - OVERVIEW

The QT9701B2 is a superset of the popular QT9701B QProx sensor IC. It adds enhanced filtering and I/O capabilities while remaining 100% backwards compatible with the QT9701B.

The QT9701B2 implements all charge-transfer (QT) control and signal processing functions necessary to make a highly sensitive and stable capacitance sensor. Only a few low cost external parts are required to make the unit fully functional; these can be readily selected for a specific range of capacitance detection.

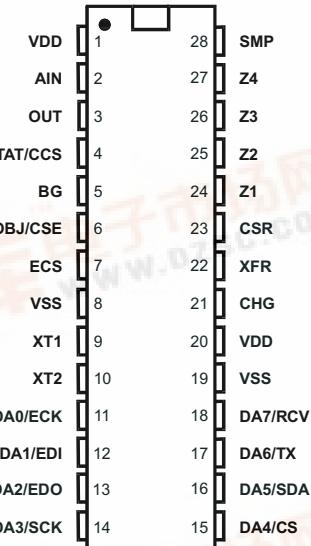

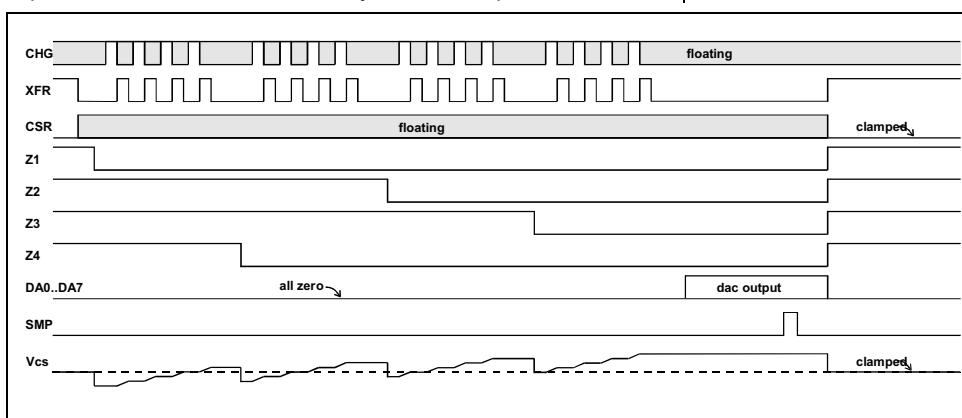

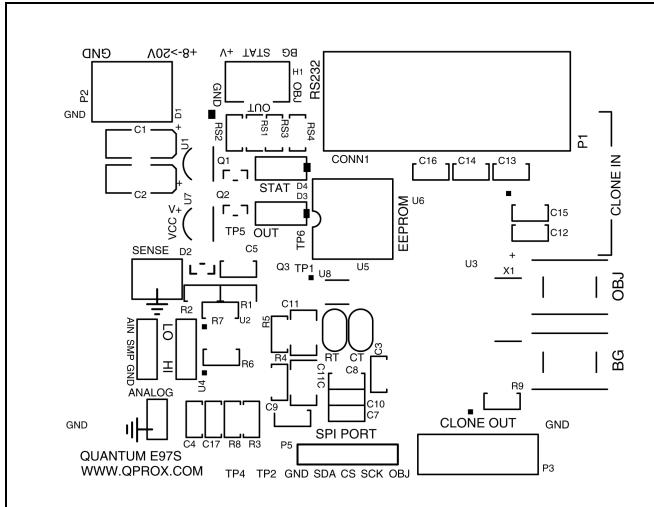

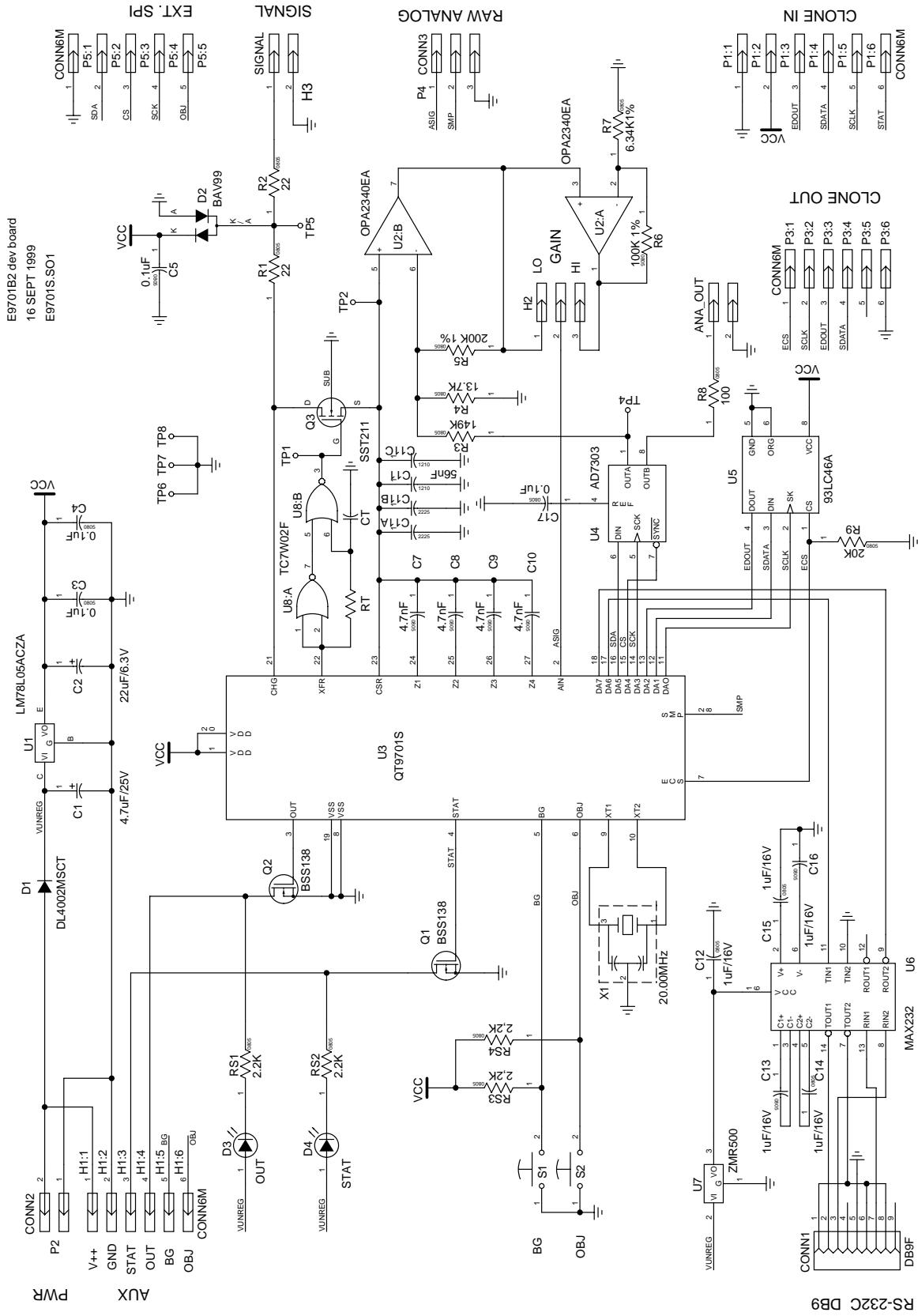

A block diagram of the device is shown in Figure 1-1. Figure 10-4 shows a typical sensor circuit using the device. □

## 1.1 BASIC OPERATION

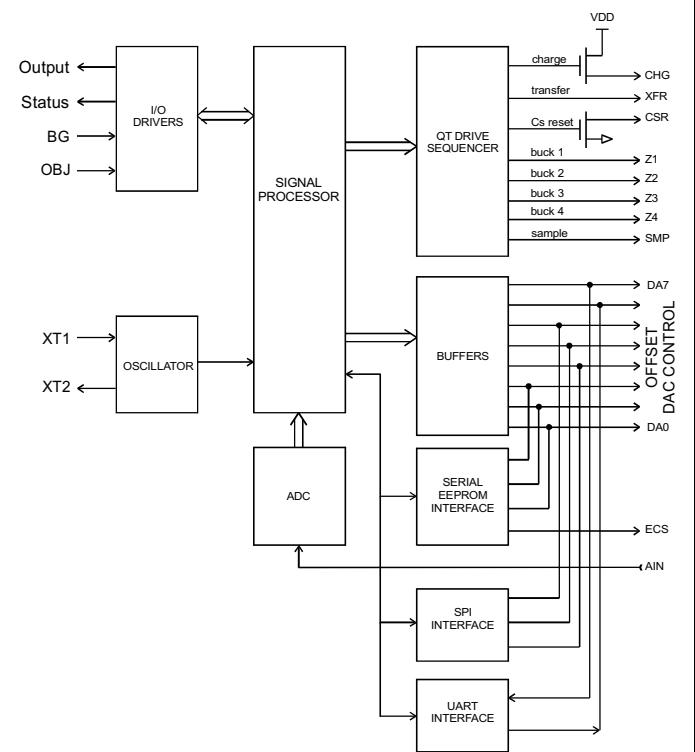

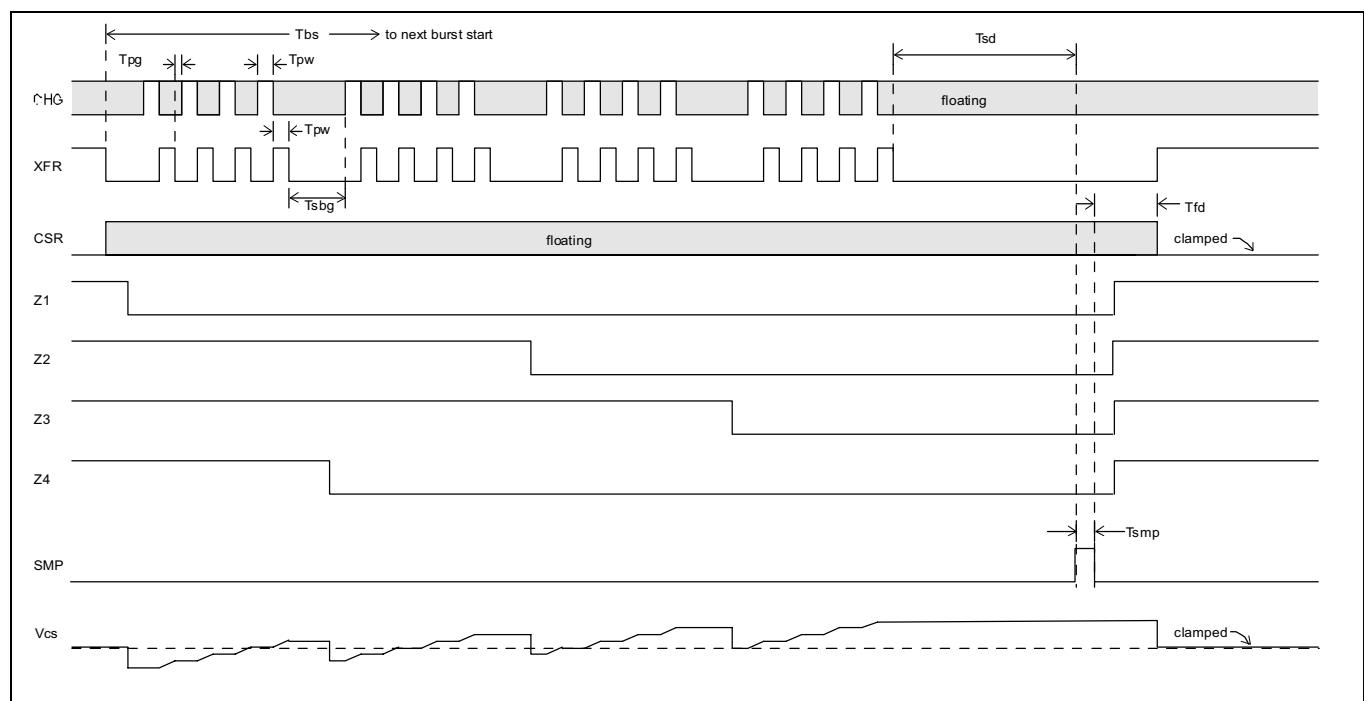

The QT9701B2 is a burst mode QT controller. QT cycles are executed via bursts of pulses on control lines CHG and XFR. CSR is provided to reset the charge detection capacitor  $C_s$ , and line SMP is provided to permit analog sampling of the amplifier signal, to create a direct analog output if desired. The number of pulses per burst is controlled via an external e<sup>2</sup>prom, or in the absence of an e<sup>2</sup>prom, it is set to 64 / burst. Timing information is found in Figure 11-1.

With each XFR control pulse, charge accumulates on cap  $C_s$ . The more transfer pulses within a burst, the higher the gain, but also the higher the accumulation of charge due to stray  $C_x$ . More transfer pulses also produce an averaging effect, with  $C_s$  acting as an integrator to produce an average of all charge accumulated within a burst. The voltage on  $C_s$  may become large enough to produce a significantly nonlinear response; charge cancellation methods are used to 'buck' the accumulation of charge as described below.

At the end of each burst, the amplified signal from Cs is converted to digital in the device and further processed. Internally the device contains several selectable processing paths which may be employed to filter noise, compensate for signal drift, and create different sensing effects.

The sensor also provides a STAT pin which acts to indicate the current state of the sensor, and an OUT pin which provides the primary output when the signal reaches a predefined criteria such as exceeding a specified signal level. The device also features a bidirectional UART based interface which can both program the e<sup>2</sup>prom and download data and status from the device in real time. It also has a synchronous SPI interface, running at a 5MHz transfer rate that can be used to off-load data.

## 1.2 BACKGROUND CX SUPPRESSION

Stray background 'Cx' is an extremely important factor in many sensor systems. For example, an attempt to convey the capacitance effect to a remote object often requires a shielded

cable which will add an offset capacitance. There are many other possible sources of such loading, for example the electrode itself, which may be in close proximity with another surface. In most cases background 'Cx' is vastly greater than the signal to be observed, and without some compensating mechanism can swamp the sensor.

The QT9701B2 employs two strategies for suppressing background Cx.

### 1.2.1 Cz Charge Cancellation

The first method of charge cancellation involves the use of

## FIGURE 1-1 BLOCK DIAGRAM

external capacitors Cz1 through Cz4, and corresponding IC pins Z1 through Z4. Normally Z1..Z4 are held to Vcc while CSR clamps Cs to ground. During the course of a burst, CSR is released, and one or more of lines Z1..Z4 may be driven to ground in sequence. Each burst is composed of 4 'sub-bursts' as shown in Figure 1-2; if the charge that accumulates on Cs is larger than about 0.3 volts, one of the Z1..Z4 lines will transition

## FIGURE 1-2 BURST WAVEFORMS

sub-bursts remains constant, while the number of pulses within each sub-burst is altered.

The amount of each bucking step is easily computed by the ratio of the values of Cz to total capacitance:

$$[1] \quad V_Z = \frac{-V_{cc} \cdot C_Z}{C_S + 4C_Z}$$

where all Cz's are equal.

Four Cz's are not always required, and in lightly loaded systems none at all may be needed. In certain applications the background load may be quite predictable or limited to a maximum value, and so the number of Cz caps can be held to a minimum. Adding Cz caps reduces system gain unless Cs is reduced to compensate.

### 1.2.2 DAC Charge Offset Circuit

The second way background Cx is accommodated involves an R2R ladder DAC driven via pins DA0 - DA7 (in Mode 1 operation) or an AD7303 serial DAC (Mode 2). After a burst has completed, but before the ADC conversion begins, this DAC is driven to a level calculated to bring the amplified signal to within a suitable portion of the ADC's range. The DAC value required to do this is iteratively determined during the self-cal process.

During the self-calibration process, the device acts to find the optimum combination of Cz charge cancellation and DAC offset. It does so by first setting the DAC offset to a high value and then applying increasing amounts of Cz cancellation in successive steps until the signal is below 0.3 volts of Vcs, as required. Then, the value of the DAC offset is fine tuned to bring the analog signal into the desired range specified by the Reference Offset setting (Setup [2] - see Table 7-1).

Cz cancellation and the DAC offset are fixed while the sensor runs. If an e<sup>2</sup>prom is installed, these values of cancellation and offset can be stored for reuse on successive power-ups, otherwise a recalibration on each power up will be performed.

## 2 - OPERATING MODES

### 2.1 MODE 1

Mode 1 is the QT9701B - compatible mode; it is engaged either by operating the device without an external e<sup>2</sup>prom, or by having an e<sup>2</sup>prom whose setting [U] is set to '0' (see Table 7-1). All data and operation pertaining to the QT9701B2 in Mode 1 can be found in the QT9701B data sheet.

The device offers three enhancements over the QT9701B in Mode 1: 1) An additional Median filter of length 9; 2) Selectable OUT and XFR polarities; 3) Ability to force default settings into the e<sup>2</sup>prom on a cold restart if desired.

### 2.2 MODE 2

Mode 2 is the enhanced operating mode, and is entered by setting setup [U] to 1 or

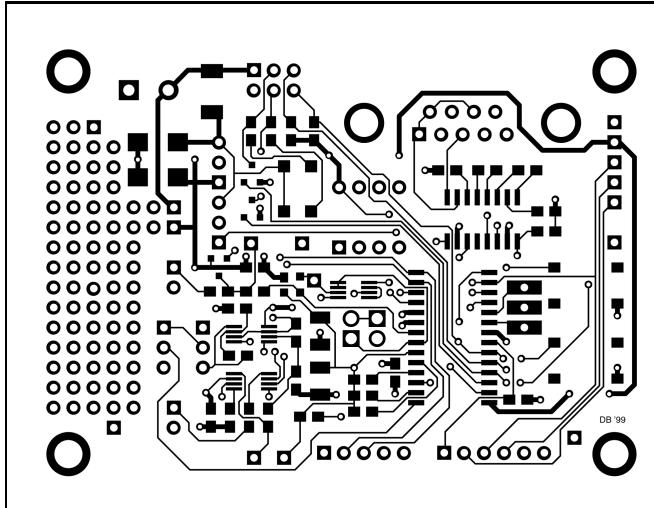

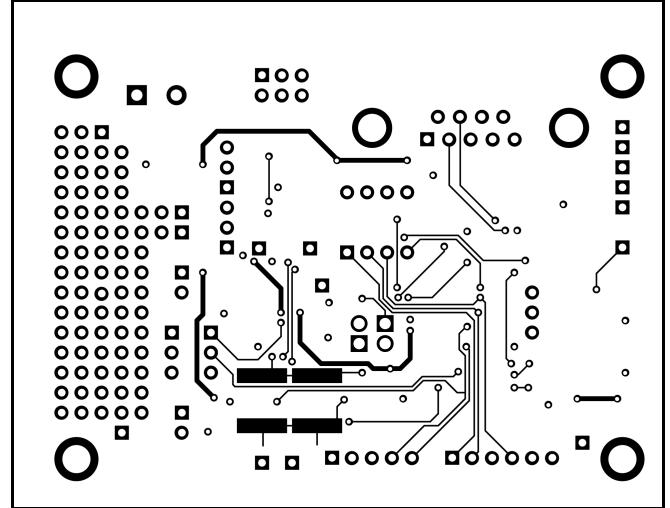

higher (see Table 7-1). The R2R ladder DAC must be replaced by an Analog Devices AD7303 dual 8-bit DAC for proper operation or an external CMOS shift register and an R2R ladder. No other circuit changes are required for Mode 2, although other circuit enhancements are supported. Refer to Figure 10-4 for a schematic of the E97S eval board which uses the enhanced hardware features.

### 2.2.1 DAC Offset Circuit

The Mode 2 DAC must be an AD7303 dual 8-bit ADC, or a shift register connected to a parallel DAC for proper operation. Refer to Figure 5-1. The shift clock SCK is found on pin 14, data SDA on

**TABLE 1-1 PIN DESCRIPTIONS**

\*Functions available only in Mode 2

| PINS  | NAME      | TYPE | DESCRIPTION                                                                                                                                                                                                                                          |

|-------|-----------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 20 | Vdd       | Pwr  | Power pin to +3 to +5 volts regulated.                                                                                                                                                                                                               |

| 2     | AIN       | I    | Analog input from opamp, range Vss to Vdd.                                                                                                                                                                                                           |

| 3     | OUT       | O    | Detection line output. *Active high or low depending on Setup [J].                                                                                                                                                                                   |

| 4     | STAT/*CCS | O    | Status line, intended primarily for driving an LED to give a visual indication of sensor health and state.<br>*Additional Mode 2 function: Secondary function is as an enable-high line to a 'clone in' eeprom temporarily connected to the circuit. |

| 5     | BG        | I    | Background calibration input line, active low.                                                                                                                                                                                                       |

| 6     | OBJ/*CSE  | I/O  | Object calibration input line, active low.<br>*Additional Mode 2 function: Generates a negative framing pulse for an external SPI device to receive data from the 9701B2, of 8 or 16 bits length.                                                    |

| 7     | ECS       | O    | Eeprom enable line. To prevent startup transients from affecting the external eeprom it is advised to use a pull-down resistor of 10K to 20K ohms. Also issues a positive 1us pulse prior to each burst for diagnostic use.                          |

| 8, 19 | Vss       | Pwr  | IC negative supply (ground).                                                                                                                                                                                                                         |

| 9     | XT1       | I    | Crystal or resonator input pin. If desired this pin can be driven from an external source, saving a part. If a crystal or resonator is used on XT1 / XT2, the pin should be loaded with a 20pf to 27pf capacitor to Vss.                             |

| 10    | XT2       | O    | Crystal or resonator output pin. If desired this pin can also drive another device if lightly loaded or buffered. If a crystal or resonator is used, the pin should be loaded with a 20pf to 27pf capacitor to Vss.                                  |

| 11-18 | DA0-DA7   | O    | Outputs the DAC value for an external R2R ladder network to create an offset for the external amplifier chain. Note additional alternate functions below.                                                                                            |

| 11    | ECK       | O    | Clock output to the serial eeprom.                                                                                                                                                                                                                   |

| 12    | EDI       | O    | Serial data output line to serial eeprom                                                                                                                                                                                                             |

| 13    | EDO       | I    | Serial data input line from serial eeprom                                                                                                                                                                                                            |

| 14    | *SCK      | O    | *Mode 2: Serial SPI clock                                                                                                                                                                                                                            |

| 15    | *CS       | O    | *Mode 2: Chip select line to AD7303 DAC                                                                                                                                                                                                              |

| 16    | *SDA      | O    | *Mode 2: SPI data output line to AD7303 / other SPI device(s)                                                                                                                                                                                        |

| 17    | *TX       | O    | *Mode 2: Transmit uart data from the device                                                                                                                                                                                                          |

| 18    | *RCV      | I    | *Mode 2: Receive uart data to the device                                                                                                                                                                                                             |

| 21    | CHG       | O    | Charge line to drive a sensor electrode                                                                                                                                                                                                              |

| 22    | XFR       | O    | Control line to drive an external transfer fet                                                                                                                                                                                                       |

| 23    | CSR       | O    | Control line to reset the Cs capacitor between bursts                                                                                                                                                                                                |

| 24-27 | Z1-Z4     | O    | Charge cancellation control lines to drive Cz1 - Cz4                                                                                                                                                                                                 |

| 28    | SMP       | O    | Sampler control line to sample external analog signal                                                                                                                                                                                                |

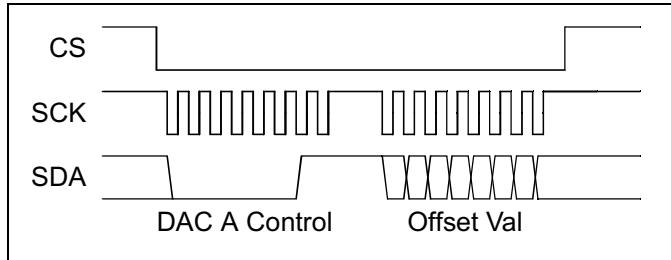

16, and sync frame CS on 15. The data is shifted out using standard SPI protocol, and clocked into DAC\_A of the AD7303 on the rising edge of SCK. Two bytes are transmitted to generate the control and data bitstream required by the AD7303.

### 2.2.2 Synthetic Analog Output

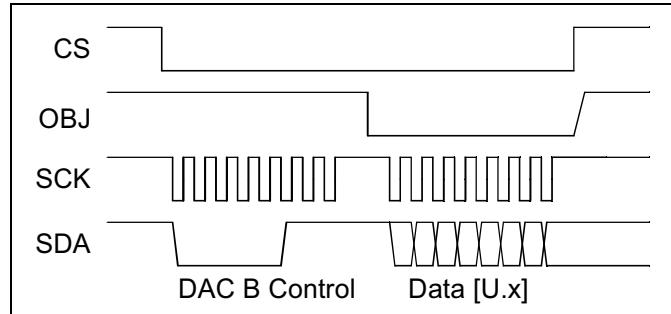

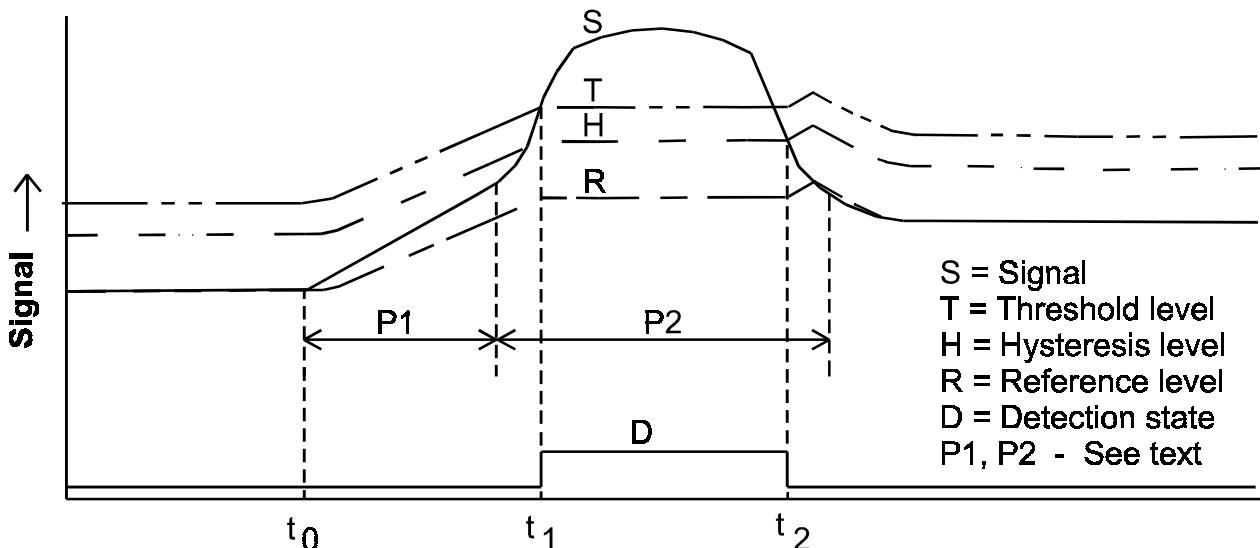

Synthetic analog, of a type determined by Setup [U], is output on AD7303 DAC\_B once shortly after each burst. The data is sent to the DAC using the SPI protocol and timings shown in Figure 5-2 or Figure 5-3, as framed by the CS line.

### 2.2.3 External Data SPI Port

The same port used to drive the AD7303 can also be used to send data to an external circuit. After each burst, data is transmitted over SDA, clocked by SCK, and framed by a negative pulse on the OBJ line. OBJ is open-drain, and must be pulled high by a 2K to 2.2K resistor to create the framing pulse. OBJ function is not compromised by this dual-usage of pin 6. An external interface to OBJ should use an open-drain (or open-collector) drive to prevent interference with framing pulse. Both 8-bit and 16 bit transmissions are possible; in a 16 bit transmission the second byte framed by OBJ (the third actual byte in the sequence) is a Status codes byte. Figures 5-2 and 5-3 show the waveforms associated with these transmissions.

### 2.2.4 UART Circuit

An interface to an external host MPU is possible using a full-duplex serial port running from 9600 to 115.2kbaud. The protocol is the same as that described in the E2SR manual, and the QT9701B2 is fully compatible with QTWinView software. There is no hardware handshaking. Both verbose and polled communications are possible; the baud rate and communications mode are determined by setup [G]. A MAX232-type interface driver circuit is all that is required to implement true RS232 communications. When interfacing directly to a host MCU, the MAX232 is not needed.

The RS232 interface should have its own voltage regulator, since these devices generate considerable switching noise on Vcc from their internal charge pumps and from the current transients generated from driving the capacitance of long cables.

## 3 - CIRCUIT OPERATION

### 3.1 QT DRIVE CIRCUITRY

The QT9701B2 allows for inverted transfer switch drive: this allows use with certain types of n-channel bus-switches known for having particularly low resistance and low charge injection. The polarity of the transfer switch drive is determined via setup [J].

#### 3.1.1 Using a Mosfet Transfer Switch

If using a mosfet transfer switch, it should be an n-channel enhancement device. The Philips BSN20 (smt) is reasonable for general purpose use. Lateral DMOS devices like the Calogic SST211 (smt) are better parts in general; they have very low amounts of charge injection, although their higher on-resistance which may limit their use with short pulsedwidths in some cases.

#### 3.1.2 Using a 'Bus Switch' Transfer Switch

The 9701B2 is also capable of driving single-gate 'bus-switch' mosfets, like the Texas Instruments SN74CBT1G125 (single, SOT23-5) or Quality Semiconductor QS3125 (quad, SO14). These are low cost devices with low charge injection and excellent thermal stability. They are active-low enable, thus the polarity of the transfer drive must be selected as 'LOW' in Setups [J].

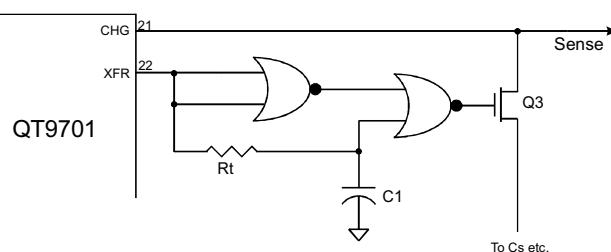

#### 3.1.3 Shortening Tpw Further

In some cases it is highly desirable to suppress the effects of moisture in and around the electrode, or to help ascertain the bulk properties of a substance without reacting much to moisture

content. There are also times when external interference must be suppressed further than simple signal processing can achieve. Shortening the transfer time to below 200ns is possible with the aid of some external circuitry (Figure 3-1). This circuit will generate almost arbitrarily short transfer times, to the limits of the gate and switch propagation delays. Rt and Ct can be adjusted using an oscilloscope; a trimpot can be used for Rt if desired.

This circuit can be disabled by removing Rt, while jumpering Ct to ground. When using this circuit it is important to keep the width Setups at 200ns ([4.0]).

Transfer switch closure time should be long enough so that transfer efficiency does not suffer. Very short transfer times (<100ns) can produce unpredictable results if significant ground and signal lead inductances are present, or if the matter to be sensed is of varying electrical conductivity. In general, signal levels and gain will appear to drop with shorter transfer times due to the increasing inability of the field currents to settle before the end of the transfer period.

### 3.2 DAC REQUIREMENTS

An 8-bit DAC is required in most implementations to provide a subranging ADC system. The DAC is used to 'servo' the analog signal to a range within the input limits of the on-board 8-bit ADC.

**In Mode 1:** An inexpensive 8-bit R2R ladder DAC is used. The CMOS drive of the device functions to drive this R2R DAC, with no further buffering required. The R2R should be 50K ohms or higher in value. CTS's p/n 750-107R100K (SIP) is suitable for this function.

**In Mode 2:** An Analog Devices AD7303 dual SPI DAC can be used. The second half of this DAC can also be driven by the QT9701B2 to create a synthetic (signal processed) analog output. Alternatively, an 8-bit CMOS shift register can be coupled to the SPI port and used to drive an R2R ladder of the type described above.

### 3.3 AMPLIFIER REQUIREMENTS

The external amplifier can be almost any moderate speed rail-to-rail output and ground-sensing input CMOS or JFET input device having a 2MHz GBW or better. Bipolar input opamps are to be avoided due to their higher input currents. Amplifiers in the same class as the TI TLC2272 and Burr Brown OPA2340 are acceptable. Two gain stages should be cascaded for if desired total gain is above 25; attempting to achieve a very high gain in one stage can result in settling time problems. It is advisable to use opamp feedback resistor values of under 200K ohms to speed settling times, these should be placed very close to the opamp pins to reduce parasitic capacitances.

There is generally no problem in using the same Vcc supply for the opamp as for the QT9701B2, provided normal supply bypassing is performed.

Figure 3-1 Circuit for Short Transfer Times

### 3.4 EXTERNAL EEPROM; CLONING

The external 93LC46A (Microchip) e<sup>2</sup>prom should be used; its contents can be cloned in from an external source (Section 3.4).

Substitute devices should have both byte-access and streaming-access modes. Many variants of the 93LC46A are only word access or non-streaming and will not function. The e<sup>2</sup>prom's contents are described fully in Section 12. A plain blank e<sup>2</sup>prom will be ignored. Refer to Table 7-1 for the Setup modes which can be enabled and altered using the external e<sup>2</sup>prom.

#### 3.4.1 Cloning-In of Setups

Cloning in from an external e<sup>2</sup>prom requires that the external e<sup>2</sup>prom's IO pins be free. An E2SR board running in its Setup mode does this, for example. The STAT line is used to enable the external e<sup>2</sup>prom being accessed. Also, after a successful clone-in the STAT line will flash 5 times in quick succession.

The QT9701B2 checks for the presence of an external cloning e<sup>2</sup>prom source during powerup, and also just after the OBJ line is asserted low momentarily and then released; if an external e<sup>2</sup>prom is found it will be read and copied in to the onboard e<sup>2</sup>prom. The clone source should be removed immediately after the STAT confirmation pattern begins.

It is also possible to force a clone function via the serial port, using a Forced Reset (Section 4.4.6) to cause the device to scan for an external e<sup>2</sup>prom.

#### 3.4.2 Cloning-Out of Setups

Cloning out to another QProx product requires that the 93LC46A connected to the QT9701B2 have its control lines floating. This occurs only while the OBJ line is held low. It is possible to clone to another QT9701B2 circuit, for example, thus created a low-cost e<sup>2</sup>prom duplicator for moderate volume production use.

#### 3.4.3 ECS Line

The ECS line (pin 7) enables the e<sup>2</sup>prom for reading and writing; it is active-high. It also produces a 1us positive pulse just prior to each burst for diagnostics; this pulse does not interfere with the operation of the e<sup>2</sup>prom. The ECS line should be pulled low with a 10K to 20K resistor to prevent power-up transients from causing false-writes to the e<sup>2</sup>prom.

### 3.5 OUT PIN

The OUT pin can be made active high or active low. The polarity of Out is determined by Setup [J].

OUT becomes active if the signal has crossed a threshold detection level and the appropriate Setups are engaged to allow OUT line to indicate detections. Setup functions are described in detail in Sections 7 and 8.

OUT can also become active if the CHG pin detects a short circuit to ground.

### 3.6 STAT PIN

STAT operates the same as in the QT9701B, but in the B2 it is also used to indicate the success of a clone-in operation. After a successful clone-in it will flash 5 times in quick succession. There is no indication for clone-out.

The STAT line acts as a multipurpose indicator that shows output state, error conditions, and input feedback. It is designed to drive an LED for meaningful operator feedback. STAT will output as follows depending on sensor state:

**Running and not detecting:** STAT outputs a positive 10ms pulse at a 10Hz rate (10% duty cycle); on an LED this generates a low, very noticeable flicker.

**Running and detecting:** STAT outputs a positive 90ms pulse at a 10Hz rate (90% duty cycle); on an LED this generates a bright but flickering output.

**When an input line (BG or OBJ) is evoked:** STAT is forced low for the duration the input line is held low.

**If BG or OBJ are evoked for >2secs:** After input release, STAT will go "solid high" for 3/4 second before it enters the new mode.

**While calibrating:** STAT will be forced "solid low"; this usually takes well under a second.

**If CHG is shorted to ground while normally running:** STAT will go "solid high" for the duration of the short.

**On a calibration error:** STAT will output a repeating error code, provided that Output Error Code [E.a] is 'on':

**Single repeating pulse:** CHG shorted to ground

**Double repeating pulse:** Excess capacitive load

**Triple repeating pulse:** Unstable signal, cannot calibrate

The device will repeatedly try to recalibrate between each set of 'Morse code' outputs. If [E.a] is off, the recalibration attempts will be much quicker, since the STAT codes are not output.

The repeating STAT code pulses are 250ms in duration with a 250ms dead time between pulses; between coded pulse groups there is a minimum 750ms dead time

### 3.7 SMP LINE

The SMP line is an active-high sample gate that can close a 74HC4066-type analog switch briefly at the end of each burst to sample-and-hold the resulting raw signal. The pulse is 4.2us wide.

### 3.8 BG / OBJ INPUTS

These control logic inputs are active low, and to use them should be pulsed low momentarily for at least the burst spacing duration; thus, if the burst spacing is 1ms, the line should be held low for at least 1ms. To engage the BG or OBJ "mode override" functions the line should be evoked for >1.6 seconds prior to release. Note that if only a simple BG or OBJ recal function is desired, it is important to not hold the line low so long that this override feature is engaged. Refer to Section 3.15 for more information about the BG and OBJ modes.

### 3.9 OSCILLATOR

Almost any 20MHz ceramic resonator will work. A quartz crystal will also function, but aside from a slight boost in accuracy, and longer startup time. The resonator should have two capacitors to ground on either side, of 15pF to 27pF. 3-pin devices having internal capacitors are available, saving considerable board space and cost.

An external oscillator having CMOS drive levels may also be used, by connecting the oscillator to pin 9 and leaving pin 10 open. The oscillator should have a 45% to 55% duty cycle.

Lower frequencies may be used if desired for reduced power consumption, however all timing functions are slaved to the oscillator and will thus slow down as well.

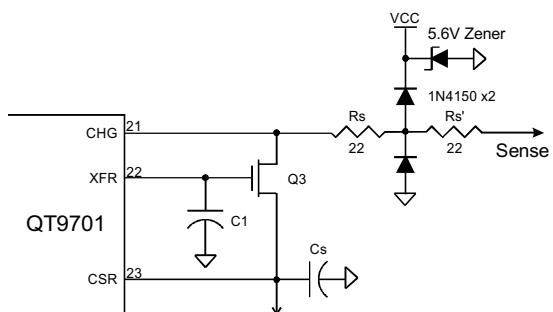

### 3.10 INPUT PROTECTION

The CHG drive and BG and OBJ lines are internally protected from ESD by clamp diodes, however, this should not be relied upon as a primary means of protection. It is highly recommended that any pins exposed to the outside world, including CHG, be clamped via two high speed, high conductance, low-C silicon diodes like type 1N4150 or BAV99 (smt), one from ground to the pin, and the other from the pin to Vcc or to a zener diode biased up to at least the level of Vcc, and that a resistor be placed between these clamp diodes and the CHG pin to further limit pin currents. See Figure 14-1.

Note that the QT9701B2 forces the XFR line high and clamps the CSR line low between bursts to self-clamp and dissipate ESD currents.

### 3.11 CHG SHORT CIRCUIT DETECTION

The QT9701B2 can sense shorts to ground on CHG. When a short is detected, the OUT and STAT lines are forced active for the duration of the short. Short detection operates by monitoring output current through the internal p-mosfet device; external ESD circuits that include a series resistance can limit this current artificially, thus rendering the short detection system ineffective. Operation of the short detection circuit is thus not guaranteed under all conditions and should only be relied upon as a backup detection method. Also, note that the device cannot determine open electrode conditions.

### 3.12 POWER SUPPLY AND PCB LAYOUT

The device requires a stable, noise-free power supply. A low cost 78L05 class regulator will work fine for virtually all applications, but it should not be shared with devices that can produce transients or erratic loading. Designs should use a regulator specifically for the QT9701B2 if possible; testing can determine if the regulator could be shared with other circuitry.

The 78L05 should be properly bypassed on its input and output. Its input supply should also be relatively stable and noise-free so as to minimize feedthrough noise components via its pass transistor. A 22 $\mu$ F tantalum or 100  $\mu$ F low-Z aluminum capacitor is recommended on the output of the 78L05.

A PCB ground plane or copper pour area throughout the circuit is highly recommended. Other circuits, including any output driver transistors, should not allow their currents to flow through the sensor's circuit area; grounds should always be led back to a common tie point at the point near the entry of the supply onto the PCB in accordance with customary "sensitive analog" practice.

Sense lead clamp diodes should shunt ESD currents back to earth via the most direct route possible, without traversing the area of the circuitry; ESD return currents should also not share a common ground path with the sensor circuitry. These clamp diodes should shunt as directly to a board mounting hole (or other major ground tie point) as possible. Positive clamped ESD currents are often neglected in designs; they should be shunted via a high quality low inductance bypass capacitor and/or zener back to the same ground tie point.

Component location is relatively unimportant and non-critical, with the above noted exceptions, and the circuit can easily be implemented on a 2-layer PCB.

### 3.13 ANALOG OUTPUT VIA SMP LINE

An analog output may optionally be obtained using a sample and hold circuit. The QT9701B2 provides a sample pulse (SMP) which is a positive-drive pulse timed to coincide with a stable portion of the output of the signal amplifier chain.

The sample and hold can be made of a 74HC4066 type switch and a 1nF ceramic capacitor, followed by a CMOS buffer amplifier.

When using a S/H circuit to obtain an analog output, avoid using a quad opamp shared also as the main gain amplifier, instead of two separate packages. The slew rate and loading of the S/H buffer can produce major disturbances in other opamps on the same die.

The SMP line should never be routed near the Cs sample cap or the amplifier opamp chain, as this pulse can easily superimpose a severe transient on the signal at the exact moment where it should be stable.

### 3.14 - SENSOR RESOLUTION

The sensor's overall sensitivity is a function of several factors, including:

1. Total sampler capacitance,  $C_s + (C_{z1} \dots C_{z4}) = C_t$

2. Burst length, N

3. Total amplifier gain,  $A_V$

4. ADC resolution, bits, n

5. Power supply voltage,  $V_s$

Differential gain at the output of the operational amplifier is determined by:

$$[2] \quad \frac{N V_s A_V}{C_t} \quad \{\text{volts / Cx}\}$$

The ADC resolution is defined in terms of volts per level, resulting in the following overall sensitivity equation:

$$[3] \quad \begin{aligned} \text{Sensitivity} &= \frac{\text{ADC resolution}}{\text{differential gain}} \\ &= \frac{V_s / (2^n - 1)}{N V_s A_V / C_t} \\ &= \frac{C_t}{N A_V (2^n - 1)} \quad \{\text{Cx per ADC level}\} \end{aligned}$$

Given:  $C_t = 0.056 \mu\text{F} + 4 \times 0.0047 \mu\text{F} = 0.0748 \mu\text{F}$

$N = 64, A_V = 284, n = 8 \text{ bits}$

Then the overall sensitivity is about 16 femtofarads per ADC level. This can easily be adjusted by altering any of three parameters: N, which can be altered in the e<sup>2</sup>prom setups, amp gain  $A_V$ , and total sampler capacitance  $C_t$ .

Note that supply voltage  $V_s$  conveniently drops out of the equation - thus, the sensor is largely immune to slow changes in supply voltage, although it can be sensitive to transient supply excursions which do not equally affect all aspects of the acquisition process.

### 3.15 BG, BG/OBJ, AND OBJ MODES

The QT9701B2 operates in either of two primary calibration modes:

1. **'Normal' mode:** sensor makes use of the setting of Detect Threshold. This mode is the factory default setting. Evoking BG in 'normal' mode simply causes a recalibration to occur, that is, the reference point is recentered and with it the threshold level(s). 'Normal' mode is BG mode and is referred to as BG mode.

2. **'Learn' mode:** The sensor ignores Detect Threshold, and 'learns by example'. There are two variations of 'Learn' mode: BG/OBJ, and OBJ.

**Switching modes:** These modes can be entered into at will by the use of the BG and OBJ control lines as explained below.

**Making the mode permanent:** The selected BG, BG/OBJ or OBJ mode can be stored "permanently" into the external e<sup>2</sup>prom if present, but only if Data Locking [F.b] is on. The mode can be changed at any time and is automatically stored again into the e<sup>2</sup>prom, overwriting the prior mode. If Data Locking is set to 0 or 9, or if the e<sup>2</sup>prom is absent, the unit will always power up in BG mode and immediately perform a full calibration after startup.

**Mode manipulation over the UART port:** The BG, OBJ, and BG/OBJ modes can be modified at will via serial (UART) commands. A serial command operates exactly like a port pin assertion, with the exception that a 'long' assertion is replaced by a capital letter command. For example, To assert a BG command, the lowercase letter 'b' is sent to the device. To assert a BG override command, the letter 'B' is sent. The OBJ command is accomplished via the letters 'o' and 'O'. Refer to Section 4 and Table 4-1 for details.

#### 3.15.1 When to Use Each Mode

Mode selection depends on the sensing effect desired.

**BG:** BG mode is designed to allow advanced processing functions like "prox trap" while also permitting drift compensation. BG only requires a single command to calibrate to the background level, but the threshold level must be set via the e<sup>2</sup>prom and cannot be 'learned'. BG will also permit maximized sensitivity with background reference drift tracking at all times. It will also permit 'motion' detection processing, where motion in either direction will cause a detection. OBJ and BG/OBJ cannot provide these functions.

**OBJ:** Use for detecting objects that generate large signals, where little processing finesse is required. Evoking OBJ will trigger a "learn by example" and set the threshold automatically, and store that setting into the e<sup>2</sup>prom if present. If no e<sup>2</sup>prom is present, this mode must be entered and recalibrated after each power up by evoking OBJ. This is a simple fixed threshold point without knowledge of the background reference level.

**BG/OBJ:** For "learn by example" calibration with continuous background drift compensation. This mode can be thought of as a hybrid between the 'pure' BG and OBJ modes. It requires two input commands, one first on the BG line, then one on OBJ. If no e<sup>2</sup>prom is present, BG/OBJ must be entered and recalibrated after each power up.

The BG input is first used to set the background reference signal calibration point; then, the object to be sensed is introduced to the sense field, and the OBJ line is toggled. The sensor then 'learns' the signal from the object to create a threshold point, but it also still 'knows' the background reference level (hence, 'BG/OBJ'). With the knowledge of the background level, the sensor can compensate for drift when the object is absent.

### 3.15.2 BG Mode Details

In BG mode the threshold level(s) are taken from Detect Threshold [0], while hysteresis is defined by [1]. There are also some further issues related to Data Locking:

If **Data Locking [F.b]** is off or e<sup>2</sup>prom absent, the unit will power up and perform a background calibration to set its initial reference point; the unit will always start out in BG mode if Data Locking is off or the e<sup>2</sup>prom is absent.

If **Data Locking [F.b]** is on, unit will use stored e<sup>2</sup>prom cal settings on powerup and not perform a BG cal. If the BG cal point has changed, it will be necessary to evoke the BG line to recalibrate, or wait until a Max On-Duration expires (if enabled and if a detection is in progress), or wait until drift compensation catches up to the error (if enabled).

Evoking BG (or sending the letter 'b' or 'B' via UART) if already in BG mode causes a full background recalibration; the unit will remain in BG mode. If Data Locking is on, evoking BG will cause the resulting cal data to be stored for reuse on next powerup.

Evoking BG (or sending the lowercase letter 'b' via UART) if in BG/OBJ mode causes a background reference point recalibration, but the prior learned threshold levels will not be altered and BG/OBJ mode will remain in force. See "BG/OBJ Mode Details", below.

If Data Locking is on, the calibration settings resulting from a prior BG evoke will be stored in the e<sup>2</sup>prom for retrieval on any subsequent powerup.

**Forcing to BG mode from OBJ mode:** Evoking BG (or sending the letter 'b' or 'B' via UART) if the device is in OBJ mode will take the device out of OBJ mode and put it into pure BG mode, triggering a BG recal as well.

**Forcing to BG mode from BG/OBJ mode:** If device is in BG/OBJ mode and it is desired to change the mode to "pure BG" mode, evoke the BG line for >1.6 seconds (or send the uppercase letter 'B' via UART). After the BG line is released high, the STAT

line will go "solid high" for 3/4 second and the device will then recal. At this point it will be in "pure BG" mode. If STAT does not go "solid high", the line was not evoked long enough.

### 3.15.3 OBJ Mode Details

OBJ mode is entered by the following process:

**Device has just powered up and is not in BG/OBJ mode:** With a target signal present (target placed at the point of desired detection) evoke OBJ (or sending the letter 'o' or 'O' via UART). Unit learns the correct threshold from the current signal level and enters OBJ mode.

**If device already in BG or BG/OBJ mode:** With a target signal present at the edge of the desired range, evoke OBJ for >1.6 seconds to clear out the BG mode and also to prevent the BG/OBJ mode from being entered (or send the uppercase letter 'O' via UART). Unit enters OBJ mode and learns the correct threshold level.

**If device already in "pure OBJ" mode:** Evoking OBJ (or sending the letter 'o' or 'O' via UART) will cause a new detection threshold point to be learned at the current signal level; unit remains in OBJ mode.

If in doubt, evoke OBJ for >1.6 seconds (or send the letter 'O' via UART). The STAT line will go "solid high" for about 3/4 second and then the device will recal in pure-OBJ mode. If STAT does not go "solid high", the line was not evoked long enough.

**Hysteresis in OBJ Mode:** The hysteresis value is taken from the value of the Detect Threshold setup, or can be forced to zero hysteresis if Hysteresis setting [1] is set to [1.3] (0 hysteresis) via the e<sup>2</sup>prom. If the e<sup>2</sup>prom is absent, the hysteresis is set to 8 counts of signal by default. For example, if the Detect Threshold is set to [0.6], and Hysteresis is set to [1.1], the actual hysteresis used in OBJ mode is fixed at 11 counts of signal.

If the hysteresis is too large for the signals encountered, 'sticking' can occur; the sensor will detect an object (usually immediately after evoking OBJ) and not release. If expected signal levels are small, BG/OBJ mode is a better option than pure OBJ because BG/OBJ will set an amount of hysteresis proportionate to the signal level.

OBJ mode has no knowledge of the background reference level, and so cannot drift compensate for background level changes. OBJ sets a rigidly fixed trip point at an absolute signal level.

OBJ will only work with Detection Mode [D] set to [D.0] or [D.8]. All other settings of [D] are 'truncated' to [D.0] or [D.8], whichever is closest in Table 7-1. Setting [D.8] can make the sensor respond to departing objects (an "absence detector").

If Data Locking is enabled, the resulting OBJ setting and trip point will be stored in the e<sup>2</sup>prom for retrieval on subsequent powerup. Then, when the unit powers up it will use the stored e<sup>2</sup>prom settings and immediately run without recalibrating.

Evoking OBJ mode with only a background level of signal present will usually cause the sensor to stick 'on', and is not advised.

### 3.15.4 BG/OBJ Mode Details

To enter BG/OBJ mode:

1. Following a powerup, evoke BG (or send the lowercase letter 'b' via UART) when the known background signal level is present (object to be detected is absent). Evoking BG will make the device recalibrate and finds its new background reference level.

2. Then, with a target signal present (target object placed at the furthest distance of desired detection) evoke OBJ (or send the lowercase letter 'o' via UART). Unit then learns the correct threshold and sets the correct hysteresis levels.

**TABLE 4-1 - POLLED MODE ASCII COMMAND SET**

| ASCII Code       | Hex Code  | Action                                                                                                                                                                                          |

|------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <                | 0x3c      | Reduces Pulse Width by one Setting to a limit of 200ns. The new setting is written to e <sup>2</sup> prom, but unit does not recalibrate thus allowing comparative signal strength analysis.    |

| >                | 0x3e      | Increases Pulse Width by one Setting to a limit of 1400ns. The new setting is written to e <sup>2</sup> prom. The new setting is written to e <sup>2</sup> prom, but unit does not recalibrate. |

| B                | 0x42      | Performs the BG function (identical to asserting BG line, long) and overrides any BG/OBJ or OBJ mode.                                                                                           |

| b                | 0x62      | Performs the BG function (identical to asserting BG line, short).                                                                                                                               |

| h                | 0x68      | Returns hysteresis value (binary value, range 0..255).                                                                                                                                          |

| l (lower case L) | 0x6c      | Returns last received character                                                                                                                                                                 |

| O (capital O)    | 0x4f      | Performs OBJ function (identical to asserting OBJ line, long); overrides any BG or BG/OBJ mode.                                                                                                 |

| o (lower case O) | 0x6f      | Performs the OBJ function (identical to asserting OBJ line, short).                                                                                                                             |

| p                | 0x70      | Puts device into 'pure' Polled mode. See 'v' below and Sections 4.3, 4.4.                                                                                                                       |

| r                | 0x72      | Resets the sensor. The command must be repeated within 90ms. See Section 4.4.6.                                                                                                                 |

| s                | 0x73      | Places unit into Setups mode, and halts sensing. See 'w' below, and Section 4.4.1.                                                                                                              |

| t                | 0x74      | Returns signal threshold value (binary value, range 0..255).                                                                                                                                    |

| v                | 0x76      | Puts into Enhanced Verbose mode. See 'p' above and Sections 4.3, 4.4.                                                                                                                           |

| V                | 0x56      | Returns part version. The returned byte is 0x21.                                                                                                                                                |

| w                | 0x77      | Write e <sup>2</sup> prom with new Setups; 's' string must end in 'w'. See 's' above, and Section 4.4.1.                                                                                        |

| 0...8            | 0x30-0x38 | Returns binary data per Data Evoke Code (Table 4-2). See Section 4.4.3.                                                                                                                         |

| ^a...^w          | 0x01-0x17 | Returns current Setups value in range 0...9 (0x30...0x39) of the Select item chosen (^a corresponds to Select [0], ^w corresponds to Select [U], where ^a means 'Alt-a' on a PC keyboard).      |

If Data Locking is on (and e<sup>2</sup>prom is present), the resulting calibration data will be stored for retrieval on any subsequent powerup. Then, when the device subsequently powers up again it will use the stored e<sup>2</sup>prom settings and immediately run with them, without performing a recalibration of any sort.

If the device is already in BG/OBJ mode, step 1 will not take the unit out of BG/OBJ mode; instead, step 1 will simply cause a recal of the reference point, leaving the differential threshold value from a prior step 2 alone. A subsequent step 2 can then set a new threshold level if desired.

If the device is already in BG/OBJ mode, evoking OBJ thereafter (repeating step 2) will cause the unit to establish a new 'learn by example' BG/OBJ threshold, leaving the reference level alone. Thus, once BG/OBJ mode is entered via the above 2-step process, you do not necessarily have to repeat step 1 to do a threshold recalibration; after evoking OBJ again it will remain in BG/OBJ mode and just properly recalibrate its threshold level.

If the device is in OBJ mode, it is cleared in step 1; evoking BG when in pure OBJ mode will always put unit into "pure BG" mode.

BG/OBJ mode can be used only with settings 0, 1, 8, or 9 of Detection Mode [D]. If settings other than these are programmed into the e<sup>2</sup>prom in error, the erroneous settings will be 'moved' to one of these legal numbers when the BG/OBJ mode is entered.

### 3.15.5 Data Locking & Drift Store

Data locking allows the sensor to store reference calibration and threshold settings, as well as BG/OBJ and OBJ mode settings. If Data Locking is off (or the e<sup>2</sup>prom is absent), the device will forget its prior settings when power is interrupted, including the fact that it might have been in a BG/OBJ or OBJ mode. BG/OBJ and OBJ modes require that fixed information be saved to operate, and so need to be manually restored after each powerup if Data Locking was not enabled.

Data locking operates seamlessly with BG, BG/OBJ, and OBJ modes; once Data Locking is specified via the e<sup>2</sup>prom setups

nothing else needs to be done. The unit will save all calibration data whenever BG or OBJ are evoked or whenever an automatic recalibration (due to a Max On-duration timeout, for example) occurs.

Drift Store mode makes the QT9701B periodically save to e<sup>2</sup>prom the drift compensated reference level, so that if the unit is unpowered it will remember its last known reference when next powered up. The Drift Store save operation can be specified to occur periodically, from one minute to 10 minutes of spacing. Note that e<sup>2</sup>proms have a limited cycle life; this may have an impact on selection of the e<sup>2</sup>prom update rate.

The Drift Store operation takes 5 milliseconds to execute and interrupts sensing, but does not occur at all if the reference level has not changed. Thus, even with this mode enabled, in OBJ mode or if Drift Rate is set to "off", no e<sup>2</sup>prom save will ever occur.

Setting to [F.1] allows Data Locking but prevents Drift Store from occurring on a timed basis.

Motion mode disables both Data Locking and timed Drift Store. Motion mode is a purely transient mode.

## 4 - UART OPERATION

There are two serial port data output options available on the QT9701B2: UART and SPI. Several variations of each can be selected such as baud rate and data type. Section 5 deals with SPI operation.

The UART serial modes exist primarily to transmit signal data to a destination such as a host controller. All data is output as 8 bits of binary.

Instead of signal data, the QT9701B2 can also be made to output a status byte, the detection integrator counter, or the internal reference level. The reference level is useful as an alternative representation of the signal, as it reflects the long-term average of

the signal level, and can be made to change very slowly via the adjustable drift compensation mechanism [8].

#### 4.1 HARDWARE AND DATA RATES

The UART employs standard NRZ coding with no or software handshaking depending on the selected mode of [G]. Buffering with an interface device such as a MAX232 is required for operation with standard RS232 ports. Direct connection to a host device, such as an MCU, is possible without buffering.

UART modes are specified by Setup [G] in Table 7-1. UART data has the following format:

**TABLE 4-2 - EVOKE CODE RESPONSES**

| EVOKED<br>(ASCII) | EVOKED<br>(HEX) | DATA TRANSMITTED                  |

|-------------------|-----------------|-----------------------------------|

| 0                 | 0x30            | Signal (0..255)                   |

| 1                 | 0x31            | Signal - Reference (0..255)       |

| 2                 | 0x32            | Reference (0..255)                |

| 3                 | 0x33            | Amplifier Offset (0..255)         |

| 4                 | 0x34            | Charge Cancellation (0..4)        |

| 5                 | 0x35            | Detect Integrator Counts (0..200) |

| 6                 | 0x36            | Any item selected by Setup [U]    |

| 7                 | 0x37            | Status bits - see Table 4-3       |

| 8                 | 0x38            | Error Code: See Section 4.5       |

**TABLE 4-3 - STATUS BYTE (H.7)**

See Section 4.3

| BITS | MEANING                                      |

|------|----------------------------------------------|

| 0    | 1 = negative detection                       |

| 1    | 1 = positive detection                       |

| 2    | 1 = unit is busy (in calibration or startup) |

| 3    | 1 = an error has occurred                    |

| 4    | 1 = BG input detected                        |

| 5    | 1 = OBJ input detected                       |

| 6, 7 | unused                                       |

**TABLE 4-4 - STATUS BYTE (U.8)**

See Section 5.2

| BITS | MEANING                                      |

|------|----------------------------------------------|

| 0, 1 | Error code, value range 0..3 (see Table 4-5) |

| 2    | 1 = negative detection                       |

| 3    | 1 = positive detection                       |

| 4    | 1 = OUT pin is active                        |

| 5    | 1 = unit is busy (in calibration or startup) |

| 6    | 1 = OBJ input detected                       |

| 7    | 1 = BG input detected                        |

**TABLE 4-5 - ERROR CODE (H.8)**

See Section 4.5

| VALUE | MEANING                             |

|-------|-------------------------------------|

| 0     | No error                            |

| 1     | Short circuit suspected             |

| 2     | Excess capacitive load              |

| 3     | Unstable readings, cannot calibrate |

**Baud rate:** 9600, 19.2K, 57.6K, or 115.2K

**Length:** 8 bits

**Stop Bits:** 1

**Parity:** None

In addition, a special 'slow mode' is available at 9600 baud, with transmissions spaced 100ms apart to allow use with slow host equipment [G.6].

#### 4.2 'NATIVE' VERBOSE SERIAL MODE

'Native' Verbose serial mode is specified by setting [G] to [G.5] or higher.

In this mode the device transmits data continuously. The data item sent from the UART is selected by Setup [H], Verbose Data.

Native Verbose mode is useful to send to the host a continuous data stream of one item, without the complexity of a bidirectional link. With this mode the selected data is transmitted on a continuous basis from the moment the unit powers up.

Verbose data is in the form of raw hex code. There are no headers or data blocks; data is merely a continuous stream of 8-bit hex code of the internal QProx data. Host receive protocol need not include anything for data synchronization; every character received will be a self-contained data point. No CR or LF codes are sent. Native Verbose mode begins immediately upon power up if setup [G] is set to [G.5] or higher.

#### 4.3 UART DATA IN VERBOSE MODE

In Verbose mode (either 'Native Verbose' mode, set by [G.5] and up) or 'Enhanced Verbose' mode (polled mode in which the letter 'v' has been sent to the 9701B2) the device will transmit back a continuous stream of data. In Native Verbose mode the data sent is that specified by [H]. These data types reflect that found in the E2SR board, thus maintaining compatibility, and can be summarized as follows (see also summary Table 4-2):

0. **Synth** outputs filtered (synthetic) data, at the end of all enabled filter stages. It is an unsigned 8-bit signal value.

1. **Synth - Ref** returns the difference between the filtered signal and the current reference. The data is 2's complement binary: If the signal dips below the reference level, the data becomes negative.

2. **Ref** returns the current signal reference level.

3. **Offset** returns the current DAC offset value being fed to the amplifier chain (Out\_A of the AD7303).

4. **Cancellation** returns the current charge cancellation value, from 0 to 4, representing the number of Cz capacitors being used to provide charge cancellation.

5. **DI** returns the current value of the Detect Integrator (see notes related to [B] in the QT9701B data sheet).

6. **From U** returns the value specified by the current setting of Select [U].

7. **Status** returns the current Status Byte according to Table 4-3. Note that the Status Byte of [U.8] is not the same.

8. **Err Code** returns the current error code (see Section 4.5).

In 'Enhanced Verbose' mode, any of the above items can be selected 'on the fly' by sending any one of ASCII characters '0' through '8' corresponding to one of the above data items. The resulting continuous datastream will persist until a differing character is sent to the 9701B2.

#### 4.4 POLLED UART MODE

Polled UART mode is specified by setting [G] to a setting between [G.1] to [G.4].

In this mode the device waits for an ASCII 'Evoke Code' from the host before sending data back. In this mode the device can also be put into an "Enhanced Verbose" mode temporarily. The data character sent back to the host is sent immediately after receipt of the Evoke Code. In Enhanced Verbose mode, the data is identical to regular Verbose mode, however the data stream can be altered 'on the fly' repeatedly to different parameters by sending new Evoke Codes in the range 0..8.

Polled mode allows Verbose mode too, plus a number of added features including remote Setups programming, forced calibration (including both BG and OBJ), and QT width changing on the fly. Polled mode also lets you examine the current Setups.

Table 4-1 shows the polled-mode ASCII command set. Evoke codes 0..8 return data according to Table 4-2. Error codes are described in Table 4-5.

#### 4.4.1 Programming Setups to New Values

The 9701B2 can have its Setups reprogrammed by a host device. This reprogramming mode is initiated by sending the lowercase character 's', which halts sensor operation and places the device into its programming mode; the device then receives program information as pairs of address and data codes. Any combination of the Setups during the course of an 's' session can be remotely programmed this way. There is no time limit during which this has to be performed, so long as the device is powered throughout. The sequence must terminate in the lowercase letter 'w' which writes the new Setups to e<sup>2</sup>prom and causes the device to sense again.

After the 'w' is sent to the device, and after the e<sup>2</sup>prom is successfully reprogrammed, the part will transmit back to the host an uppercase 'A' (hex 0x41) as a means of confirmation.

Following the transmission of the initiating 's', two-byte Setup Pairs of codes must be sent:

(1) A Select code, from hex 0x01 (1 decimal) to 0x17 (23 decimal) which corresponds to the keyboard control characters ^a through ^w (control-a ... control-w). 0x01 corresponds to Select Item 0; 0x17 corresponds to Select Item 'U'. See Table 4-6. This acts as an address into the e<sup>2</sup>prom locations.

(2) a Setting code from ascii '0' through '9' (hex 0x30 ... 0x39).

Each pair will alter the corresponding Select item to be the new Setting code, from 0 through 9.

As many pairs as required may be sent, even to overwrite prior pairs sent in the same session if a mistake is made. NO CR/LF CODES should inadvertently be sent after pair characters, or at any time. CR/LF codes correspond to codes 0x0d and 0x0a, which are valid Select codes during Remote Setups. (CR =

Carriage Return, LF = Line Feed; these are often accompanied automatically by many programs when data is sent, and as such should ALWAYS be suppressed in any interaction with the 9701B2).

A typical Remote Setup session might look like (unit already set to Polled Mode):

```

s ^a 9 ^i 1 ^d 5 ^s 1 ^a 8 w

<pause while unit recalibrates, then...> 1 v

```

Note that '^s' (control-'s', same as Select item 'J') is often intercepted by terminal programs and may not actually be sent from the host when so desired. There are usually ways around this. 'w' programs the e<sup>2</sup>prom and recalibrates the sensor before running (unless in Instant Start mode, in which case the sensor just runs again). Note also that the second '^a' pair (^a 8) overrides the first one; thus, Detect Threshold is set to '8' (6 counts of threshold level as shown in Table 7-1). After the recalibration, the unit is placed back into Enhanced Verbose mode and then sends a stream of data item '1' (signal - reference), following the 1 v sequence.

Table 4-6 shows the equivalence between the 's' Setups codes and Function Setup Table 7-1.

#### 4.4.2 Recalibration after Remote Setups

Remote Setup does not cause the QT9701B2 to recalibrate. This permits alteration of critical parameters without disturbing the sensing function, allowing dynamic alteration of basic operating parameters 'on the fly' without disturbing the data stream or calibration point.

If recalibration is desired after a Remote Setups sequence, for example after altering the device's Burst Length, any of the 'B', 'b', 'O', or 'o' commands can be sent afterwards to induce the desired recalibration.

#### 4.4.3 UART Evoke Data in Polled Mode

In polled mode the QT9701B2 will return any data item described for Verbose Mode in Section 4.2. The host device must send an evoke character from ASCII '0' through '8' to cause the device to respond with the corresponding data item (see also Table 4-2). Only one byte is returned after each evoke code, with no terminating CR or CR/LF.

#### 4.4.4 Last-Command Evoke

In polled mode, the host can interrogate the device to see if the last command sent was properly received using the character 'l' (Lower case L, ASCII code 0x6c). This is useful to obtain positive feedback that a command was received from the host.

In cases where a sequence of identical commands are issued, such as a string of 'b' commands, a nonfunctional dummy

**TABLE 4-6 - REMOTE SETUP CODES** (refer also to Table 7-1)

| Select | Description       | ASCII | Hex  | Select | Description               | ASCII | Hex  |

|--------|-------------------|-------|------|--------|---------------------------|-------|------|

| 0      | Detect Threshold  | ^a    | 0x01 | C      | Max On-Duration           | ^m    | 0x0D |

| 1      | Hysteresis        | ^b    | 0x02 | D      | Detection Mode            | ^n    | 0x0E |

| 2      | Reference Offset  | ^c    | 0x03 | E      | Calibration Control       | ^o    | 0x0F |

| 3      | <i>unused</i>     | ^d    | 0x04 | F      | Drift Store, Data Locking | ^p    | 0x10 |

| 4      | Width Pots        | ^e    | 0x05 | G      | Serial Modes              | ^q    | 0x11 |

| 5      | Burst Length      | ^f    | 0x06 | H      | Verbose Data              | ^r    | 0x12 |

| 6      | Burst Spacing     | ^g    | 0x07 | J      | Polarities                | ^s    | 0x13 |

| 7      | Randomize         | ^h    | 0x08 | L      | Output Stretch            | ^t    | 0x14 |

| 8      | Drift Rate        | ^i    | 0x09 | N      | <i>unused</i>             | ^u    | 0x15 |

| 9      | Median Filter     | ^j    | 0x0A | P      | <i>unused</i>             | ^v    | 0x16 |

| A      | Boxcar Average    | ^k    | 0x0B | U      | Mode / SPI Data Output    | ^w    | 0x17 |

| B      | Detect Integrator | ^l    | 0x0C |        |                           |       |      |

character can be sent to the device (such characters are also mirrored back to the host; See 4.4.7 below) to act as a separator, ensuring that the Last-Command byte returned in fact relates to the immediately prior byte sent to the device, and not a byte sent earlier in the sequence. Any ASCII code not shown in Table 4-1 will work as a separator.

#### 4.4.5 Remote Setup of Serial Mode / Baud Rate

Programming via Remote Setup of [G] is treated as a special

delay of at least 20ms but less than 90ms can be used to ensure that the second 'r' is properly received.

#### 4.4.7 Unknown Character Mirroring

If the QT9701B2 receives a character it does not recognize as valid, it will transmit that character back to the host immediately. Otherwise the device will be silent or will report back with the selected polled data item.

### 4.5 ERROR CODE REPORTING

The Error code reported by Evoke Code '8', or via [H.8] in either Verbose mode, is shown in Table 4-5. There are 4 possible values with the meanings shown.

Value = 1 indicates a very low signal, possibly due to a short circuit or a failed transfer mosfet or other circuit fault.

Value = 2 indicates excessive signal, more than can be calibrated against; it can also indicate that the mosfet is defective, for example due to heavy internal leakage.

Value = 3 usually indicates a very unstable signal due to substantial amounts of noise or violent signal swings.

These codes are reported after each calibration attempt, except Value 1 which can be detected at any time if a short circuit to ground occurs on the CHG pin. Note that the device will attempt to recalibrate in a manner dependent on Setup [E] if the error was found during a recalibration process; if a short was sensed during normal running, the device takes no further action. Refer to the QT9701B datasheet for further details on [E].

**FIGURE 5-1 - SPI OFFSET TIMING TO DAC A**

**FIGURE 5-2 - SPI DATA OUT, 8-BIT MODE**

case. To facilitate continued communication after a baud rate or serial mode change, the device will only begin the new serial setting after it is reset. This can be accomplished by unpowering the device, or by executing a Reset command 'r' (see below).

#### 4.4.6 Forced Reset Command

The QT9701B2 can be forcibly reset by sending it the ASCII letter 'r' (lower case R) twice in succession. After the first 'r' is received, the device will mirror back the letter 'r' over the serial port. After it has received the second 'r', it will transmit the letter 'R' (capital R). The two Forced Reset command characters must be sent within a 90ms timespan otherwise the command is canceled. Also, the host should receive the first returned 'r' back before sending the second 'r' to prevent the possibility of a comm overrun in the 9701B2. If full duplex communications are not possible, a 'safety'

## 5 SPI OPERATION

### 5.1 SPI CLOCKING AND FRAMING

The SPI port uses an 8 or 16 bit clocking scheme; data is clocked out on the falling edge of the SCK signal; the receiving device must be configured to accept data on the rising edge of SCK.. There is only one SPI port that is shared by both the AD7303 and the external world, but the port is framed by two different lines so as to separate the data streams for their respective destinations. The AD7303 contains two independent 8-bit DACs called DAC A and DAC B. DAC A is used to generate the offset voltage for the amplifier chain, and DAC B is used to create a processed 'synthetic' analog output.

The data rate is 5MHz (200ns clocking). SPI framing is provided by two sources:

#### 5.1.1 CS Framing to the Dual DAC

CS (pin 15) provides negative-going frame pulses for shifts of data to parts 'A' and 'B' of an AD7303 dual DAC. Two shifts of data occur during each burst cycle. In both cases the first byte sent is a control byte for the AD7303 used to direct the data byte to its internal part A or B DAC, and is of no particular value to the

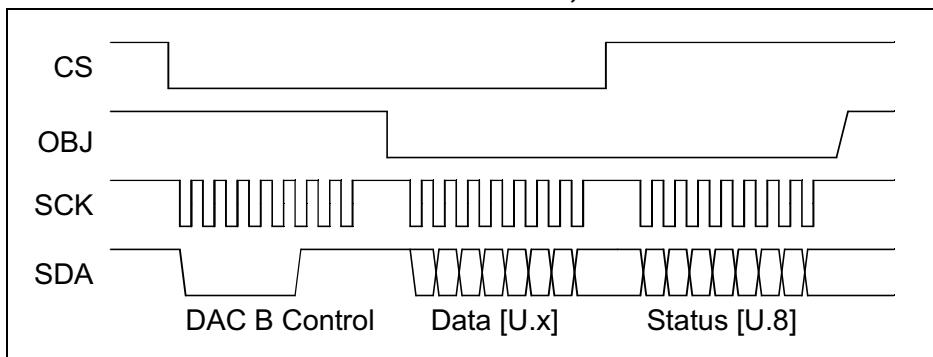

**FIGURE 5-3 - SPI DATA OUT, 16-BIT MODE**

external world. In both cases the second byte contains the actual data of interest.

Figure 5-1 shows timing waveforms of the data shifts to part A used to drive the offset node of the external amplifier chain; this transmission occurs just prior to each burst.

Figure 5-2 shows the timing waveforms of data shifts to part B of the AD7303; this is commonly used to supply an analog output which can be one of several different types, depending on Setup [U]. The 'B' transmission occurs just after all internal signal processing has completed, between bursts. The position of this shift will vary depending on the amount of signal processing being performed.

There can also be a third byte transmitted as part of the DAC B shift process if [P.1] is selected, but this third byte is not framed by CS and is thus always ignored by the AD7303 (Figure 5-3).

### 5.1.2 OBJ Framing to an External Device

OBJ (pin 6) frames SPI data to the external world, separate from the DAC framing provided by CS. It encompasses the second or second and third bytes sent as part of the DAC B send to the AD7303. An external receiver of data from the device will thus not receive the DAC control byte portion of the transmission but will receive the relevant data specified by [U.x]. Since the transmission is partly shared with DAC B it is not possible to send separate data to DAC B and an external device.

If [P.0] is selected (8-bit data mode), OBJ frames just the single 8-bit data element chosen by Setups [U.x] (Figure 5-2).

If [P.1] is selected (16-bit data mode, Figure 5-3), OBJ frames first the data element specified by [U.x] and also secondly a byte containing the Status bits described in Table 4-4. Note that only the last two are framed by OBJ; the AD7303 receives data framed by the CS line, namely only the first two bytes of the sequence.

The OBJ line must be pulled high with a resistor, e.g. 2.2K 5% to operate properly, and should not be loaded with external

capacitance to ensure a crisp risetime. The dual-use of OBJ does not interfere with the normal functioning of the OBJ input line, but an external contact closure from OBJ to ground may prevent a slave SPI port from receiving the correct data.

## 5.2 SPI DATA MODES [U]

Setup [U.x] specifies the type of data being output by the SPI port in Mode 2. All data returned is unsigned 8 bits, unless mode [P.1] is selected in which case 16 bits are transmitted, the last 8 of which are Status [U.8] (see Section 5.1 and Table 4-4).

**[U.1] Raw** outputs directly acquired, unfiltered data, regardless of any internal filtering that might be enabled.

**[U.2] Synth** outputs filtered (synthetic) data, at the end of all enabled filter stages.

**[U.3] +Synth** returns the positive difference between the current filtered signal and the current reference. If the signal dips below the reference level, the data is truncated to zero.

**[U.4] -Synth** returns the negative difference between the current filtered signal and the current reference. If the signal rises above the reference level, the data is truncated to zero. The value returned is the absolute value of the difference.

**[U.5] |Synth|** returns the absolute value of the difference between the current filtered signal and the current reference, whether above or below the reference level.

**[U.6] Reference** returns the current internal reference value. This may be of value as a form of ultra-slow filtered signal.

**[U.7] DI** returns the value of the Detection Integrator.

**[U.8] Status** returns a status byte composed of bits with meanings as shown in Table 4-4.

Serial SPI data is updated after each burst. Data is output after a burst and after the burst data is fully filtered (if any filtering is enabled).

**TABLE 7-1 - QT9701B2 SETUPS****BOLD BOXES DENOTE DEFAULT SETTINGS IF BLANK OR NO EEPROM FOUND**

| SELECT | DESCRIPTION                                 | 0              | 1                | 2          | 3             | 4                  | 5                 | 6          | 7          | 8          | 9          |

|--------|---------------------------------------------|----------------|------------------|------------|---------------|--------------------|-------------------|------------|------------|------------|------------|

| 0      | <b>Defect Threshold, counts</b>             | 62             | 40               | 32         | 25            | 19                 | 14                | 11         | 8*         | 6          | 4          |

| 1      | <b>Hysteresis, % of Threshold</b>           | 50             | <b>25*</b>       | 12.5       | 0             |                    |                   |            |            |            |            |

| 2      | <b>Reference Offset (hex / decimal)</b>     | 0x10 / 16      | 0x20 / 32        | 0x40 / 64  | 0x60 / 96     | <b>0x70 / 112*</b> | <b>0x80 / 128</b> | 0xA0 / 160 | 0xC0 / 192 | 0xE0 / 224 | 0xF0 / 240 |

| 3      | unused                                      |                |                  |            |               |                    |                   |            |            |            |            |

| 4      | <b>Pulse Width - ns</b>                     | 200            | 400              | 600        | 800           | <b>1,000*</b>      | 1,200             | 1,400      |            |            |            |

| 5      | <b>Burst Length, pulses</b>                 | 4              | 8                | 16         | 24            | 32                 | 40                | 48         | 56         | <b>64*</b> | ‡          |

| 6      | <b>Burst Spacing</b>                        | 200 $\mu$ s    | 500 $\mu$ s      | 1ms        | <b>2ms*</b>   | 5ms                | 10ms              | 20ms       | 50ms       | 100ms      | ‡          |

| 7      | <b>Randomize Bursts, %</b>                  | <b>off*</b>    | 12.5%            | 25%        | 50%           | ‡                  |                   |            |            |            |            |

| 8      | <b>Drift Rate, seconds/bit</b>              | off            | 100              | 50         | 20            | 10                 | <b>5</b>          | 2          | 1          | 0.5        | 0.2        |

| 9      | <b>Median Filter, length</b>                | off            | <b>5*</b>        | 9          |               |                    |                   |            |            |            |            |

| A      | <b>Boxcar Average, length</b>               | off            | 2                | 4          | 8             | 16                 | <b>32*</b>        | 64         | ‡          |            |            |

| B      | <b>Defect Integrator, counts</b>            | off            | 1                | 2          | 5             | <b>10*</b>         | 20                | 50         | 100        | 200        | ‡          |

| C      | <b>Max On-Duration, seconds</b>             | infinite       | 100              | 50         | <b>20*</b>    | 10                 | 5                 | 2          | 1          | 0.5        | 0.2        |

| D      | <b>Detection Mode</b>                       |                |                  |            |               |                    |                   |            |            |            |            |

| D.a    | Output on positive signals                  | <b>X*</b>      | X                | X          | X             | X                  | X                 |            |            |            |            |

| D.b    | Output on negative signals                  |                |                  |            |               | X                  | X                 | X          | X          |            |            |

| D.c    | Max On-Duration engages on +/- crossing     | <b>+</b> *     | +                | +/-        | +/-           | +/-                | +/-               | +/-        | -          |            |            |

| D.d    | Drift compensation during detect            |                | X                |            | X             |                    | X                 |            | X          |            | X          |

| E      | <b>Calibration control</b>                  |                |                  |            |               |                    |                   |            |            |            |            |

| E.a    | output error code if cal error              | off            | <b>on*</b>       | off        | on            |                    |                   |            |            |            |            |