## QS3244, QS32244

# High-speed CMOS QuickSwitch Buffers

QS3244 QS32244

## FEATURES/BENEFITS

- $5\Omega$  switches connect inputs to outputs

- Pin compatible to the 74F244, 74FCT244, and 74FCT244T

- Low power CMOS proprietary technology

- Zero ground bounce Available in 20-pin DIP, SOIC, and QSOP

## DESCRIPTION

The QS3244 and QS32244 provide a set of eight high-speed CMOS TTL-compatible bus switches in a pinout compatible with 74FCT244, 74F244, 74ALS/AS/LS244 8-bit drivers. The low on resistance (5Ω ohms) of the 3244 allows inputs to be connected outputs without adding propagation delay and without generating additional ground bounce noise. The two enable (nG) signals turn the switches on similar to the nG signals of the 74'244. The QS32244 device includes 25 ohm series termination resistors.

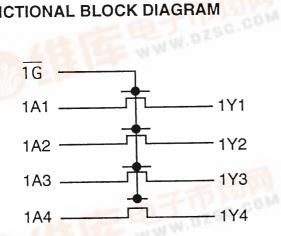

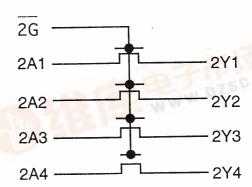

## FUNCTIONAL BLOCK DIAGRAM

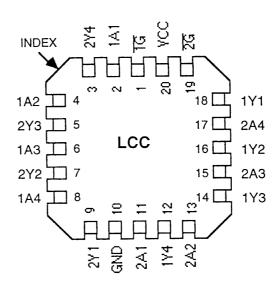

## **QS3244 PINOUT**

## PDIP, SOIC, QSOP

**ALL PINS TOP VIEW**

## 3244 PIN DESCRIPTION

| Name  | Description   |

|-------|---------------|

| 1G/2G | Output Enable |

| An    | Data I/O's    |

| Yn    | Data I/O's    |

#### 3244 FUNCTION TABLE

| 1G | 2G | 1A, 1Y I/Os  | 2A, 2Y I/Os  |

|----|----|--------------|--------------|

| Н  | Н  | Disconnected | Disconnected |

| L  | Н  | 1An=1Yn      | Disconnected |

| Н  | L  | Disconnected | 2An=2Yn      |

| L  | L  | 1An=1Yn      | 2An=2Yn      |

## **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage to Ground                   | -0.5V to +7.0V |

|--------------------------------------------|----------------|

| DC Switch Voltage V <sub>S</sub>           | -0.5V to +7.0V |

| DC Input Voltage VI                        | -0.5V to +7.0V |

| AC Input Voltage (for a pulse width 20 ns) | 3.0V           |

| DC Channel Current Max. current/pin        | 120 mA         |

| Maximum Power Dissipation                  | 0.5 watts      |

| T <sub>STG</sub> Storage Temperature       | -65° to +165°C |

## CAPACITANCE

$TA = 25 \,^{\circ}C$ ,  $f = 1 \, MHz$ , Vin = 0V,  $Vout = 0 \, V$

| Pins                 | sc  | SOIC QSC |     | OP P |     | DIP | Unit |

|----------------------|-----|----------|-----|------|-----|-----|------|

|                      | Тур | Max      | Тур | Max  | Тур | Max |      |

| Controls             | 3   |          | 3   |      | 4   |     |      |

| QuickSwitch Channels | 7   |          | 7   |      | 8   | l   |      |

Note: Capacitance is characterized but not tested

## DC ELECTRICAL CHARACTERISTICS OVER OPERATING RANGE

Commercial  $T_A = 0$ ° C to 70°C,  $Vcc = 5.0V \pm 5\%$  Military  $T_A = -55$ °C to 125° C,  $Vcc = 5.0V \pm 10\%$

| Symbol  | Parameter                 | Test Conditions                             |       |    | Тур | Max | Unit  |

|---------|---------------------------|---------------------------------------------|-------|----|-----|-----|-------|

| Vih     | Input HIGH Voltage        | Guaranteed Logic HIGH<br>for Control Inputs |       |    | -   | -   | Volts |

| Vil     | Input LOW Voltage         | Guaranteed Logic LOW<br>for Control Inputs  |       | -  | -   | 0.8 |       |

| I lin I | Input Leakage Current     | 0 ≤ Vin ≤ Vcc                               |       | -  | -   | 5   | μΑ    |

| l loz l | Off State Current (Hi-Z)  | 0 ≤ A, B ≤ Vcc                              |       | -  | -   | 5   |       |

| llosl   | Short Circuit Current (2) | A (B) = 0V, B (A) = Vcc                     |       |    | 300 |     | mA    |

| Ron     | Switch On Resistance      | Vcc = Min, Vin = 0.0 Volts                  | 3244  | -  | 5   | 7   | Ω     |

|         | (Note 3)                  | Ion = 30 mA                                 | 32244 | 20 | 28  | 40  |       |

|         |                           | Vcc = Min, Vin = 2.4 Volts   324   322      |       | -  | 10  | 15  |       |

|         |                           |                                             |       | 20 | 35  | 48  |       |

#### Notes:

- Typical values indicate V<sub>CC</sub>=5.0V and T<sub>A</sub>=25°C.

Not more than one output should be used to test this high power condition, and the duration is 1 second.

Measured by voltage drop between A and Y pin at indicated current through the switch. On resistance is determined by the lower of the voltages on the two pins.

- 4. During input/output leakage testing all pins are at a High or Low state, and the /OE control is High.

### POWER SUPPLY CHARACTERISTICS

| Symbol | Parameter                                 | Test Conditions (1)                                                       | Min | Тур | Max  | Unit       |

|--------|-------------------------------------------|---------------------------------------------------------------------------|-----|-----|------|------------|

| Icc    | Quiescent Power<br>Supply Current         | Vcc = MAX, $Vi = GND$ or $Vcc$ , $f = 0$                                  | -   | -   | 2.5  | mA         |

| ΔΙσσ   | Pwr Supply Current,<br>per Input High (2) | Vcc = MAX, Input = 3.4 V, f = 0 Per control input                         | -   | -   | 3.5  | mA         |

| Qccd   | Dynamic Pwr Supply<br>Current per MHz (3) | Vcc = MAX, A & B pins open,<br>Control input toggling<br>@ 50% duty cycle | -   | -   | 0.25 | mA/<br>MHz |

#### Notes:

- 1. For conditions shown as MIN or MAX use the appropriate values specified under DC specifications.

- 2. Per TTL driven input (Vi=3.4V, control inputs only). A and Y pins do not contribute to lcc.

- Guaranteed by design. This current applies to the control inputs only and represents the current required to switch internal capacitance at the specified frequency. The A and Y inputs generate no significant AC or DC currents as they transition.

## SWITCHING CHARACTERISTICS OVER OPERATING RANGE

Commercial  $T_A = 0^\circ$  C to 70°C,  $Vcc = 5.0V \pm 5\%$  Military  $T_A = -55^\circ$ C to 125° C,  $Vcc = 5.0V \pm 10\%$  Cload = 50 pF, Rload = 500 unless otherwise noted.

| Symbol       | Description                                            | Note  | Com |      | Mil |      | Unit |  |

|--------------|--------------------------------------------------------|-------|-----|------|-----|------|------|--|

|              |                                                        |       | Min | Max  | Min | Max  |      |  |

| t AY         | Data Propagation Delay<br>An to Yn                     | 1,2,3 |     | 0.25 |     | 0.25 | nS   |  |

| t GY         | Switc <u>h</u> T <u>ur</u> n On Delay<br>1G, 2G to Yn  | 1     | 0.5 | 5.6  | 0.5 | 6.6  | nS   |  |

| tPLZ<br>tPHZ | Switc <u>h</u> T <u>ur</u> n Off Delay<br>1G, 2G to Yn | 1,2   | 0.5 | 5.2  | 0.5 | 6.2  | nS   |  |

#### Notes:

- 1. See Test Circuit and Waveforms. Minimums guaranteed but not tested.

- 2. This parameter is guaranteed by design but not tested.

- 3. The bus switch contributes no propagation delay other than the RC delay of the on resistance of the switch and the load capacitance. The time constant for the switch alone is of the order of 0.25 ns for 50 pF load. Since this time constant is much smaller than the rise/fall times of typical driving signals, it adds very little propagation delay to the system. Propagation delay of the bus switch when used in a system is determined by the driving circuit on the driving side of the switch and its interaction with the load on the driven side.