### 5C060 16-MACROCELL CMOS PLD

- High-Performance LSI Semi-Custom Logic Alternative to Low-End Gate Arrays, TTL, and 74HC SSI and MSI Logic

- 16 Macrocells with Programmable I/O Architecture; up to 20 Inputs (4 Dedicated, 16 I/O) or 16 Outputs

- Programmable Output Registers can be Configured as D, T, SR, or JK Types

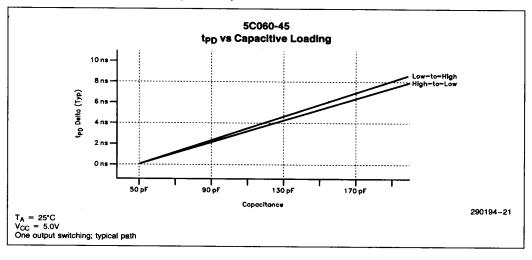

- t<sub>PD</sub> (max) 45 ns, 26.3 MHz Pipelined, 22.2 MHz w/Feedback

- Programmable Clock System with 2 Synchronous Clocks and Asynchronous Clocking Option on all Registers

- 8 P-Terms, Selectable SOP Invert, Clear and OE P-Terms for Each Macrocell

- Programmable Security Bit Allows Total Protection of Proprietary Designs

- CMOS EPROM Technology Based. UV Erasable (CerDIP) or OTP

- Progammable Low Power Option;

50 μA Typical Standby Current

- 100% Generically Tested Logic Array

- 100% Compatible with EP600

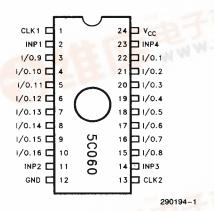

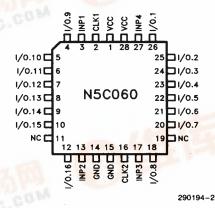

- Available in 24-Pin 300-mil CerDIP/PDIP and 28-Pin PLCC Packages

(See Packaging Specifications, Order Number 240800, Package Types D, P, and N)

Figure 1, 5C060 Pin Configurations

October 1955

Order Number: 290 194-005

PDC1.0ZSC.COM

The Intel 5C060 PLD (Programmable Logic Device) is a 16-macrocell, 24-pin, general purpose device. The device can be used to replace low-end gate arrays, multiple programmable logic arrays and LS TTL and 74HC (CMOS) SSI and MSI logic devices. The 5C060 can also be used as a direct, low-power

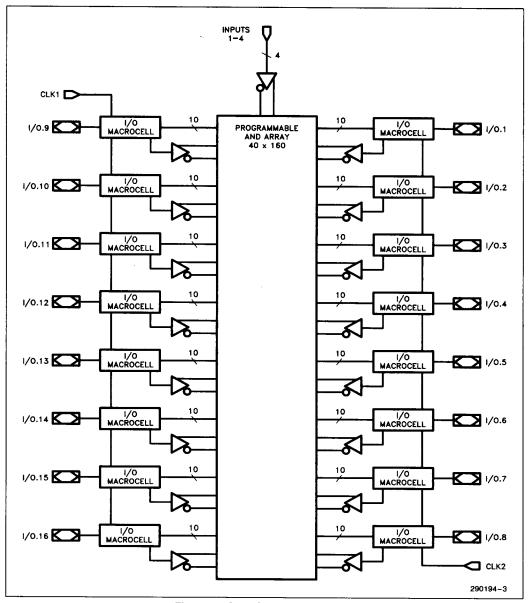

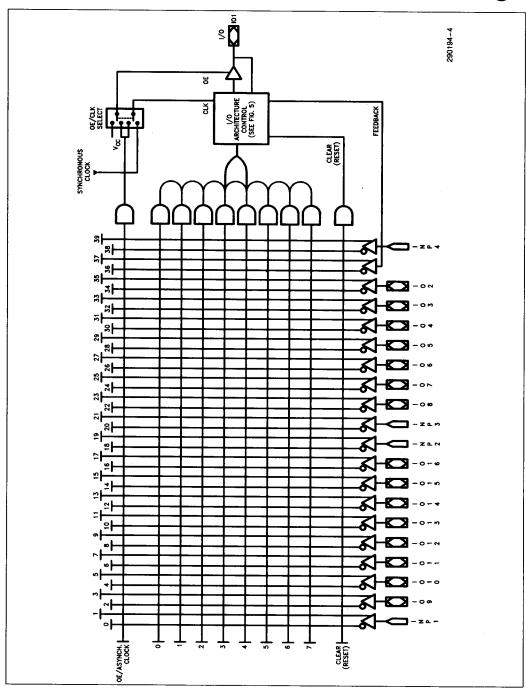

replacement for most, common 24-pin fuse-based programmable logic devices. With its revolutionary programmable I/O architecture, the device has advanced functional capabilities beyond that of typical programmable logic. Figure 2 shows the global architecture of the device.

Figure 2. 5C060 Global Architecture

# intطا

The 5C060 PLD uses CMOS EPROM (floating gate) cells as logic control elements instead of fuses. The CMOS EPROM technology reduces power consumption of PLDs to less than 20% of a comparable bipolar device without sacrificing speed performance. In addition, Intel's advanced CMOS II-E EPROM process technology enables greater logic densities to be achieved with superior speed and low-power performance over other comparable devices. Intel's ELPDs add the benefits of "zero" stand-by power not available on other programmable logic devices. EPROM technology allows these devices to be 100% factory tested by programming and erasing all the EPROM logic control elements.

The architecture of the 5C060 is based on the "Sum of Products" PLA (Programmable Logic Array) structure with a programmable AND array feeding into a fixed OR array. The device accommodates combinational and sequential logic functions. A proprietary programmable I/O architecture provides individual selection of either combinatorial or registered output and feedback signals all with selectable polarity.

A feature unique to the 5C060 is the ability to individually program the output registers as a D-, T-, SR-, or JK-type Flip-Flop without sacrificing the utilization of programmable AND logic. Additionally, each output register can be individually clocked from any of the

input or feedback paths available within the AND array. With these features, a wide variety of logic functions can be simultaneously implemented—all on the same device.

#### ARCHITECTURE DESCRIPTION

Externally, the 5C060 has 4 dedicated data input pins, 16 I/O pins which may be configured for input, output, or bidirectional operations, and 2 synchronous clock inputs. The 5C060 is contained in a 24-pin windowed package (0.3 inch wide) or 28-lead J-leaded chip carrier package, and contains 16 programmable registers.

The basic Macrocell architecture for the 5C060 is shown in Figure 3. The 5C060 has 16 of these Macrocells (one for each I/O pin). The Macrocell is organized in the familiar sum-of-products structure with a programmable AND array attached to a fixed OR term. The inputs to the programmable AND array originate from the true and complement signals from each of the dedicated input pins and each of the I/O control blocks. The 40-input AND array of the 5C060 feeds 160 AND gates (product terms) which are distributed among the 16 available Macrocells within that device.

Figure 3. 5C060 Macrocell Architecture

The Macrocells contain ten product terms total. Eight of the ten product terms (AND gates) are dedicated for logic implementation. One product term on each Macrocell is used for RESET control to the output register associated with the Macrocell. The final product term is used for OUTPUT ENABLE/Asynchronous Clock implementation.

Within the AND array, there is an EPROM connection at every intersection of an input signal (true and complement) and a product term to a given Macrocell. Before programming an erased device, every EPROM connection is made at every intersection. But during the programming process, these connections are opened so that only the desired connections remain. Therefore, the true or complement of any input signal can be connected to any product term. If both the true and complement connections of any signal are left intact, a logical false results on the output of the AND gate. However, if both the true and complement connections are open, then a logic "don't care" results on the AND gate. Lastly, if all the inputs of a product term are programmed open, then a logical true results on the output of the AND gate.

The 5C060 has two dedicated clock inputs to provide synchronous clock signals to the internal registers. Each of the clock signals controls half the total registers within the given device. For example, CLK1 provides synchronous clocking to the registers in Macrocells in the left half of the array while CLK2 controls the registers associated with Macrocells in the right half of the array. The advanced I/O architecture allows for any number of the registers to be synchronously clocked (from none to all). Both of the dedicated clock inputs latch the data into a given register when triggered on a positive edge.

# MACROCELL ARCHITECTURE SELECTION

The 5C060 architecture provides each Macrocell with over 50 different possible I/O register configurations. Each I/O pin can be configured for combinatorial or registered output (true or complement) with feedback. In addition, four different types of output registers can be implemented into every I/O pin without any additional logic requirements. The feedback mechanism for each register back into the AND array can be programmed to provide for either registered feedback from the Macrocell or input feedback (treating the pin as an input). Another advantage of the advanced I/O capability of the 5C060 is the ability to individually clock each internal register from asynchronous clock signals.

#### Output Enable (OE)/Clock Selection

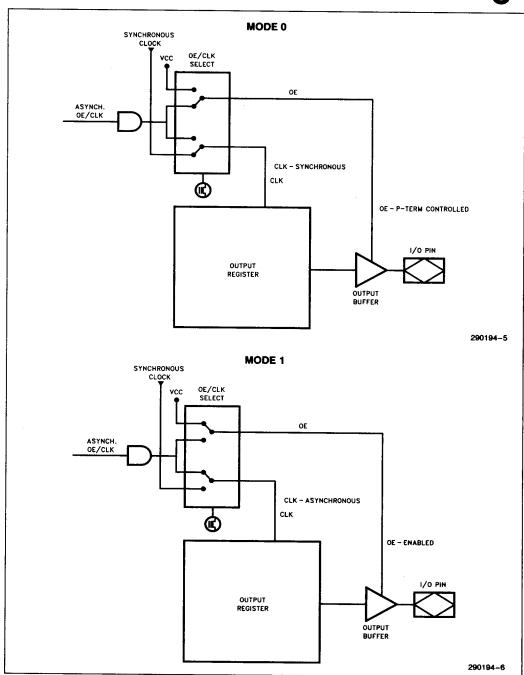

Two modes of operation are provided by the OE/CLK Select Multiplexer as a part of each Macrocell. One mode provides for three-state buffering of outputs while in the other mode, the outputs are always enabled. The operation of the OE/CLK Select Multiplexer sets the mode within a given Macrocell. Therefore, the output mode can be selected individually on every output. Figure 4 illustrates the two modes of OE/CLK operation.

#### MODE 0: THREE-STATE BUFFERING

In Mode 0, the three-state output buffer is controlled by a single product term originating from the AND array. The output is enabled when the product term is a logical true. Conversely, the output appears as high impedance when the product term is a logical false as shown in Table 1. In Mode 0, the Macrocell Flip-Flop is connected to its associated synchronous clock (either CLK1 or CLK2 depending upon the Macrocell's location within the device). Thus, the Macrocell Flip-Flop may be clocked by its respective synchronous clock but its output will not become valid until the output is enabled.

**Table 1. Mode 0 Output Selection**

| Product Term | Output Buffer |

|--------------|---------------|

| FALSE        | Three-State   |

| TRUE         | Enabled       |

#### **MODE 1: OUTPUT BUFFER ENABLED**

In Mode 1, the Output Buffer is always enabled. In addition, the Macrocell Flip-Flop is connected to the AND array. The Macrocell Flip-Flop may now be triggered from an asynchronous clock signal generated by the AND array logic to the OE/CLK multiplexable term. Mode 1 allows the Macrocell Flip-Flops to be individually clocked from any of the available signals in the AND array. Since both true and complement values appear in the AND array, the Flip-Flop may be clocked by any positive- or negative-going signals at any input pin. Gated clock structures can be created since the Flip-Flop clock is created by a product term.

#### **Invert Select EPROM Bit**

The Invert Select EPROM bit is used to invert the product term input into the register. This applies to all inputs including double inputs on the JK and SR registers.

Figure 4. Output Enable/Clock Configuration

# intel.

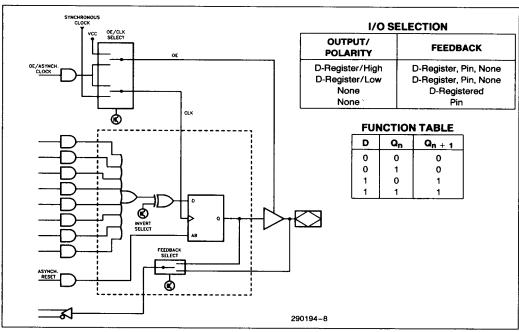

#### REGISTER SELECTION

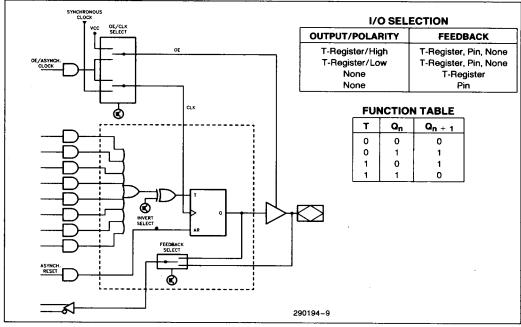

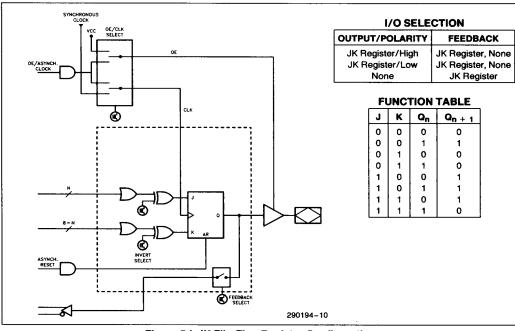

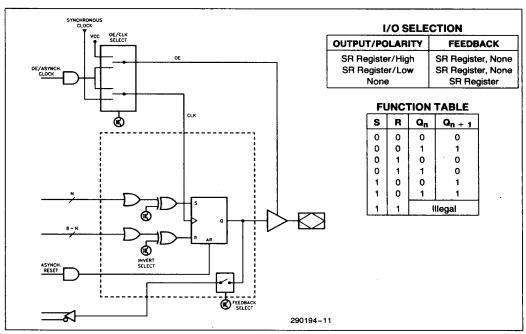

The advanced I/O architecture of the 5C060 allows four different register types along with combinatorial output as illustrated in Figure 5a. The register types include a T, D, JK, or SR Flip-Flop and each Macrocell I/O structure may be independently configured. In addition, all registers have an individual asynchronous RESET control from a dedicated product term derived in the AND array. When this dedicated product term is a logical one, the Macrocell register is immediately cleared to a logical zero independent of the register clock. The RESET function occurs automatically on power-up.

#### **Output Register Configuration**

The four different register types shown in Figure 5b-5e are described below.

D- or T-type Flip-Flops

When either a D- or T-type Flip-Flop is configured as part of the I/O structure, all eight of the product terms into the Macrocell are ORed together and fed into the register input.

JK or SR Registers

When either a JK or SR register is configured, the eight product terms are shared among two OR gates (one for the J or S input and the other for the K or R input). The allocation for these product terms for each of the register inputs is optimized by the PLDshell Plus software.

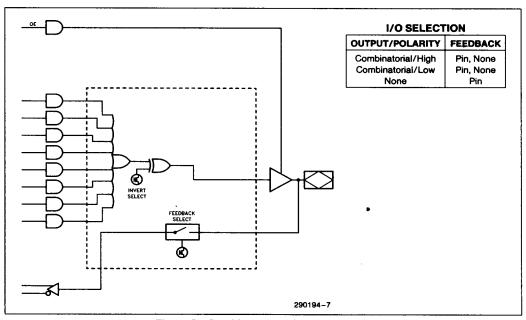

#### OUTPUT/FEEDBACK

The Output Select Multiplexer allows for either registered, combinatorial or no output.

The Feedback Select Multiplexer EPROM bit enables registered, I/O (using the pin for bidirectional input or just input), or no feedback to the AND array.

The Feedback Select is also important for building product terms with more than 8 products. The 8-product product term of a Macrocell can be fed back into the AND array and combined with still more signals to create a much larger product term (of more than 8-inputs). In addition, if the feedback product term is not to be output, then the PLDshell Plus software will reserve the associated Macrocell pin and indicate it in the REPORT file. A reserved pin should be left floating (no connect) when assembled onto a circuit board.

Any I/O pin may be configured as a dedicated input by selecting no output and pin feedback through the appropriate multiplexers.

Figure 5a. Combinatorial I/O Configuration

Figure 5b. D-Type (T-type) Flip-Flop Register Configuration

Figure 5c. Toggle T-Type Flip-Flop Register Configuration

Figure 5d. JK Flip-Flop Register Configuration

Figure 5e. SR Flip-Flop Register Configuration

#### **Erased-State Configuration**

Prior to programming or after erasing, the I/O structure is configured for combinatorial active low output with input (pin) feedback.

#### **ERASURE CHARACTERISTICS**

Erasure characteristics of the device are such that erasure begins to occur upon exposure to light with wavelengths shorter than approximately 4000Å. It should be noted that sunlight and certain types of flourescent lamps have wavelengths in the 3000Å–4000Å. Data shows that constant exposure to room level flourescent lighting could erase the typical device in approximately three years, while it would take approximately one week to cause erasure when exposed to direct sunlight. If the 5C060 is to be exposed to these types of lighting conditions for extended periods of time, conductive opaque labels should be placed over the device window to prevent unintentional erasure.

The recommended erasure procedure for the 5C060 is exposure to shortwave ultraviolet light with a wavelength of 2537Å. The integrated dose (i.e., UV intensity  $\times$  exposure time) for erasure should be a minimum of fifteen (15) Wsec/cm². The erasure time with this dosage is approximately 15 to 20 minutes using an ultraviolet lamp with a 12,000  $\mu\text{W/cm}^2$  power rating. The 5C060 should be placed within one inch of the lamp tubes during erasure. The maximum integrated dose the 5C060 can be exposed to without damage is 7258 Wsec/cm² (1 week at 12,000  $\mu\text{W/cm}^2$ ). Exposure to high intensity UV light for longer periods may cause permanent damage to the device.

#### PROGRAMMING CHARACTERISTICS

Initially, and after erasure, all the EPROM control bits of the 5C060 are connected (in the "1" state). Each of the connected control bits are selectively disconnected by programming the EPROM cells into their "0" state. Programming voltage and waveform specifications are available by request from Intel to support programming of the 5C060.

### **Intelligent Programming Algorithm**

The 5C060 supports the Intelligent Programming Algorithm which rapidly programs Intel ELPDs using an efficient and reliable method. The Intelligent Programming Algorithm is particularly suited to the production programming environment. This method ensures reliability as the incremental program margin of each bit is continually monitored to determine when the bit has been successfully programmed.

#### **FUNCTIONAL TESTING**

Since the logical operation of the 5C060 is controlled by EPROM elements, the device is completely testable. Each programmable EPROM bit controlling the internal logic is tested using application-independent test program patterns. After testing, the devices are erased before shipment to customers. No post-programming tests of the EPROM array are required.

The testability and reliability of EPROM-based programmable logic devices is an important feature over similar devices based on fuse technology. Fuse-based programmable logic devices require a user to perform post-programming tests to insure proper programming. These tests must be done at the device level because of the cummulative error effect. For example, a board containing ten devices each possessing a 2% device fallout translates into an 18% fallout at the board level (it should be noted that programming fallout of fuse-based programmable logic devices is typically 2% or higher).

#### **DESIGN RECOMMENDATIONS**

For proper operation, it is recommended that all input and output pins be constrained to the voltage range GND <  $(V_{IN} \text{ or } V_{OUT})$  <  $V_{CC}$ . Unused inputs and I/Os should be tied to  $V_{CC}$  or GND to minimize device power consumption. Reserved pins (as indicated in the logic compiler REPORT file) should be left floating (no connect) so that the pin can attain the appropriate logic level. A power supply decoupling capacitor of at least 0.2  $\mu$ F must be connected directly between  $V_{CC}$  and GND pins of the device.

As with all CMOS devices, ESD handling procedures should be used with the 5C060 to prevent damage to the device during programming, assembly, and test.

#### **DESIGN SECURITY**

A single EPROM bit provides a programmable design security feature that controls the access to the data programmed into the device. If this bit is set, a proprietary design within the device cannot be copied. This EPROM security bit enables a higher degree of design security than fused-based devices

since programmed data within EPROM cells is invisible even to microscopic evaluation. The EPROM security bit, along with all the other EPROM control bits, will be reset by erasing the device.

#### **AUTOMATIC STAND-BY MODE**

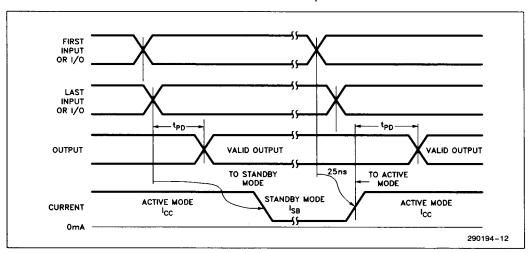

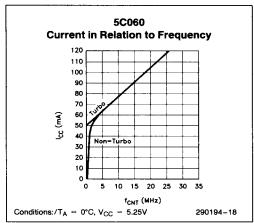

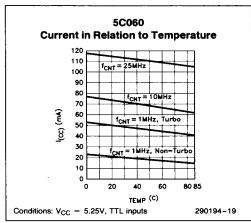

The 5C060 contains a programmable bit, the Turbo Bit, that optimizes operation for speed or for power savings. When the Turbo Bit is programmed (TURBO = ON), the device is optimized for maximum speed. When the Turbo Bit is not programmed (TURBO = OFF), the device is optimized for power savings by entering standby mode during periods of inactivity.

Figure 6 shows the device entering standby mode approximately 100 ns after the last input transition. When the next input transition is detected, the device returns to active mode. Wakeup time adds an additional 25 ns to the propagation delay through the device as measured from the first input. No delay will occur if an output is dependent on more than one input and the last of the inputs changes after the device has returned to active mode.

After erasure, the Turbo Bit is unprogrammed (OFF); automatic standby mode is enabled. When the Turbo Bit is programmed (ON), the device never enters standby mode.

#### LATCH-UP IMMUNITY

All of the input, I/O, and clock pins of the 5C060 have been designed to resist latch-up which is inherent in inferior CMOS structures. The 5C060 is designed with Intel's proprietary CMOS II-E EPROM process. Thus, each of the pins will not experience latch-up with currents up to  $\pm\,100$  mA and voltages ranging from  $-\,1V$  to (VCC  $+\,1V$ ). Furthermore, the programming pin is designed to resist latch-up to the 13.5V maximum device limit.

#### SOFTWARE SUPPORT

Full logic compilation and functional simulation for the 5C060 is supported by PLDshell Plus software.

PLDshell Plus design software is Intel's user-friendly design tool for µPLD design. PLDshell Plus allows users to incorporate their preferred text editor, programming software, and additional design tools into an easy-to-use, menued design environment that includes Intel's PLDasm logic compiler and simulation software along with disassembly, conversion, and translation utilities. The PLDasm compiler and simulator software accepts industry-standard PDS source files that express designs as Boolean equations, truth tables, or state machines. On-line help, data sheet briefs, technical notes, and error message information, along with waveform viewing/ printing capability make the design task as easy as possible. PLDshell Plus software is available from Intel Literature channels or from your local Intel sales representative.

Figure 6. 5C060 Standby and Active Mode Transitions

Tools that support schematic capture and timing simulation for the 5C060 are available. Please refer to the "Development Tools" section of the Programmable Logic Handbook.

The 5C060 is also supported by third-party logic compilers such as ABEL\*, CUPL\*, PLDesigner\*, Log/IC\*, etc. Programming support is provided by third-party programmer companies such as Data I/O, Logical Devices, STAG, etc. Please refer to the "Third-Party Support" lists in the *Programmable Logic* handbook for complete information and vendor contacts.

#### ORDERING INFORMATION

| t <sub>PD</sub><br>(ns) | t <sub>CO</sub><br>(ns) | f <sub>MAX</sub><br>(MHz) | Order<br>Code | Package | Operating<br>Range |

|-------------------------|-------------------------|---------------------------|---------------|---------|--------------------|

| 45                      | 22                      | 26                        | D5C060-45     | CERDIP  | Commercial         |

|                         |                         |                           | P5C060-45     | PDIP    |                    |

|                         |                         |                           | N5C060-45     | PLCC    |                    |

| 55                      | 25                      | 23                        | D5C060-55     | CERDIP  | Commercial         |

|                         |                         |                           | P5C060-55     | PDIP    |                    |

|                         |                         |                           | N5C060-55     | PLCC    | ٠                  |

| 45                      | 22                      | 26                        | TD5C060-45    | CERDIP  | Industrial         |

| 45                      | 22                      | 26                        | TN5C060-45    | PLCC    | Industrial         |

<sup>\*</sup>Abel is a trademark of Data I/O, Corp. CUPL is a trademark of Logical Devices, Inc. PLDesigner is a trademark of MINC, Inc. Log/IC is a trademark of ISDATA, Inc.

#### **ABSOLUTE MAXIMUM RATINGS\***

| Symbol           | Parameter                     | Min  | Max                  | Units |

|------------------|-------------------------------|------|----------------------|-------|

| Vcc              | Supply Voltage <sup>(1)</sup> | -2.0 | 7.0                  | ٧     |

| V <sub>PP</sub>  |                               |      | 13.5                 | ٧     |

| VI               | DC Input Voltage(1)(2)        | -0.5 | V <sub>CC</sub> +0.5 | ٧     |

| t <sub>stg</sub> | Storage Temperature           | -65  | + 150                | ů     |

| t <sub>emb</sub> | Ambient Temperature(3)        | -10  | + 85                 | °C    |

NOTICE: This is a production data sheet. The specifications are subject to change without notice.

\*WARNING: Stressing the device beyond the "Absolute Maximum Ratings" may cause permanent damage. These are stress ratings only. Operation beyond the "Operating Conditions" is not recommended and extended exposure beyond the "Operating Conditions" may affect device reliability.

#### NOTES:

1. Voltages with respect to ground.

- 2. Minimum DC input is -0.5V. During transitions, the inputs may undershoot to -2.0V or overshoot to 7.0V for periods less than 20 ns under no load conditions.

- 3. Under bias. Extended temperature versions are also available.

#### RECOMMENDED OPERATING CONDITIONS

| Symbol             | Parameter             | Min  | Max             | Unit       |

|--------------------|-----------------------|------|-----------------|------------|

| V <sub>CC</sub>    | Supply Voltage        | 4.75 | 5.25            | . <b>V</b> |

| VIN                | Input Voltage         | 0    | V <sub>CC</sub> | ٧          |

| V <sub>O</sub>     | Output Voltage        | 0    | V <sub>CC</sub> | V          |

| TA                 | Operating Temperature | 0    | + 70            | °C         |

| t <sub>R</sub> (4) | Input Rise Time       |      | 500             | ns         |

| t <sub>F</sub> (4) | Input Fall Time       |      | 500             | ns         |

#### NOTE:

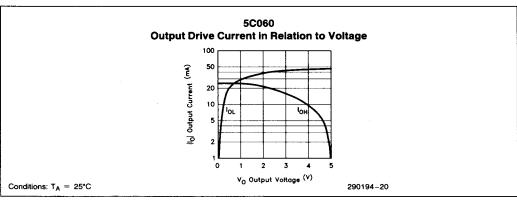

### **D.C. CHARACTERISTICS** $T_A = 0$ °C to 70°C, $V_{CC} = 5.0V \pm 5$ %

| Symbol                         | Parameter                    | Conditions                                                       | Min  | Тур | Max            | Unit |

|--------------------------------|------------------------------|------------------------------------------------------------------|------|-----|----------------|------|

| V <sub>IH</sub> (5)            | HIGH Level Input Voltage     |                                                                  | 2.0  |     | $V_{CC} + 0.3$ | ٧    |

| V <sub>IL</sub> (5)            | LOW Level input Voltage      |                                                                  | -0.3 |     | 0.8            | ٧    |

| V <sub>OH</sub> (6)            | HIGH Level Output Voltage    | $I_{O} = -4.0$ mA DC, $V_{CC} = Min.$                            | 2.4  |     |                | V    |

| VOL                            | LOW Level Output Voltage     | $I_O = 4.0$ mA DC, $V_{CC} = Min$ .                              |      |     | 0.45           | ٧    |

| l <sub>l</sub>                 | Input Leakage Current        | V <sub>CC</sub> = Max., GND < V <sub>IN</sub> < V <sub>CC</sub>  |      |     | ±10.0          | μΑ   |

| loz                            | Output Leakage Current       | V <sub>CC</sub> = Max., GND < V <sub>OUT</sub> < V <sub>CC</sub> |      |     | ± 10.0         | μΑ   |

| I <sub>SC</sub> <sup>(7)</sup> | Output Short Circuit Current | $V_{CC} = Max., V_{OUT} = 0.5V$                                  |      | 20  | 30             | mA   |

| I <sub>SB</sub> (8)            | Standby Current (Standby)    | $V_{CC} = Max., V_{IN} = V_{CC} \text{ or GND}$                  |      | 50  | 100            | μΑ   |

<sup>4.</sup> t<sub>R</sub>, t<sub>F</sub> for CLK is 250 ns max.

# **D.C. CHARACTERISTICS** $T_A = 0^{\circ}C$ to $70^{\circ}C$ , $V_{CC} = 5.0V \pm 5\%$ (Continued)

| Symbol | Parameter                                                                                                                 | Con | Min                             | Тур | Max | Unit |    |

|--------|---------------------------------------------------------------------------------------------------------------------------|-----|---------------------------------|-----|-----|------|----|

| lcc    | Power Supply Current<br>(Active) (Turbo Bit Off)<br>Device Prog. as 16-Bit Ctr.<br>(See I <sub>CC</sub> vs. Freq. Graph.) |     | No Load,<br>Input Freq. = 1 MHz |     | 10  | 15   | mA |

#### NOTES:

- 5. Absolute values with respect to device GND; all over and undershoots due to system or tester noise are included.

- 6.  $I_O$  at CMOS levels (3.84V) = -2 mA.

- 7. Not more than 1 output should be tested at a time. Duration of that test must not exceed 1 second.

- 8. With Turbo Bit Off, device automatically enters standby mode approximately 100 ns after last input transition.

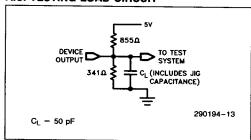

#### A.C. TESTING LOAD CIRCUIT

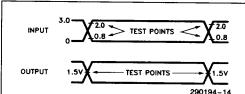

#### A.C. TESTING INPUT, OUTPUT WAVEFORM

A.C. Testing: Inputs are Driven at 3.0V for a Logic "1" and 0V for a Logic "0". Timing Measurements are made at 2.0V for a Logic "1" and 0.8V for a Logic "0" on inputs. Outputs are measured at a 1.5V point. Device input rise and fall times < 6 ns.

#### CAPACITANCE

| Symbol           | Parameter             | Conditions                         | Min | Тур | Max | Unit |

|------------------|-----------------------|------------------------------------|-----|-----|-----|------|

| C <sub>IN</sub>  | Input Capacitance     | V <sub>IN</sub> = 0V, f = 1.0 MHz  |     |     | 20  | pF   |

| C <sub>OUT</sub> | Output Capacitance    | V <sub>OUT</sub> = 0V, f = 1.0 MHz |     |     | 20  | ρF   |

| C <sub>CLK</sub> | Clock Pin Capacitance | V <sub>IN</sub> = 0V, f = 1.0 MHz  |     |     | 20  | pF   |

| C <sub>VPP</sub> | V <sub>PP</sub> Pin   | CLK2 on 5C060, f = 1.0 MHz         |     |     | 50  | ρF   |

# A.C. CHARACTERISTICS $T_A = 0^{\circ}C$ to $70^{\circ}C$ , $V_{CC} = 5V \pm 5\%$ , Turbo Bit On(9)

| Symbol                |               |                |                     |     | Dev | vice              |     |     |                           |      |

|-----------------------|---------------|----------------|---------------------|-----|-----|-------------------|-----|-----|---------------------------|------|

|                       | From          | То             | 5C060-45<br>EP600-3 |     |     | 5C060-55<br>EP600 |     |     | Non-(11)<br>Turbo<br>Mode | Unit |

|                       |               |                | Min                 | Тур | Max | Min               | Тур | Max | Mode                      |      |

| t <sub>PD1</sub>      | Input         | Comb. Output   |                     |     | 43  |                   |     | 53  | + 25                      | ns   |

| t <sub>PD2</sub>      | 1/0           | Comb. Output   |                     |     | 45  |                   |     | 55  | + 25                      | ns   |

| t <sub>PZX</sub> (10) | I or I/O      | Output Enable  |                     |     | 45  |                   |     | 55  | + 25                      | ns   |

| t <sub>PXZ</sub> (10) | For I/O       | Output Disable |                     |     | 45  |                   |     | 55  | + 25                      | ns   |

| tCLR                  | Asynch. Reset | Q Reset        |                     |     | 45  |                   |     | 55  | + 25                      | ns   |

Typical Values are at T<sub>A</sub> = 25°C, V<sub>CC</sub> = 5V, Active Mode.

10. tpzx and tpxz are measured at  $\pm 0.5 \text{V}$  from steady state voltage as driven by spec. output load. tpxz is measured with  $C_L = 5 \text{ pF}$ .

11. If device is operated with Turbo Bit Off (Non-Turbo Mode), and the device has been inactive for approx. 100 ns, increase time by amount shown.

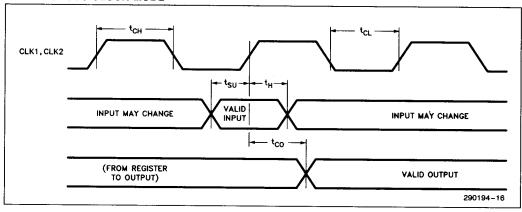

### SYNCHRONOUS CLOCK MODE A.C. CHARACTERISTIC

$T_A = 0$ °C to 70°C,  $V_{CC} = 5.0V \pm 5$ %, Turbo Bit On(9)

|                  | •                                                              | Device              |     |      |                   |     |      |                           |      |

|------------------|----------------------------------------------------------------|---------------------|-----|------|-------------------|-----|------|---------------------------|------|

| Symbol           | Parameter                                                      | 5C060-45<br>EP600-3 |     |      | 5C060-55<br>EP600 |     |      | Non-(11)<br>Turbo<br>Mode | Unit |

|                  |                                                                | Min                 | Тур | Max  | Min               | Тур | Max  | MOGE                      |      |

| f <sub>MAX</sub> | Max. Frequency (Pipelined) (1/t <sub>SU</sub> —No Feedback)    |                     |     | 26.3 |                   |     | 23.3 |                           | MHz  |

| f <sub>CNT</sub> | Max. Count Frequency (1/t <sub>CNT</sub> —With Feedback)       |                     |     | 22.2 |                   |     | 18.2 |                           | MHz  |

| t <sub>SU1</sub> | Input Setup Time to CLK                                        | 36                  |     |      | 41                |     |      | + 25                      | ns   |

| t <sub>SU2</sub> | I/O Setup Time to CLK                                          | 38                  |     |      | 43                |     |      | + 25                      | ns   |

| t <sub>H</sub>   | I or I/O Hold after CLK High                                   | 0                   |     |      | 0                 |     |      |                           | ns   |

| tco              | CLK High to Output Valid                                       |                     |     | 22   |                   |     | 25   |                           | ns   |

| <sup>†</sup> CNT | Register Output Feedback<br>to Register Input—Internal<br>Path | 45                  |     |      | 55                |     |      | + 25                      | ns   |

| t <sub>CH</sub>  | CLK High Time                                                  | 17.5                |     |      | 21.5              |     |      |                           | ns   |

| t <sub>CL</sub>  | CLK Low Time                                                   | 17.5                |     |      | 21.5              |     |      |                           | ns   |

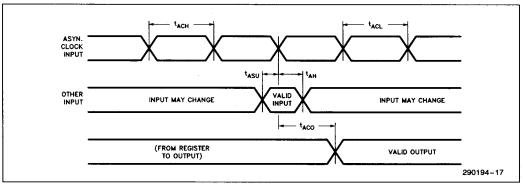

#### ASYNCHRONOUS CLOCK MODE A.C. CHARACTERISTICS

$T_A = 0$ °C to 70°C,  $V_{CC} = 5.0V \pm 5$ %, Turbo Bit On(8)

| Symbol            | Device                                                         |                     |     |      |                   |     |      |                           |      |

|-------------------|----------------------------------------------------------------|---------------------|-----|------|-------------------|-----|------|---------------------------|------|

|                   | Parameter                                                      | 5C060-45<br>EP600-3 |     |      | 5C060-55<br>EP600 |     |      | Non-(11)<br>Turbo<br>Mode | Unit |

|                   |                                                                | Min                 | Тур | Max  | Min               | Тур | Max  | Mode                      |      |

| f <sub>ACNT</sub> | Max. Count Frequency<br>(1/t <sub>ACNT</sub> —With Feedback)   |                     |     | 22.2 |                   |     | 18.2 |                           | MHz  |

| t <sub>ASU1</sub> | Input Setup Time to<br>Asynch. Clock                           | 10                  |     |      | 10                |     |      | + 25                      | ns   |

| t <sub>ASU2</sub> | I/O Setup Time to<br>Asynch. Clock                             | 12                  |     |      | 12                |     |      | + 25                      | ns   |

| t <sub>AH</sub>   | Input or I/O Hold After<br>Asynch. Clock                       | 15                  |     |      | 15                |     | ·    |                           | ns   |

| t <sub>ACO</sub>  | Asynch. CLK to Output Valid                                    |                     |     | 50   |                   |     | 58   | + 25                      | ns   |

| <sup>t</sup> ACNT | Register Output Feedback<br>to Register Input—Internal<br>Path | 45                  |     |      | 55                |     |      | + 25                      | ns   |

| t <sub>ACH</sub>  | Asynch. CLK High Time                                          | 17.5                |     |      | 21.5              |     |      | + 25                      | ns   |

| t <sub>ACL</sub>  | Asynch. CLK Low Time                                           | 17.5                |     |      | 21.5              |     |      | + 25                      | ns   |

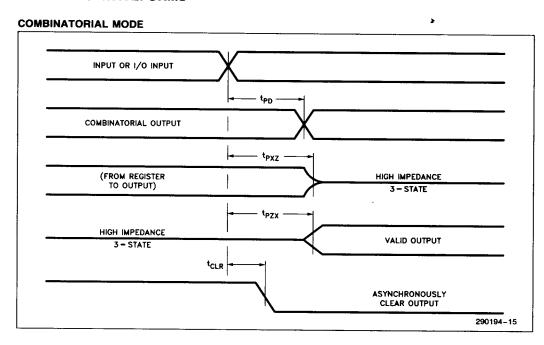

#### **SWITCHING WAVEFORMS**

#### SYNCHRONOUS CLOCK MODE

### **SWITCHING WAVEFORMS** (Continued)

#### **ASYNCHRONOUS CLOCK MODE**

# **SWITCHING WAVEFORMS (Continued)**