# QUALCOMM

# Q1650

# k=7 MULTI-CODE RATE VITERBI DECODER

2.5, 10, 25 Mbps Data Rates

Technical Data Sheet

# Other QUALCOMM VLSI Products

- Viterbi Decoders 256 Kbps to 25 Mbps Maximum Data Rates

- Pragmatic Trellis Modulation Codecs

- Direct Digital Synthesizers (DDS)

- 1.6 GHz Phase Locked Loop Frequency Synthesizers

- Low Data Rate Vocoders

- DDS and PLL Evaluation Boards

- VCOs

QUALCOMM Incorporated 10555 Sorrento Valley Road San Diego, CA 92121-1617 USA

Copyright @ 1991, 1992 QUALCOMM Incorporated. All rights reserved. Printed in the United States of America.

QUALCOMM® is a registered trademark of QUALCOMM Incorporated.

October 1992 DL90-1650 C

**FIGURES**

#### CONTENTS

| Title                                     | Page | Nι | ımber                                   | Page |

|-------------------------------------------|------|----|-----------------------------------------|------|

| FEATURES                                  | 4    | 1  | Typical Application of FEC              |      |

|                                           |      |    | in a Communication System               | 5    |

| GENERAL DESCRIPTION                       | 4    | 2  | Q1650 Encoder Block Diagram             |      |

|                                           |      | 3  | Q1650 Decoder Block Diagram             |      |

| THEORY OF OPERATION                       | 6    | 4  | k=7 Convolutional Encoder               |      |

| Convolutional Encoder                     | 6    | 5  | Punctured Coding System                 |      |

| Viterbi Decoder                           |      | 6  | Best Punctured Code Patterns            | 9    |

| Puncture Coding                           | 7    | 7  | Q1650 Clocking Scheme                   |      |

| O                                         |      | 8  | Q1650 Coding Performance                |      |

| FUNCTIONAL OVERVIEW                       |      | 9  | Re-Encode and Compare Circuit           |      |

| Interfacing                               | 10   | 10 | Hard vs. Soft Decision Code Performance |      |

| Clocking Scheme                           |      | 11 | Bit Error Rate Measurement Circuit      |      |

| Coding Performance                        |      | 12 | Parallel Data Mode                      |      |

| Performance Monitoring                    |      | 13 | Serial Data Mode                        |      |

| Synchronization                           |      | 14 | Normalization Rate Monitor Circuit      |      |

| Decoder Input Data Formats                |      |    | Q1650 Pinout Diagram                    |      |

| Reset Circuit Operation                   |      |    | PLCC Packaging                          |      |

| Monitoring Channel Bit Error Rate         |      |    | CLDCC Packaging                         |      |

| Data Scrambling                           |      |    | 8 8                                     |      |

| Parallel vs. Serial Data Modes            |      |    |                                         |      |

| Device Throughput Delay                   |      |    | TABLES                                  |      |

| Full vs. Short Memory Chainback           |      |    |                                         | _    |

| Normalization Rate Monitor Operation      |      | N  | umber                                   | Page |

| (Synchronization Status Monitor)          | 18   | 1  | Q1650 Modes of Operation                | 22   |

| Direct vs. Peripheral Data Mode Operation |      | 2  | Q1650 Read Registers Memory Map         |      |

| Zacco (or respective zacco operate        |      | 3  | Q1650 Write Registers Memory Map        |      |

| MODES OF OPERATION                        |      | 4  | Q1650 Read Registers                    |      |

| Code Rate 1/2 Mode Operation              | 20   | 5  | Q1650 Write Registers                   |      |

| Code Rate 1/3 Mode Operation              |      | 6  | Q1650 Pin Functions                     |      |

| Code Rate 3/4 or 7/8 Mode Operation       |      |    | ~                                       |      |

| Higher Code Rate Operation Using Extern   |      |    |                                         |      |

| Puncturing Mode                           | 24   |    |                                         |      |

|                                           |      |    |                                         |      |

| TECHNICAL SPECIFICATIONS                  |      |    |                                         |      |

| Processor Interface                       |      |    |                                         |      |

| Pin Descriptions                          |      |    |                                         |      |

| Absolute Maximum Ratings                  |      |    |                                         |      |

| DC Electrical Characteristics             |      |    |                                         |      |

| Timing                                    | 38   |    |                                         |      |

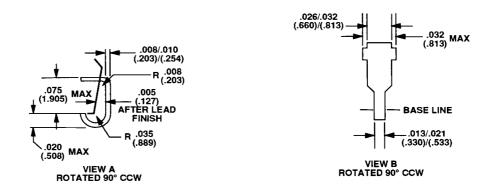

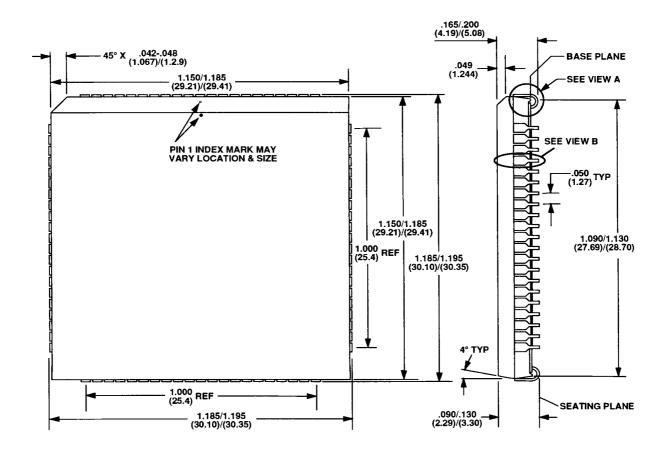

| PLCC Packaging                            | 46   |    |                                         |      |

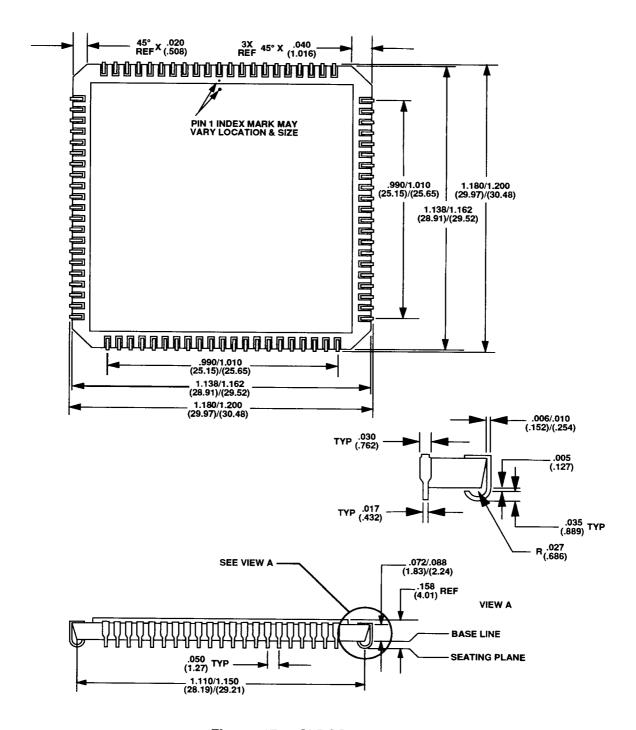

| CLDCC Packaging                           | 47   |    |                                         |      |

| REFERENCES                                | 48   |    |                                         |      |

| GLOSSARY                                  | 48   |    |                                         |      |

| ORDERING INFORMATION                      | 49   |    |                                         |      |

#### **FEATURES**

- Stand-Alone Full-Duplex Rate 1/3, 1/2, 3/4, and 7/8 Encoder/Decoder

- On-Chip Bit Error Rate Monitor

- Three Pin-for-Pin Compatible Versions: 2.5, 10, and 25 Mbps Maximum Data Rates

- Processor Interface Simplifies Control and Status

- 3-Bit Soft-Decision Decoder Inputs

- 5.2 dB Coding Gain (Rate 1/2), 5.5 dB Coding Gain (Rate 1/3) at 10<sup>-5</sup> BER

- Easy Implementation of Additional Code Rates

- Automatic Synchronization Capability

- Parallel or Serial Decoder Data Inputs

- On-Chip V.35 Data Scrambler/Descrambler

- Low Power CMOS Implementation

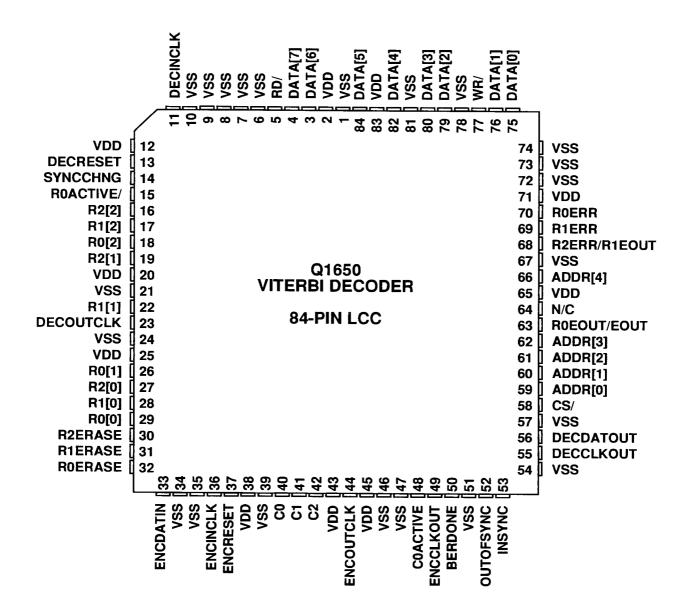

- Standard 84-Pin LCC Package

- Complies with INTELSAT IESS-308 and 309

- Commercial and MIL versions available

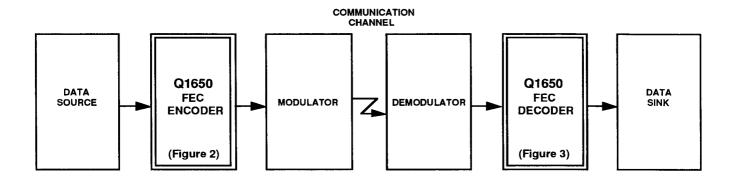

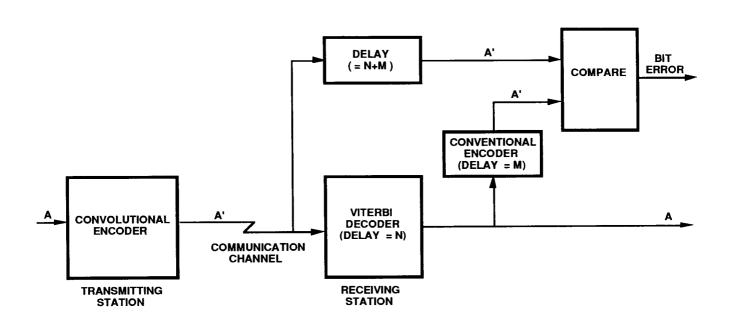

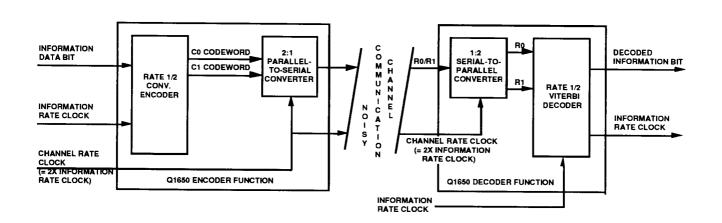

Forward Error Correction (FEC) techniques provide higher throughput data rates with improved bit error rate performance for power-limited (and in some cases bandwidth-limited) digital communication channels. Convolutional encoding of data combined with Viterbi decoding at the receiving node is the industry FEC standard for digital channels, especially those concerned with errors caused by the introduction of additive white Gaussian noise (AWGN). Satellite communication channels are examples of this noise environment. Figure 1 shows a typical application of FEC techniques in a communication system.

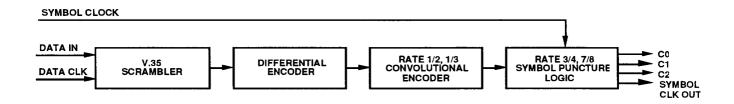

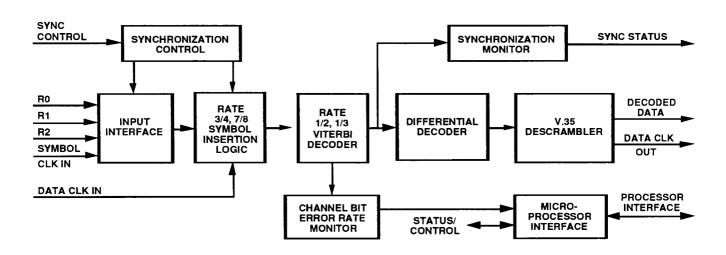

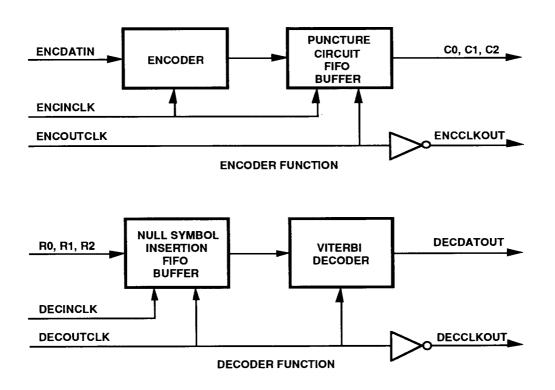

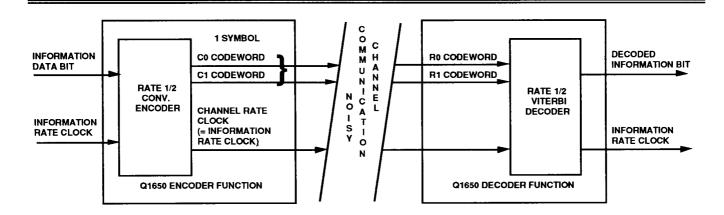

The Q1650 decoder provides convolutional encoding and Viterbi decoding of data channels while also incorporating powerful built-in features. Its capabilities have been optimized for modern digital communication channels. Figures 2 and 3 show block diagrams of the encoder and decoder functions of the Q1650 FEC system.

The Q1650 device processes data at one of four selectable code rates (1/3, 1/2, 3/4, and 7/8) using the industry standard constraint length (k) seven algorithms. It can operate at other code rates with minimal external circuitry. The Q1650 device provides built-in synchronization capability for standard BPSK (Binary Phase Shift Keying), QPSK (Quadrature), and OQPSK (Offset Quadrature)

modems and operates with either 1-bit hard-decision data or 3-bit soft-decision encoded data.

The decoder is available in multiple speed grades with maximum data rates of 2.5, 10, and 25 Mbps to suit a variety of systems applications. All speed versions are pin-for-pin compatible; a single modem board design can be used for many of data rates.

The Q1650 device includes two powerful built-in techniques for monitoring synchronization status and for performing channel bit error rate measurements. In addition, the device includes a processor interface to facilitate control and status monitoring functions while keeping device pinout to a minimum.

The Q1650 decoder is packaged in an 84-pin plastic or ceramic LCC package and is implemented in fully static CMOS logic to reduce power consumption. The device uses fully parallel circuit architecture to negate the requirement for a higher speed computation clock as found in most Viterbi decoder implementations.

The Q1650 decoder is well suited to commercial satellite communication networks, including INTELSAT and INMARSAT, and to military and NASA communication systems. The low cost and high performance of the Q1650 product line make it ideal for FEC requirements in systems like DBS, VSAT, digital modems, and digital cellular telephone applications.

Figure 1. Typical Application of FEC in a Communication System

Figure 2. Q1650 Encoder Block Diagram

Figure 3. Q1650 Decoder Block Diagram

#### THEORY OF OPERATION

#### Convolutional Encoder

Convolutional codes have been studied and used for forward error correction (FEC) in digital communication systems since the 1950s. A convolutional code maps a number (n) of information bits into a number (m) of single-bit "code words" to be transmitted over the channel, where m>n. The ratio of <sup>n</sup>/m is referred to the code rate. For instance, a commonly used convolutional code transforms each information bit (i.e., n=1) to two code words (i.e., m=2) prior to transmission over the noisy channel. This is a rate <sup>1</sup>/<sub>2</sub> code.

The transformation from information bits to code words for transmission is accomplished by a time convolution of the information data with a finite-memory windowing function commonly referred to as a generating function. In the case of the rate ½ code previously described, two generating functions (G0

and G1) are convolved with the information data stream such that each time a new information data bit is considered, the G0 and G1 generating functions each create one output bit or code word (C0, C1, respectively).

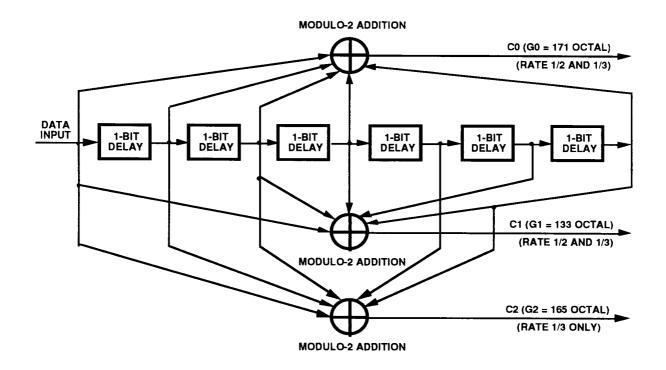

The length of the finite memory of the convolutional generating function is the "constraint length" of the code. Figure 4 shows the generating functions of the rate  $^{1}/_{2}$  and  $^{1}/_{3}$  codes implemented by the Q1650 convolutional encoder. As the diagram shows, the memory length of the encoder is six previous bits plus the current input bit; thus, this is a constraint length seven code (commonly denoted as k=7). The generating functions of the convolutional code are identified by denoting the "taps" of each convoluting function. For the rate  $^{1}/_{2}$ , k=7 code shown in Figure 4, the generating functions are denoted as G0=1111001 (binary) or 171 (octal) and G1=1011011 (binary) or 133 (octal). This algorithm provides the best error correcting performance of all rate  $^{1}/_{2}$ , k=7 codes.

Figure 4. Constraint Length Seven (k=7) Convolutional Encoder

The Q1650 device implements two fundamental convolutional codes. Specifically, these codes are the rate  $^{1}/_{2}$  code previously described and a second code which is also k=7, but with a code rate of  $^{1}/_{3}$ . The rate  $^{1}/_{3}$  algorithm involves three generating functions which are applied each time a new information bit is input to the encoder as shown in Figure 4. Two of these three generating functions (specifically G0 and G1) have the same values, i.e., 171 and 133 (octal), respectively, as the rate  $^{1}/_{2}$ . The third generating function (G2) for the rate  $^{1}/_{3}$  code is 165 (octal).

In addition to these two fundamental codes, the Q1650 decoder can implement higher code rates through "punctured coding." This technique is described below. Higher code rates, such as rate  $^3\!/_4$  or  $^7\!/_8$ , reduce the coding gain of the FEC system. However, these higher code rates increase the bandwidth efficiency of the communication system when compared to a rate  $^1\!/_2$  or  $^1\!/_3$  code.

#### Viterbi Decoder

While the implementation of a convolutional encoder is quite straightforward and simple as shown in the previous section, the decoding of such a coded data stream at the receiving node is quite complex. In the late 1960s, Dr. A. J. Viterbi described a maximum likelihood decoding technique which greatly reduced the circuit sophistication of previous approaches. In spite of this advance, the circuit complexity of such a decoder prevented high-speed single-chip implementations of the Viterbi algorithm until the mid-1980s when QUALCOMM introduced the Q1401 Viterbi decoder. Now, the Q1650 decoder offers the most efficient and powerful single-chip implementation of the Viterbi decoder algorithm.

Viterbi decoding consists fundamentally of three processes. The first step in the decoder process is to generate a set of correlation measurements, known as "branch metrics", for each "m" grouping of code words input from the communication channel (where "m" is 2 for rate ½ codes, 3 for rate ½ codes, etc.). These branch metric values indicate the correlation between the received code words and the 2<sup>m</sup> possible code word combinations.

The Viterbi decoder determines the state of the 7-bit memory at the encoder using a maximum likelihood technique. Once the value of the encoder memory is determined, the original information is known, since the encoder memory is simply the information that has been stored in the memory. To determine the

encoder state, the second step in the Viterbi algorithm generates a set of  $2^{k-1}$  (remember that "k" is the constraint length, i.e., k=7 for the Q1650 algorithms) "state metrics" which are measurements of the occurrence probability for each of the  $2^{k-1}$  possible encoder memory states. As the state metrics are computed, a binary decision is formed for each of the  $2^{k-1}$  possible states as to the probable path taken to arrive at that particular state. These binary decision are stored in a "path memory."

Step three computes the decoded output data. To do this, the "path" from the current state to some point in the finite past is traced back by "chaining" the binary decisions stored in the path memory during step 2 from state to state. The effects caused by noise to the one and only correct result are mitigated as the paths within the "chainback" memory converge after The greater the "depth" of the some history. chainback process the more likely that the final decoded result is error free. As a result, higher code rates and constraint lengths require longer chainback depth for best performance. The chainback memory in the Viterbi decoder traces the history of the previous states to arrive at the most probable state of the encoder in the past, and thus determine the transmitted data.

### Puncture Coding

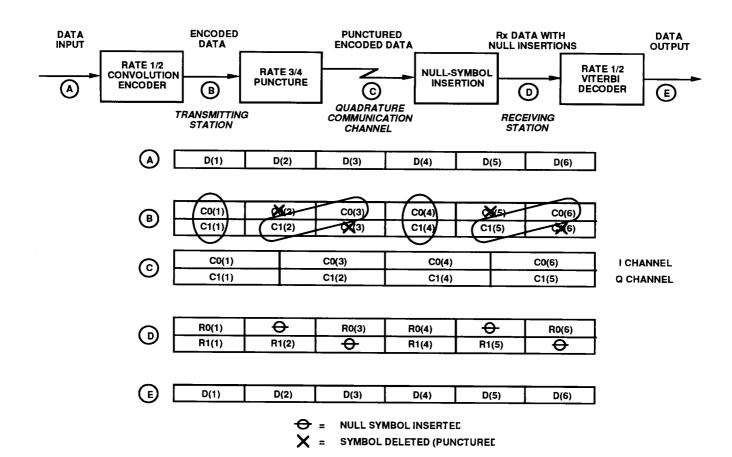

Punctured coding techniques allow a lower rate encoder/decoder (e.g., rate 1/2) to be used to generate a higher rate coding function (e.g., rate  $\frac{3}{4}$ ). operation of a punctured code system is illustrated in Figure 5. This figure shows a system based on a rate 1/2 encoder and decoder used to generate a transmitted code rate of <sup>3</sup>/<sub>4</sub>. This operation first consists of encoding the information (A) to be transmitted with a rate 1/2 encoder (B). However, prior to transmission certain of the symbols of the rate 1/2 encoded stream are "punctured" or deleted and not transmitted (C). In the example of Figure 5, two out of six bits from the rate 1/2 encoder are deleted in a repeating pattern. Since for every three information bits to be transmitted only four encoded bits are actually transmitted, this is a rate 3/4 code operation.

At the receiving node the punctured encoded bits are replaced with "null" symbols prior to decoding with the rate ½ decoder (D). These nulls symbols are indicated to the Q1650 decoder inputs by asserting the "erase" input pins as appropriate for R0, R1, or R2. The decoder treats these null symbols as a symbol which is neither a received "1" nor "0", but is exactly

between the "1" and "0"; that is, no information is conveyed by that symbol. This is, of course, reducing the amount of information available to the rate ½ decoder from which to make decisions about the original data stream. However, the coding performance of this "punctured" rate ¾ code operation matches the coding performance of the best known classic rate ¾ convolutional code.

The major advantage to this approach is that a single code rate decoder (i.e., rate ½ or ⅓) can implement a wide range of codes. Specifically, any code rate of the form (n-1)/n can be efficiently implemented with this structure. Of course, the best performance is achieved only with a certain pattern of the puncturing of symbols. These best puncture

codes have been researched and are shown in Figure 6 for rates from <sup>2</sup>/<sub>3</sub> through <sup>15</sup>/<sub>16</sub>. One important aspect of operation with punctured codes is that the chainback depth of the rate 1/2 decoder must increase as the code rate increases. Whereas a chainback memory depth of 35-40 states is adequate for rate 1/2 decoding, rate 3/4 decoders require memory depths of at least 70 states to be efficient, and rate <sup>7</sup>/<sub>8</sub> puncture decoders should have a minimum chainback depth of more than 90 states. The Q1650 device implements a minimum chainback memory depth of 96 states and therefore is very effective at decoding code rates up to <sup>7</sup>/<sub>8</sub>. Operation with code rates higher than rate 7/8 will result in a minor performance degradation in the coding gain when compared to the theoretical best.

Figure 5. Punctured Coding System

One additional aspect to punctured coding operation is the requirement to synchronize the decoder "null symbol insertion" pattern to the encoder symbol puncture pattern. The Q1650 device performs all the necessary encoder symbol puncture, decoder null symbol insertion, and synchronization functions required to implement the best rate <sup>3</sup>/<sub>4</sub> and <sup>7</sup>/<sub>8</sub> patterns. In addition, the Q1650 decoder includes integral First-In-First-Out (FIFO) circuits to ease the frequent requirement of punctured code systems to re-

align the punctured encoded stream to a channel clock which is a non-integer multiple of the information data rate.

The Q1650 decoder also provides "symbol erasure" input pins for the R0, R1 and R2 decoder inputs. These pins allow the designer to implement punctured code rates other than the rate  $^{3}$ /4 and  $^{7}$ /8 patterns implemented internally on the device.

| CODE<br>RATE | SYMBOL | PUNCTURE PATTERN (0 = DELETED CODEWORD) |

|--------------|--------|-----------------------------------------|

|              | co:    | 1                                       |

| 1/2          | C1:    | 1                                       |

| 2/3          | CO:    | 10                                      |

| 2/0          | C1:    | 11                                      |

| 3/4*         | co:    | PV)                                     |

| 3/4          | C1:    | 166                                     |

| 4/5          | co:    | 1000                                    |

| 4/5          | C1:    | 1111                                    |

| 5/6          | CO:    | 10101                                   |

| 5/6          | C1:    | 11010                                   |

| 6/7          | co:    | 100101                                  |

| 0//          | C1:    | 111010                                  |

| 7/8*         | CO:    | (1009)91                                |

| 1/6          | C1:    | 101666                                  |

| 11/12        | CO:    | 10001000001                             |

| 11/12        | C1:    | 11110111110                             |

| 12/13        | CO:    | 10000001010                             |

| 12/13        | C1:    | 11111110101                             |

| 15/16        | CO:    | 100110100101101                         |

| 15/16        | C1:    | 111001011010010                         |

| 46/47        | CO:    | 1010101101111010                        |

| 16/17        | C1:    | 1101010010000101                        |

<sup>\*</sup>Two-code word groupings are shown for operation with code rates  $^{3}/_{4}$  and  $^{7}/_{8}$  in parallel data mode. C0 and C1 code words are output on the C0 and C1 signals, respectively, except for the second symbol in rate  $^{7}/_{8}$  pattern. In that case, the second of the two C1 code words is output on the C0 signal.

Figure 6. Best Punctured Code Patterns

#### **FUNCTIONAL OVERVIEW**

#### Interfacing

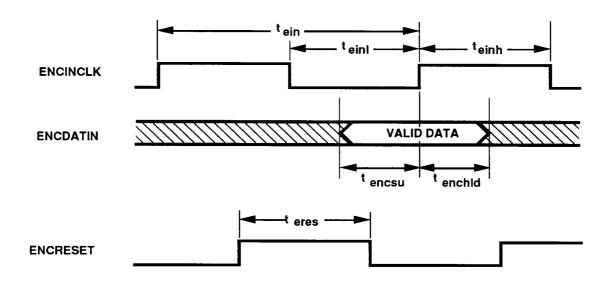

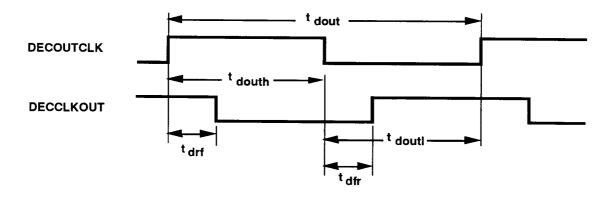

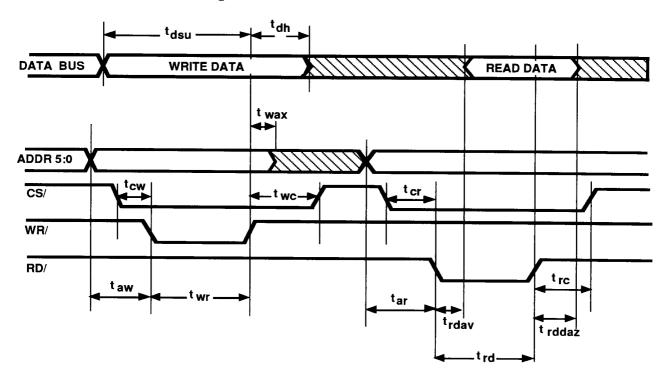

Interfacing with the Q1650 decoder is straightforward. All data inputs are provided to the device synchronously with externally sourced clocks. Data signals are clocked into the device on the rising edge of the encoder and decoder clock inputs. Data outputs change on the rising edge of the encoder and decoder clock outputs. To provide varying code rates, the Q1650 device requires two externally generated clock inputs for operation of the encoder and decoder, specifically a data rate clock and a channel rate clock. The frequency relationship of these two clocks varies according to code rate and data input format.

Most control and status information is provided to and from the Q1650 device through a bus-oriented processor interface. This interface uses an 8-bit data bus and a 5-bit address bus along with read, write, and chip select signals to read from status ports and write to control ports. In addition, the encoder and decoder input and output data can be written and read directly using the processor interface. In this mode, the Q1650 device acts as a peripheral for forward error correcting of data processed by a host processor.

#### Clocking Scheme

Multiple code rate operation of the Q1650 encoder and decoder functions requires special timing circuits to provide for the various modes of operation. For each code rate R, the Q1650 encoder function outputs  $\frac{1}{12}$  encoded bits for each input information bit. For instance, two encoded output bits are generated for each information bit when operating with code rate  $\frac{1}{2}$ . As described below, these encoded bits can be output in either "parallel" or "serial" fashion.

When encoded bits are output in the parallel mode, the outputs are provided on two output signals which are clocked at the same frequency as the input information. However, if the two encoded bits are output in the serial manner, all outputs are provided on the same pin and the data on this pin changes at twice the rate of the input information bits. Thus, two clocks must be provided to the encoder functions: the first clock is used for the input of information bits on the ENCDATIN pin and the second clock is used to output the serial format data on the C0 output pin.

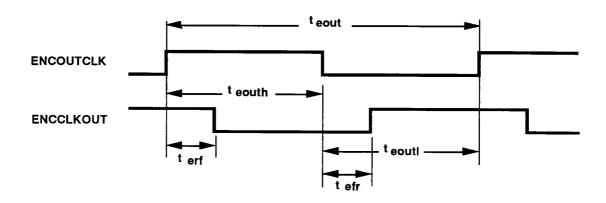

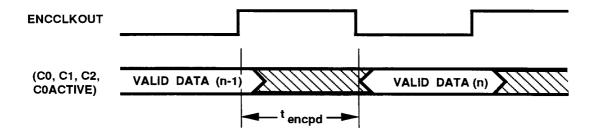

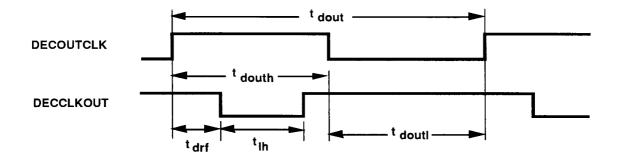

The decoder allows for this condition by clocking the input information data on a completely independent clock from that used to output encoded data from the encoder. The input information is clocked into the device relative to the ENCINCLK signal, while output data is clocked relative to the ENCOUTCLK. The information sourced to the encoder function is resynchronized to the output clock within the decoder with an asynchronous first-in first-out (FIFO) circuit. This asynchronous buffer capability is especially useful when operating with a code rate in which the output-to-input bit rate is not an integer (e.g., rate <sup>3</sup>/<sub>4</sub> or <sup>7</sup>/<sub>8</sub>). Figure 7 shows the general clocking scheme for the Q1650 encoder and decoder functions. Note that the output clock input to the encoder is also provided as an output from the encoder. The Q1650 decoder function also makes use of two different clock signals to provide for changing code rates.

The ratio between the frequency of the input information clock and output encoded bit clock changes with changing code rate. When operating at code rate ½ and serial output mode, the ratio of the encoder input clock to encoder output clock frequency is ½. When operating with rate ½ coding and parallel data mode the frequency of the input and output clock is the same. In fact, the decoder clock scheme is symmetrical to the encoder clock scheme.

Operation with rates 3/4 and 7/8 involves a more sophisticated relationship between the input information clock to the encoder or decoder and the output bit clock. Specifically, when operating with rate 3/4 coding and parallel outputs, the ratio of ENCINCLK frequency to ENCOUTCLK frequency is  $\frac{3}{2}$ . This is because for every three input information bits two outputs of two bits each are formed (refer to the section on rate  $\frac{3}{4}$  encoding operation below). These two clock frequencies must be provided by external circuitry. In a typical communication system only one of the two clocks is explicitly provided by the system, usually the channel clock signal. In this kind of system the information clock signal may be generated using various synthesis techniques such as phase-locked loop (PLL) circuits. The FIFO buffer allows for phase jitter in the relationship of the two clocks in that the FIFO is eight words deep. Upon reset the FIFO is set to operate in a half-full condition. This allows up to four input clock periods or output clock periods to occur without overflowing or under flowing the FIFO buffer.

The ratio between the information clock and the encoded clock frequencies is <sup>4</sup>/<sub>7</sub> when operating with rate <sup>7</sup>/<sub>8</sub> coding and parallel mode.

#### **Coding Performance**

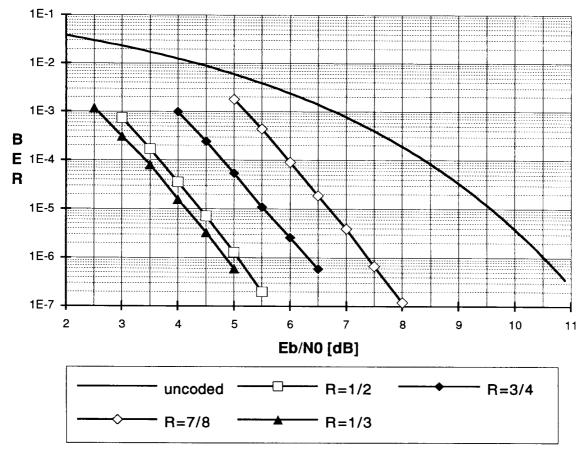

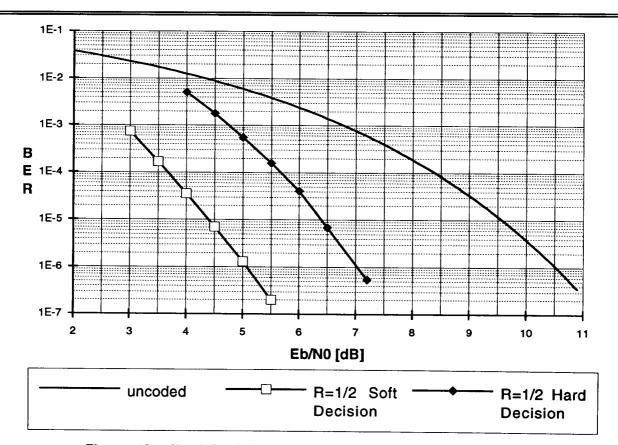

The Q1650 decoder provides coding performance very near the theoretical limits for the optimal k=7 rate  $^{1}/_{3}$ ,  $^{1}/_{2}$  and  $^{3}/_{4}$  Viterbi decoder algorithm and very good performance for rate  $^{7}/_{8}$  decoding as shown in Figure 8. Coding gain of 5.5 dB is achieved when operating at a code rate of  $^{1}/_{3}$  and decoded bit error rate of  $^{1}0^{-5}$  with a BPSK or QPSK optimal soft-decision modem. Coding gain is 5.2 dB for the same conditions when operating with rate  $^{1}/_{2}$  coding.

#### **Performance Monitoring**

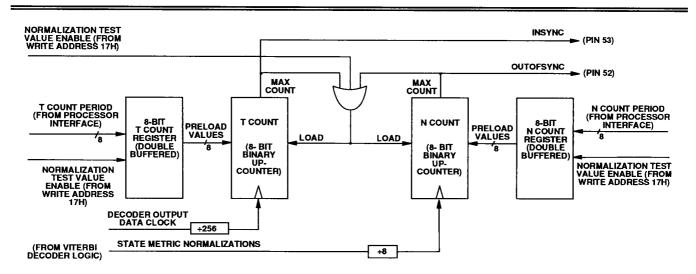

The Q1650 decoder provides two powerful means of monitoring the Viterbi decoder function performance. The first technique monitors the rate at which the internal state metrics of the Viterbi algorithm increase in value. Rapidly increasing state metric values indicate that the decoder may be out of synchronization to the phase or symbol grouping associated with the input symbols. When all state metrics in the Viterbi decoder reach a certain numeric value, a normalization circuit reduces the value of all metrics by a fixed amount to prevent metric overflow.

The Q1650 device monitors the rate that these normalizations occur while decoding data. The system designer determines an acceptable normalization rate threshold and programs this threshold into the device. The designer controls both the period of time in which the metric normalization is monitored as well as the number of normalizations allowed during that time. These two numbers, which provide for more than 65,000 possible settings, are programmed into the device using the microprocessor interface. If the threshold is exceeded during any test period, a signal (OUTOFSYNC) indicates the detected loss of synchronization. In many cases, this signal can be connected to a synchronization control input pin (SYNCCHNG). In this configuration, the Q1650 decoder will try to correct the synchronization by changing the synchronization state of the decoder input and perform a retest. This technique provides a complete self-synchronizing Viterbi decoder function for a variety of communication systems with no external logic required.

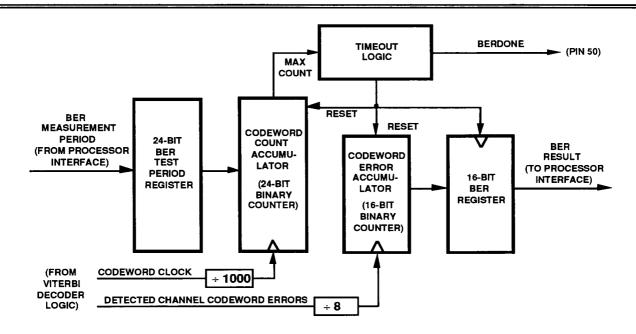

The second performance monitor built into the Q1650 decoder is a channel bit error rate monitor. This

Figure 7. Q1650 Clocking Scheme

monitor works on a re-encode and compare principle as shown in Figure 9. Specifically, if a data stream {A} is first convolutionally encoded to be a data stream {A'} and then Viterbi decoded without errors injected by the transmission channel, the resulting data stream will be the original {A}. If the output data stream of the decoder were to be re-encoded with the same convolutional encoder algorithm as the original stream, then the encoded stream {A'} is again generated. Delaying the input data stream to the decoder by the exact delay associated with the Viterbi decoder and re-encoder and then comparing this delayed input with the re-encoded stream on a bit-by-bit basis will result in a constant equal comparison if the channel introduces no errors. However, if the channel introduces bit errors to the received data stream {A'}, this bit-by-bit comparison will indicate a miss whenever these channel bit errors occur. The monitor tracks the errors to generate a highly accurate estimate of the channel bit error rate (BER). Of course, the BER monitor will also indicate errors when the decoder fails to correct an

information bit error. However, the probability of an error occurring in a decoder output bit is at least two orders of magnitude below the probability of a channel error during normal operating conditions. Therefore, the effect of decoder errors on the accuracy of the BER measurement is minimal.

#### Synchronization

The Q1650 decoder can automatically synchronize incoming data streams to the Viterbi decoder circuit. Synchronization may require on-chip offsetting for bit, phase, and puncture pattern alignment depending on the particular mode of operation of the decoder. The synchronization technique is a two-step process. First, the decoder quality state is constantly monitored using the "state metric normalization rate" circuit described above. The user programs an "insync/out-of-sync" threshold for this internal circuit. The success or failure of this test for each test period is indicated on Q1650 output pins 53 (INSYNC) and 52

Figure 8. Q1650 Coding Performance

(OUTOFSYNC). This synchronization monitor function is operational whenever the Q1650 decoder function is processing data.

The second step of the automatic synchronization process attempts to correct an indicated out-of-sync condition by offsetting the data input to the decoder just prior to the actual decoding process. particular offsetting technique depends on the specific mode of operation selected. In all cases, the effects of the out-of-sync condition can be compensated for either by a timing re-alignment or by permutation of the decoder input data. Wiring the OUTOFSYNC output pin (pin 52) directly to the SYNCCHNG input pin (pin 14) on the Q1650 device a feedback path between provides synchronization monitor and the synchronization correction circuit. When an out-of-sync condition is the input processor switches indicated, synchronization state. The synchronization monitor test continues and will indicate whether the offsetting action taken by the decoder input processor has corrected the out-of-sync condition.

Some operating modes allow more than two synchronization states. If, in such cases, an out-of-sync condition is again indicated by the synchronization monitor circuit, the input processor will continue to step through all possible

synchronization states. If an out-of-sync condition continues to be indicated after all possible synchronization states have been attempted, the decoder repeats the process of stepping through all the possible states until the out-of-sync indications are no longer received (i.e., an in-sync condition exists).

Descriptions of the particular synchronization states attempted for each mode of operation follow.

#### **Decoder Input Data Formats**

As seen in Figure 10, the Viterbi decoder provides the highest coding gain performance when processing multiple bit "soft-decision" values for the R0, R1, and R2 (if applicable) code words. The optimal softdecision values are linearly quantized 3-bit values for each code word. (See QUALCOMM Application Note AN1650-2 "Setting Soft-Decision Thresholds for Viterbi Decoder Code Words from PSK Modems" for techniques on optimizing the soft decision for demodulator output samples.) The 3-bit soft-decision values can be input to the Q1650 decoder inputs (R0, R1, and R2) in either sign-magnitude or offset-binary notation. The encoding of soft-decision values for each format is given in Table 5, Q1650 Write Registers, Decoder Control Register 2. Input format selection is made via the microprocessor interface.

Figure 9. Re-Encode and Compare Circuit

When using the Q1650 Viterbi decoder with hard-decision (single-bit) values for R0, R1, and R2, the decoder input format should be set to sign-magnitude notation. The Rx[0] "magnitude" bits (R0[0], R1[0], and R2[0]) should be set to logic "1" (logic high). The Rx[1] "magnitude" bits (R0[1], R1[1], and R2[1]) should be set to logic "0" (logic low). The hard decision code word should be input on the "sign" signal pins (R0[2], R1[2], and R2[2]) as appropriate.

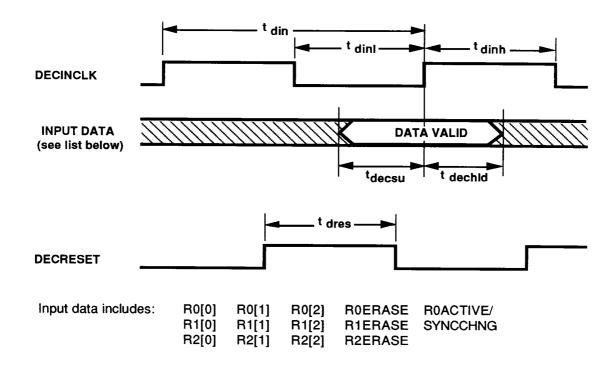

#### **Reset Circuit Operation**

The Q1650 encoder and decoder functions have individual reset inputs. A reset operation should be performed when the decoder is initially configured and when a change occurs in the mode of operation.

The reset operation can be performed using either the external input pins DECRESET (pin 13) and ENCRESET (pin 37) or reset bits in control registers of the processor interface. The operation of external input pins and processor controlled bits is identical.

When an encoder or decoder reset is asserted, either by setting the input pin to logic high or setting the processor interface bit to "1," the reset is latched synchronously into the Q1650 decoder. Both input clocks of the encoder and/or decoder must be operational during reset. The reset operation is edge-triggered, and the actual reset occurs only during the first clock periods after the reset line is asserted. Continuing to hold the reset line or bit to the logic high or "1" condition does not cause a continuous reset.

A reset affects the internal state of the puncture and synchronization circuits. Resetting the encoder circuit sets all the states of the convolutional encoder to logic "0." Resetting the decoder does not set the internal states of the path memory to a fixed value.

#### Monitoring Channel Bit Error Rate

The technique for monitoring the channel bit error rate (i.e., the "symbol error rate") using the internal "re-encode and compare" circuit on the decoder has been previously described in this data sheet. The bit error outputs of the re-encode and compare circuit can

Figure 10. Hard Decision vs. Soft Decision Code Performance

be monitored either using the on-chip bit error rate (BER) monitor circuit or externally using an off-chip circuit. The on-chip BER monitor circuit is a flexible and powerful technique for determining the channel error rate. The use of an external circuit should not be required in most systems.

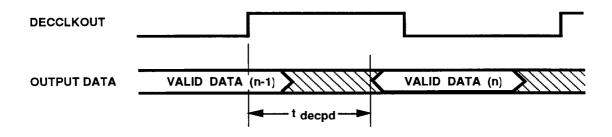

Figure 11 shows the functional diagram of the on-chip bit error rate measurement circuit. This circuit consists of two accumulators acting as counters. The first accumulator counts decoder input code words. The second accumulator counts code word errors detected by the re-encode and compare circuit. The period of the BER measurement is determined by the user-selectable value for the maximum count of the code word-count accumulator. This value is the two's complement 24-bit binary value entered into the Q1650 device via the processor interface. The loaded value is multiplied by 1000 to give the actual number of code words to be monitored in the BER measurement.

The BER measurement operates whenever the clock signal DECOUTCLK (pin 23) is active (i.e., toggling). During the BER measurement period, the detected errors are accumulated in the code word-error accumulator. This 16-bit binary accumulator is reset at the beginning of each BER measurement period. Once the 24-bit period of the BER measurement is

entered, the loaded value is activated by writing any value to the "BER Test Value Enable" processor interface port (address 18 hex). The BER measurement is completed when the code word-count accumulator completes its count. At this point the number of detected code word errors recorded in the error-count accumulator is transferred to a parallel 16-bit buffer register.

The completion of the BER measurement period is indicated by BERDONE (pin 50), which goes to logic high for two periods of DECOUTCLK (pin 23). The BERDONE signal can be used as an interrupt or polled status bit to a controlling processor. The accumulated error value can then be read via the processor interface. The actual measured bit error count is found from the following formula: Actual Error Count = (Register Value – 1)\*8, where "Register Value" is the value read from the 16-bit BER measurement register. That is, if no errors are recorded, the BER measurement register will have a value of "1" stored. If the number of errors exceeds the limit of the 16-bit register, the BER measurement will read as "0000h." The BER test continues running and stores the next test value in the 16-bit BER measurement register upon the completion of each test.

The actual symbol BER is computed by dividing the measured error quantity by the number of code words

Figure 11. Bit Error Rate Measurement Circuit

in the test. This measurement division is facilitated if the measurement period is a power of 10, such as 10,000 or 100,000 code words long. In this case, the binary number recorded by the error accumulator is the mantissa of the symbol BER and the exponent of the BER value is determined by the measurement period. For example, if the test period is set to  $100,000 \ (= 10^5)$  code words and 250 errors are recorded during the measurement period, the measured symbol BER is  $2.5 \times 10^{-3}$ .

In the event that more than 2<sup>19</sup> code word errors are recorded in the measurement period, the code word error accumulator will saturate at an "all zeros" value. If this condition is indicated at the completion of a BER measurement, the period of the measurement should be reduced until a value less than saturation is recorded.

For an accurate measurement of the symbol BER, at least 100 errors should be detected within a given test period. If fewer than 100 are recorded, the statistical variance associated with such a measurement will be high. In this case, the measurement period should be increased until more than 100 code word errors are detected during the BER test.

The on-chip BER monitor can be used for measurements other than simply the symbol BER. For example, by setting the measurement period to the code word rate (i.e., code words per second), the test period becomes equal to exactly one second in time. The BER monitor therefore becomes a straightforward means for monitoring error-free seconds, which is frequently a useful error statistic. If no errors are recorded during the one second period this is an error-free second. External hardware or software can record the percentage of error-free seconds for error statistics purposes.

#### Data Scrambling

The Q1650 decoder includes an on-chip data scrambling circuit which can be enabled or disabled via the processor interface. Data scrambling is frequently used in conjunction with FEC techniques to guarantee minimum transition densities in the transmitted signal for purposes such as timing loop synchronization. The Q1650 device implements a specific scrambling algorithm specified in CCITT Recommendation V.35. Actually, the decoder implements two versions of the V.35 algorithm. The first version meets the letter of the CCITT specification exactly. The second version is a very

slight modification of the CCITT specification which complies with a *de facto* scrambling standard used in several leading communication networks, including the INTELSAT IBS and IDR services. The details of these algorithms are described in QUALCOMM Application Note AN1650-1 "Data Scrambling Algorithms Implemented in the Q1650 Viterbi Decoder." Selection of the particular scrambling algorithm is via the microprocessor interface.

Data scrambling is performed "outside" the convolutional coding functions. That is, data scrambling, when enabled, is performed prior to differential encoding and convolutional encoding in the encoding function of the Q1650 decoder. In a symmetric manner, data descrambling is performed after data is Viterbi decoded and differentially decoded in the Q1650 decoder function.

A system consideration when designing with the data scrambling enabled is the multiplication of output bit errors from the Viterbi decoder. Error multiplication occurs because the data scrambler output bits are affected by several bits input to the descrambler. If a single bit error occurs at the output of the Viterbi decoder function the data descrambler will theoretically generate up to three output errors due to the multi-output influence of the single bit error. However, in actuality the error statistics at the output of the Viterbi decoder are such that the error multiplication is reduced to an actual factor of 1.5 to 2. This equates to a coding gain loss of only about 0.2 to 0.3 dB. This loss is an acceptable tradeoff for the advantages of the data scrambling function in many systems.

#### Parallel vs. Serial Data Modes

The O1650 convolutional encoder function produces multiple encoded bits for each information input bit. This encoded data can be selected to be output in either "parallel" or "serial" data mode, as shown in Figures 12 and 13. When operating in "parallel" output mode multiple encoded bits are output during each period of the encoder output clock (ENCOUTCLK). Specifically, when operating with code rate 1/2, two encoded bits are output during each period of ENCOUTCLK, when operating in either parallel or serial data mode. These two bits are the C0 and C1 encoded bits for a given information input bit. When operating in the parallel data mode these two output bits are presented at the C0 and C1 output pins during each period of ENCOUTCLK. In this case, the ENCOUTCLK frequency should be the same

as the frequency of ENCINCLK. This mode is most often used for data transmission over a channel that offers 2-bit wide transmission symbols, such as a QPSK channel. In like manner, when operating with rate ½ coding in the parallel mode, three encoded bits (i.e., C0, C1, and C2) are presented at the output pins C0, C1, and C2, respectively, during each period of the ENCOUTCLK signal. As with the rate ½ parallel operation, the frequency of ENCOUTCLK should be the same as the frequency of the ENCINCLK signal.

When operating with either of the punctured coding rates, the operation of parallel data mode differs slightly. Specifically, for operation with rate <sup>3</sup>/<sub>4</sub> code rate in parallel data mode, two output bits are provided during each period of the ENCOUTCLK signal at the C0 and C1 pins. These parallel outputs are two-bit symbols which have been formed from the rate 1/2 encoded bits which remain after the puncturing process. The grouping of these symbols is shown in Figure 6. Again, this mode is most commonly used when operating with transmission systems utilizing two-bit wide symbols, such as with a QPSK system. Operation with rate  $\frac{7}{8}$  coding is similar to that of rate <sup>3</sup>/<sub>4</sub> coding and the formation of two-bit wide symbols after the puncturing process is also shown in Figure 6. In the case of rate 3/4 parallel data mode operation the frequency of ENCOUTCLK must be set to be  $\frac{2}{3}$  the frequency of ENCINCLK.

This is because two 2-bit symbols are formed for every three input information bits. This non-integer clock multiplication must be provided with external circuitry. The frequency of the ENCOUTCLK signal must be  $\frac{4}{7}$  the frequency of ENCINCLK when

operating in rate <sup>7</sup>/<sub>8</sub> parallel output mode.

When operating with serial output mode, all encoded bits are provided on the single output pin C0 in a bit-serial fashion at the period of the ENCOUTCLK signal. In this mode, the output data format is identical to that of the parallel mode, regardless of the code rate, except that the data is serialized before output. The first output bit for each symbol will be the C0 bit, followed by the C1 bit, and finally by the C2 bit (if operating with code rate ½). The Q1650 device indicates the current bit by applying a logic "1" level to output C0ACTIVE (pin 48) during output of the C0 encoded bit. Serial data mode is commonly used when operating with transmission channels that transmit a single bit during each symbol, such as with BPSK or binary optical systems.

The Q1650 decoder inputs data in either serial or parallel mode. When operating in the parallel input mode, multiple input code words are provided to the decoder during each period of the DECINCLK signal on the R0, R1, and R2 (if operating with rate 1/3 coding) inputs. The R0, R1, and R2 input values map directly to the C0, C1, and C2 output bits from the encoder. When operating in the serial mode, the decoder inputs all encoded data using only the R0 input pins. The sequence of the input code words must be the same as the sequence of the serial data output from the encoder function. The explicit location of the R0 input symbol in the input stream is indicated by setting the ROACTIVE/signal to logic "0" during clock periods when the R0 code word is input. The relationship of the DECINCLK to DECOUTCLK frequencies is the reciprocal of the relationship of the encoder ENCINCLK to ENCOUTCLK frequencies.

Figure 12. Parallel Data Mode

Note that when operating in the serial data input mode, all of the bits of the soft-decision decoder input code word, including the erasure bit, if used, are input during the same period of the DECINCLK signal. The "serial" mode refers to the manner by which multiple code words are input to the decoder, not to the multiple bits of the soft decision code words.

#### **Device Throughput Delay**

The input-to-output delay through the Q1650 encoder or decoder functions depends on the mode of operation selected. When operating with either rate 1/2 or 1/3 coding and parallel data input, the throughput delay of the encoder is 10½ periods of the ENCINCLK clock, which is normally the same frequency as the ENCOUTCLK input signal in these modes. In these same modes the delay through the decoder is 1821/2 periods of the DECINCLK clock, which is the same frequency as the DECOUTCLK signal, when operating in full memory mode. Operation in short memory mode reduces this decoder throughput delay to 1021/2 clock periods. These throughput delay values are the same for operation in both direct and peripheral modes. These delays will increase by one clock each if the data scrambler or descrambler is enabled.

With serial data operation, the delay in terms of the input clocks will be approximately the same as when using parallel data mode. However, the exact relation between the input and output clock phasing will increase or decrease the throughput delay by as much as one clock period.

When operating with the built-in puncture coding modes (rate  $^{3}/_{4}$  or  $^{7}/_{8}$ ), the throughput delay of the encoder and decoder varies with the exact synchronization state. This uncertainty can be as much as  $\pm 4$  periods of the clock due to the varying delay in the internal Q1650 FIFO buffers.

# Full vs. Short Memory Chainback

The Viterbi decoder function of the Q1650 device can be selected to operate with one of two chainback path depths. "Full" chainback memory operation provides a minimum chainback depth of 96 states while "short" chainback memory operation provides a minimum chainback depth of 48 states. Operation with code rates 1/3 or 1/2 will result in near theoretical coding performance when either full or short chainback depth is selected. Operation with short chainback depth reduces the throughput delay of the decoder function. However, when operating with code rates higher than rate 1/2 (e.g., rate 3/4 or 7/8) the decoder should be operated with full chainback memory in order to provide maximum coding gain. The determination of the chainback depth is selected with bit 0 in the Decoder Control Register 3 of the processor interface.

# Normalization Rate Monitor Operation (Synchronization Status Monitor)

As previously described, the Q1650 decoder includes a circuit for monitoring the rate at which state metric normalizations occur. This "normalization rate" monitoring is a useful technique for determining when the decoder is not in synchronization with the phase

Figure 13. Serial Data Mode

ambiguity, code word grouping, or puncture pattern sequence. In fact, the outputs of the normalization rate monitor circuit are two signals, OUTOFSYNC and INSYNC. The system designer selects the allowed normalization rate (percentage) above which the decoder will indicate an out-of-sync condition.

Figure 14 shows the functional diagram of the onchip normalization circuit. This circuit consists of two counters, similar in operation to the channel BER monitor previously described. The system designer controls the periods of these two counters. The first counter (T) measures the number of decoded bits. The second counter (N) measures the number of state metric normalizations. The normalization rate threshold is determined by taking the ratio of the count of normalizations (the N counter) and the time period (the T counter). Each of these 8-bit wide binary counters is pre-loaded using the processor interface registers. Both the N and T counters are loaded with binary values which are the two's complement of the actual count value. The count value loaded into the T counter is multiplied by 256 to determine the actual number of decoded bits in the normalization test period.

The actual count of the N counter is determined by the following formula: n=(N-1)\*8+4, where "n" is the actual number of normalizations allowed, and "N" is the two's complement value of the 8-bit number loaded into the N counter. With this programming capability, the system designer selects the

normalization rate threshold for determining an insync or out-of-sync condition as well as the period of the measurement. For example, when operating with rate  $^{1}\!/_{2}$  decoding, a normalization rate threshold of about 10% will reliably detect a loss of synchronization.

To avoid false detection of synchronization loss due to a noise burst, the normalization measurement should detect at least 20-30 normalizations before declaring a loss of synchronization. As an example, the system designer may select the number of normalizations to be detected to be approximately 50. By loading the 8-bit two's complement value of seven (i.e., 0F9h) into the N counter register, the actual number of normalizations allowed in a test period without indicating a loss of synchronization would be (7-1)\*8+4 = 52. The value for the T counter must be approximately ten times the value in the N counter: that is, loading the T counter with the two's complement value of 2 (i.e., 0FEh) the actual count value for T will be (2\*256) = 512. Therefore, the actual normalization rate threshold will be 52/512 = 10.2%. This is an appropriate threshold for reliable synchronization when operating with rate ½ coding. The threshold should be set to approximately 1.7% for rate  $\frac{3}{4}$  coding and 0.8% for rate  $\frac{7}{8}$  coding. rate 3/4, programming the N counter to 7 (i.e., 0F9h) and the T counter to 12 (i.e., 0F4h) will give the desired normalization rate of 1.7%. Likewise, for rate 7/8, programming the N counter to 8 (i.e., 0F8h) and the T counter to 29 (i.e., 0E3h) will give the desired normalization rate of 0.8%.

Figure 14. Normalization Rate Monitor Circuit

# Direct vs. Peripheral Data Mode Operation

The Q1650 decoder interfaces data via dedicated signal pins or via the processor interface. The Direct Data mode interfaces all data via the dedicated pins and is most commonly used with synchronous data channels. The Peripheral Data mode interfaces all data signals, including the R0, R1, and R2 inputs and the C0, C1, and C2 outputs, via processor interface registers. This mode is used when the Q1650 device is used as an error control peripheral to the processor system. When operating in Peripheral Data mode the functions of the ENCDATIN (pin 33), ENCINCLK (pin 36), ENCOUTCLK (pin 44), ENCRESET (pin 37), R0 (pins 29, 26, 18), R1 (pins 28, 22, 17), R2 (pins 27, 19, 16), R0ERASE (pin 32), R1ERASE (pin 31), R2ERASE (pin 30), DECINCLK (pin 11), and DECOUTCLK (pin 23), and DECRESET (pin 13) signals are provided by writing to port addresses. In this mode all the above pins should be connected to logic "0." The selection of the Direct or Peripheral Data mode is made by setting bit 3 in both Encoder Control Register 2 and Decoder Control Register 2 of the processor interface. (1 = Peripheral, 0 = Direct).

When the Q1650 device operates in the peripheral mode, each data bit handled by either the encoder or the decoder requires four processing steps. First, the input data to the encoder or decoder is written to the appropriate register using the processor interface (see tables 2 through 5). Second, the processor controlled activation of ENCINCLK or DECINCLK is performed by writing to the appropriate processor interface address. Third, processor controlled activation of ENCOUTCLK or DECOUTCLK is performed by writing to the appropriate processor interface address. Finally, the output data is read from the appropriate register. This cycle repeats for each bit processed by the Q1650 decoder.

#### MODES OF OPERATION

The Q1650 device can operate in one of four internally generated code rates without external circuitry other than that required to generate the clock signals for the particular mode selected. The code rate of the on-chip encoder function can be selected to be different than that of the decoder function. In addition to the basic code rate selection, the Q1650 device supports various user-selected additional operational functions and modes. The selection of the mode of operation is made using the control registers of the

processor interface as described below. The following paragraphs described the functions performed and the design considerations associated with each mode. Table 1 shows all possible combinations of the various modes and identifies the synchronization parameters adjusted by the decoder's internal synchronization circuit (when enabled).

#### Code Rate 1/2 Mode Operation

When operating with code rate ½, two encoded bits (C0 and C1) are generated by the encoder for every information bit. Likewise, two encoded symbols are input to the decoder for every information bit output from the decoder. The encoded bits from the encoder can be output on two signal pins (C0 and C1) at the same clock frequency as the input data when operating in the parallel data mode. Alternatively, both the C0 and C1 encoded bits can be output from the same signal pin (specifically the C0 pin) at two times the frequency of the input information when in serial data mode.

The decoder's operation is similar to that of the encoder, in that the input code words can be input in a parallel fashion with both code words (R0 and R1) input during one period of the DECINCLK clock or serially in two periods of DECINCLK.

The synchronization states differ between the parallel and serial input modes of rate 1/2 operation. When operating with parallel input data the synchronization states of the decoder function assume operation with a QPSK demodulation system. In these types of systems the C0 code word of the rate 1/2 encoded output is commonly transmitted on the in-phase or quadrature channel of the QPSK modulator, while the C1 code word is transmitted on the remaining channel. In this case, the synchronization state machine on the Q1650 decoder must resolve one of two possible values. The initial synchronization state, upon device reset, connects the R0 code word inputs to the internal R0 data lines and the R1 code word inputs to the R1 data lines. This is referred to as the "normal" synchronization state. When the synchronization state of the Q1650 decoder changes due to the assertion of the SYNCCHNG signal the "alternate" synchronization state occurs in which the R0 code word input is used internally as the R1 code word and vice versa. In addition, this mode inverts the R0 value.

The alternate synchronization state offsets the effects of a 90 degree phase ambiguity associated

with QPSK demodulators. A QPSK demodulator actually can synchronize in one of four phase states. However, two of the four states are related to the other two in that they are inversions of both the R0 and R1 values. The effects of this data inversion can be offset by enabling the on-chip differential encoder and decoder circuits on the Q1650 decoder.

Thus, the Q1650 device need only differentiate between the "normal" and the "alternate" synchronization states in order to provide synchronization to QPSK demodulators as long as the differential decoder function is enabled, or some other means is provide by the system to offset the effects of the inversion of the data. When operating in rate  $\frac{1}{2}$ parallel data mode and Offset QPSK (OQPSK) modulation systems an additional step is required when in the alternate synchronization state. In this case, the R1 input data is delayed by a single period of the DECINCLK signal prior to the "swap and invert" of the alternate synchronization state described for QPSK demodulators. This delay is useful for correcting the time offset of the in-phase (I) and quadrature (Q) channels of the OQPSK system.

When operating with rate  $\frac{1}{2}$  coding and serial input data mode, the Q1650 decoder does not adjust for the phase ambiguity, but simply the symbol grouping of the input serial code words. That is, since the two code words for the rate 1/2 encoded symbol are input one at a time the Q1650 decoder must group these inputs prior to the actual decoding process. The input symbols can be grouped (paired) in one of two ways. Only one pairing sequence is correct, that is pairing the R0 input code word with the next input, which would be the associated R1 code word. However, if the Q1650 decoder is not provided with explicit information as to which input is the R0 code word (i.e., if the signal ROACTIVE is not used), the code word pairings may incorrectly group the R1 input of an encoded symbol with the next input, which would be the R0 code word from the next symbol. In this case, the automatic synchronization circuit will detect the incorrect alignment and the assertion of the SYNCCHNG signal will adjust the input symbol stream by stopping the input grouping circuit for a single period of the DECINCLK signal, resulting in the correct pairing of code words. This technique requires that the C0 code word for a given encoded symbol always be transmitted immediately prior to the C1 code word of the same symbol. operating the Q1650 encoder function in serial data mode this is the sequence in which code words are output on the C0 signal.

#### Code Rate 1/3 Mode Operation

Operation with code rate  $\frac{1}{3}$  is similar in function to the rate 1/2 operation just described, except that three code words are generated by the encoder for each input information bit. When operating with code rate 1/3 and parallel data input mode at the decoder, the synchronization circuit does not affect the data. Data input to the decoder in this mode must be in the correct sequence and input on the correct R0, R1, and R2 inputs. However, the on-chip differential decoder can be enabled to offset the inversion of the data which may occur in such systems as a BPSK transmission network. When operating with rate 1/3 coding in serial data mode the decoder will group the input code words in a triplet grouping. If the SYNCCHNG signal is used to correct this code word grouping the decoder will adjust the grouping by stopping the serial-to-parallel conversion process internally for a single period of DECINCLK. In this mode there are three possible synchronization states. It is required that the input sequence to the decoder be the R0, R1, and finally the R2 input code word for each given symbol. This is the order in which the serialized code words C0, C1, and C2 are output from the encoder when operating in serial data mode.

# Code Rate 3/4 or 7/8 Mode Operation (Internal Puncture Mode)

Operation with the internal puncture code rates is similar to rate ½ operation except that the possible synchronization states increase due to the ambiguity with the pattern of the puncture process. When operating with either code rate 3/4 or 7/8 with automatic synchronization enabled, the decoder first performs either the phase ambiguity resolution process (when operating in parallel data mode) or the code word pairing process (when operating in serial input data mode). Next, the paired code words are processed by a "null"-symbol insertion circuit that must correctly insert the null symbols in the place where code words were erased at the encoder. When operating with code rate 3/4 this additional synchronization process adds a factor of two to the number of possibly correct synchronization states for a total of four possibly correct states. When operating with code rate <sup>7</sup>/<sub>8</sub>, the puncture pattern can have one of four possible states; thus eight synchronization states are possible. The Q1650 decoder synchronization circuit attempts each possible state

Table 1. Q1650 Modes of Operation

|      |      |        |     |             | ·   | C    | ontrol Reg                            | ister Bits | ·        |        | See Notes N | lext Pa |

|------|------|--------|-----|-------------|-----|------|---------------------------------------|------------|----------|--------|-------------|---------|

| Code | Data | Modu-  | R   | R           | R   | R    | SERIAL                                |            | PHASE    | SWAP   | Int Sync    | Erase   |

| Rate | Mode | lation | 1/2 | 1/3         | 3/4 | 7/8  | ENABLE                                | OQPSK      | SYNC     | ERASE  | Method      | Bit     |

|      | l    |        |     | L           |     |      |                                       |            |          |        | <u></u>     | Sync    |

| 4.0  |      | 22014  |     |             |     |      |                                       |            |          |        |             | ,       |

| 1/2  | Ser  | BPSK   | 1   | 0           | 0   | 0    | 1                                     |            |          | 0      | 1           | N/A     |

| 1/2  | Par  | QPSK   | 1   | 0           |     | _    |                                       |            |          | _      |             | · ·     |

| 1/2  | Гаі  | QF3K   |     | 0           | 0   | 0    | 0<br>0                                | 0          | 0        | 0      | 2           | A       |

|      |      |        |     | 0           | 0   | 0    | 0                                     | 0          | 0<br>1   | 1<br>0 | 2<br>3      | В       |

|      |      |        | 1   | 0           | o   | 0    | 0                                     | 0          | 1        | 1      | 3           | A<br>B  |

|      |      |        | ·•  |             |     |      |                                       |            |          | I      |             |         |

| 1/2  | Par  | OQPSK  | 1   | 0           | 0   | 0    | 0                                     | 1          | 0        | 0      | 4           | Α       |

|      |      |        | 1   | 0           | 0   | 0    | 0                                     | 1          | o        | 1      | 4           | Ĉ       |

| 1 1  |      |        | 1   | 0           | 0   | 0    | 0                                     | 1          | 1        | 0      | 5           | Ā       |

|      |      |        | 1   | 0           | 0   | 0    | 0                                     | 1          | 1        | 1      | 5           | С       |

|      |      |        |     |             |     |      |                                       |            |          |        |             |         |

| 1/3  | Ser  | BPSK   | 0   | 1           | 0   | 0    | 1                                     |            | _        | 0      | 1           | N/A     |

|      | Par  |        | 0   | _1          | 0   | 0    | 0                                     |            |          | 0      | 6           | N/A     |

| F    | -    |        |     |             |     |      |                                       |            |          |        |             |         |

| 3/4  | Par  | QPSK   | 0   | 0           | 1   | 0    | 0                                     | 0          | 0        | 0      | 7           | A       |

|      |      |        | 0   | 0           | 1   | 0    | 0                                     | 0          | 0        | 1      | 7           | В       |

|      |      |        | 0   | 0           | 1   | 0    | 0                                     | 0          | 1        | 0      | 3           | A       |

|      |      |        | U   | 0           | 11  | 0    | 0                                     | 0          | 1        | 1      | 3           | В       |

| 3/4  | Par  | OQPSK  | 0   | 0           | 1   | 0    | 0                                     |            | 0        | _      |             | . 1     |

| 0,7  | 1 41 |        | 0   | 0           | 1   | 0    | o l                                   | 1<br>1     | 0        | 0<br>1 | 8<br>8      | A<br>C  |

| 1 1  |      |        | ō   | ő           | 1   | ő    | ő                                     | †          | 1        | 0      | 8<br>5      | A       |

|      |      |        | ō   | ŏ           | i   | ŏ    | ő                                     | 1          |          | 1      | 5           | Ĉ       |

|      |      |        |     | ··········· |     |      | · · · · · · · · · · · · · · · · · · · | · ·        | <u> </u> | •      | <u>_</u>    |         |

| 7/8  | Par  | QPSK   | 0   | 0           | 0   | 1    | 0                                     | 0          | 0        | 0      | 7           | Α       |

|      |      |        | 0   | 0           | 0   | 1    | 0                                     | 0          | 0        | 1      | 7           | В       |

|      |      |        | 0   | 0           | 0   | 1    | 0                                     | 0          | 1        | 0      | 3           | Ā       |

|      |      |        | 0   | 0           | 0   | 1    | 0                                     | 0          | 1        | 1      | 3           | В       |

| 7.0  |      | 005011 |     |             |     | 1    |                                       |            |          |        |             |         |

| 7/8  | Par  | OQPSK  | 0   | 0           | 0   | 1    | 0                                     | 1          | 0        | 0      | 8           | Α       |

|      | l    |        | 0   | 0           | 0   | 1    | 0                                     | 1          | 0        | 1      | 8           | С       |

|      | l    | ł      | 0   | 0           | 0   | 1    | 0                                     | 1          | 1        | 0      | 5           | A       |

| L    | 1    |        | U   | U           | U   | _ 11 | 0                                     | 1          | 1        | 1      | 5           | С       |

#### **NOTES**

#### **Internal Synchronization Methods**

- 1. Shifts input grouping pattern by one code word.

- 2. Edge actuation of SYNCCHNG signal toggles between alternate decoder input mapping states:

- State 1:  $R0_N --> R0_N$ ,  $R1_{N}--> R1_N$

- State 2:  $R0_N --> R1_N /, R1_N --> R0_N$

- 3. Level activation of SYNCCHNG signal forces one of two decoder input mapping states:

State 1 (SYNCCHNG = 0):  $R0_N --> R0_N$ ,  $R1_N --> R1_N$

State 2 (SYNCCHNG = 1):  $R0N \rightarrow R1N/$ ,  $R1N \rightarrow R0N$

- 4. Edge actuation of SYNCCHNG signal toggles one of two decoder input mapping states:

- State 1:  $R0_N --> R0_N$ ,  $R1_N --> R1_N$

- State 2:  $R0_N --> R1_N /, R1_{N-1} --> R0_N$

- 5. Level actuation of SYNCCHNG signal forces one of two decoder input mapping states:

State 1 (SYNCCHNG = 0):  $R0_N --> R0_N$ ,  $R1_{N}--> R1_N$

State 2 (SYNCCHNG = 1):  $R0_N --> R1_N /, R1_{N-1} --> R0_N$

- 6. No internal synchronization control is provided; SYNCCHNG signal should be tied to logic 0.

- 7. Edge actuation of SYNCCHNG performs the same operation as synchronization method 2. In addition, the puncture code pattern is shifted by one state every other activation of SYNCCHNG.

- 8. Edge actuation of SYNCCHNG performs the same operation as synchronization method 4. In addition, the puncture code pattern is shifted by one state every other activation of SYNCCHNG.

#### **Erase Bit Synchronization**

- A. ROERASE and R1ERASE inputs follow R0 and R1 data signal synchronization methods.

- B. ROERASE and R1ERASE inputs do not follow R0 and R1 data signal synchronization methods.

- C. R0ERASE input is not affected by synchronization methods. R1ERASE is delayed by one input code word when in synchronization state 2.

in sequence. The synchronization state changes each time the SYNCCHNG input is asserted. Synchronization of the puncture pattern sequence can be explicitly controlled while in parallel data input mode. Automatic synchronization mode should be disabled by connecting SYNCCHNG (pin 14) to logic "0." The R2ERASE signal (pin 30) indicates the clock period just prior to the first code word pair of the rate  $^{3}/_{4}$  or  $^{7}/_{8}$  puncture pattern. With either code rate, the first code word pair of the sequence is the pair in which the C0 and C1 bits are from the same rate 1/2 code word pair as shown in Figure 6. The R2ERASE signal should be set to logic "1" just once after chip reset during the period of DECINCLK prior to input of the first code word pair. R2ERASE should be set to logic "0" after this initial synchronization. The first symbol pair output from the encoder is indicated by an active high state at the C2 (pin 42) output when operating in rate 3/4 or 7/8 mode.

Higher Code Rate Operation Using External Puncturing Mode

The Q1650 encoder and decoder can encode and decode punctured code rates other than the rate <sup>3</sup>/<sub>4</sub> and <sup>7</sup>/<sub>8</sub> code implemented internally. Operation with these other codes requires the use of external puncture and null-symbol insertion circuits. The Q1650 decoder function includes symbol erasure inputs for the R0, R1, and R2 code words which are used to indicate a null-symbol to the decoder. When operating with an external puncture code synchronization for both phase ambiguity effects and the puncture pattern are typically performed using external circuitry.

#### TECHNICAL SPECIFICATIONS

#### **Processor Interface**

The on-chip processor interface of the Q1650 device allows a processor to set the operational mode and monitor the internal status of the device. The interface includes an 8-bit wide data bus, a 5-bit wide address bus, and read enable, write enable, and chip select lines. This interface will operate with most major microprocessor and signal processor families without wait state logic. It can also be used to write and read data to and from the encoder and decoder functions. In this mode, the Q1650 decoder operates as a single-chip FEC peripheral to the processor system.

The Q1650 processor interface has four read registers and 21 write registers. Not all registers are required

in every operational mode.

Tables 2 and 3 show the memory maps of the read and write registers, while Tables 4 and 5 describe the functions of each register and bit in detail.

# Table 2. Q1650 Read Registers Memory Map

| ADDI | ADDRESS DATA BITS                       |            |            |                 |             |                  |            |            |                |  |  |

|------|-----------------------------------------|------------|------------|-----------------|-------------|------------------|------------|------------|----------------|--|--|

| DEC  | <u>HEX</u>                              | <u>D7</u>  | <u>D 6</u> | <u>D 5</u>      | <u>D 4</u>  | <u>D3</u>        | <u>D 2</u> | <u>D 1</u> | <u>D 0</u>     |  |  |

|      | •                                       | Decoder D  | ata Output | Register        |             |                  |            |            |                |  |  |

| 00   | 0 0                                     | Rsvd       | Rsvd       | R0EOUT/<br>EOUT | Rsvd        | R2ERR/<br>R1EOUT | R1ERR      | R0ERR      | DECDAT-<br>OUT |  |  |

|      | Encoder Data Output Register            |            |            |                 |             |                  |            |            |                |  |  |

| 0 2  | 0 2                                     | Rsvd       | Rsvd       | Rsvd            | Rsvd        | C0ACTIVE         | C2         | C1         | C0             |  |  |

|      |                                         | BER Measu  | urement LS | Byte Outp       | ut Register | •                |            |            |                |  |  |

| 03   | 0 3                                     | Bit 7 (MS) | Bit 6      | Bit 5           | Bit 4       | Bit 3            | Bit 2      | Bit 1      | Bit 0 (LS)     |  |  |

|      | BER Measurement MS Byte Output Register |            |            |                 |             |                  |            |            |                |  |  |

| 0 4  | 0 4                                     | Bit 7 (MS) | Bit 6      | Bit 5           | Bit 4       | Bit 3            | Bit 2      | Bit 1      | Bit 0 (LS)     |  |  |

Table 3. Q1650 Write Registers Memory Map

| ADD | RESS       |                      |                 |                  | DATA               | BITS              |                  |                  |                      |

|-----|------------|----------------------|-----------------|------------------|--------------------|-------------------|------------------|------------------|----------------------|

| DEC | <u>HEX</u> | <u>D 7</u>           | <u>D 6</u>      | D 5              | <u>D 4</u>         | <u>D 3</u>        | <u>D 2</u>       | <u>D 1</u>       | <u>D 0</u>           |

|     |            | Decoder D            | ata Input F     | legister 1       |                    |                   |                  |                  |                      |

| 0 0 | 0 0        | R0-<br>ERASE         | R0[2]           | R0[1]            | R0[0]              | R1-<br>ERASE      | R1[2]            | R1[1]            | R1[0]                |

| •   |            | Decoder D            | ata Input F     | legister 2       |                    |                   |                  |                  |                      |

| 0 1 | 0 1        | R2-<br>ERASE         | R2[2]           | R2[1]            | R2[0]              | Set to 0          | Set to 0         | Set to 0         | Set to 0             |

|     |            | Decoder C            | ontrol Regi     | ster 1           |                    |                   |                  |                  |                      |

| 0 2 | 0 2        | Set to 0             | Set to 0        | RATE 7/8         | RATE 1/3           | RATE 3/4          | RATE 1/2         | OQPSK            | MODE<br>SELECT       |

|     |            | Decoder C            | ontrol Regi     | ster 2           |                    |                   |                  |                  |                      |

| 03  | 0 3        | Set to 0             | DESCR<br>MODE   | DESCR<br>ENABLE  | DIFF DEC<br>ENABLE | PERIPR/<br>DIRECT | SWAP<br>ERASE    | PHASE<br>SYNC    | SMG/OBN              |

|     |            | Decoder C            | ontrol Regi     | ster 3           |                    |                   |                  |                  |                      |

| 0 4 | 0 4        | Set to 0             | Set to 0        | Set to 0         | Set to 0           | Set to 0          | S/W DEC<br>RESET | Set to 0         | FUL/SHT<br>MEM       |

|     |            | Encoder D            | ata Input I     | Register         |                    |                   |                  |                  |                      |

| 0 5 | 0 5        | Set to 0             | Set to 0        | Set to 0         | Set to 0           | Set to 0          | Set to 0         | Set to 0         | ENCDATIN             |

|     |            | Encoder C            | ontrol Regi     | ster 1           |                    |                   |                  |                  |                      |

| 06  | 0 6        | Set to 0             | Set to 0        | RATE 7/8         | RATE 1/3           | RATE 3/4          | RATE 1/2         | S/W ENC<br>RESET | SER/PAR<br>MODE      |

|     |            |                      | ontrol Regi     | ster 2           |                    |                   |                  |                  |                      |

| 07  | 0 7        | Set to 0             | SCRAMB<br>MODE  | SCRAMB<br>ENABLE | DIFF ENC<br>ENABLE | BUS/PIN<br>MODE   | Set to 0         | Set to 0         | Set to 0             |

|     |            |                      |                 |                  | out Registe        | r                 |                  |                  |                      |

| 8 0 | 8 0        | TCOUNT<br>Bit 7 (MS) | TCOUNT<br>Bit 6 | TCOUNT<br>Bit 5  | TCOUNT<br>Bit 4    | TCOUNT<br>Bit 3   | TCOUNT<br>Bit 2  | TCOUNT<br>Bit 1  | TCOUNT<br>Bit 0 (LS) |