捷多邦,专业PCB打样工厂 \_,24小时加急出货

## Quadrature Phase Modulator Transmitter Circuit

### **Preliminary Data**

#### Features

- Double-balanced mixers

- Direct modulation

- Linear modulating inputs

- Symmetrical circuitry

- Generation of orthogonal carriers without external elements, no trimming required

- 35 dB carrier rejection, 42 dB SSB rejection

- 42 dB rejection of third order products at normal drive level

- 38 dB rejection of doubled RF output frequency

- 0 dBm linear output power

5 dBm output power at 1 dB compression

- Power ON/OFF switch, low standby current

- Supply voltage range 4.4 V to 5.8 V

- LO frequency range 800 MHz to 1000 MHz

- Modulation frequency range 0 to 400 MHz

- P-DSO-16, P-DSO-20 and P-DSO-20-4 (Shrink) package

- Temperature range 25 °C to 85 °C

### Applications

- Digital mobile radio and WLAN

- GSM-, JDC-, DAMPS-systems

- Continuous phase modulation, e.g. GMSK

- Various kinds of QPSK modulation and linear QAM

- Frequency fine tuning

emiconductor Group

Image reject up and down mixer

| Туре         | Version | Ordering Code | Package                                            |

|--------------|---------|---------------|----------------------------------------------------|

| PMB 2200T    | V2.1    | Q67000-A6081  | P-DSO-20-4 (SMD)                                   |

| PMB 2200T    | V2.1    | Q67006-A6081  | P-DSO-20 Tape & Reel (SMD)                         |

| PMB 2200T-16 | V2.1    | Q67000-A6082  | P-DSO-16-3(SMD)                                    |

| PMB 2200T-16 | V2.1    | Q67006-A6082  | P-DSO-16 Tape & Reel (SMD)                         |

| PMB 22005    | V2.1    | Q67000-A6080  | P-DSO-20-4 Shrink (SMD)                            |

| PMB 2200S    | V2.1    | Q67006-A6080  | P-DSO-20-4 Shrink, Tape & Reel (SMD)               |

|              |         |               | A CONTRACT AND |

1

**Bipolar IC**

### PMB 2200

## SIEMENS

#### **Device Overview**

The PMB 2200 is part of the Siemens QPSK chip set<sup>1</sup>) which offers all the functions needed in a hand set for digital mobile radio systems. The functions implemented in this device meet the requirements introduced by the Groupe Spéciale Mobile (GSM) with an output power of 0 dBm.

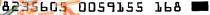

The PMB 2200 transmitter circuit performs a modulation of the phase  $\psi(t) - \omega_M t$  of the RF-carriers in the 900-MHz band. This is done by means of the base band signals

$I(t) = K_2 \sin \omega_M t$  and  $Q(t) = -K_2 \cos \omega_M t = K_2 \sin (\omega_M t - \frac{\pi}{2})$ .

$\begin{aligned} \mathsf{X}(t) &= \mathsf{K}_1 \sin \psi(t) \times \mathsf{K}_2 \sin \omega_{\mathsf{M}} t + \mathsf{K}_1 \cos \psi(t) \times \mathsf{K}_2 \cos \omega_{\mathsf{M}} t \\ &= \mathsf{K}_1 \mathsf{K}_2 \cos (\psi(t) - \omega_{\mathsf{M}} t) \rightarrow \mathsf{lower sideband} \end{aligned}$

Realisation to eq.(8) in GSM rec.05.04.Feb.88. The actual internal generated orthogonal LO carriers work in switching mode.

\*) The other GSM RF-chips are: PMB 2306, PLL PMB 2312, Prescaler

PMB 2400, GSM Receiver Circuit PMB 2401, GSM Receiver Circuit PMB 2205, Modulator for Upconversion PMB 2206, Modulator with Upconversion

The CMOS circuits for digital signal processing include: PMB 2705, GOLD - GSM One Chip Logic Device PMB 2900, GSM Baseband Codec

## 8235605 0059156 0T4 🗖

2

### Logic Symbol PMB 2200 Logic- and Analog Interfaces

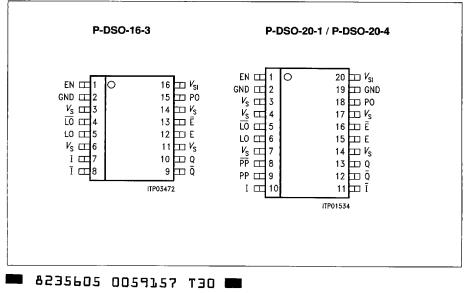

### Pin Configuration

(top view)

## PMB 2200

# SIEMENS

| Pir                      | n <b>No.</b> | Symbol          | Function                                                                                                                         |

|--------------------------|--------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------|

| P-DSO-20-1<br>P-DSO-20-4 | P-DSO-16-3   |                 |                                                                                                                                  |

| 1                        | 1            | EN              | Enable, power ON/OFF switch                                                                                                      |

| 2                        | 2            | GND             | Ground, 0 V                                                                                                                      |

| 3                        | 3            | Vs              | Supply voltage, 4.2 to 5.8 V                                                                                                     |

| 4                        |              | Vs              | Supply voltage, connected to pin 3                                                                                               |

| 5                        | 4            | LO              | Local oscillator frequency input, inverted                                                                                       |

| 6                        | 5            | LO              | Local oscillator frequency input                                                                                                 |

| 7                        | 6            | Vs              | Supply voltage, connected to pin 3                                                                                               |

| 8                        |              | PP              | Test input, inverted                                                                                                             |

| 9                        |              | PP              | Test input                                                                                                                       |

| 10                       | 7            | 1               | Modulating input I, open base                                                                                                    |

| 11                       | 8            | Ī               | Inverted modulating input I, open base                                                                                           |

| 12                       | 9            | Q               | Inverted modulating input $\overline{Q}$ , open base                                                                             |

| 13                       | 10           | Q               | Modulating input Q, open base                                                                                                    |

| 14                       | 11           | Vs              | Supply voltage, connected to pin 3                                                                                               |

| 15                       | 12           | E               | RF output, open collector                                                                                                        |

| 16                       | 13           | Ē               | Inverted RF output, open collector                                                                                               |

| 17                       | 14           | Vs              | Supply voltage, connected to pin 3                                                                                               |

| 18                       | 15           | PO              | Output emitter source resistor of output stage,<br>to be connected to GND direct or via a resistor<br>to program emitter current |

| 19                       |              | GND             | Ground, connected to pin 2                                                                                                       |

| 20                       | 16           | V <sub>SI</sub> | Test output of internal bias voltage                                                                                             |

### **Pin Definitions and Functions**

■ 8235605 0059158 977 ■

4

8235605 0059159 803

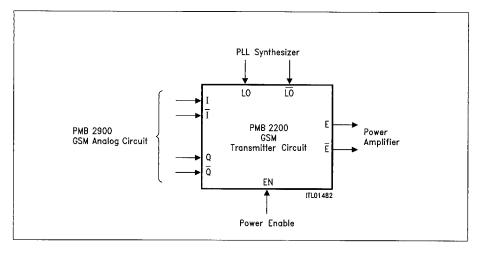

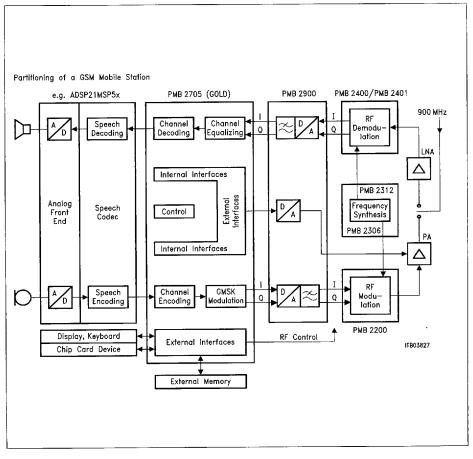

### System Integration

The basic structure of a mobile receiver built with the Siemens GSM chip set is shown below.

The PMB 2200 receives the I and Q baseband transmit signal from the GSM Channel Codec GOLD (PMB 2705) via the GSM Analog circuit (PMB 2900), which performs a D/A conversion. The baseband signal phase-modulates the RF carrier according GSM specification, while the RF amplitude remains constant.

The resulting RF signal is fed into the transmitter power amplifier following the PMB 2200.

### GSM Hand-Set with the PMB 2200

8235605 0059360 525 🛾

#### Functional Description

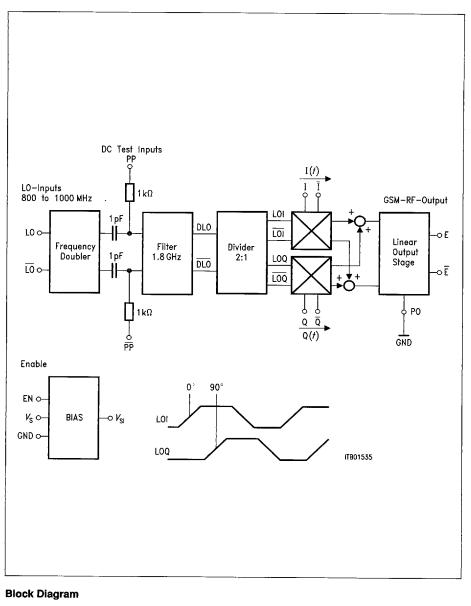

The transmission frequency  $f_0$  at the differential inputs LO,  $\overline{LO}$  is first doubled and then bandpass filtered at 2  $f_0$  about 1.8 GHz.

This frequency is the clock for a 2:1 divider. At the outputs of the two latches of this divider orthogonal carriers LOI and LOQ for the modulator are provided.

The modulator consists of two Gilbert Multipliers which are operated in switching mode by LOI and LOQ respectively. Furthermore these multipliers are driven with high linearity by the modulating signals I(t) and Q(t) up to 1.5 Vpp.

The output signals of both Gilbert cells are combined at the addition points. The sum drives a linear output stage.

An internal current source resistor of the output stage is fed to PO. This pad should be connected to GND when minimal nonlinear distortion and maximum output power is desired.

Alternatively a resistor can be inserted, e.g. 30  $\Omega$ , in order to reduce the output current by half. The pads PP,  $\overline{PP}$  and  $V_{sl}$  are used for DC-testing.

A power-down switch EN reduces the current consumption from approximately 42 mA in the active mode to less than 10  $\mu A$  in the standby mode.

### **Electrical Characteristics**

### **Absolute Maximum Ratings**

### $T_{\rm A} = -25$ to 85 °C

| Parameter                                           | Symbol             | Limit Values              | Unit |

|-----------------------------------------------------|--------------------|---------------------------|------|

| Supply voltage                                      | Vs                 | - 0.5 to 7                | V    |

| Differential input voltage (any differential input) | V <sub>Diff</sub>  | - 3 to 3                  | V    |

| Output voltage at E and E                           | VOUT               | V <sub>s</sub> – 1.6 to 7 | V    |

| Junction temperature                                | T                  | 125                       | °C   |

| Storage temperature                                 | T <sub>stg</sub>   | – 55 to 125               | °C   |

| Thermal resistance P-DSO-20                         | R <sub>th JA</sub> | 90                        | K/W  |

| Thermal resistance P-DSO-16                         | R <sub>th JA</sub> | 110                       | K/W  |

| Thermal resistance P-DSO-20-4                       | R <sub>th JA</sub> | 143                       | K/W  |

The pins E and  $\overline{E}$  have no additional internal ESD protection circuitry.

### **Operational Range**

Within the operational range the IC operates as described in the circuit description. The AC/DC characteristic limits are not guaranteed.

| Parameter                              | Symbol          | Lim     | Unit  |     |

|----------------------------------------|-----------------|---------|-------|-----|

|                                        |                 | min.    | max.  |     |

| Supply voltage                         | Vs              | 4.4     | 5.8   | V   |

| Ambient temperature                    | T <sub>A</sub>  | - 25    | 85    | °C  |

| LO frequency range                     | flo             | 800     | 1000  | MHz |

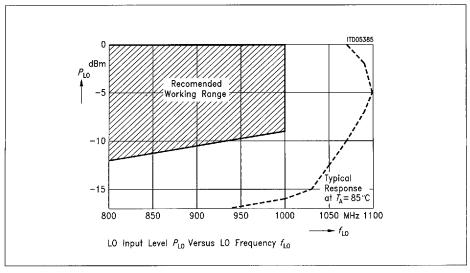

| LO input level referred to 50 $\Omega$ | P <sub>LO</sub> | see fig | ure 6 |     |

## 8235605 0059162 3T8 🖬

8

### **PMB 2200**

### **AC/DC Characteristics**

$V_{\rm S} = 5.0$  V;  $T_{\rm A} = 25$  °C;  $P_{\rm LO} = -6$  dBm (referred to test circuit)

| Parameter | Symbol | Limit Values |      | ies  | Unit | Test Condition |

|-----------|--------|--------------|------|------|------|----------------|

|           |        | min.         | typ. | max. |      |                |

### Supply Current

| Normal operation | $I_{\rm E} + I_{\rm \widetilde{E}}$ | 11.5 | 14.5 | 18 | mA | EN = H |

|------------------|-------------------------------------|------|------|----|----|--------|

| Normal operation | Is                                  | 23   | 27.5 | 33 | mA | EN = H |

| Powered down     | Is                                  |      | 0.15 | 10 | μA | EN = L |

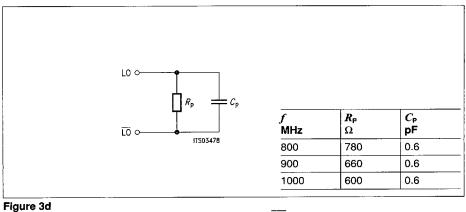

## Transmit Frequency Input LO/LO

| Internal DC voltage at the<br>input bases     | V <sub>DC</sub> | 3.3 | 3.6 | 3.8 | V  | $V_{\rm S} = 5  \rm V$ |

|-----------------------------------------------|-----------------|-----|-----|-----|----|------------------------|

| Differential AC input<br>impedance at 900 MHz | R <sub>LO</sub> |     | 660 |     | Ω  |                        |

| $C_{\rm LO}$ in parallel to $R_{\rm LO}$      | CLO             |     | 0.6 | 1   | pF |                        |

## Modulation inputs I to $\overline{I}$ and Q to $\overline{Q}$

| Input bias current of the<br>open bases at<br>I, Ī, Q, Q **        | IB               |            | 6   | 12         | μA              |                                                            |

|--------------------------------------------------------------------|------------------|------------|-----|------------|-----------------|------------------------------------------------------------|

| External DC references at I, $\overline{I}$ and Q, $\overline{Q}$  | V <sub>REF</sub> | 2.1<br>2.1 |     | 2.6<br>3.2 | V<br>V          | $V_{\rm S} = 4.5 V$<br>$V_{\rm S} = 5.5 V$                 |

| Differential input swing for<br>linear output power                | VI,Q             |            | 1.0 |            | V <sub>PP</sub> |                                                            |

| Differential input swing for 3 dB compression                      | V <sub>I,Q</sub> |            | 1.9 |            | V <sub>PP</sub> |                                                            |

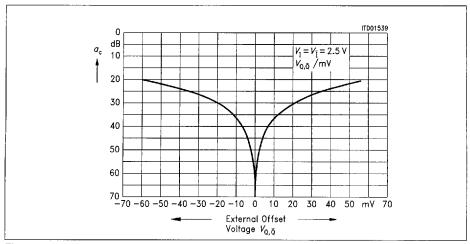

| External differential<br>input offset voltage at<br>I, Ī or Q, Q * | Voffset          |            |     | 10         | mV              | For 35 dB carrier suppression, <b>see figure 1</b>         |

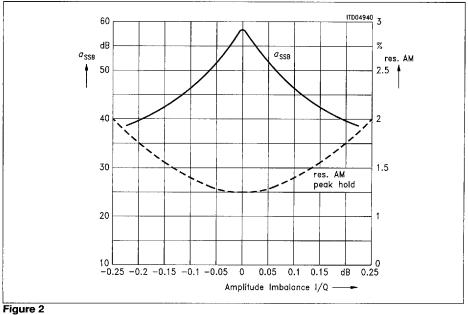

| External amplitude<br>imbalance of I, Q<br>modulation signals *    | V/VQ             |            |     | 0.15       | dB              | For single sideband<br>suppression ≥ 40 dB<br>see figure 2 |

- \* Design hint.

- \*\* To avoid offset voltages, the base input should have identical bias resistances and source impedances.

8235605 0059163 234 🔳

### AC/DC Characteristics (cont'd)

$V_{\rm S}$  = 5.0 V;  $T_{\rm A}$  = 25 °C;  $P_{\rm LO}$  = -6 dBm (referred to test circuit)

| Parameter                                                                       | Symbol         | Symbol Limit Values |      |      |     | Test Condition                                      |

|---------------------------------------------------------------------------------|----------------|---------------------|------|------|-----|-----------------------------------------------------|

|                                                                                 |                | min.                | typ. | max. | ]   |                                                     |

| Phase error of I, Q<br>modulation signals *                                     | ΔφΙ, Q         |                     |      | 1    | deg | For single sideband suppression $\ge 40 \text{ dB}$ |

| Differential input impedance at the ports I, $\overline{I}$ ; Q, $\overline{Q}$ | R <sub>1</sub> |                     | 140  |      | kΩ  | <i>f</i> = 100 kHz                                  |

| I, Q baseband input<br>frequency range: 0 Hz up to<br>the 3 dB point *          | f              |                     |      | 400  | MHz | With appropriate AC grounding of PP and PP          |

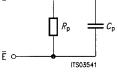

## Output E/E (open collector)

| Output power at 3 dB compression **     | POUT             |     | 6     |   | dBm        | $V_{1,Q} = 1.9 V_{PP}$                               |

|-----------------------------------------|------------------|-----|-------|---|------------|------------------------------------------------------|

| Output power at 1 dB compression **     | P <sub>OUT</sub> |     | 4.5   |   | dBm        | $V_{\rm I,Q} = 1.5 V_{\rm PP}$                       |

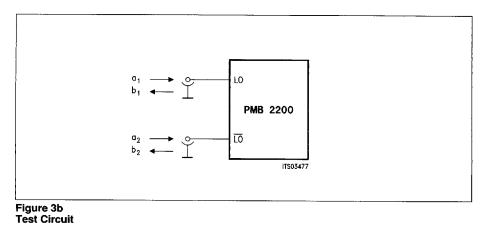

| Linear output power,<br>low spurious ** | P <sub>OUT</sub> | - 3 | 0     | 3 | dBm        | $V_{I,Q} = 1.0 V_{PP}$<br>see test circuit           |

| Rejection of third order products       |                  |     | 42    |   | dB         | $V_{I,Q} = 1.0 V_{PP}$                               |

| Carrier suppression see figure 1        | a <sub>c</sub>   | 32  | 35    |   | dB         | $V_{1,Q} = 1.0 V_{PP}$<br>no external offset voltage |

| Single sideband suppression ***         | a <sub>SSB</sub> | 40  | 42    |   | dB         | see test circuit                                     |

| Output noise floor                      | P <sub>N</sub>   |     | - 145 |   | dBm/<br>Hz | see figure 5                                         |

| Residual AM                             |                  |     | 2     |   | %          | see figure 2                                         |

\* Design hint.

\*\* Design hint for matched output.

\*\*\* 90° phase shift between I and Q

## BB 8235605 0059164 170 BB

### AC/DC Characteristics (cont'd)

$V_{\rm S}$  = 5.0 V;  $T_{\rm A}$  = 25 °C;  $P_{\rm LO}$  = - 6 dBm (referred to test circuit)

| Parameter | Symbol | Limit Values |      | Unit | Test Condition |  |

|-----------|--------|--------------|------|------|----------------|--|

|           |        | min.         | typ. | max. |                |  |

### **Power ON/OFF Switching**

| Input voltage at EN<br>Active<br>Powered down | V <sub>EN</sub><br>V <sub>EN</sub> | 4.2<br>0 | _   | V <sub>S</sub><br>0.8 | v<br>v   | EN = H<br>EN = L |

|-----------------------------------------------|------------------------------------|----------|-----|-----------------------|----------|------------------|

| Input current at EN                           | I <sub>EN</sub>                    |          | 30  | 80<br>0.1             | μΑ<br>μΑ | EN = H<br>EN = L |

| Power up/down time                            | ts                                 |          | 1.0 |                       | μs       | EN = H ↔ L       |

PMB 2200

-

**PMB 2200**

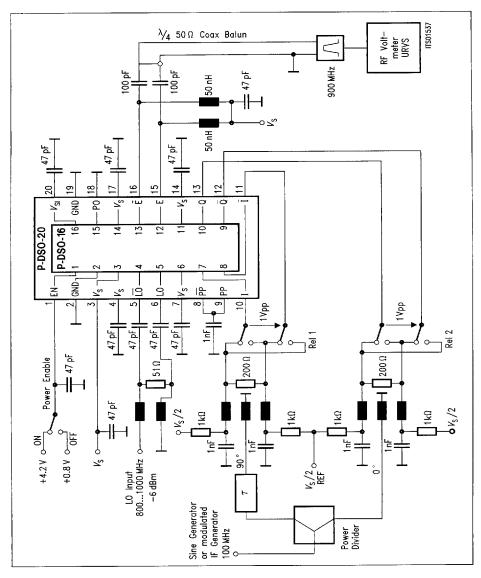

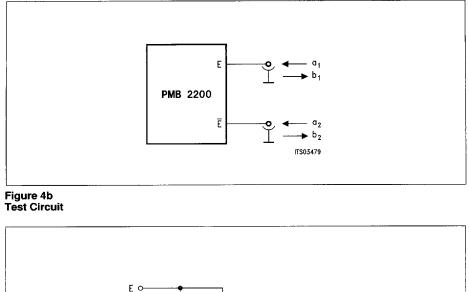

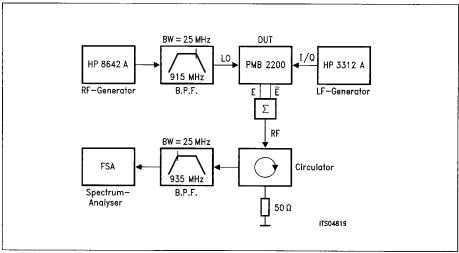

Test Circuit RF Test Circuit for AC/DC Characteristics with SSB Sine Modulation

**8**235605 0059166 T43

PMB 2200

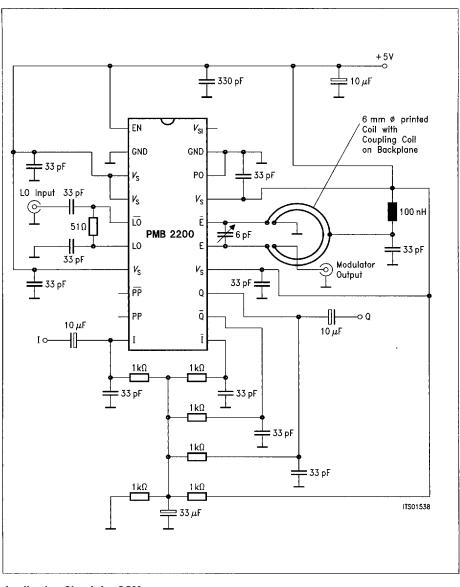

### Application Circuit for GSM

**B235605 0059167 987** Semiconductor Group 13

**PMB 2200**

Figure 1 Carrier Suppression  $a_c$  versus Offset at Q,  $\overline{Q}$

Single Sideband Suppression a<sub>SSB</sub> and Residual AM versus I/Q Amplitude Imbalance

8235605 0059168 816 8 Semiconductor Group

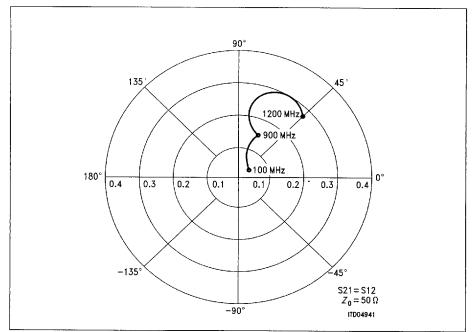

#### Figure 3a Input Impedance between $LO - \overline{LO}$ Typical S-Parameter

15

## 8235605 0059169 752 Semiconductor Group

Figure 3c Input Impedance between  $LO - \overline{LO}$

Parallel Equivalent Circuit of Input Impedance at LO, LO

8235605 0059170 474 |

Semiconductor Group

-

PMB 2200

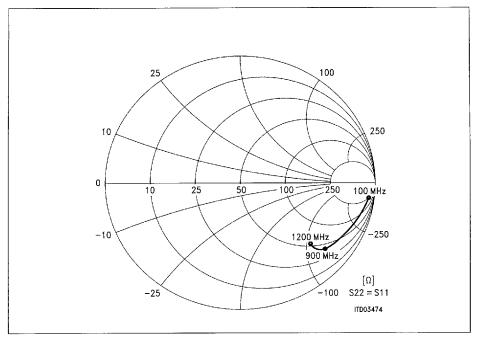

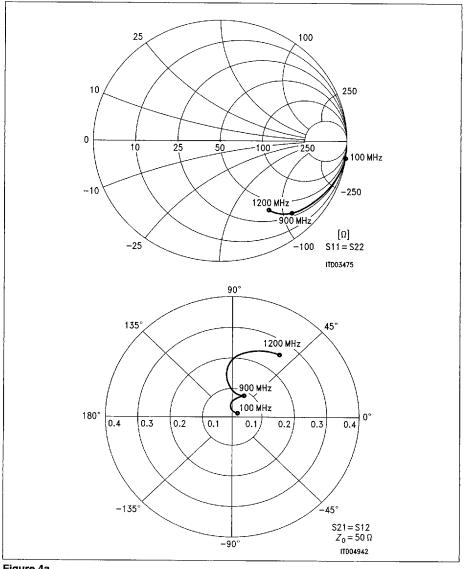

#### Figure 4a Output Impedance between E and E Typical S-Parameter 8235605 0059171 300

Semiconductor Group

\_

### PMB 2200

# SIEMENS

| f<br>MHz | <b>R</b> <sub>P</sub><br>Ω | C <sub>₽</sub><br>pF |  |

|----------|----------------------------|----------------------|--|

| 800      | 1270                       | 0.8                  |  |

| 900      | 1000                       | 0.8                  |  |

| 1000     | 870                        | 0.8                  |  |

# Figure 4c Parallel Equivalent Circuit of the Output Impedance at E, $\overline{\rm E}$

| f<br>MHz | S11  | ∠ (S11)<br>degree | S21                    | ∠ (S21)<br>degree |

|----------|------|-------------------|------------------------|-------------------|

| 800      | 0.85 | - 41.4            | 8.6 x 10 <sup>-2</sup> | 45.8              |

| 850      | 0.83 | - 44.1            | 7.9 x 10 <sup>-2</sup> | 45.7              |

| 900      | 0.81 | - 47.2            | 6.9 x 10 <sup>-2</sup> | 49.4              |

| 950      | 0.78 | - 49.8            | 6.6 x 10 <sup>-2</sup> | 67.4              |

| 1000     | 0.74 | - 51.9            | 7.7 x 10 <sup>-2</sup> | 82.1              |

### Figure 4d

## Typical S-Parameter at Output E, $\overline{E}$ $Z_0 = 50 \Omega$

8235605 0059172 247 🖿

### Figure 5 Noise Measurement Test Circuit

## 📕 8235605 0059173 183 🔳

-

Figure 6 LO Input Level  $P_{LO}$  versus LO Frequency  $f_{LO}$

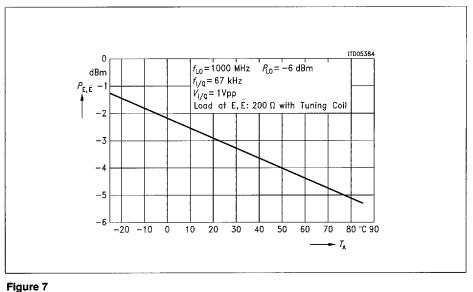

Output Power  $P_{E,\overline{E}}$  versus Temperature  $T_A$

🗰 8235605 0059174 OlT 🛛

**PMB 2200**

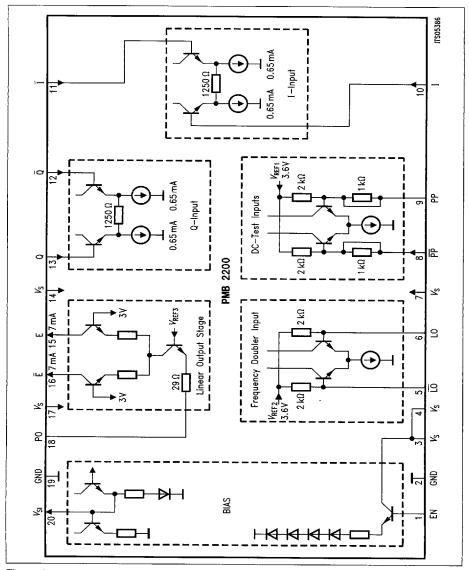

### Figure 8 PMB 2200 – Input/Output Circuitry

8235605 0059175 T56

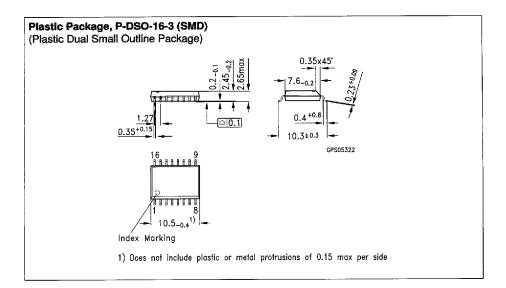

## Plastic Package, P-DSO-20-1 (SMD)

SMD = Surface Mounted Device **8**235605 0059176 992 **1** Semiconductor Group

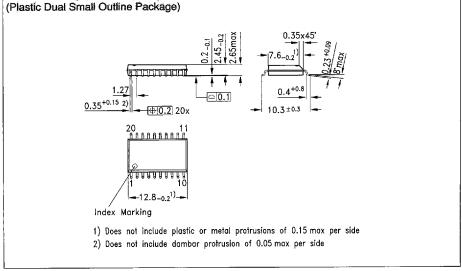

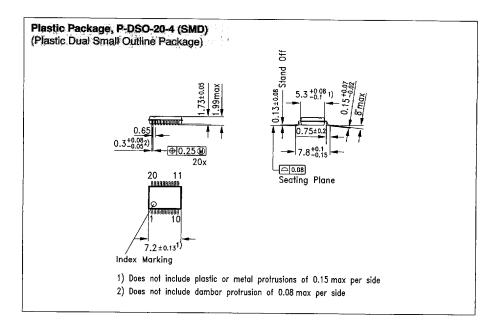

Dimensions in mm

Sorts of Packing Package outlines for tubes, trays etc. are contained in our Data Book "Package Information" SMD = Surface Mounted Device 8235605 0059177 829 B115-H6629-GI-X-7600

Dimensions in mm