# 捷多邦,专业PCB打样工厂,24小时 加急出货

LC<sup>2</sup>MOS

## **8-Bit DAC with Output Amplifier**

**AD7224**

#### 1.1 Scope.

This specification covers the detail requirements for a monolithic CMOS 8-bit, voltage output, digital-toanalog converter with output amplifier and double-buffered interface logic. No external trims are required to achieve full specified performance for the part.

#### 1.2 Part Number.

The complete part numbers per Tables 1 and 2 of this specification are as follows:

| Device | Part Number <sup>1</sup> |

|--------|--------------------------|

| -1     | AD7224T(X)/883B          |

| -2     | AD7224U(X)/883B          |

#### NOTE

<sup>1</sup>See paragraph 1.2.3 for package identifier.

#### 1.2.3 Case Outline.

See Appendix 1 of General Specification ADI-M-1000: package outline:

| ( <b>X</b> ) | Package       | Description               |

|--------------|---------------|---------------------------|

| Q            | Q-18          | 18-Pin Cerdip             |

| E            | E-20A         | 20-Contact LCC            |

| 1.3 A        | bsolute Maxim | num Ratings. $(T_A = +2)$ |

#### 5°C unless otherwise noted)

| V <sub>DD</sub> to AGND            |  |  |  |  |  |  |

|------------------------------------|--|--|--|--|--|--|

| VDB to AGND -0.3V +17V             |  |  |  |  |  |  |

| V <sub>DD</sub> to DGND            |  |  |  |  |  |  |

| V <sub>SS</sub> to AGND            |  |  |  |  |  |  |

| $V_{SS}$ to DGND                   |  |  |  |  |  |  |

| $V_{DD}$ to $V_{SS}$               |  |  |  |  |  |  |

| AGND to DGND                       |  |  |  |  |  |  |

| Digital Input Voltage to DGND      |  |  |  |  |  |  |

| $V_{REF}$ to AGND                  |  |  |  |  |  |  |

| Vout to AGND                       |  |  |  |  |  |  |

| Power Dissipation                  |  |  |  |  |  |  |

| Up to $+\hat{7}5^{\circ}$ C        |  |  |  |  |  |  |

| Derates above +75°C                |  |  |  |  |  |  |

| Operating Temperature Range        |  |  |  |  |  |  |

| Storage Temperature                |  |  |  |  |  |  |

| Lead Temperature (Soldering 10sec) |  |  |  |  |  |  |

#### 1.5 Thermal Characteristics.

Thermal Resistance  $\theta_{IC} = 35^{\circ}\text{C/W}$  for Q-18 and E-20A  $\theta_{IA} = 120^{\circ}\text{C/W}$  for Q-18 and E-20A

## **AD7224—SPECIFICATIONS**

Table 1.

| Test                                        | Symbol              | Device     | Design<br>Limit<br>T <sub>min</sub> -T <sub>max</sub> |     | Sub<br>Group<br>2, 3 | Sub<br>Group<br>4 | Test Condition <sup>1</sup>                                                                               | Units             |

|---------------------------------------------|---------------------|------------|-------------------------------------------------------|-----|----------------------|-------------------|-----------------------------------------------------------------------------------------------------------|-------------------|

| Resolution                                  | RES                 | -1,2       | 8                                                     |     |                      |                   |                                                                                                           | Bits              |

| Relative Accuracy                           | RA                  | -1<br>-2   | 1 1/2                                                 | 1   | 1 1/2                | 1/2               | $V_{DD} = +14V; V_{SS} = -5V; V_{REF} = +10V$                                                             | ± LSB max         |

| Total Unadjusted Error                      | E <sub>T</sub>      | -1         | 2                                                     | 2   | 2                    |                   | $V_{DD} = + 14V; V_{SS} = -5V; V_{REF} = +10V$                                                            | ± LSB max         |

| D                                           |                     | -2         | 1                                                     | 2   | 1                    |                   |                                                                                                           |                   |

| Differential Nonlinearity                   | DNL                 | -1,2       | 1                                                     | 1   | 1                    |                   | Guaranteed Monotonic to 8-Bits                                                                            | ± LSB max         |

| Full-Scale Error                            | AE                  | -1         | 3/2                                                   | 3/2 | 3/2                  |                   | $V_{DD} = + 14V; V_{SS} = -5V; V_{REF} = + 10V$                                                           | ± LSB max         |

|                                             |                     | - 2        | 1                                                     | 3/2 | 1                    | 1                 |                                                                                                           |                   |

| Zero Code Error                             | Azce                | -1         | 30                                                    | 30  | 30                   | ••                | $V_{DD} = 16.5V, 11.4V \text{ and } 14V; V_{SS} = -5V;$<br>$V_{REF} = V_{DD} - 4$                         | ± mV max          |

|                                             |                     | <b>– 2</b> | 20                                                    | 30  | 20                   | 20                |                                                                                                           |                   |

| Full-Scale Temp Coefficient                 | dA <sub>E</sub> /dT | -1,2       | 20                                                    |     |                      |                   | $V_{DD} = 14V \text{ to } 16.5V, V_{REF} = +10V$                                                          | ± ppm/°C<br>max   |

| Voltage Output Settling Time <sup>2</sup>   | t <sub>SL</sub>     | -1,2       | 5                                                     |     |                      |                   | Positive Full-Scale Change                                                                                | μs max            |

|                                             |                     |            | 7                                                     |     |                      |                   | Negative Full-Scale Change                                                                                |                   |

| Voltage Output Slew Rate                    | t <sub>SR</sub>     | -1,2       | 2.5                                                   |     |                      |                   |                                                                                                           | V/μs min          |

| Minimum Load Resistance                     | RLMIN               | -1,2       | 2                                                     |     |                      |                   | $V_{OUT} = +10V; V_{DD} = +14V$                                                                           | kΩ min            |

| Reference Voltage Range                     | V <sub>REF</sub>    | -1,2       | 2 to<br>(V <sub>DD</sub> - 4)                         |     |                      |                   |                                                                                                           | V min to<br>V max |

| Reference Input Resistance                  | R <sub>I</sub>      | -1,2       | 8                                                     | 8   | 8                    |                   | V <sub>DD</sub> = 14V                                                                                     | kΩ min            |

| Reference Input Capacitance                 | Cı                  | -1,2       | 100                                                   |     |                      |                   | Occurs When DAC Is Loaded with All 1's                                                                    | pF min            |

| Digital Input High Voltage                  | V <sub>IH</sub>     | -1,2       | 2.4                                                   | 2.4 | 2.4                  |                   | $V_{DD} = 11.4V; V_{REF} = V_{DD} - 4$                                                                    | V min             |

| Digital Input Low Voltage                   | $V_{1L}$            | -1,2       | 0.8                                                   | 0.8 | 0.8                  |                   | $V_{DD} = 11.4V; V_{REF} = V_{DD} + 4$                                                                    | V max             |

| Digital Input Leakage Current               | I <sub>IN</sub>     | -1,2       | 1                                                     | 1   | 1                    |                   | $V_{IN} = 0V \text{ or } V_{DD}; V_{DD} = 11.4V$                                                          | ± μA max          |

| Digital Input Capacitance                   | Cı                  | -1,2       | 8                                                     |     |                      |                   |                                                                                                           | pF max            |

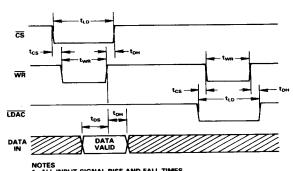

| Chip Select/Load DAC Pulse Width            | $t_{LD}$            | -1,2       | 200                                                   |     |                      |                   |                                                                                                           | ns min            |

| Write/Reset Pulse Width                     | twr                 | -1,2       | 200                                                   |     |                      |                   |                                                                                                           | ns min            |

| Chip Select/Load DAC to Write<br>Setup Time | t <sub>CS</sub>     | - 1, 2     | 0                                                     |     |                      |                   |                                                                                                           | ns min            |

| Chip Select/Load DAC to Write<br>HoldTime   | <sup>t</sup> CH     | -1,2       | 0                                                     |     |                      |                   |                                                                                                           | ns min            |

| Data Valid to Write Setup Time              | t <sub>DS</sub>     | -1,2       | 100                                                   |     |                      |                   |                                                                                                           | ns min            |

| Data Valid to Write Hold Time               | t <sub>DH</sub>     | -1,2       | 10                                                    |     |                      |                   |                                                                                                           | ns min            |

| Power Supply Voltage Range                  | $V_{DD}$            | -1,2       | 11.4                                                  |     |                      |                   | For Specified Performance                                                                                 | + V min           |

|                                             |                     |            | 16.5                                                  |     |                      |                   |                                                                                                           | + V max           |

|                                             | Vs                  | -1,2       | 4.5                                                   |     |                      |                   | For Specified Performance                                                                                 | – V min           |

|                                             |                     |            | 5.5                                                   | ]   |                      |                   | ·                                                                                                         | - V max           |

| Power Supply Current                        | I <sub>DD</sub>     | -1,2       | 6                                                     | 4   | 6                    |                   | Output Unloaded: $V_{IN} = V_{IL}$ or $V_{IH}$<br>$V_{DD} = 16.5V$ ; $V_{SS} = -5.5V$ ; $V_{REF} = 12.5V$ | mA max            |

|                                             | Iss                 | -1,2       | 5                                                     | 3   | 5                    |                   |                                                                                                           |                   |

NOTE: DUAL SUPPLY OPERATION  $^{1}V_{DD} = +11.4V$  to 16.5V;  $V_{SS} = -5V \pm 10\%$ ; AGND = DGND = 0V;  $V_{REF} = +2V$  to  $(V_{DD} - 4V)$  unless otherwise stated.  $^{2}V_{REF} = +10V$ ; settling time to  $\pm$  1/2LSB.

Table 2.

| Test                                        | Symbol          | Device | Design<br>Limit<br>T <sub>min</sub> -T <sub>max</sub> | Sub<br>Group<br>1 | Sub<br>Group<br>2,3 | Sub<br>Group<br>4 | Test Condition <sup>1</sup>                                          | Units     |

|---------------------------------------------|-----------------|--------|-------------------------------------------------------|-------------------|---------------------|-------------------|----------------------------------------------------------------------|-----------|

| Resolution                                  | RES             | -1,2   | 8                                                     |                   |                     |                   |                                                                      | Bits      |

| Total Unadjusted Error                      | ET              | -1,2   | 2                                                     | 2                 | 2                   |                   | V <sub>DD</sub> = +14V                                               | ± LSB max |

| Differential Nonlinearity                   | DNL             | -1,2   | 1                                                     | 1                 | 1                   |                   | V <sub>DD</sub> = + 14V;<br>Guaranteed Monotonic to 8-Bits           | ± LSB max |

| Voltage Output Settling Time <sup>2</sup>   | t <sub>SL</sub> | -1,2   | 5                                                     |                   |                     |                   | Positive Full-Scale Change                                           | μs max    |

|                                             |                 |        | 20                                                    |                   |                     |                   | Negative Full-Scale Change                                           |           |

| Voltage Output Slew Rate                    | t <sub>SR</sub> | -1,2   | 2                                                     |                   |                     |                   |                                                                      | V/μs min  |

| Minimum Load Resistance                     | RLMIN           | -1,2   | 2                                                     | 2                 | 2                   |                   | $V_{OUT} = +10V; V_{DD} = +15V$                                      | kΩ min    |

| Reference Input Resistance                  | Rt              | -1,2   | 8                                                     |                   |                     |                   | V <sub>DD</sub> = 14.25V                                             | kΩ min    |

| Reference Input Capacitance                 | Cı              | -1,2   | 100                                                   |                   |                     |                   | Occurs When DAC Is Loaded with All 1's                               | pF max    |

| Digital Input High Voltage                  | VIH             | -1,2   | 2.4                                                   | 2.4               | 2.4                 |                   | $V_{DD} = 14.25V$                                                    | V min     |

| Digital Input Low Voltage                   | VIL             | -1,2   | 0.8                                                   | 0.8               | 0.8                 |                   | $V_{DD} = 14.25V$                                                    | V max     |

| Digital Input Leakage Current               | I <sub>IN</sub> | -1,2   | 1                                                     |                   |                     |                   | $V_{IN} = 0V \text{ or } V_{DD}; V_{DD} = 14.25V$                    | ± μA max  |

| Digital Input Capacitance                   | Cı              | -1,2   | 8                                                     |                   |                     |                   |                                                                      | pF max    |

| Chip Select/Load DAC Pulse Width            | t <sub>LD</sub> | -1,2   | 200                                                   |                   | 1                   |                   |                                                                      | ns min    |

| Write/Reset Pulse Width                     | twr.            | -1,2   | 200                                                   |                   |                     |                   |                                                                      | ns min    |

| Chip Select/Load DAC to Write<br>Setup Time | tcs             | -1,2   | 0                                                     |                   |                     |                   |                                                                      | ns min    |

| Chip Select/Load DAC to Write<br>HoldTime   | t <sub>СН</sub> | -1,2   | 0                                                     |                   |                     |                   |                                                                      | ns min    |

| Data Valid to Write Setup Time              | t <sub>DS</sub> | -1,2   | 100                                                   |                   |                     |                   |                                                                      | ns min    |

| Data Valid to Write Hold Time               | t <sub>DH</sub> | -1,2   | 10                                                    |                   |                     |                   |                                                                      | ns min    |

| Power Supply Voltage Range                  | $V_{DD}$        | -1,2   | 14.25                                                 |                   |                     |                   | For Specified Performance                                            | + V min   |

|                                             |                 |        | 15.75                                                 |                   |                     |                   |                                                                      | + V max   |

| Power Supply Current                        | I <sub>DD</sub> | -1,2   | 6                                                     |                   |                     |                   | Outputs Unloaded; $V_{IN} = V_{IL}$ or $V_{IH}$<br>$V_{DD} = 15.75V$ | mA max    |

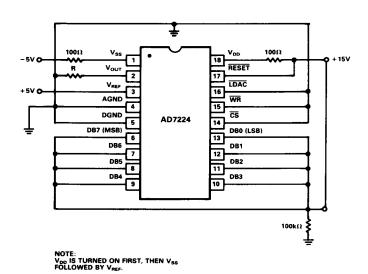

NOTE: SINGLE SUPPLY OPERATION  $^1V_{DD}=+15V\pm5\%;V_{55}=AGND=DGND=0V;V_{REF}=+10V$  unless otherwise stated.  $^2Settling time to \pm 1/2LSB$ .

### **AD7224**

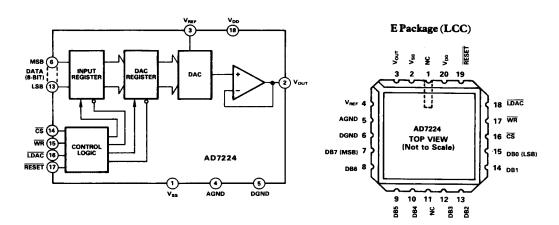

#### 3.2.1 Functional Block Diagram and Terminal Assignments.

#### 3.2.4 Microcircuit Technology Group.

This microcircuit is covered by technology group (80).

#### 4.2.1 Life Test/Burn-In Circuit.

Steady state life test is per MIL-STD-883 Method 1005. Burn-in is per MIL-STD-883 Method 1015 test condition (B).

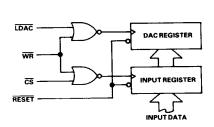

Table 3. AD7224 Truth Table

| RESE     | T LDAC | WR       | <del>CS</del> | Function                                                              |

|----------|--------|----------|---------------|-----------------------------------------------------------------------|

| Н        | L      | L        | L             | Both Registers are Transparent                                        |

| H        | x      | Н        | x             | Both Registers are Latched                                            |

| Н        | н      | X        | H             | Both Registers are Latched                                            |

| Н        | н      | L        | L             | Input Register Transparent                                            |

| Н        | н      | <b>-</b> | L             | Input Register Latched                                                |

| Н        | L      | L        | Н             | DAC Register Transparent                                              |

| н        | L      |          | H             | DAC Register Latched                                                  |

| L        | x      | X        | x             | Both Registers Loaded<br>With All Zeros                               |

| <b>-</b> | Н      | Н        | Н             | Both Register Latched With<br>All Zeros and Output Remains<br>at Zero |

| <u>.</u> | L      | L        | L<br>         | Both Registers are Transparent and Output Follows Input Data          |

H = High State, L = Low State, X = Don't Care

Figure 1. Input Control Logic

NOTES 1. ALL IMPUT SIGNAL RISE AND FALL TIMES MEASURED FROM 10% TO 90% of  $V_{DD}$ ,  $t_{\rm r}=t_{\rm r}=20$ ns over  $V_{\rm DD}$  range 2. TIMING MEASUREMENT REFERENCE LEVEL IS  $\frac{V_{\rm BMH}+V_{\rm BML}}{V_{\rm BMH}+V_{\rm BML}}$

Figure 2. Write Cycle Timing Diagram