# PF0025查询PF0025供应商

## **MOS FET Power Amplifier**

#### **FEATURES**

- Surface Mounted Small Package 1 cc, 3g with Shielded Cover

- High Efficiency 47% Typical at Actual Output Condition 1.2W

- Low Voltage Operation 6V

- Low Power Control Current 300 μA

## 捷多邦,专业PCB打样工厂,24小时

加急出货

0001-1

2

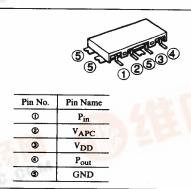

### PIN OUT

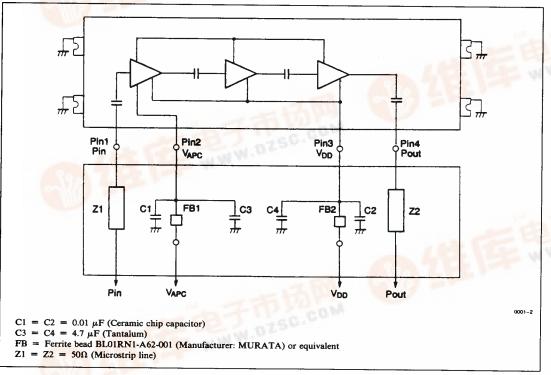

## BLOCK DIAGRAM AND EXTERNAL CIRCUIT

#### PF0025 -----

## **ABSOLUTE MAXIMUM RATINGS** (T<sub>A</sub> = 25°C)

| Item                       | Symbol              | Rating        | Unit |

|----------------------------|---------------------|---------------|------|

| Supply Voltage             | V <sub>DD</sub>     | 12            | v    |

| Supply Current             | I <sub>DD</sub>     | 2             | A    |

| APC Voltage                | V <sub>APC</sub>    | ±8            | v    |

| Input Power                | P <sub>in</sub>     | 20            | mW   |

| Operating Case Temperature | T <sub>C</sub> (op) | - 30 to + 100 | °C   |

| Storage Temperature        | T <sub>stg</sub>    | - 30 to + 100 | •C   |

#### ELECTRICAL CHARACTERISTICS (T<sub>A</sub> = 25°C)

| Item                    | Symbol               | Min                         | Max  | Unit | Test Conditions                                                                                                                                                                                                                                   |  |

|-------------------------|----------------------|-----------------------------|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Drain Cutoff Current    | IDS                  | _                           | 100  | μΑ   | $V_{DD} = 12V, V_{APC} = 0V, Rg = R_L = 50\Omega$                                                                                                                                                                                                 |  |

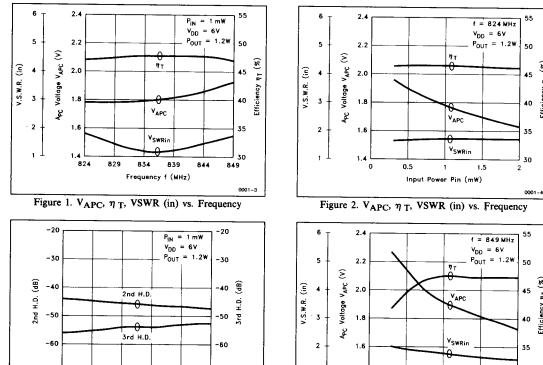

| Total Efficiency        | ητ                   | 43                          | —    | %    | f = 824  to  849  MHz,  Pin = 2  mW,<br>$V_{\text{DD}} = 6V, \text{ Rg} = \text{R}_{\text{L}} = 50\Omega,$<br>$P_{\text{out}} = 1.2W \text{ (at APC Controlled)}$                                                                                 |  |

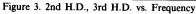

| 2nd Harmonic Distortion | 2nd H.D.             | _                           | - 30 | dB   |                                                                                                                                                                                                                                                   |  |

| 3rd Harmonic Distortion | 3rd H.D.             | —                           | - 30 | dB   |                                                                                                                                                                                                                                                   |  |

| Input VSWR              | VSWR (in)            | _                           | 3    | —    |                                                                                                                                                                                                                                                   |  |

| Output VSWR             | P <sub>out</sub> (1) | 1.6                         | _    | w    | $V_{DD} = 6V, F = 824 \text{ to } 849 \text{ MHz}, P_{in} = 2 \text{ mW},$<br>$V_{APC} = 4V, Rg = R_L = 50\Omega$                                                                                                                                 |  |

| Isolation               | P <sub>out</sub> (2) | -                           | - 40 | dBm  | $V_{DD} = 6V, f = 824 \text{ to } 849 \text{ MHz}, P_{in} = 2 \text{ mW},$<br>$V_{APC} = 0.5V, Rg = R_L = 50\Omega$                                                                                                                               |  |

| Load VSWR Tolerance     | _                    | No Degradation              |      | _    | $\begin{array}{l} V_{DD} \leq 8V, f = 824 \ \text{to} \ 849 \ \text{MHz}, P_{\text{in}} = 2 \ \text{mW}, \\ Rg = 50\Omega, V_{APC} \leq 4V, t = 20 \ \text{sec.}, \\ \text{Load VSWR} \leq 20 \ \text{All Phase Angles} \end{array}$              |  |

| Stability               |                      | No Parasitic<br>Oscillation |      |      | $ \begin{array}{l} f = 824 \mbox{ to } 849 \mbox{ MHz}, P_{in} = 2 \mbox{ mW}, \\ V_{DD} = 5.2 \mbox{ to } 7.5 \mbox{ V}, P_{out} \leq 1.6 \mbox{ W}, Zg = 50 \mbox{ \Omega}, \\ Load \mbox{ VSWR } \leq 3 \mbox{ All Phase Angles} \end{array} $ |  |

## HITACHI

46

Hitachi America, Ltd. • Hitachi Plaza • 2000 Sierra Point Pkwy. • Brisbane, CA 94005-1819 • (415) 589-8300

11 (%)

Efficiency

Efficiency n<sub>T</sub> (%)

30

0001-6

2

2

-70

1 L

1.4

0

-70

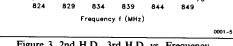

Figure 4. VAPC,  $\eta$  T, VSWR (in) vs. Input Power

1

Input Power Pin (mW)

1.5

0.5

47

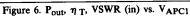

Figure 5. Pout,  $\eta$  T vs. Frequency

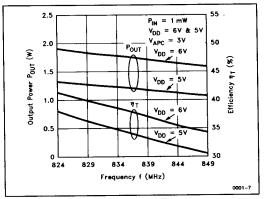

Figure 7. ID,  $\eta$  T vs. Frequency

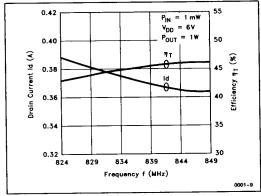

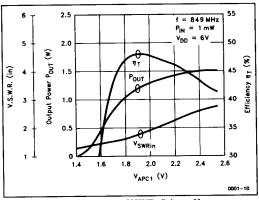

Figure 8. Pout, 7 T, VSWR (in) vs. VAPC1

## HITACHI Hitachi America, Ltd. • Hitachi Plaza • 2000 Sierra Point Pkwy. • Brisbane, CA 94005-1819 • (415) 589-8300

#### PF0025

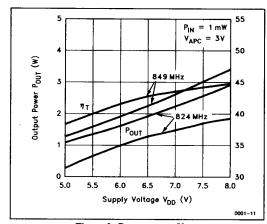

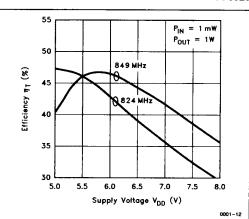

Figure 9. Pout,  $\eta_{T}$  vs. V<sub>DD</sub>

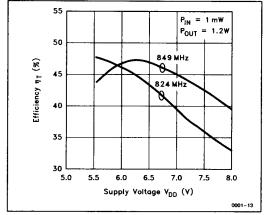

Figure 11.  $\eta$  T vs. V<sub>DD</sub>

Figure 10.  $\eta_{T}$  vs.  $V_{DD}$

PF0025 -

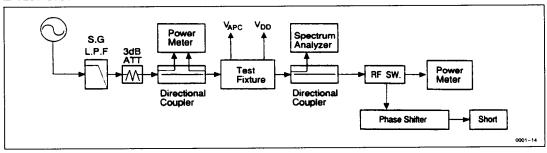

#### **TEST SYSTEM DIAGRAM**

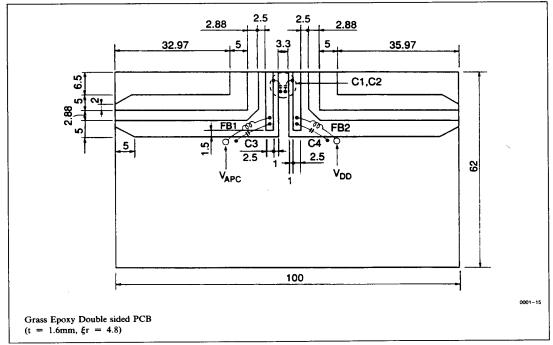

#### **TEST FIXTURE PATTERN**

(Unit: mm)

#### PF0025

#### Notes for Use

- · Unevenness and distortion at the surface to attached PF0025 should be as small as possible.

- There should be no dust between the PF0025 and the surface to which it is attached.

- Don't apply the reflow soldering process to the whole of package.

- · Don't apply the dipping solder process to the lead pins.

- To avoid the stress against the lead pins, lead pins should be soldered after the soldering of ground flange.

- Soldering temperature and time should be less than 230°C, 10 sec.

- To protect devices from electro-static damage, soldering iron, measuring equipment and human body, etc., they should be grounded.

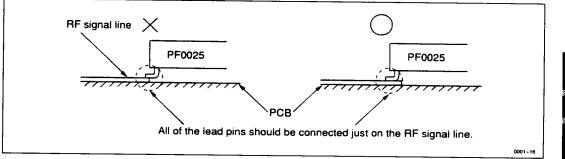

- To avoid the degradation of efficiency and output power, lead pins should not be floated from PCB, and connected just on the RF signal line. (Refer to Figure 12.)

- · Recommendation to decrease the thermal resistance is shown below.

- 1. Arrangement of through holes under as many as possible under PF0025.

- 2. Addition of external heat sink on the metal case of PF0025.

Figure 12

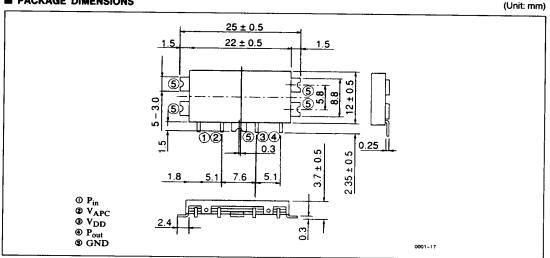

#### PACKAGE DIMENSIONS

......