时加急出货

# 85C22V10 HIGH PERFORMANCE 10-MACROCELL CMOS PLD

- High-Speed Upgrade to Bipolar 22V10/22VP10 and CMOS Equivalents

- High Performance, LSI Semi-Custom Logic Alternative to Low-End Gate Arrays, TTL, 74HC SSI and MSI Logic, and Bipolar PLDs

- t<sub>PD</sub> 10 ns, 95.2 MHz with Feedback. 100 MHz with No Feedback

- 12 Dedicated Inputs and 10 I/O Pins

- 10 Macrocells with Programmable I/O Architecture (Register/Combinatorial)

- Variable P-terms—Up to 16 per Macrocell, Selectable Output Polarity. Separate Output Enable P-term

- Global Asynchronous Clear and **Synchronous Preset P-terms**

- 1-Micron CHMOS IIIE EPROM Technology, UV-Erasable (CerDIP) or **OTP**

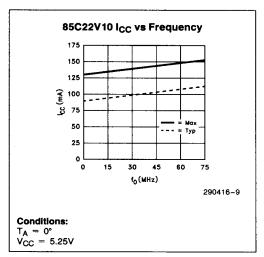

- Typical I<sub>CC</sub> = 90 mA @ 15 MHz

- Programmable Invert Clock Option

- Programmable "Security Bit" Allows **Total Protection of Proprietary Designs**

- 100% Generically Tested Logic Array

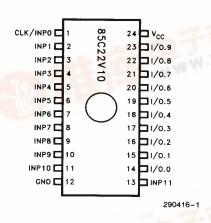

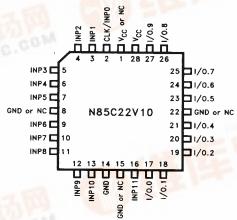

- Available in 300-mil 24-Pin CerDIP/PDIP and 28-Pin PLCC Packages

(See Packaging Spec., Order Number 240800, Package Type D, N and P)

Figure 1. Pinout Diagrams

290416-2

## INTRODUCTION

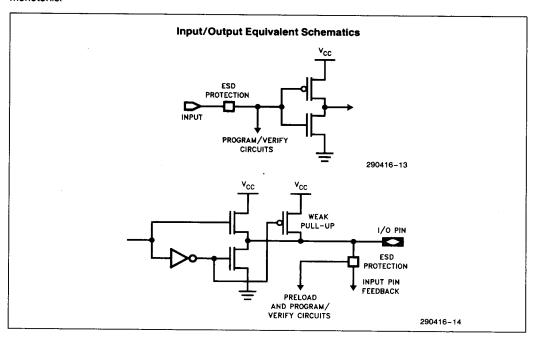

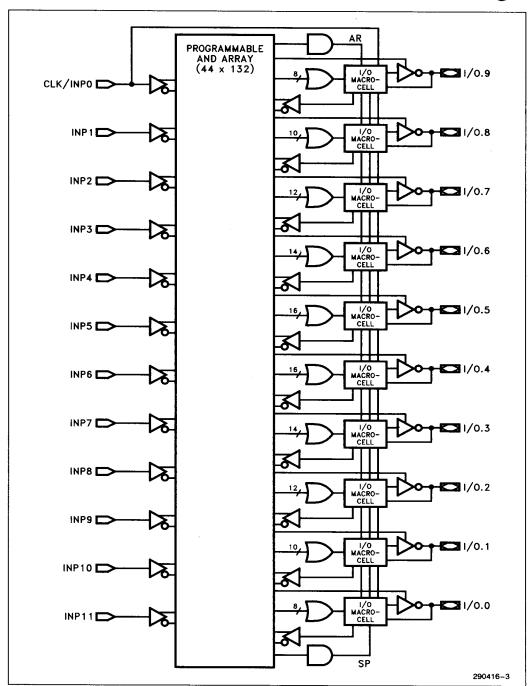

The 85C22V10 is a high-performance, high-integration, general-purpose CMOS PLD. The 85C22V10 accommodates logic functions with up to 22 inputs and 10 I/O macrocells. I/O macrocells include an average of 12 p-terms for input, with a separate p-term for output enable. Figure 2 shows the global architecture of the device.

## JEDEC AND PIN COMPATIBILITY

The 85C22V10 is 100% JEDEC-, pin- and function-compatible with the industry-standard 22V10 PLD. JEDEC files developed for 22V10 devices can be used to program the 85C22V10. For designs requiring the 85C22V10 superset features, a new JEDEC must be developed. When the N85C22V10 (28-pin PLCC) is used to replace a conventional 22V10 in an existing design socket, pins 8, 15, 22 and 1 are left as No Connects (NC). New designs can take advantage of the additional device  $V_{CC}$  and grounds these pins offer.

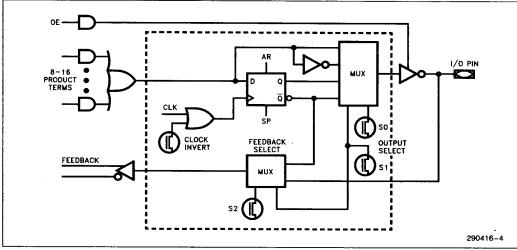

## PROGRAMMABLE MACROCELLS

In addition to the 12 dedicated input pins, the 85C22V10 contains 10 programmable macrocells. Each of the macrocells can be programmed to function as an input or as a combinatorial or registered output. Programmable output polarity and program-

mable feedback options allow the 85C22V10 to be tailored to the precise needs of the target application. Figure 3 shows the architecture of each macrocell.

## **Output Polarity**

The output polarity for each 85C22V10 macrocell is programmable. Each combinatorial or registered output can be active-high or active-low.

## **Feedback Options**

85C22V10 macrocells programmed as combinatorial outputs support pin feedback to the logic array (i.e., feedback from the I/O pin). 85C22V10 macrocells programmed as registers allow internal register feedback to the logic array. These options are supported on both the 22V10 and 22VP10 devices.

85C22V10 macrocells programmed as registers also allow feedback to the logic array from the I/O pin. This feature is also supported on 22VP10 devices.

In addition, however, the 85C22V10 provides a *superset* feature with its ability to implement a combinatorial output with registered feedback to the logic array. This feedback option allows a single 85C22V10 macrocell to implement designs that would take up two macrocells in 22V10/22VP10 devices.

## ORDERING INFORMATION

| f <sub>CNT1</sub> (MHz) | f <sub>MAX</sub> (MHz) | t <sub>PD</sub> (ns) | Order Code   | Package | Operating Range |  |  |

|-------------------------|------------------------|----------------------|--------------|---------|-----------------|--|--|

| 95.2                    | 100                    | 10                   | D85C22V10-10 | *CerDIP | Commercial      |  |  |

|                         |                        |                      | P85C22V10-10 | PDIP    | Commercial      |  |  |

|                         |                        |                      | N85C22V10-10 | PLCC ,  | Commercial      |  |  |

| 64.5                    | 83.3                   | 15                   | D85C22V10-15 | *CerDIP | Commercial      |  |  |

|                         |                        |                      | P85C22V10-15 | PDIP    | Commercial      |  |  |

|                         |                        |                      | N85C22V10-15 | PLCC    | Commercial      |  |  |

<sup>\*</sup>Only the windowed CerDIP package allows UV erase.

Figure 2. 85C22V10 Global Architecture

Figure 3. 85C22V10 Macrocell Architecture

Table 1 lists the macrocell configurations:

Table 1. 85C22V10 Macrocell Configurations

| S2 | S1 | SO | Output/Polarity            | Feedback   |

|----|----|----|----------------------------|------------|

| 0  | 0  | 0  | Registered/Active Low      | Registered |

| 0  | 0  | 1  | Registered/Active High     | Registered |

| 0  | 1  | 0  | Combinatorial/Active Low   | Pin        |

| 0  | 1  | 1  | Combinatorial/Active High  | Pin        |

| 1  | 0  | 0  | **Registered/Active Low    | Pin        |

| 1  | 0  | 1  | **Registered/Active High   | Pin        |

| 1  | 1  | 0  | *Combinatorial/Active Low  | Registered |

| 1  | 1  | 1  | *Combinatorial/Active High | Registered |

<sup>\*</sup>Not available on the 22V10 or 22VP10.

## **Clock Invert**

A clock invert option for each macrocell allows macrocell registers to be independently clocked on the rising or falling edge of the global clock. This *superset* feature allows the 85C22V10 to implement designs that could not be implemented in a 22V10/22VP10 device.

## **Register Preset/Reset**

85C22V10 macrocell registers can be preset or reset using global preset and reset p-terms. Register preset is synchronous and must meet the specified setup time to the clock signal. Register reset is asynchronous and has no setup requirement to the clock. Preset and reset set or reset the register. Output polarity is selected separately.

## **Programmable Output Enable**

Each macrocell contains an output buffer that can place the respective output in a high-impedance state (three-state). The output buffer is controlled by a single p-term per macrocell in the logic array and is asynchronous.

#### **POWER-ON CHARACTERISTICS**

85C22V10 inputs and outputs begin responding 1  $\mu$ s (max.) after V<sub>CC</sub> power-up (V<sub>CC</sub> = 4.75V) or after a power-loss/power-up sequence. All macrocells programmed as registers are set to a logic low.

#### **ERASURE CHARACTERISTICS**

Erase time for the 85C22V10 is  $2\frac{1}{2}$  hours at 12,000  $\mu$ W/cm<sup>2</sup> with a 2537Å lamp.

Erasure begins upon exposure to light with wavelengths shorter than approximately 4000Å. Sunight and certain types of fluorescent lamps have wavelengths in the 3000Å to 4000Å range. Erase data indicates that constant exposure to room level fluorescent lighting will erase the device in approximately six years. It would take approximately two weeks of constant exposure to direct sunlight to erase the device.

<sup>\*\*</sup>Not available on the 22V10.

## PROGRAMMING CHARACTERISTICS

Prior to programming or after erasure, all EPROM logic array cells are in the "connected" state. The macrocells by default are configured for registered output, active-low operation with registered feedback.

## Intelligent Programming Alogrithm

The 85C22V10 supports the Intelligent Programming Algorithm, a fast, reliable algorithm for programming many types of Intel programmable devices.

## PROCESS TECHNOLOGY

The 85C22V10 is fabricated on Intel's CHMOS EPROM process. Over 20 million devices (including EPROMs and Microcontrollers) have been fabricated on this process.

## **TESTABILITY**

The 85C22V10 is completely tested at the factory. Unlike fuse-based PLDs, which have one-time programmable fuse links that limit testing to small-scale sampling, each EPROM cell in the 85C22V10 is tested and erased prior to shipment.

## REGISTER PRELOAD

85C22V10 macrocell registers can be preloaded with any pattern to allow testing of all possible logic states. Information on register preload for test purposes is available from Intel.

## **SECURITY**

A single programmable bit, called the security bit or verify protect bit, controls access to the data programmed into the device. Once this security bit is set, the design cannot be copied. The security bit is cleared via UV-erasure along with device contents.

Since data in the device is stored in EPROM cells, the contents of the device cannot be read even with microscopic examination, providing an additional level of design security not available with fuse-based devices.

## **DEVELOPMENT SOFTWARE**

The 85C22V10 is supported by Intel's PLDshell Plus software and third-party development tools. Since it is JEDEC compatible with other manufacturer's 22V10/22VP10 devices, it is supported on all design tools that support the 22V10/22VP10.

Full logic compilation and functional simulation for the 85C22V10 is supported by PLDshell Plus software.

PLDshell Plus design software is Intel's new, userfriendly design tool for µPLD design. PLDshell Plus allows users to incorporate their preferred text editor, programming software, and additional design tools into an easy-to-use, menued design environment that includes Intel's PLDasm logic compiler and simulation software along with disassembly. conversion, and translation utilities. The PLDasm compiler and simulator software accepts industrystandard PDS source files that express designs as Boolean equations, truth tables, or state machines. On-line help, datasheet briefs, technical notes, and error message information, along with waveform viewing/printing capability make the design task as easy as possible. PLDshell Plus software is available from Intel Literature channels or from your local Intel sales representative, order #468810.

Tools that support schematic capture and timing simulation for the 85C22V10 are available. Support under iPLS II is still available. Please refer to the "Development Tools" section of the Programmable Logic handbook.

## **ABSOLUTE MAXIMUM RATINGS\***

$$\begin{split} & \text{Supply Voltage } (V_{CC})^{(1)} \dots -2.0 \text{V to } +7.0 \text{V} \\ & \text{Programming Supply} \\ & \text{Voltage } (V_{PP})^{(1)} \dots -2.0 \text{V to } +13.5 \text{V} \\ & \text{D.C. Input Voltage } (V_I)^{(1, \, 2)} \dots -0.5 \text{V to } V_{CC} +0.5 \text{V} \\ & \text{Storage Temperature } (T_{stg}) \dots -65^{\circ}\text{C to } +150^{\circ}\text{C} \\ & \text{Ambient Temperature } (T_A)^{(3)} \dots -10^{\circ}\text{C to } +85^{\circ}\text{C} \end{split}$$

NOTICE: This is a production data sheet. The specifications are subject to change without notice.

\*WARNING: Stressing the device beyond the "Absolute Maximum Ratings" may cause permanent damage. These are stress ratings only. Operation beyond the "Operating Conditions" is not recommended and extended exposure beyond the "Operating Conditions" may affect device reliability.

## RECOMMENDED OPERATING CONDITIONS

| Symbol          | Parameter             | Min  | Max             | Units |

|-----------------|-----------------------|------|-----------------|-------|

| V <sub>CC</sub> | Supply Voltage        | 4.75 | 5.25            | V     |

| V <sub>IN</sub> | Input Voltage         | 0    | V <sub>CC</sub> | v     |

| Vo              | Output Voltage        | 0    | V <sub>CC</sub> | V     |

| TA              | Operating Temperature | 0    | +70             | °C    |

| t <sub>R</sub>  | Input Rise Time       |      | 5               | ns    |

| t <sub>F</sub>  | Input Fall Time       |      | 5               | ns    |

# **D.C. CHARACTERISTICS** $(T_A = 0^{\circ}C \text{ to } + 70^{\circ}C, V_{CC} = 5.0V + 5\%)$

| Symbol              | Parameter                                                     | Min            | Тур | Max                   | Units | Test Conditions                                                                                                                             |

|---------------------|---------------------------------------------------------------|----------------|-----|-----------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>IH</sub> (4) | High Level Input Voltage                                      | 2.0            |     | V <sub>CC</sub> + 0.3 | ٧     |                                                                                                                                             |

| V <sub>IL</sub> (4) | Low Level Input Voltage                                       | -0.3           |     | 0.8                   | V     |                                                                                                                                             |

| V <sub>OH</sub>     | TTL High Output Voltage                                       | 2.4            |     |                       | V     | $I_O = -4$ mA D.C., $V_{CC} = Min$                                                                                                          |

|                     | CMOS High Output Voltage                                      | $V_{CC} - 0.3$ |     |                       | V     | $I_O = -100 \text{ pH}, V_{CC} = \text{Min}$                                                                                                |

| V <sub>OL</sub>     | Low Level Output Voltage                                      |                |     | 0.45                  | V     | I <sub>O</sub> = 16 mA D.C., V <sub>CC</sub> = Min                                                                                          |

| l <sub>l</sub>      | Input Leakage Current                                         |                |     | 10                    | μА    | V <sub>CC</sub> = Max., GND < V <sub>IN</sub> < V <sub>CC</sub>                                                                             |

| loz                 | Output Leakage Current                                        |                |     | 10                    | μΑ    | V <sub>CC</sub> = Max., GND < V <sub>OUT</sub> < V <sub>CC</sub>                                                                            |

| lsc <sup>(5)</sup>  | Output Short Circuit Current                                  |                |     | 120                   | mA    | V <sub>CC</sub> = Max., V <sub>OUT</sub> = 0.5V                                                                                             |

| lcc                 | Power Supply Current<br>(See I <sub>CC</sub> vs. Freq. Graph) |                | 90  | 130                   | mA    | V <sub>CC</sub> = Max., V <sub>IN</sub> = V <sub>CC</sub> or GND,<br>No Load, f <sub>IN</sub> = 15 MHz,<br>Device Prog. as a 10-Bit Counter |

#### NOTES:

- Voltages with respect to GND.

- 2. Minimum D.C. input is -0.5V. During transitions, the inputs may undershoot to -2.0V or overshoot to +7.0V for periods of less than 20 ns under no load conditions.

- 3. Under bias. Extended Temperature versions are also available.

- 4. Absolute values with respect to device GND; all over and undershoots due to system or tester noise are included.

- 5. Not more than 1 output should be tested at a time. Duration of that test should not exceed 1 second.

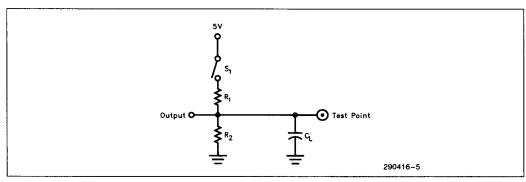

## A.C. TESTING LOAD CIRCUIT

| Specification                     |                              |       | Comn                          | nercial | Measured                                                                                                |  |              |

|-----------------------------------|------------------------------|-------|-------------------------------|---------|---------------------------------------------------------------------------------------------------------|--|--------------|

| Specification                     | S <sub>1</sub>               | CL    | R <sub>1</sub> R <sub>2</sub> |         | R <sub>1</sub> R <sub>2</sub>                                                                           |  | Output Value |

| t <sub>PD</sub> , t <sub>CO</sub> | Closed                       |       |                               |         | 1.5V                                                                                                    |  |              |

| t <sub>PZX</sub>                  | Z → H: Open<br>Z → L: Closed | 50 pF | 240Ω                          | 160Ω    | 1.5V                                                                                                    |  |              |

| t <sub>PXZ</sub>                  | H → Z: Open<br>L → Z: Closed | 5 pF  |                               |         | $\begin{array}{c} H \longrightarrow Z: V_{OH} - 0.5V \\ L \longrightarrow Z: V_{OL} + 0.5V \end{array}$ |  |              |

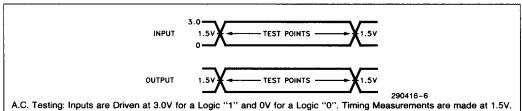

## A.C. TESTING INPUT, OUTPUT WAVEFORM

A.C. Testing: Inputs are Driven at 3.0V for a Logic "1" and 0V for a Logic "0". Timing Measurements are made at 1.5V. Outputs are measured at 1.5V. Device input rise and fall times < 3 ns.

## **CAPACITANCE** ( $T_A = 0$ °C to 70°C; $V_{CC} = 5.0V \pm 5\%$ )(6)

| Symbol           | Parameter         | Min | Тур | Max | Units | Conditions                  |

|------------------|-------------------|-----|-----|-----|-------|-----------------------------|

| C <sub>IN</sub>  | Input Capacitance |     | 5   | 8   | pF    | $V_{IN} = 0V, f = 1.0 MHz$  |

| C <sub>IO</sub>  | I/O Capacitance   |     | 6   | 8   | рF    | $V_{OUT} = 0V, f = 1.0 MHz$ |

| C <sub>CLK</sub> | CLK Capacitance   |     | 15  | 17  | pF    | $V_{OUT} = 0V, f = 1.0 MHz$ |

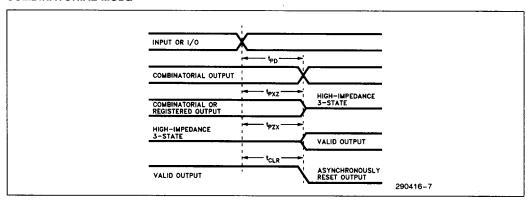

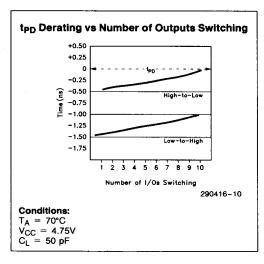

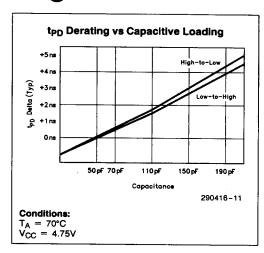

## COMBINATORIAL MODE A.C. CHARACTERISTICS

$(T_A = 0^{\circ}C \text{ to } +70^{\circ}C, V_{CC} = 5.0V \pm 5\%)$ (7)

| Symbol               | Parameter                                               | 85C22V10-10 |     |     | 85  |     |     |       |

|----------------------|---------------------------------------------------------|-------------|-----|-----|-----|-----|-----|-------|

|                      | Min Typ                                                 |             | Тур | Max | Min | Тур | Max | Units |

| t <sub>PD</sub> (8)  | Input or I/O to Output Valid—<br>w/10 Outputs Switching | 3           |     | 10  | 3   |     | 15  | ns    |

| t <sub>PZX</sub> (9) | Input or I/O to Output Enable                           | 3           |     | 10  | 3   |     | 15  | ns    |

| t <sub>PXZ</sub> (9) | Input or I/O to Output Disable                          | 3           |     | 10  | 3   |     | 15  | ns    |

| tCLR                 | Input or I/O to Asynch. Reset                           |             |     | 15  |     |     | 20  | ns    |

## NOTES:

- 6. These values are evaluated at initial characterization and whenever design modifications occur that may affect capacitance.

- 7. Typical values are at  $T_A = +25$ °C,  $V_{CC} = 5V$ .

- 8. Ten outputs switching.

- 9.  $t_{PZX}$  and  $t_{PXZ}$  are measured at  $\pm 0.5V$  from steady state voltage as driven by spec. output load.  $t_{PXZ}$  is measured with  $C_L = 5$  pF.  $Z \rightarrow H$  and  $Z \rightarrow L$  are measured at 1.5V on output.

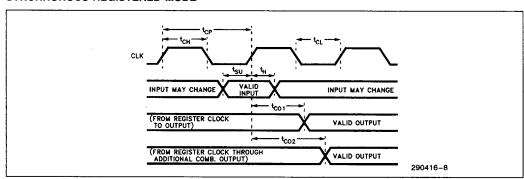

# REGISTER MODE—SYNCHRONOUS CLOCK A.C. CHARACTERISTICS

$(T_A = 0^{\circ}C \text{ to } + 70^{\circ}C, V_{CC} = 5.0V \pm 5\%)$ (7)

| Symbol                | Parameter                                                                       | 850  | C22V10 | )-10  | 850  |     |     |       |

|-----------------------|---------------------------------------------------------------------------------|------|--------|-------|------|-----|-----|-------|

| - Symbol              | - arameter                                                                      |      | Тур    | Max   | Min  | Тур | Max | Units |

| f <sub>CNT1</sub> (8) | Max. Counter Frequency 1/(t <sub>SU</sub> + t <sub>CO</sub> )—External Feedback | 95.2 | 100    | , and | 64.5 | 70  |     | MHz   |

| f <sub>CNT2</sub> (8) | Max. Counter Frequency 1/(t <sub>CNT</sub> )—Internal Feedback                  | 100  | 105    |       | 83.3 | 95  |     | MHz   |

| f <sub>MAX</sub> (8)  | Max. Frequency (Pipelined) 1/t <sub>CP</sub> —No Feedback                       | 100  | 1.10   |       | 83.3 | 95  |     | MHz   |

| t <sub>SU1</sub>      | Input or I/O Setup Time to CLK                                                  | 3.5  |        |       | 7.5  |     |     | ns    |

| t <sub>SU2</sub>      | Input or I/O Setup Time to Inverted CLK                                         | 4.5  |        |       | 8.5  |     |     | ns    |

| tsp                   | Input or I/O Setup Time to Synchronous<br>Preset                                | 4.5  |        |       | 7.5  |     |     | ns    |

| t <sub>H</sub>        | Input or I/O Hold Time from CLK                                                 | 0    |        |       | 0    |     |     | ns    |

| t <sub>CO1</sub>      | CLK to Output Valid                                                             | 3    |        | 7     | 2    |     | 8   | ns    |

| t <sub>CO1</sub>      | Inverted CLK to Output Valid                                                    | 3    |        | 7     | 2    |     | 8   | ns    |

| t <sub>CO2</sub>      | CLK to Output Valid Fed Through<br>Combinatorial Macrocell                      |      |        | 16    |      |     | 18  | ns    |

| <sup>t</sup> CNT      | Register Output Feedback to<br>Register Input—Internal Path                     |      |        | 10    |      |     | 12  | ns    |

| t <sub>CL</sub>       | CLK Low Time                                                                    | 4    | -      | -     | 5    |     |     | ns    |

| t <sub>CH</sub>       | CLK High Time                                                                   | 4    |        |       | 5    |     |     | ns    |

| t <sub>CP</sub>       | CLK Period                                                                      | 10   |        |       | 12   |     |     | ns    |

| t <sub>arw</sub>      | Asynchronous Reset Pulse Duration                                               | 4    |        |       | 5    |     |     | ns    |

| tarr                  | Asynchronous Reset to CLK ↑ Recovery Time                                       | 7    |        |       | 9    |     | -   | ns    |

#### 85C22V10

## **COMBINATORIAL MODE**

#### SYNCHRONOUS REGISTERED MODE

# intel.

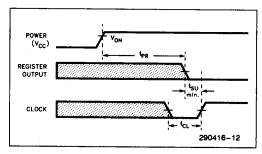

## POWER-UP RESET

Internal power-up reset circuits ensure that all flipflops will be reset to a logic 0 after the device has powered up. Because  $V_{CC}$  rise can vary significantly from one application to another,  $V_{CC}$  rise must be monotonic.

## **POWER-UP RESET**

## POWER-UP RESET CHARACTERISTICS

| Parameter<br>Symbol | Parameter<br>Description | Value        |  |  |

|---------------------|--------------------------|--------------|--|--|

| t <sub>PR</sub>     | Power-Up<br>Reset Time   | 1000 ns Max. |  |  |

| VON                 | Turn-On<br>Voltage       | 4.75V        |  |  |