# **CHMOS WINCHESTER DISK CONTRO** WITH ON-CHIP ERROR DETECTION AND CORRECTION

- Controls ST506/ST412 Interface Winchester Disk Drives

- 5 Mbit/sec Data Transfer Rate

- Compatible with All Intel and Most Other Microprocessors

- High Speed Operation

- "Zero Wait State" Operation with 8 MHz 80286 and 10 MHz 80186/188

- "One Wait State" Operation with 10 MHz 80286

- Eight High-Level Commands: Restore, Seek, Read Sector, Write Sector, Scan ID. Write Format, Compute Correction. **Set Parameter**

- **Low Power CHMOS III**

- On-Chip ECC Unit Automatically **Corrects Errors**

- 5 or 11-Bit Correction—Span Software Selectable

- Implied Seeks with Read/Write Commands

- Multiple Sector Transfer Capability

- 128, 256, 512 and 1024 Byte Sector Lengths

- Available in 40-Lead Plastic Dual In-Line

(See Packaging Spec., Order #231369)

The 82064 Winchester Disk Controller (WDC) with on-chip error detection and correction circuitry interfaces microprocessor systems to 51/4" Winchester disk drives. The 82064 is a CHMOS version of the Western Digital WD2010. It is an upgrade to the Western Digital WD1010A-05 Winchester Disk Controller, and includes on-chip ECC, support for drives with up to 2k tracks, and has an additional control signal which eliminates an external decoder.

The 82064 is fabricated on Intel's advanced CHMOS III technology and is available in 40-lead plastic DIP.

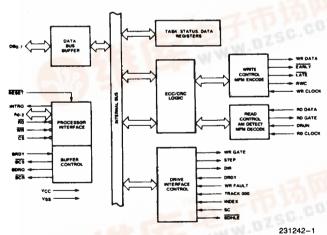

Figure 1. 82064 Block Diagram

Figure 2, 82064 Pinout

August 1990

5

Table 1. Pin Description

| Complete          | Pin   | No.            | T    | Name and Function                                                                                                                                                                                                                                                                          |

|-------------------|-------|----------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol            | DIP   | PLCC           | Туре | Name and Function                                                                                                                                                                                                                                                                          |

| BCS               | 1     | 1              | 0    | BUFFER CHIP SELECT: Output used to enable reading or writing of the external sector buffer by the 82064. When low, the host should not be able to drive the 82064 data bus, RD, or WR lines.                                                                                               |

| BCR               | 2     | 2              | 0    | BUFFER COUNTER RESET: Output that is asserted by the 82064 prior to read/write operation. This pin is asserted whenever BCS changes state. Used to reset the address counter of the buffer memory.                                                                                         |

| INTRQ             | 3     | 3              | 0    | INTERRUPT REQUEST: Interrupt generated by the 82064 upon command termination. It is reset when the STATUS register is read, or a new command is written to the COMMAND register. Optionally signifies when a data transfer is required on Read Sector commands.                            |

| SDHLE             | 4     | 4              | 0    | SDHLE is asserted when the SDH register is written by the host.                                                                                                                                                                                                                            |

| RESET             | 5     | 7              |      | RESET: Initializes the controller and clears all status flags.  Does not clear the Task Register File.                                                                                                                                                                                     |

| RD                | 6     | 8              | 1/0  | READ: Tri-state, bi-directional signal. As an input, RD controls the transfer of information from the 82064 registers to the host. RD is an output when the 82064 is reading data from the sector buffer (BCS low).                                                                        |

| WR                | 7     | 9              | 1/0  | WRITE: Tri-state, bi-directional signal. As an input, WR controls the transfer of command or task information into the 82064 registers. WR is an output when the 82064 is writing data to the sector buffer (BCS low).                                                                     |

| CS                | 8     | 10             | I    | CHIP SELECT: Enables RD and WR as inputs for access to the Task Registers. It has no effect once a disk command starts.                                                                                                                                                                    |

| A <sub>0-2</sub>  | 9-11  | 11-13          | 1    | ADDRESS: Used to select a register from the task register file.                                                                                                                                                                                                                            |

| DB <sub>0-7</sub> | 12-19 | 14-16<br>18-22 | 1/0  | DATA BUS: Tri-state, bi-directional 8-bit Data Bus with control determined by BCS. When BCS is high the microprocessor has full control of the data bus for reading and writing the Task Register File. When BCS is low the 82064 controls the data bus to transfer to or from the buffer. |

| V <sub>ss</sub>   | 20    | 23             |      | Ground                                                                                                                                                                                                                                                                                     |

| WR DATA           | 21    | 24             | 0    | WRITE DATA: Output that shifts out MFM data at a rate determined by Write Clock. Requires an external D flip-flop clocked at 10 MHz. The output has an active pullup and pulldown that can sink 4.8 mA.                                                                                    |

| LATE              | 22    | 25             | 0    | LATE: Output used to derive a delay value for write precompensation. Valid when WR GATE is high. Active on all cylinders.                                                                                                                                                                  |

| EARLY             | 23    | 26             | 0    | <b>EARLY:</b> Output used to derive a delay value for write precompensation. Valid when WR GATE is high. Active on all cylinders.                                                                                                                                                          |

Table 1. Pin Description (Continued)

|                                           | Die | 1 No. |      | . Pin Description (Continued)                                                                                                                                                                                                                                          |

|-------------------------------------------|-----|-------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol                                    | DIP | PLCC  | Туре | Name and Function                                                                                                                                                                                                                                                      |

| WR GATE                                   | 24  | 27    | 0    | WRITE GATE: High when write data is valid. WR GATE goes low if the WR FAULT input is active. This output is used by the drive to enable head write current.                                                                                                            |

| WR CLOCK                                  | 25  | 29    | ı    | <b>WRITE CLOCK:</b> Clock input used to derive the write data rate. Frequency = 5 MHz for the ST506 interface.                                                                                                                                                         |

| DIR                                       | 26  | 30    | 0    | <b>DIRECTION:</b> High level on this output tells the drive to move the head inward (increasing cylinder number). The state of this signal is determined by the 82064's internal comparison of actual cylinder location vs. desired cylinder.                          |

| STEP                                      | 27  | 31    | 0    | STEP: This signal is used to move the drive head to another cylinder at a programmable frequency. Pulse width $= 1.6 \mu s$ for a step rate of 3.2 $\mu s$ /step, and 8.4 $\mu s$ for all other step rates.                                                            |

| DRDY                                      | 28  | 32    | ı    | DRIVE READY: If DRDY from the drive goes low, the command will be terminated.                                                                                                                                                                                          |

| INDEX                                     | 29  | 33    | 1    | INDEX: Signal from the drive indicating the beginning of a track. It is used by the 82064 during formatting, and for counting retries. Index is edge triggered. Only the rising edge is valid.                                                                         |

| WR FAULT                                  | 30  | 34    | ı    | WRITE FAULT: An error input to the 82064 which indicates a fault condition at the drive. If WR FAULT from the drive goes high, the command will be terminated.                                                                                                         |

| TRACK 000                                 | 31  | 35    | ı    | TRACK ZERO: Signal from the drive which indicates that the head is at the outermost cylinder. Used to verify proper completion of a RESTORE command.                                                                                                                   |

| SC                                        | 32  | 36    |      | SEEK COMPLETE: Signal from the drive indicating to the 82064 that the drive head has settled and that reads or writes can be made. SC is edge triggered. Only the rising edge is valid.                                                                                |

| RWC                                       | 33  | 37    | 0    | REDUCED WRITE CURRENT: Signal goes high for all cylinder numbers above the value programmed in the Write Precomp Cylinder register. It is used by the precompensation logic and by the drive to reduce the effects of bit shifting.                                    |

| DRUN                                      | 34  | 38    | ı    | DATA RUN: This signal informs the 82064 when a field of all ones or all zeroes has been detected in the read data stream by an external one-shot. This indicates the beginning of an ID field. RD GATE is brought high when DRUN is sampled high for 16 clock periods. |

| buffer is ready for reading (full), or wr |     |       |      | <b>BUFFER READY:</b> Input used to signal the controller that the buffer is ready for reading (full), or writing (empty), by the host $\mu P$ . Only the rising edge indicates the condition.                                                                          |

## intel

| Symbol          | Pin No. |                | Туре  | Name and Function                                                                                                                                                                   |

|-----------------|---------|----------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>- ,</b>      | DIP     | PLCC           | .,,,, |                                                                                                                                                                                     |

| BDRQ            |         |                | 0     | BUFFER DATA REQUEST: Activated during Read or Write commands when a data transfer between the host and the 82064's sector buffer is required. Typically used as a DMA request line. |

| RD DATA         | 37      | 41             | I     | <b>READ DATA:</b> Single ended input that accepts MFM data from the drive.                                                                                                          |

| RD GATE         | 38      | 42             | 0     | READ GATE: Output that is asserted when a search for an address mark is initiated. It remains asserted until the end of the ID or data field.                                       |

| RD CLOCK        | 39      | 43             | ŀ     | READ CLOCK: Clock input derived from the external data recovery circuits.                                                                                                           |

| V <sub>CC</sub> | 40      | 44             | ı     | D.C. POWER: +5V.                                                                                                                                                                    |

| NC              | _       | 5, 6<br>17, 28 |       | No Connects                                                                                                                                                                         |

Table 1. Pin Description (Continued)

#### **FUNCTIONAL DESCRIPTION**

The Intel 82064 CHMOS Winchester Disk Controller (WDC) interfaces microprocessor systems to Winchester disk drives that use the Seagate Technology ST506/ST412 interface. The device translates parallel data from the microprocessor to a 5 Mbit/sec, MFM-encoded serial bit stream. It provides all of the drive control logic and control signals which simplify the design of external data separation and write precompensation circuitry. The 82064 is designed to interface to the host processor through an external sector buffer.

On-chip error detection algorithms include the CRC/CCITT and a 32-bit computer generated ECC polynomial. If the ECC code is selected, the 82064 provides three possible error handling techniques if an error is detected during a read operation:

- Automatically correct the data in the sector buffer, providing the host with good information.

- 2. Provide the host with the error location and pattern, allowing the host to correct the error.

- 3. Take no action other than setting the error flag.

The Intel 82064 is an enhanced version of the Western Digital WD2010 Winchester Disk Controller. The 82064 has been completely redesigned for Intel's advanced CHMOS III fabrication process, allowing Intel to offer a high quality, low power device while at the same time maintaining complete compatibility with the WD2010.

Enhancements to the basic design include:

Conversion to a CHMOS III fabrication process for low power consumption.

Improvements to the processor interface to provide high-speed "zero wait state" operation with 10 MHz 80186/188 and 8 MHz 80286. High-speed "one wait state" operation with 10 MHz 80286.

The 82064 is completely socket and software compatible with the WD2010 Winchester Disk Controller. As with the WD2010, the 82064 is also socket and software compatible with existing WD1010A-05 designs that do not include external ECC.

#### INTERNAL ARCHITECTURE

The internal architecture of the 82064 is shown in more detail in Figure 3. It is made up of seven major blocks as described below.

#### **PLA Controller**

The PLA interprets commands and provides all control functions. It is synchronized with WR CLOCK.

#### Magnitude Comparator

An 11-bit magnitude comparator is used to calculate the direction and number of steps needed to move the heads from the present to the desired cylinder position. It compares the cylinder number in the task file to the internal "present position" cylinder number.

A separate high-speed equivelance comparator is used to compare ID field bytes when searching for a sector ID field.

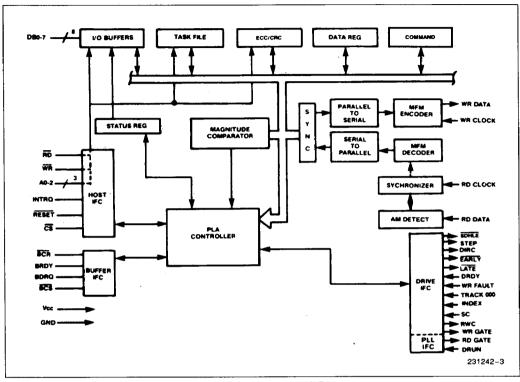

Figure 3. 82064 Detailed Block Diagram

#### **CRC and ECC Generator and Checker**

The 82064 provides two options for protecting the integrity of the data field. The data field may have either a CRC (SDH register, bit 7=0), or a 32-bit ECC (SDH register, bit 7=1) appended to it. The ID field is always protected by a CRC.

The CRC mode provides a means of verifying the accuracy of the data read from the disk, but does not attempt to correct it. The CRC generator computes and checks cyclic redundancy check characters that are written and read from the disk after ID and data fields. The polynomial used is:

$$X16 + X12 + X5 + 1$$

The CRC register is preset to all one's before computation starts.

If the CRC character generated while reading the data does not equal the one previously written an error exists. If an ID field CRC error occurs the "ID not found" bit in the error register will be set. If a

data field CRC error occurs the "ECC/CRC" bit in the error register will be set.

The ECC mode is only applicable to the data field. It provides the user with the ability to detect and correct errors in the data field automatically. The commands and registers which must be considered when ECC is used are:

- 1. SDH Register, bit 7 (CRC/ECC)

- 2. READ SECTOR Command, bit 0 (T)

- READ SECTOR and WRITE SECTOR Commands, bit 1 (L)

- 4. COMPUTE CORRECTION Command

- 5. SET PARAMETER Command

- STATUS Register, bit 2 error correction successful

- 7. STATUS Register, bit 0 error occurred

- 8. ERROR Register, bit 6 uncorrectable error

To enable the ECC mode, bit 7 of the SDH register must be set to one.

# intel

Bit 0 (T) of the READ Command controls whether or not error correction is attempted. When T=0 and an error is detected, the 82064 tries up to 10 times to correct the error. If the error is successfully corrected, bit 2 of the STATUS Register is set. The host can interrogate the status register and detect that an error occurred and was corrected. If the error was not correctable, bit 6 of the ERROR Register is set. If the correction span was set to 5 bits, the host may now execute the SET PARAMETER Command to change the correction span to 11 bits, and attempt the read again. If the error persists, the host can read the data, but it will contain errors.

When T=1 and an error is detected, no attempt is made to correct it. Bit 0 of the STATUS Register and bit 6 of the ERROR Register are set. The user now has two choices:

- 1. Ignore the error and make no attempt to correct it.

- Use the COMPUTE CORRECTION Command to determine the location and pattern of the error, and correct it within the user's program.

When the COMPUTE CORRECTION Command is implemented, it must be done before executing any command which can alter the contents of the ECC Register. The READ SECTOR, WRITE SECTOR, SCAN ID, and FORMAT Commands will alter this register and correction will be impossible. The COMPUTE CORRECTION Command rflay determine that the error is uncorrectable, at which point the error bits in the STATUS and ERROR Registers are set.

Although ECC generation starts with the first bit of the F8H byte in the data ID field, the actual ECC bytes written will be the same as if the A1H byte was included. The ECC polynomial used is:

$$X32 + X28 + X26 + X19 + X17 + X10 + X6 + X2 + 1$$

For automatic error correction, the external sector buffer must be implemented with a static RAM and counter, not with a FIFO.

The SET PARAMETER Command is used to select a 5-bit or 11-bit correction span.

When the L Bit (bit 1) of the READ SECTOR and WRITE SECTOR commands is set to one, they are referred to as READ LONG and WRITE LONG commands. For these commands, no CRC or ECC characters are generated or checked by the 82064. In effect, the data field is extended by 4 bytes which are passed to/from the sector buffer.

With proper use of the WRITE SECTOR, READ LONG, WRITE LONG, and READ SECTOR Commands, a diagnostic routine may be developed to test the accuracy of the error correction process.

#### MFM ENCODER/DECODER

Encodes and decodes MFM data to be written/read from the drive. The MFM encoder operates from WR CLOCK, a clock having a frequency equal to the bit rate. The MFM decoder operates from RD CLOCK, a bit rate clock generated by the external data separator. RD CLOCK and WR CLOCK need not be synchronous.

The MFM encoder also generates the write precompensation control signals. Depending on the bit pattern of the data, EARLY or LATE may be asserted. External circuitry uses these signals to compensate for drift caused by the influence one bit has over another. More information on the use of the EARLY and LATE control signals can be found in the section which describes the drive interface.

### Address Mark (AM) Detection

An address mark is comprised of two unique bytes preceeding both the ID field and the data field. The first byte is used for resynchronization. The second byte indicates whether it is an ID field or a data field.

The first byte, A1H, normally has a clock pattern of 0EH; however, one clock pulse has been suppressed, making it 0AH. With this pattern, the AM detector knows it is looking at an address mark. It now examines the next byte to determine if it is an ID or data field. If this byte is 111101XX or 111111XX it is an ID field. Bits 3, 1, and 0 are the high order cylinder number bits. If the second byte is F8H, it is a data field.

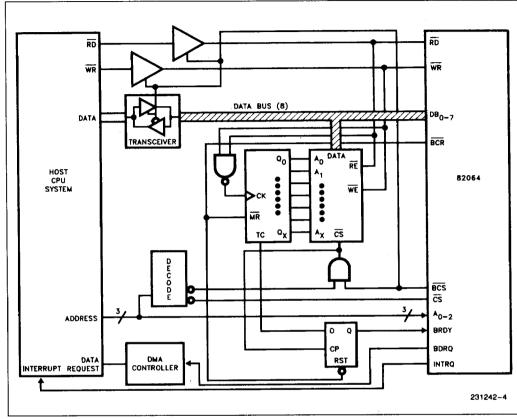

#### Host/Buffer Interface Control

The primary interface between the host processor and the 82064 is an 8-bit bi-directional bus. This bus is used to transmit and receive data for both the 82064 and the sector buffer. The sector buffer consists of a static RAM and counter. Since the 82064 makes the bus active when accessing the sector buffer, a transceiver must be used to isolate the host during this time. Figure 4 illustrates a typical interface with a sector buffer. Whenever the 82064 is not using the sector buffer, the BUFFER CHIP SELECT (BCS) is high (disabled). This allows the host access to the 82064's Task Register File and to the sector buffer. A decoder is used to generate BCS when A<sub>0-2</sub> is '000', an unused address in the 82064. A binary counter is enabled whenever RD or WR go active. The location within the sector buffer which is addressed by the counter will be accessed. The counter will be incremented by the trailing edge of the RD or WR. This allows the host to access se-

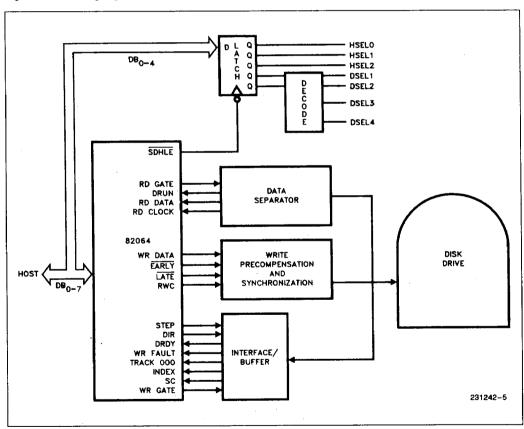

Figure 4. Host Interface Block Diagram

quential bytes within the sector buffer. The decoder also generates a  $\overline{CS}$  for the 82064 whenever  $A_{0-2}$  does not equal '000', allowing access to the 82064's internal Task Register File while keeping the sector buffer tri-stated.

intal

During a WRITE SECTOR Command, the host processor sets up data in the Task Register File and then issues the command. The 82064 asserts BUFFER COUNTER RESET (BCR) to reset the counter. It then generates a status to inform the host that it can load the sector buffer with data to be written. When the counter reaches its maximum count, the BUFFER READY (BRDY) signal is asserted by the carry out of the counter, informing the 82064 that the sector buffer is full. (BRDY is a rising edge triggered signal which will be ignored if asserted before the 82064 asserts BCR.) BCS is then asserted, discon-

necting the host through the transceivers, and the  $\overline{\text{RD}}$  and  $\overline{\text{WR}}$  lines become outputs from the 82064 to allow access to the sector buffer. When the 82064 is done using the buffer, it deasserts  $\overline{\text{BCS}}$  which again allows the host to access the local bus. The READ SECTOR command operates in a similar manner, except the buffer is loaded by the 82064 instead of the host.

Another control signal, BUFFER DATA REQUEST (BDRQ), can be used with a DMA controller to indicate that the 82064 is ready to send or receive data. When data transfer is via a programmed I/O environment, it is the responsibility of the host to interrogate the DRQ status bit to determine if the 82064 is ready (bit 3 of the status register). For further explanation, refer to the individual command descriptions and the A.C. Characteristics.

When INTRQ is asserted, the host is signaled that execution of a command has terminated (either a normal termination or an aborted command). For the READ SECTOR command, interrupts may be programmed to be asserted either at the termination of the command, or when BDRQ is asserted. INTRQ will remain active until the host reads the STATUS register to determine the cause of the termination, or writes a new command into the COMMAND register.

The 82064 asserts SDHLE whenever the SDH register is being written. This signal can be used to latch the drive and head select information in an external register for decoding. Figure 5 illustrates one method.

#### Drive Interface

The drive side of the 82064 WDC requires three sections of external logic. These are the control line buffer/receivers, data separator, and write precompensation. Figure 5 illustrates a drive interface.

The buffer/receivers condition the control lines to be driven down the cable to the drive. The control lines are typically single-ended, resistor terminated, TTL levels. The data lines to and from the drive also require buffering. This is typically done with differential RS-422 drivers. The interface specification for the drive will be found in the drive manufacturer's OEM

Figure 5. Drive Interface Block Diagram

manual. The 82064 supplies TTL compatible signals, and will interface to most buffer/driver devices.

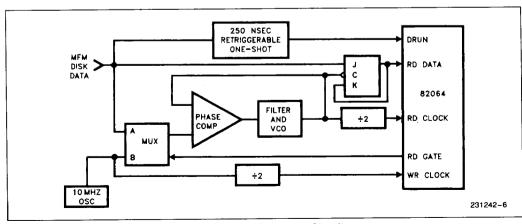

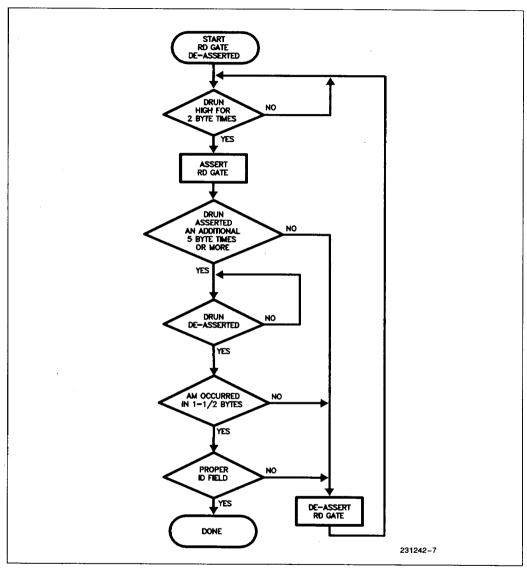

The data recovery circuits consist of a phase locked loop, data separator, and associated components. The 82064 interacts with the data separator through the DATA RUN (DRUN) and RD GATE signals. A block diagram of a typical data separator circuit is shown in Figure 6. Read data from the drive is presented to the RD DATA input of the 82064, the reference multiplexor, and a retriggerable one shot. The RD GATE output will be deasserted when the 82064 is not inspecting data. The PLL should remain locked to the reference clock.

When any READ or WRITE command is initiated and a search for an address mark begins, the DRUN input is examined. The DRUN one-shot is set for slightly longer than one bit time, allowing it to retrigger constantly on a field of all ones or all zeroes. An internal counter times out to see that DRUN is asserted for two byte times. RD GATE is asserted by the 82064, switching the data separator to lock on to the incoming data stream. If DRUN is deasserted prior to an additional seven byte times, RD GATE is deasserted and the process is repeated. RD GATE will remain asserted until a non-zero, non-address mark byte is detected. The 82064 will then deassert RD GATE for two byte times to allow the PLL to lock back on the reference clock, and start the DRUN search again. If an address mark is detected, RD GATE remains asserted and the command will continue searching for the proper ID field. This sequence is shown in the flow chart in Figure 7.

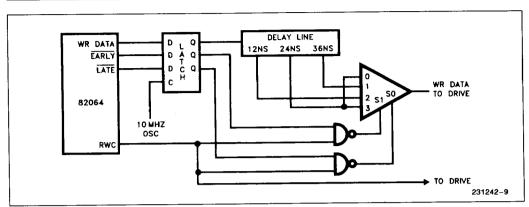

The write precompensation circuitry is designed to reduce the drift in the data caused by interaction between bits. It is divided into two parts, REDUCED WRITE CURRENT (RWC) and EARLY/LATE writing of bits. A block diagram of a typical write precompensation circuit is shown in Figure 8.

The cylinder in which the RWC line becomes active is controlled by the REDUCE WRITE CURRENT register in the Task Register File. When a cylinder is written which has a cylinder number greater than or equal to the contents of this register, the write current will be reduced. This will decrease the interaction between the bits.

Drift may also be caused by the bit pattern. With certain combinations of ones and zeroes some of the bits can drift far enough apart to be difficult to read without error. This phenomenon can be minimized by using EARLY and LATE as described below. The 82064 examines three bits, the last one written, the one being written, and the next one to be written. From this, it determines whether to assert EARLY or LATE. Since the bit leaving the 82064 has already been written, it is too late to make it early. Therefore, the external delay circuit must be as follows:

$\overline{\text{EARLY}}$  asserted and  $\overline{\text{LATE}}$  deasserted = no delay

EARLY deasserted and LATE deasserted = one unit delay (typically 12-15 ns)

EARLY deasserted and LATE assetted = two units delay (typically 24-30 ns)

EARLY and LATE are always active, and should be gated externally by the RWC signal. Figure 8 illustrates one method of using these signals.

Figure 6. Data Separator Circuit

Figure 7. PLL Control Sequence

Figure 8. Write Precompensation Circuit

#### TASK REGISTER FILE

The Task Register File is a bank of nine registers used to hold parameter information pertaining to each command, status information, and the command itself. These registers and their addresses are:

| A2  | A1 | ΑO | READ           | WRITE                |

|-----|----|----|----------------|----------------------|

| 0   | 0  | 0  | BUS TRI-STATED | BUS TRI-STATED       |

| 0   | 0  | 1  | ERROR REGISTER | REDUCE WRITE CURRENT |

| 0   | 1  | 0  | SECTOR COUNT   | SECTOR COUNT         |

| 0   | 1  | 1  | SECTOR NUMBER  | SECTOR NUMBER        |

| 1   | 0  | 0  | CYLINDER LOW   | CYLINDER LOW         |

| 1   | 0  | 1  | CYLINDER HIGH  | CYLINDER HIGH        |

| 1   | 1  | 0  | SDH            | SDH                  |

| - 1 | 1  | 1  | STATUS         | COMMAND              |

#### NOTE:

These registers are not cleared by RESET being asserted.

#### **ERROR REGISTER**

This read only register contains specific error information after the termination of a command. The bits are defined as follows:

| 7  | 7 6     |   | 4  | 3 | 2  | 1     | 0   |

|----|---------|---|----|---|----|-------|-----|

| ВВ | CRC/ECC | 0 | ID | 0 | AC | TK000 | DAM |

Bit 7 - Bad Block Detect (BB)

This bit is set when an ID field has been encountered that contains a bad block mark. It is used for bad sector mapping.

## Bit 6 - CRC/ECC Data Field Error (CRC/ECC)

When in the CRC mode (SDH register, bit 7 = 0), this bit is set when a CRC error occurs in the data field. When retries are enabled, ten more attempts are made to read the sector correctly. If none of these attempts are successful bit 0 in the STATUS register is also set. If one of the attempts is successful, the CRC/ECC error bit remains set to inform the host that a marginal condition exists; however, bit 0 in the STATUS register is not set.

When in the ECC mode (SDH register, bit 7 = 1), this bit is set when the first non-zero syndrome is detected. When retries are enabled, up to ten attempts are made to correct the error. If the error is successfully corrected, this bit remains set; however, bit 2 of the STATUS register is also set to inform the host that the error has been corrected. If the error is not correctable, the CRC/ECC error bit remains set and bit 0 of the STATUS register is also set

The data may be read even if uncorrectable errors exist.

NOTE: If the long mode (L) bit is set in the READ or WRITE command, no error checking is performed.

Bit 5 - Reserved

Not used. Forced to zero.

#### Bit 4 - ID Not Found (ID)

This bit is set to indicate that the correct cylinder, head, sector, or size parameter could not be found, or that a CRC error occurred in the ID field. This bit is set on the first failure and remains set even if the error is recovered on a retry. When recovery is unsuccessful, the Error bit (bit 0) of the STATUS register is also set.

For a SCAN ID command with retries enabled (T=0), the Error bit in the STATUS register is set after ten unsuccessful attempts have been made to find the correct ID. With retries disabled (T=1), only two attempts are made before setting the Error bit.

For a READ or WRITE command with retries enabled (T=0), ten attempts are made to find the correct ID field. If there is still an error on the tenth try, an auto-scan and auto-seek are performed. Then ten more retries are made before setting the Error bit. When retries are disabled (T=1), only two tries are made. No auto-scan or auto-seek operations are performed.

Bit 3 - Reserved

Not used. Forced to zero.

Bit 2 - Aborted Command (AC)

Command execution is aborted and this bit is set if a command was issued while DRDY is deasserted or WR FAULT is asserted. This bit will also be set if an undefined command is written to the COMMAND register; however, an implied seek will be executed.

Bit 1 - Track 000 Error (TK000)

This bit is set during the execution of a RESTORE command if the TRACK 000 pin has not gone active after the issuance of 2047 step pulses.

Bit 0 - Data Address Mark (DAM) Not Found

This bit is set during the execution of a READ SEC-TOR command if the DAM is not found following the proper sector ID.

## REDUCE WRITE CURRENT REGISTER

This register is used to define the cylinder number where the RWC output (Pin 33) is asserted.

| 7 | 6 | 5    | 4      | 3     | 2     | 1 | 0 |

|---|---|------|--------|-------|-------|---|---|

|   |   | CYLI | NDER N | UMBER | 7 ÷ 4 |   |   |

The value (00-FFH) loaded into this cylinder is internally multiplied by four to specify the actual cylinder where RWC is asserted. Thus a value of 01H will cause RWC to be asserted on cylinder 04H, 02H on cylinder 08H, ..., 9CH on cylinder 270H, 9DH on cylinder 274H, and so on. RWC will be asserted when the present cylinder is greater than or equal to four times the value of this register. For example, the ST506 interface requires precomp on cylinder 80H and above. Therefore, the REDUCE WRITE CURRENT register should be loaded with 20H.

A value of FFH causes RWC to remain deasserted, regardless of the actual cylinder number.

#### SECTOR COUNT REGISTER

This register is used to define the number of sectors that need to be transferred to the buffer during a READ MULTIPLE SECTOR or WRITE MULTIPLE SECTOR command.

| 7                 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |  |

|-------------------|---|---|---|---|---|---|---|--|--|--|--|

| NUMBER OF SECTORS |   |   |   |   |   |   |   |  |  |  |  |

The value contained in the register is decremented after each sector is transferred to/from the sector buffer. A zero represents a 256 sector transfer, a one a one sector transfer, etc. This register is a "don't care" when single sector commands are specified.

#### SECTOR NUMBER REGISTER

This register holds the sector number of the desired sector.

| 7 | 6             | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |  |  |

|---|---------------|---|---|---|---|---|---|--|--|--|--|--|

|   | SECTOR NUMBER |   |   |   |   |   |   |  |  |  |  |  |

For a multiple sector command, it specifies the first sector to be transferred. It is incremented after each sector is transferred to/from the sector buffer. The SECTOR NUMBER register may contain any value from 0 to 255.

The SECTOR NUMBER register is also used to program the Gap 1 and Gap 3 lengths to be used when formating a disk. See the WRITE FORMAT command description for further explanation.

## 5

#### CYLINDER NUMBER LOW REGISTER

This register holds the lower byte of the desired cylinder number.

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |   |

It is used with the CYLINDER NUMBER HIGH register to specify the desired cylinder number over a range of 0 to 2047.

#### CYLINDER NUMBER HIGH REGISTER

This register holds the three most significant bits of the desired cylinder number.

| ۱ | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|

|   | х | x | × | × | × | # | # | # |

The CYLINDER NUMBER LOW/HIGH register pair determine where the R/W heads are to be positioned. The host writes the desired cylinder number into these registers. Internal to the 82064 is another pair of registers that hold the present head location. When any command other than a RESTORE is executed, the internal head location registers are compared to the CYLINDER NUMBER registers to determine how many cylinders to move the heads and in what direction.

The internal head location registers are updated to equal the CYLINDER NUMBER registers after the completion of the seek.

When a RESTORE command is executed, the internal head location registers are reset to zero while DIR and STEP move the heads to track zero.

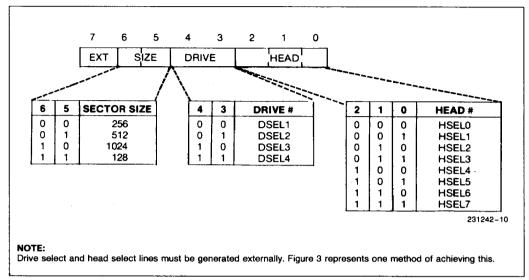

## SECTOR/DRIVE/HEAD (SDH) REGISTER

The SDH register contains the desired sector size, drive number, and head parameters. The format is shown in Figure 9. The EXT bit (bit 7) is used to select between the CRC or ECC mode. When bit 7 = 1 the ECC mode is selected for the data field. When bit 7 = 0 the CRC mode is selected.

The SDH byte written in the ID field of the disk by the FORMAT command is different than the SDH register contents. The recorded SDH byte does not have

the drive number recorded, but does have the bad block mark written. The format of the SDH byte written on the disk is:

| 7      | 6  | 5  | 4 | 3 | 2    | 1 | 0 |

|--------|----|----|---|---|------|---|---|

| BAD B. | SI | ZE | 0 | 0 | HEAD |   |   |

#### STATUS REGISTER

The status register is used to inform the host of certain events performed by the 82064, as well as reporting status from the drive control lines. Reading the STATUS register deasserts INTRQ. The format is:

| 7    | 6     | 5  | 4  | 3   | 2   | 1   | 0   |

|------|-------|----|----|-----|-----|-----|-----|

| BUSY | READY | WF | SC | DRQ | DWC | CIP | ERR |

#### Bit 7 - Busy

This bit is asserted when a command is written into the COMMAND register and, except for the READ command, is deasserted at the end of the command. When executing a READ command, Busy will be deasserted when the sector buffer is full. Commands should not be loaded into the COMMAND register when Busy is set. When the Busy bit is set, no other bits in the STATUS or ERROR registers are valid.

#### Bit 6 - Ready

This bit reflects the status of DRDY (pin 28). When this bit equals zero, the command is aborted and the status of this bit is latched.

#### Bit 5 - Write Fault (WF)

This bit reflects the status of WR FAULT (pin 30). When this bit equals one the command is aborted, INTRQ is asserted, and the status of this bit is latched.

#### Bit 4 - Seek Complete (SC)

This bit reflects the status of SC (pin 32). When a seek or implied seek has been initiated by a command, execution of the command pauses until the seek is complete. This bit is latched after an aborted command error.

Figure 9. SDH Register Format

#### Bit 3 - Data Request (DRQ)

The DRQ bit reflects the status of BDRQ (pin 36). It is asserted when the sector buffer must be written into or read from. DRQ and BDRQ remain asserted until BRDY indicates that the sector buffer has been filled or emptied, depending upon the command. BDRQ can be used for DMA interfacing, while DRQ is used in a programmed I/O environment.

#### Bit 2 - Data Was Corrected (DWC)

When set, this bit indicates that an ECC error has been detected during a read operation, and that the data in the sector buffer has been corrected. This provides the user with an indication that there may be a marginal condition within the drive before the errors become uncorrectable. This bit is forced to zero when not in the ECC mode.

#### Bit 1 - Command In Progress (CIP)

When this bit is set a command is being executed and a new command should not be loaded. Although a command is being executed, the sector buffer is still available for access by the host. When the 82064 is no longer Busy (bit 7 = 0) the STATUS register can be read. If other registers are read while CIP is set the contents of the STATUS register will be returned.

#### Bit 0 - Error

This bit is set whenever any bits in the ERROR register are set. It is the logical 'or' of the bits in the ERROR register and may be used by the host processor to quickly check for nonrecoverable errors. The host must read the ERROR register to determine what type of error occurred. This bit is reset when a new command is written into the COMMAND register.

#### **COMMAND REGISTER**

The command to be executed is written into this write-only register:

| 7 | 6 | 5 | 4   | 3    | 2 | 1 | 0 |

|---|---|---|-----|------|---|---|---|

|   |   |   | COM | MAND |   |   |   |

The command sets Busy and CIP, and begins to execute as soon as it is written into this register. Therefore, all necessary information should be loaded into the Task Register File prior to entering the command. Any attempt to write a register will be ignored until command execution has terminated, as indicated by the CIP bit being cleared. INTRQ is deasserted when the COMMAND register is written.

| COMMAND            | 7 | 6 | 5 | 4 | 3   | 2  | 1  | 0  |

|--------------------|---|---|---|---|-----|----|----|----|

| RESTORE            | 0 | 0 | 0 | 1 | R3  | R2 | R1 | R0 |

| SEEK               | 0 | 1 | 1 | 1 | R3  | R2 | R1 | R0 |

| READ SECTOR        | 0 | 0 | 1 | Ò | - 1 | М  | L  | T  |

| WRITE SECTOR       | 0 | 0 | 1 | 1 | 0   | M  | L  | Т  |

| SCAN ID            | 0 | 1 | 0 | 0 | 0   | 0  | 0  | T  |

| WRITE FORMAT       | 0 | 1 | 0 | 1 | 0   | G  | 0  | 0  |

| COMPUTE CORRECTION | 0 | 0 | 0 | 0 | 1   | 0  | 0  | 0  |

| SET PARAMETER      | 0 | 0 | 0 | 0 | 0   | 0  | 0  | S  |

R<sub>3-0</sub> = Stepping Rate Field

For 5 MHz WR CLOCK:

$R_{3-0} = 0000 35 \, \mu s$ 0001 0.5 ms 0010 1.0 ms 0011 1.5 ms 0100 2.0 ms 0101 2.5 ms 0110 3.0 ms 0111 3.5 ms 1000 4.0 ms 1001 4.5 ms 1010 5.0 ms 1011 5.5 ms 1100 6.0 ms 1101 6.5 ms 1110 3.2 µs 1111 16 us

- I = Interrupt Control

- I = 0 INTRQ occurs with BDRQ/DRQ indicating the sector buffer is full. Valid only when M = 0

- | = 1 INTRQ occurs when the command is completed and the host has read the sector buffer.

- M = Multiple Sector Flag

- M = 0 Transfer one sector. Ignore the SECTOR COUNT register.

- M = 1 Transfer multiple sectors.

- L = Long Mode

- L = 0 Normal mode. Normal CRC or ECC functions are performed.

- L = 1 Long mode. No CRC or ECC bytes are developed or error checking performed on the data field. The 82064 appends the four additional bytes supplied by the host or disk to the data field.

- T = Retry Enable

- T = 0 Enable retries.

- T = 1 Disable retries.

- G = Gap Filler Byte.

- G = 0. Gaps 1, 3 and pad bytes "4E".

- G = 1. Gaps 1, 3 and pad bytes "AA".

- S = Error Correction Span

- S = 0 5-bit span.

- S = 1 11-bit span.

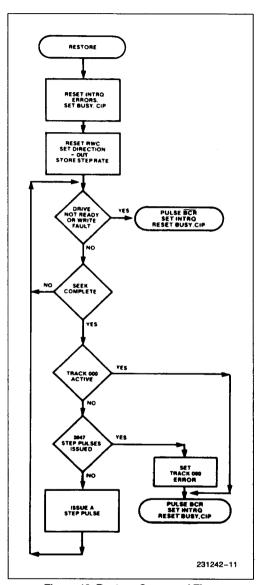

#### RESTORE COMMAND

The RESTORE command is used to position the R/W heads over track zero. It is usually issued by the host when a drive has just been turned on. The 82064 forces an auto-restore when a FORMAT command has been issued following a drive number change.

The actual step rate used for the RESTORE command is determined by the seek complete time. A step pulse is issued and the 82064 waits for a rising edge on the SC line before issuing the next pulse. If the rising edge of SC has not occurred within ten revolutions (INDEX pulses) the 82064 switches to sensing the level of SC. If after 2047 step pulses the TRACK 000 line does not go active the 82064 will set the TRACK 000 bit in the ERROR register, assert INTRQ, and terminate execution of the command. An interrupt will also occur if WR FAULT is asserted on DRDY is deasserted at any time during execution.

The rate field specified (R<sub>3-0</sub>) is stored in an internal register for future use in commands with implied seeks.

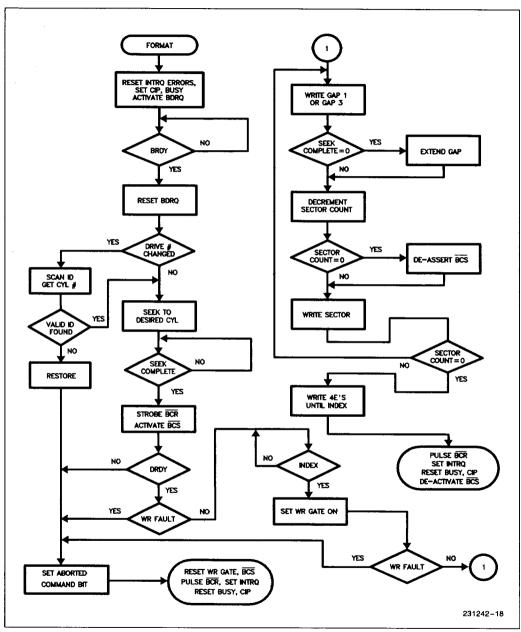

A flowchart of the RESTORE command is shown in Figure 10.

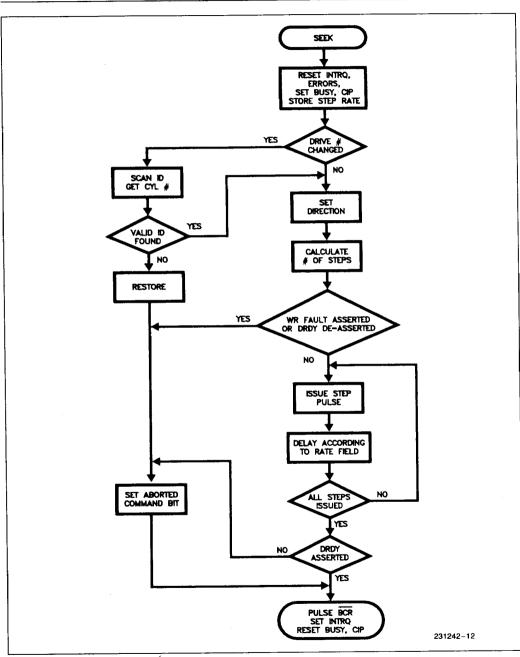

#### **SEEK COMMAND**

The SEEK command can be used for overlapping seeks on multiple drives. The step rate used is taken from the Rate Field of the command, and is stored in an internal register for future use by those commands with implied seek capability.

The direction and number of step pulses needed are calculated by comparing the contents of the CYLIN-DER NUMBER registers in the Task Register File to the present cylinder position stored internally. After all the step pulses have been issued the present cylinder position is updated, INTRQ is asserted, and the command terminated.

If DRDY is deasserted or WR FAULT is asserted during the execution of the command, INTRQ is asserted and the command aborts setting the AC bit in the ERROR register.

If an implied seek is performed, the step rate indicated by the rate field is used for all but the last step pulse. On the last pulse, the command execution continues until the rising edge of SC is detected. If 10 INDEX pulses are received without a rising edge of SC, the 82064 will switch to sensing the level of SC.

A flowchart of the SEEK command flow is shown in Figure 11.

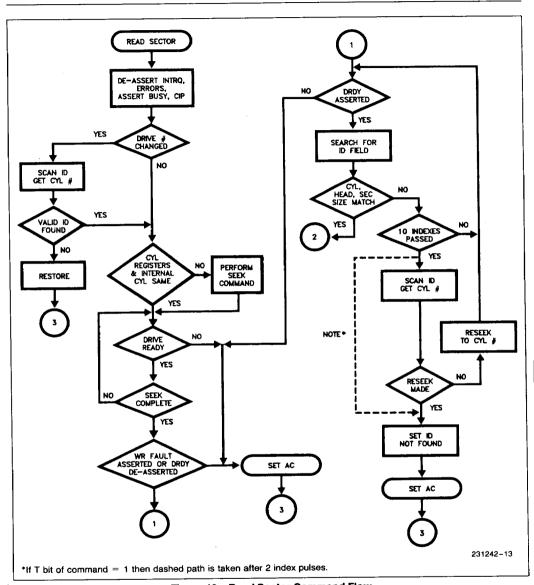

#### **READ SECTOR**

The READ SECTOR command is used to transfer one or more sectors of data from the disk to the sector buffer. Upon receipt of the command, the 82064 checks the CYLINDER NUMBER LOW/HIGH register pair against the internal cylinder position register to see if they are equal. If not, the direction and number of steps calculation takes place, and a seek is initiated. As stated in the description of the SEEK command, if an implied seek occurs, the step rate specified by the rate field is used for all but the last step pulse. On the last step pulse the seek continues until the rising edge of SC is detected.

If the 82064 detects a change in the drive number since the last command, an auto-scan ID is performed. This updates the internal cylinder position register to reflect the current drive before the seek begins.

After the 82064 senses SC (with or without an implied seek) it must find an ID field with the correct cylinder number, head, sector size, and CRC. If retries are enabled (T=0), ten attempts are made to find the correct ID field. If there is still an error on the tenth try, an auto-scan ID and auto-seek are performed. Then ten more retries are attempted before setting the ID Not Found error bit. When retries are disabled (T=1) only two tries are made. No auto-scan or auto-seek operations are performed.

When the data address mark (DAM) is found, the 82064 is ready to transfer data into the sector buffer. When the disk has filled the sector buffer, the 82064 asserts BDRQ and DRQ and then checks the I flag. If I=0, INTRQ is asserted, signaling the host to read the contents of the sector buffer. If I=1, INTRQ occurs after the host has read the sector buffer and the command has terminated. If after successfully reading the ID field, the DAM is not found the DAM Not Found bit in the ERROR register is set.

Figure 10. Restore Command Flow

Figure 11. Seek Command Flow

An optional M flag can be set for multiple sector transfers. When M=0, one sector is transferred and the SECTOR COUNT register is ignored. When M=1, multiple sectors are transferred. After each sector is transferred, the 82064 decrements the SECTOR COUNT register and increments the SECTOR NUMBER register. The next logical sector is transferred regardless of any interleave. Sectors are numbered during the FORMAT command by a byte in the ID field.

For the 82064 to make multiple sector transfers to the sector buffer, the BRDY signal must be toggled from low to high for each sector. The transfers continue until the SECTOR COUNT register equal zero. If the SECTOR COUNT is not zero (indicating more sectors remain to be read), and the sector buffer is full, BDRQ will be asserted and the host must unload the sector buffer. Once this occurs, the sector buffer is free to accept the next sector.

WR FAULT and DRDY are monitored throughout the command execution. If WR FAULT is asserted or DRDY is deasserted, the command will terminate and the Aborted Command bit in the ERROR register will be set. For a description of the error checking procedure on the data field see the explanation in the section entitled "CRC and ECC Generator and Checker."

Both the READ and WRITE commands feature a "simulated completion" to ease programming. BDRQ, DRQ, and INTRQ are generated in a normal manner upon detection of an error condition. This allows the same program flow for successful or unsuccessful completion of a command.

In summary then, the READ SECTOR operation is as follows:

#### When M = 0 (Single Sector Read)

- HOST: Sets up parameters. Issues READ SECTOR command.

- 82064: Asserts BCR.

- 82064: Finds sector specified. Asserts BCR and BCS. Transfers data to sector buffer.

- 82064: Asserts BCR. Deasserts BCS.

- 5. 82064: Asserts BDRQ and DRQ.

- 6. 82064: If I = 1 then go to 9.

- HOST: Read contents of sector buffer.

- 82064: Wait for BRDY, then assert INTRQ. End.

- 82064: Assert INTRQ.

- 10. HOST: Read contents of sector buffer. End.

When M = 1 (Multiple Sector Read)

- HOST: Sets up parameters. Issues READ SECTOR command.

- 82064: Asserts BCR.

- 82064: Finds sector specified. Asserts BCR and BCS. Transfers data to sector buffer

- 4. 82064: Asserts BCR, Deasserts BCS.

- 5. 82064: Asserts BDRQ and DRQ.

- HOST: Reads contents of sector buffer.

- 7. SECTOR

- BUFFER: Indicates data has been transferred by asserting BRDY.

- 82064: When BRDY is asserted, decrement SECTOR COUNT, increment SECTOR NUMBER. If SECTOR COUNT = 0, go to 10.

- 9. 82064: Go to 2.

- 10. 82064: Assert INTRQ.

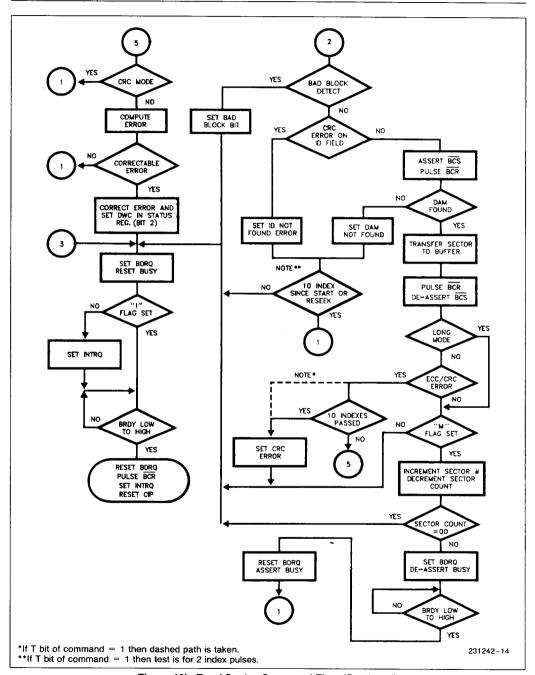

A flowchart of the READ SECTOR command is shown in Figure 12.

#### WRITE SECTOR

The WRITE SECTOR command is used to write one or more sectors of data from the sector buffer to the disk. Upon receipt of the command, the 82064 checks the CYLINDER NUMBER LOW/HIGH register pair against the internal cylinder position register to see if they are equal. If not, the direction and number of steps calculation takes place, and a seek is initiated. As stated in the description of the SEEK command, if an implied seek occurs, the step rate specified by the rate field is used for all but the last step pulse. On the last step pulse the seek continues until the rising edge of SC is detected.

If the 82064 detects a change in the drive number since the last command, an auto-scan ID is performed. This updates the internal cylinder position register to reflect the current drive before the seek begins.

After the 82064 senses SC (with or without an implied seek) BDRQ and DRQ are asserted and the host begins filling the sector buffer with data. When BRDY is asserted, a search for the ID field with the correct cylinder number, head, sector size, and CRC is initiated. If retries are enabled (T=0), ten attempts are made to find the correct ID field. If there is still an error on the tenth try, an auto-scan ID and auto-seek are performed. Then ten more retries are attempted before setting the ID Not Found error bit. When retries are disabled (T=1) only two tries are performed. No auto-scan or auto-seek operations are performed.

Figure 12a. Read Sector Command Flow

Figure 12b. Read Sector Command Flow (Continued)

5

When the correct ID is found, WR GATE is asserted and data is written to the disk. When the CRC/ECC bit (SDH Register, bit 7) is zero, the 82064 generates a two byte CRC character to be appended to the data. When the CRC/ECC bit is one, four ECC bytes replace the CRC character. When L = 1, the polynomial generator is inhibited and neither CRC or ECC bytes are generated. Instead four bytes of data supplied by the host are written.

During a WRITE MULTIPLE SECTOR command (M = 1), the SECTOR NUMBER register is incremented and the SECTOR COUNT register is decremented. If BRDY is asserted after the first sector is read from the sector buffer, the 82064 continues to read data from the sector buffer for the next sector. If BRDY is deasserted, the 82064 asserts BDRQ and waits for the host to place more data in the sector buffer.

In summary then, the WRITE SECTOR operation is as follows:

When M = 0.1

1. HOST: Sets up parameters. Issues WRITE SECTOR command.

2, 82064; Asserts BDRQ and DRQ.

3 HOST: Loads sector buffer with data.

4. 82064: Waits for rising edge of BRDY.

5. 82064: Finds specified ID field. Writes sector to disk.

82064: If M = 0, asserts INTRQ. End.

7. 82064: Increments SECTOR NUMBER. Decrements SECTOR COUNT.

8. 82064: IF SECTOR COUNT = 0, assert INTRQ. End.

9. 82064: Go to 2.

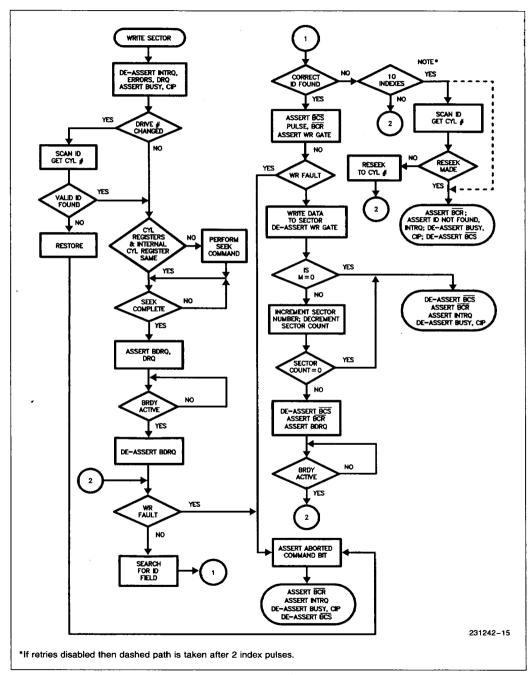

A flowchart of the WRITE SECTOR command is shown in Figure 13.

#### SCAN ID

The SCAN ID command is used to update the SDH, SECTOR NUMBER, and CYLINDER NUMBER LOW/HIGH registers.

After the command is loaded, the SC line is sampled until it is valid. The DRDY and WR FAULT lines are also monitored throughout execution of the command. If a fault occurs the command is aborted and the appropriate error bits are set. When the first ID field is found, the ID information is loaded into the SDH, SECTOR NUMBER, and CYLINDER NUMBER registers. The internal cylinder position register is also updated. If this is an auto-scan caused by a

change in drive numbers, only the internal position register is updated. If a bad block is detected, the BAD BLOCK bit will also be set.

If an ID field is not found, or if a CRC error occurs, and if retries are enabled (T=0), ten attempts are made to read it. If retries are disabled (T=1), only two tries are made. There is no auto-seek in this command and the sector buffer is not disturbed.

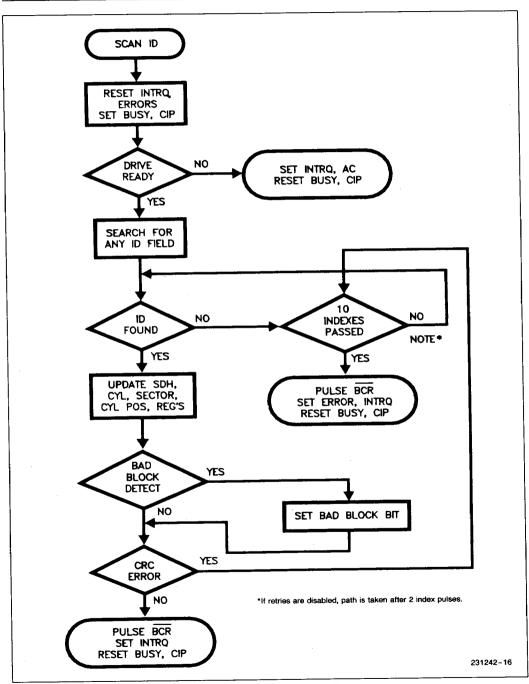

A flowchart of the SCAN ID command is shown in Figure 14.

#### WRITE FORMAT

The WRITE FORMAT command is used to format one track using information in the Task Register File and the sector buffer. During execution of this command, the sector buffer is used for additional parameter information instead of data. Shown in Figure 15 is the contents of a sector buffer for a 32 sector track with an interleave factor of two.

Each sector requires a two byte sequence. The first byte designates whether a bad block mark is to be recorded in the sector's ID field. An 00H is normal; an 80H indicates a bad block mark for that sector. In the example of Figure 15, sector 04 will get a bad block mark recorded. The second byte indicates the logical sector number to be recorded. This allows sectors to be recorded with any interleave factor desired. The remaining memory in the sector buffer may be filled with any value; its only purpose is to generate a BRDY to tell the 82064 to begin formatting the sector buffer may be filled with any value; its only purpose is to generate a BRDY to tell the 82064 to begin formatting the sector buffer may be filled with any value; its only purpose is to generate a BRDY to tell the 82064 to begin formatting the sector buffer may be filled with any value; its only purpose is to generate a BRDY to tell the 82064 to begin formatting the sector buffer may be filled with any value; its only purpose is to generate a BRDY to tell the 82064 to begin formatting the sector buffer may be filled with any value; its only purpose is to generate a BRDY to tell the 82064 to begin formatting the sector buffer may be filled with any value; its only purpose is to generate a BRDY to tell the 82064 to begin formatting the sector buffer may be filled with any value; its only purpose is to generate a BRDY to tell the 82064 to begin formatting the sector buffer may be filled with any value; its only purpose is to generate a BRDY to tell the 82064 to begin formatting the sector buffer may be filled with any value; its only purpose is to generate a BRDY to tell the 82064 to begin formatting the sector buffer may be filled with any value; its only purpose is to generate a BRDY to tell the 82064 to begin formatting the sector buffer may be filled with any value; its only purpose is to generate a BRDY to tell the 82064 to begin formatting the sector buffer may be filled with a sector buffer may be filled with a sector buffer may be filled

If the drive number has been changed since the last command, an auto-restore is initiated, positioning the heads to track 000. The internal cylinder position register is set to zero and the heads seek to the track specified in the Task Register File CYLINDER NUMBER register. This prevents an ID Not Found error from occurring due to an incompatible format, or the track having been erased. A normal implied seek is also in effect for this command.

The SECTOR COUNT register is used to hold the total number of sectors to be formatted (FFH = 255 sectors), while the SECTOR NUMBER register holds the number of bytes, minus three, to be used for Gap 1 and Gap 3. If, for example, the SECTOR COUNT register value is 02H and the SECTOR NUMBER register value is 00H, then 2 sectors are formatted and 3 bytes of 4EH are written for Gap 1 and Gap 3. The data fields are filled with FFH and the CRC or ECC is automatically generated and appended. After the last sector is written the track is filled with 4EH.

Figure 13. Write Sector Command Flow

Figure 14. Scan ID Command Flow

| DATA |    |    |    |    |    |    |     |    |  |  |

|------|----|----|----|----|----|----|-----|----|--|--|

| ADDR | 0  | 1  | 2  | 3  | 4  | 5  | 6   | 7  |  |  |

| 00   | 00 | 00 | 00 | 10 | 00 | 01 | 00  | 11 |  |  |

| 08   | 00 | 02 | 00 | 12 | 00 | 03 | 00  | 13 |  |  |

| 10   | 80 | 04 | 00 | 14 | 00 | 05 | 00  | 15 |  |  |

| 18   | 00 | 06 | 00 | 16 | 00 | 07 | 00  | 17 |  |  |

| 20   | 00 | 08 | 00 | 18 | 00 | 09 | 00  | 19 |  |  |

| 28   | 00 | 0A | 00 | 1A | 00 | OB | 00  | 18 |  |  |

| 30   | 00 | 0C | 00 | 1C | 00 | OD | 00  | 1D |  |  |

| 38   | 00 | 0E | 00 | 1E | 00 | 0F | 00  | 1F |  |  |

| 40   | FF  | FF |  |  |

|      |    |    |    |    |    |    | . , |    |  |  |

|      |    |    |    | :  |    |    |     |    |  |  |

| F0   | FF  | FF |  |  |

Figure 15. Format Command Buffer Contents

The user may select a value of 4EH or AAH for Gaps 1, 3 and pad bytes. This is done by setting bit 2 (Gap Filler Byte) of the format command to "0" for a value of 4EH or "1" for a value of AAH. AAH provides better frequency discrimination with MFM decoding, allowing for simpler circuitry.

The Gap 3 value is determined by the drive motor speed variation, data sector length, and the interleave factor. The interleave factor is only important when 1:1 interleave is used. The formula for determining the minimum Gap 3 length is:

Gap 3 =

$$(2*M*S)+K+E$$

where:

M = motor speed variation (e.g., 0.03 for + 3%)

S = sector length in bytes

K = 18 for an interleave factor of 1

0 for any other interleave factor

E = 2 if ECC is enabled (SDH register, bit 7 = 1)

As for all commands, if WR FAULT is asserted or DRDY is deasserted during execution of the command, the command terminates and the Aborted Command bit in the ERROR register is set.

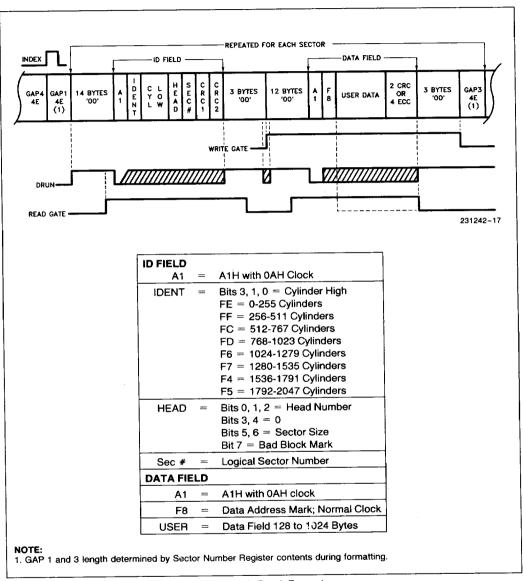

Figure 16 shows the format which the 82064 will write on the disk.

A flowchart of the WRITE FORMAT command is shown in Figure 17.

#### **COMPUTE CORRECTION**

The COMPUTE CORRECTION command determines the location and pattern of a single burst error, but does not correct it. The host, using the data provided by the 82064, must perform the actual correction. The COMPUTE CORRECTION command is used following a data field ECC error. The command initiating the read must specify no retries (T = 1).

The COMPUTE CORRECTION command first writes the four syndrome bytes from the internal ECC register to the sector buffer. Then the ECC register is clocked. With each clock, a counter is incremented and the pattern examined. If the pattern is correctable, the procedure is stopped and the count and pattern are written to the sector buffer, following the syndrome. The process is also stopped if the count exceeds the sector size before a correctable pattern is found.

When the command terminates the sector buffer contains the following data:

Syndrome MSB

Syndrome

Syndrome

Syndrome LSB

Error Pattern Offset Error Pattern Offset

Error Pattern MSB

Error Pattern

Error Pattern LSB

As an example, when the Error Pattern Offset is zero the following procedure may correct the error. The first data byte of the sector is exclusive OR'd with the MSB of the Error Pattern, the second data byte with the second byte of the Error Pattern, and the third data byte with the LSB of the Error Pattern.

If the sector buffer count exceeds the sector size, or if the error burst length is greater than that selected by the Set Parameter command, the ECC/CRC error in the ERROR register and the Error bit in the STATUS register is set.

#### SET PARAMETER

This command selects the correction span to be used for the error correction process. A 5-bit span is selected when bit zero of the command equals 0, and an 11-bit span when bit zero equals 1. The 82064 defaults to a 5-bit span after a RESET.

Figure 16. Track Format

Figure 17. Write Format Command Flow

# ELECTRICAL CHARACTERISTICS ABSOLUTE MAXIMUM RATINGS\*

Ambient Temperature Under Bias .....0°C to 70°C Storage Temperature ......-65°C to + 150°C Supply Voltage ......-0.5V to +8V Voltage on Any Input .......GND - 2V to +6.5V Voltage on Any Output .GND - 0.5V to V<sub>CC</sub> + 0.5V Power Dissipation ..............1 Watt

NOTICE: This is a production data sheet. The specifications are subject to change without notice.

\*WARNING: Stressing the device beyond the "Absolute Maximum Ratings" may cause permanent damage. These are stress ratings only. Operation beyond the "Operating Conditions" is not recommended and extended exposure beyond the "Operating Conditions" may affect device reliability.

#### D.C. CHARACTERISTICS $T_A = 0^{\circ}C$ to $70^{\circ}C$ ; $V_{CC} = +5V \pm 10^{\circ}$ ; GND = 0V

| Symbol           | Parameter                   | Min                          | Max                   | Units | Test Conditions                                          |

|------------------|-----------------------------|------------------------------|-----------------------|-------|----------------------------------------------------------|

| կլ               | Input Leakage Current       |                              | ±10                   | μΑ    | $V_{IN} = V_{CC}$ to $0V_{\underline{}}$                 |

| l <sub>OFL</sub> | Output Leakage Current      |                              | ± 10                  | μА    | $V_{OUT} = V_{CC}$ to 0.45V                              |

| V <sub>IH</sub>  | Input High Voltage          | 2.0                          | V <sub>CC</sub> + 0.5 | V     |                                                          |

| V <sub>IL</sub>  | Input Low Voltage           | -0.5                         | 8.0                   | V     |                                                          |

| V <sub>OH</sub>  | Output High Voltage         | V <sub>CC</sub> - 0.4<br>3.0 | -                     | ٧     | $I_{OH} = -100 \mu\text{A}$<br>$I_{OH} = -2.5 \text{mA}$ |

| V <sub>OL</sub>  | Output Low Voltage          |                              | 0.4<br>0.45           | V     | I <sub>OL</sub> = 2.5 mA<br>6.0 mA P21,<br>22, 23        |

| Icc              | Supply Current              |                              | 20<br>45              | mA    | See Note 10<br>See Note 11                               |

| ICCSB            | Standby Supply Current      |                              | 2                     | mA    | See Note 12                                              |

| Cin              | Input Capacitance           |                              | 10                    | рF    | f <sub>c</sub> = 1 MHz                                   |

| C <sub>I/O</sub> | I/O Capacitance             |                              | 20                    | pF    | Unmeasured pins returned to GND                          |

| For Pins         | 25, 34, 37, 39 (WR CLOCK, [ | RUN, READ D                  | ATA, READ CL          | оск)  |                                                          |

| TRS              | Rise Time                   |                              | 30                    | ns    | 0.9V to 4.2V                                             |

## A.C. CHARACTERISTICS $T_A = 0^{\circ}C$ to $70^{\circ}C$ ; $V_{CC} = +5V \pm 10\%$ ; GND = 0V

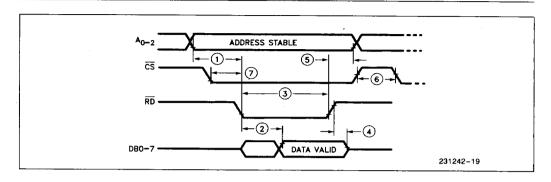

#### HOST READ TIMING WR CLOCK = 5.0 MHz

| Symbol | Parameter                   | Min | Max | Units | Test Conditions |

|--------|-----------------------------|-----|-----|-------|-----------------|

| 1      | Address Stable Before RD ↓  | 0   |     | ns    |                 |

| 2      | Data Delay from RD ↓        |     | 150 | ns    |                 |

| 3      | RD Pulse Width              | 100 |     | ns    |                 |

| 4      | Data Valid after RD ↑       | 10  | 100 | ns    |                 |

| 5      | Address Hold Time after RD↑ | 0   |     | ns    |                 |

| 6      | Read Recovery Time          | 300 |     | ns    |                 |

| 7      | CS Stable before RD ↓       | 0   | _   | ns    | See Note 6      |

-

# intel

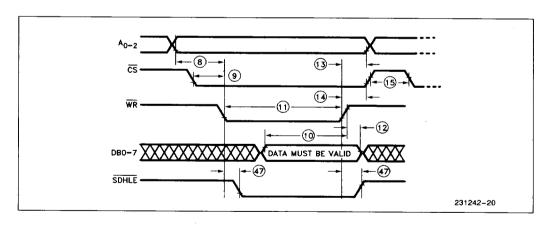

## HOST WRITE TIMING WR CLOCK = 5.0 MHz

| Symbol | Parameter                   | Min | Max   | Units | Test Conditions |

|--------|-----------------------------|-----|-------|-------|-----------------|

| 8      | Address Stable Before WR↓   | 0   |       | ns    |                 |

| 9      | CS Stable Before WR↓        | 0   |       | ns    |                 |

| 10     | Data Setup Time Before WR ↑ | 75  |       | ns    |                 |

| 11     | WR Pulse Width              | 100 | 10000 | ns    |                 |

| 12     | Data Hold Time After WR↑    | 0   |       | ns    |                 |

| 13     | Address Hold Time After WR↑ | 0   |       | ns    |                 |

| 14     | CS Hold Time After WR↑      | 0   |       | ns    | See Note 7      |

| 15     | Write Recovery Time         | 300 |       | ns    |                 |

| 47     | SDHLE Propagation Delay     | 20  | 150   | ns    |                 |

# intel

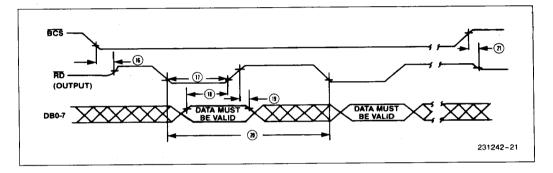

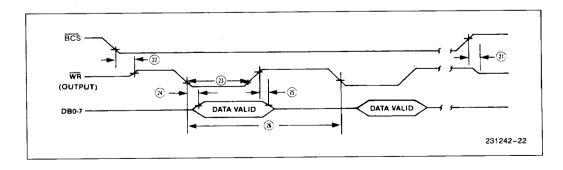

## BUFFER READ TIMING (WRITE SECTOR COMMAND) WR CLOCK = 5.0 MHz

| Symbol | Parameter             | Min | Тур | Max | Units | Test Conditions |

|--------|-----------------------|-----|-----|-----|-------|-----------------|

| 16     | BCS ↓ to RD Valid     | 0   |     | 100 | ns    |                 |

| 17     | RD Output Pulse Width | 300 | 400 | 500 | ns    | See Note 3      |

| 18     | Data Setup to RD↑     | 140 |     |     | ns    |                 |

| 19     | Data Hold from RD↑    | 0   |     |     | ns    |                 |

| 20     | RD Repetition Rate    | 1.2 | 1.6 | 2.0 | μs    | See Note 8      |

| 21     | RD Float from BCS↑    | 0   |     | 100 | ns    |                 |

## BUFFER WRITE TIMING (READ SECTOR COMMAND) WR CLOCK = 5.0 MHz

| Symbol | Parameter             | Min | Тур | Max | Units | Test Conditions |

|--------|-----------------------|-----|-----|-----|-------|-----------------|

| 22     | BCS ↓ to WR Valid     | 0   |     | 100 | ns    |                 |

| 23     | WR Output Pulse Width | 300 | 400 | 500 | ns    | See Note 3      |

| 24     | Data Valid from WR ↓  |     |     | 150 | ns    |                 |

| 25     | Data Hold from WR ↑   | 60  |     | 200 | ns    |                 |

| 26     | WR Repetition Rate    | 1.2 | 1.6 | 2.0 | μs    | See Note 8      |

| 27     | WR Float from BCS↑    | 0   |     | 100 | ns    |                 |

5

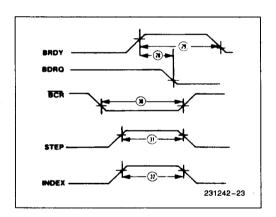

## **MISCELLANEOUS TIMING**

| Symbol | Parameter            | Min  | Тур | Max  | Units  | Test Conditions                           |

|--------|----------------------|------|-----|------|--------|-------------------------------------------|

| 28     | BDRQ Reset from BRDY | 20   |     | 200  | ns     |                                           |

| 29     | BRDY Pulse Width     | 400  |     |      | ns     | See Note 4                                |

| 30     | BCR Pulse Width      | 1.4  | 1.6 | 1.8  | μs     | See Notes 9, 13, 15                       |

| 31     | STEP Pulse Width     | 1.5  | 1.6 | 1.7  | μs     | Step Rate = 3.2 µs/step                   |

|        |                      | 7.6  | 8.0 | 8.4  | μs     | All other step rates,<br>See Notes 14, 15 |

| 32     | INDEX Pulse Width    | 500  |     |      | ns     |                                           |

| 33     | RESET Pulse Width    | 24   |     |      | WR CLK | See Note 2                                |

| 34     | RESET ↓ to BCR ↓     | 0    | 1.6 | 3.2  | μs     | See Notes 1, 15                           |

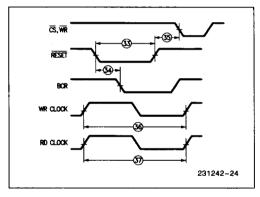

| 35     | RESET ↑ to WR, CS ↓  | 6.4  | _   |      | μs     | See Note 1                                |

| 36     | WR CLOCK Frequency   | 0.25 | 5.0 | 5.25 | MHz    | 50% Duty Cycle                            |

| 37     | RD CLOCK Frequency   | 0.25 | 5.0 | 5.25 | MHz    | See Note 5                                |

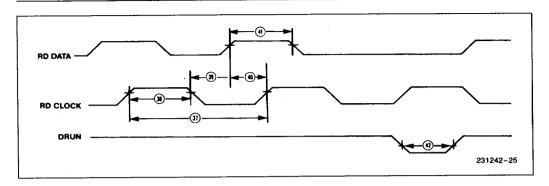

## **READ DATA TIMING WR CLOCK = 5.0 MHZ**

| Symbol | Parameter                 | Min | Тур | Max   | Units | Test Conditions |

|--------|---------------------------|-----|-----|-------|-------|-----------------|

| 38     | RD CLOCK Pulse Width      | 95  |     | 2000  | ns    | 50% Duty Cycle  |

| 39     | RD DATA after RD CLOCK ↓  | 10  |     |       | ns    |                 |

| 40     | RD DATA before RD CLOCK ↑ | 20  |     |       | ns    |                 |

| 41     | RD DATA Pulse Width       | 40  |     | T38/2 | ns    |                 |

| 42     | DRUN Pulse Width          | 30  |     |       | ns    |                 |

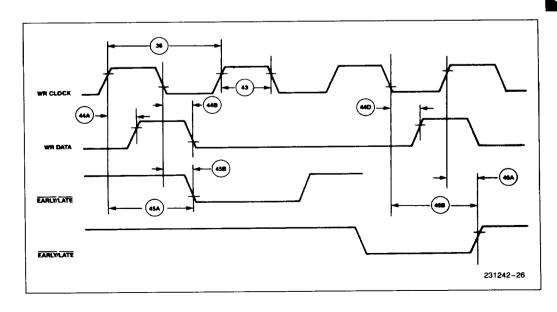

## WRITE DATA TIMING WR CLOCK = 5.0 MHZ

| Symbol | Parameter                  | Min  | Тур | Max  | Units | Test Conditions |

|--------|----------------------------|------|-----|------|-------|-----------------|

| 43     | WR CLOCK Pulse Width       | 95   |     | 2000 | ns    | 50% Duty Cycle  |

|        | Propagation Delay          |      |     |      |       |                 |

| 44A    | WR CLOCK ↑ to WR DATA ↑    | 10   |     |      |       |                 |

| 44B    | WR CLOCK ↓ to WR DATA ↓    |      |     | 65   | ns    |                 |

| 44D    | WR CLOCK ↓ to WR DATA ↑    |      |     |      |       |                 |

| 45A    | WR CLOCK ↑ to EARLY/LATE ↓ | 10   |     | 65   | ns    |                 |

| 45B    | WR CLOCK ↓ to EARLY/LATE ↓ |      |     |      | 113   |                 |

| 46A    | WR CLOCK ↑ to EARLY/LATE ↑ | 10   | ļ   | 65   | ns    |                 |

| 46B    | WR CLOCK ↓ to EARLY/LATE ↑ | 1 10 |     |      |       |                 |

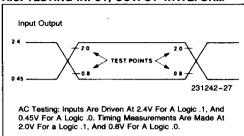

#### A.C. TESTING INPUT, OUTPUT WAVEFORM

## A.C. TESTING LOAD CIRCUIT DEVICE UNDER TEST CL = 50 pF 100 pF Databus pins only 231242-28 C<sub>1</sub> Includes Jig Capacitance

#### NOTES

- 1. Based on WR CLOCK = 5.0 MHz

- 2. 24 WR CLOCK periods = 4.8 µs at 5.0 MHz.

- 3. 2 WR CLOCK periods ± 100 ns.

- 4. Previous restrictions on BRDY no longer apply. There are no restrictions on when BRDY may come. BRDY may be connected directly to BDRQ.

- 5. WR CLOCK Frequency = RD CLOCK Frequency ± 15%.

- 6. RD may be asserted before CS as long as it remains active for at least the minimum T3 pulse width after CS is asserted. 7. WR may be asserted before CS as long as it remains active for at least the minimum T11 pulse width after CS is asserted.

- 8. 8 WR CLOCK periods ±2 WR CLOCK periods.

- 9. 8 WR CLOCK periods ±1 WR CLOCK period.

- 10. V<sub>IL</sub> = GND, V<sub>IH</sub> = V<sub>CC</sub>, Outputs Open.

11. V<sub>IL</sub> = 0.8V, V<sub>IH</sub> = 2.0V, Outputs Open.

12. WR CLOCK & RD CLO<u>CK</u> = DC, V<sub>IL</sub> = 0V, V<sub>IH</sub> = V<sub>CC</sub>, all output o<u>pen.</u> <del>CS</del> inactive.

- 13. This specification is for BCR pulse width during command execution. BCR is also triggered by RESET. In this case, BCR pulse width is greater than RESET pulse width.

- 14. 40 WR Clocks ±2.

- 15. Specification represents actual functionality of 82064 and WD2010. Previous datasheets contain typographical errors.