查询Z8002/BQA供应商

捷多邦,专业PCB打样工厂,24小时加急出货

# IMAGE UNAVAILABLE

会の程序。WWW.dzsc.com

の発展に関する。MWW.dzsc.com

の数据に関する。MWW.dzsc.com

の数据に関する。MWW.dzsc.com

の数据に関する。MWW.dzsc.com

の数据に関する。MWW.dzsc.com

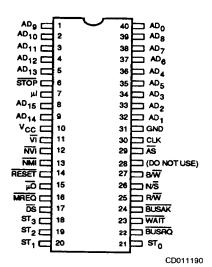

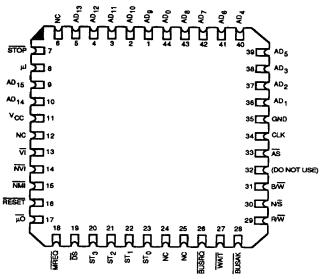

# CONNECTION DIAGRAMS Top View

DIPs

LCC

CD011180

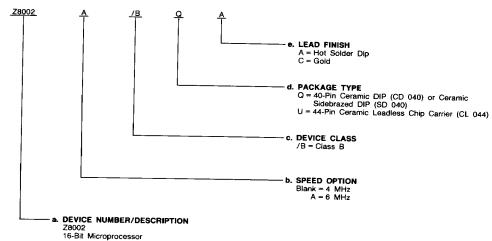

## MILITARY ORDERING INFORMATION

#### **APL Products**

AMD products for Aerospace and Defense applications are available in several packages and operating ranges. APL (Approved Products List) products are fully compliant with MIL-STD-883C requirements. The order number (Valid Combination) is formed by b. Speed Option (if applicable)

- c. Device Class

- d. Package Type

- e. Lead Finish

| Valid Combinations |  |                  |  |  |  |  |

|--------------------|--|------------------|--|--|--|--|

| Z8002              |  | /504 /500 /511   |  |  |  |  |

| Z8002A             |  | /BQA, /BQC, /BUA |  |  |  |  |

#### **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations or to check for newly released valid combinations.

#### **Group A Tests**

Group A tests consist of Subgroups 1, 2, 3, 7, 8, 9, 10, 11.

#### **ABSOLUTE MAXIMUM RATINGS**

| Storage Temperature65 to | + 150°C |

|--------------------------|---------|

| Voltage at any Pin       |         |

| Relative to VSS0.3 to    | o +7.0V |

| Power Dissipation        | 2 5W/   |

Stresses above those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

#### **OPERATING RANGES**

| Military (M) Devices                      |   |

|-------------------------------------------|---|

| Temperature (T <sub>C</sub> )55 to +125°C | 2 |

| Supply Voltage (V <sub>CC</sub> )5 V ± 5% | 6 |

Operating ranges define those limits between which the functionality of the device is guaranteed.

DC CHARACTERISTICS over operating range (for APL Products, Group A, Subgroups 1, 2, 3 are tested unless otherwise noted)

| Parameter<br>Symbol             | Parameter<br>Description                | Test Conditions                        | Min.                 | Max.                   | Unit |

|---------------------------------|-----------------------------------------|----------------------------------------|----------------------|------------------------|------|

| V <sub>CH</sub> †               | Clock Input HIGH Voltage                | Driven by External Clock Generator     | V <sub>CC</sub> -0.4 | V <sub>CC</sub> +0.3*  | V    |

| V <sub>CL</sub> †               | Clock Input LOW Voltage                 | Driven by External Clock Generator     | -0.3*                | 0.45                   | ٧    |

| VIH †                           | Input HIGH Voltage                      |                                        |                      | V <sub>CC</sub> + 0.3* | ٧    |

| V <sub>IH</sub> NMI, †<br>Reset | Input HIGH Voltage                      | IA!                                    | -(4)                 | V <sub>CC</sub> + 0.3* | ٧    |

| V <sub>IL</sub> †               | Input LOW Voltage                       | 20 114                                 | -0.3*                | 0.8                    | ٧    |

| VoH                             | Output HIGH Voltage                     | I <sub>O</sub> -2                      | 2.4                  |                        | V    |

| V <sub>OL</sub>                 | Output LOW Voltage                      | I <sub>O</sub> And And                 |                      | 0.4                    | V    |

| l <sub>IL</sub>                 | Input teal the Except SLST<br>Pin       | $0.4 \leqslant V_{ N} \leqslant +2.4V$ |                      | ±10                    | μΑ   |

| II <sub>L</sub> on SEGT         | Input Lakage on SEGT Pin                |                                        | -100                 | 100                    | μΑ   |

| loL                             | Output Leakage                          | 0.4 ≤ V <sub>OUT</sub> ≤ + 2.4V        |                      | ±10                    | μΑ   |

| ICC                             | V <sub>CC</sub> Supply Current (Note 1) |                                        |                      | 400                    | mA   |

Notes: 1. ICC is measured while running a functional pattern with the loads turned on.

<sup>\*</sup> Not tested; guaranteed by design. † Group A, Subgroups 7 and 8 only are tested.

## Standard Test Conditions

The characteristics below apply for the following test conditions, unless otherwise noted. All voltages are referenced to GND. Positive current flows into the referenced pin. Standard conditions are as follows:

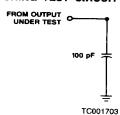

#### SWITCHING TEST CIRCUIT

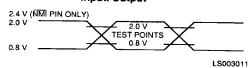

# SWITCHING TEST WAVEFORMS Input/Output

AC testing outputs are driven at 2.0 V for a logical 1 and 0.5 V for a logical 0. The clock is driven at  $V_{CC}$  -0.4 V and 0.45 V. Timing measurements are made at 2.0 V for a logical 1 and 0.5 V for a logical 0.

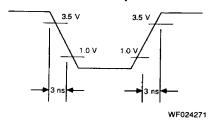

#### **AC Clock Input**

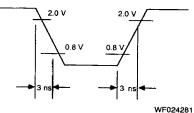

#### AC Input (Except Clock)

**SWITCHING CHARACTERISTICS** over operating range (for APL Products, Group A, Subgroups 9, 10, 11 are tested unless otherwise noted)

| Parameter<br>No. Symbol |           | 4-MHz                                              | 4-MHz Devices |      | 6-MHz Devices |      |    |

|-------------------------|-----------|----------------------------------------------------|---------------|------|---------------|------|----|

|                         |           | Min.                                               | Max.          | Min. | Max.          | Unit |    |

| 1                       | TcC       | Clock Cycle Time                                   | 250           | 500  | 160           | 500  | ns |

| _ 2                     | TwCh      | Clock Width (HIGH)                                 | 105           | 250  | 70            | 250  | ns |

| 3                       | TwCl      | Clock Width (LOW)                                  | 105           | 250  | 70            | 250  | ns |

| 4                       | TfC       | Clock Fall Time (Note 1)                           |               | 20   |               | 10   | ns |

| 5                       | TrC       | Clock Rise Time (Note 1)                           |               | 20   |               | 15   | ns |

| 8                       | TdC(Bz)   | Clock 1 to Bus Float (Note 2)                      |               | 65   |               | 55   | ns |

| 9                       | TdC(A)    | Clock ↑ to Address Valid                           |               | 100  |               | 75   | ns |

| 10                      | TdC(Az)   | Clock † to Address Float (Note 2)                  |               | 65   |               | 55   | ns |

| 11                      | TdA(DR)   | Address Valid to Read Data Required Valid (Note 2) |               | 475  |               | 305  | ns |

| 12                      | TsDI(C)   | Data In to Clock ↓ Setup Time                      | 50            |      | 20            |      | ns |

| 13                      | TdDS(A)   | DS to Address Active (Note 2)                      | 80            |      | 45            |      | ns |

| 14                      | TdC(DW)   | Clock † to Write Data Valid                        |               |      |               | 75   | ns |

| 15                      | ThDI(DS)  | Data In to DS † Hold Time                          | W             |      | 0             |      | ns |

| 16                      | TdDO(DS)  | Data Out Valid to DS 1 Delay (Note 2)              | 4-2           |      | 195           |      | ns |

| 17                      | TdA(MR)   | Address Valid to MREQ   Delay (Note 2)             | 55            |      | 35            |      | ns |

| 18                      | TdC(MR)   | Clock ; to MREQ ; Delay                            |               | 80   |               | 60   | ns |

| 19                      | TwMRh     | MREQ Width (HIGH) (Note 2)                         | 210           |      | 135           |      | ns |

| 20                      | TdMR(A)   | MREQ   to Address Not Active (No. 2)               | 70            |      | 35            |      | ns |

| 21                      | TdDO(DSW) | Data Out Valid to DS   Write (Note 2)              | 55            |      | 35            |      | ns |

| 22                      | TdMR(DR)  | MREQ 1 to Read Data A quire Valid (Note 2)         |               | 370  |               | 230  | ns |

| 23                      | TdC(MR)   | Clock   to MREQ   Lay                              |               | 80   |               | 60   | ns |

| 24                      | TdC(ASf)  | Clock † to A Nelson                                | <u> </u>      | 80   | 7.1           | 60   | ns |

| 25                      | TdA(AS)   | Address Vita to AS 1 Delay (Note 2)                | 55            |      | 35            |      | ns |

| 26                      | TdC(ASr)  | Clock . 6 5 Delay                                  |               | 90   |               | 80   | ns |

| 27                      | TdAS(DR)  | AS 1 to Read Data Required Valid (Note 2)          |               | 360  |               | 220  | ns |

| 28                      | TdDS(AS)  | DS 1 to AS 1 Delay (Note 2)                        | 70            |      | 35            |      | ns |

| 29                      | TwAS      | AS Width (LOW) (Note 2)                            | 85            |      | 55            |      | ns |

| 30                      | TdAS(A)   | AS ↑ to Address Not Active Delay (Note 2)          | 70            |      | 45            |      | ns |

| 31                      | TdAz(DSR) | Address Float to DS (Read) ↓ Delay (Note 2)        | 0             |      | 0             |      | ns |

| 32                      | TdAS(DSR) | AS ↑ to DS (Read) ↓ Delay (Note 2)                 | 80            |      | 55            |      | ns |

| 33                      | TdDSR(DR) | DS (Read) 1 to Read Data Required Valid (Note 2)   |               | 205  |               | 130  | ns |

| 34                      | TdC(DSr)  | Clock 1 to DS 1 Delay                              |               | 70   |               | 65   | ns |

| 35                      | TdDS(DW)  | DS 1 to Write Data and STATUS Not Valid (Note 2)   | 75            |      | 45            |      | ns |

| 36                      | TdA(DSR)  | Address Valid to DS (Read) ↓ Delay (Note 2)        | 180           |      | 110           |      | ns |

| 37                      | TdC(DSR)  | Clock ↑ to DS (Read) ↓ Delay                       |               | 120  |               | 85   | ns |

| 38                      | TwDSR     | DS (Read) Width (LOW) (Note 2)                     | 275           |      | 185           |      | ns |

Notes: See next page for notes.

## SWITCHING CHARACTERISTICS (Cont'd.)

| Parameter  | Parameter Description | 4-MHz                                                   | 4-MHz Devices |      | 6-MHz Devices |      |    |

|------------|-----------------------|---------------------------------------------------------|---------------|------|---------------|------|----|

| No. Symbol |                       | Min.                                                    | Max.          | Min. | Max.          | Unit |    |

| 39         | TdC(DSW)              | Clock ↓ to DS (Write) ↓ Delay                           |               | 95   |               | 80   | ns |

| 40         | TwDSW                 | DS (Write) Width (LOW) (Note 2)                         | 185           |      | 110           |      | ns |

| 41         | TdDSI(DR)             | DS (Input) ↓ to Read Data Required Valid (Note 2)       |               | 330  |               | 210  | ns |

| 42         | TdC(DSF)              | Clock ↓ to DS (I/O) ↓ Delay                             |               | 120  |               | 100  | ns |

| 43         | TwDS                  | DS (I/O) Width (LOW) (Note 2)                           | 410           |      | 255           |      | ns |

| 44         | TdAS(DSA)             | AS t to DS (Acknowledge)   Delay (Note 2)               | 1065          |      | 690           |      | ns |

| 45         | TdC(DSA)              | Clock ↑ to DS (Acknowledge) ↓ Delay                     |               | 20   |               | 85   | ns |

| 46         | TdDSA(DR)             | DS (Acknowledge) I to Read Data Required Delay (Note 2) | No.           | 4.   |               | 295  | ns |

| 47         | TdC(S)                | Clock † to Status Valid Delay                           |               | 110  |               | 85   | ns |

| 48         | TdS(AS)               | Status Valid to AS † Delay (Note 2)                     | 1             |      | 30            |      | ns |

| 49         | TsR(C)                | RESET to Clock † Setup Time                             | 180           |      | 70            |      | ns |

| 50         | ThR(C)                | RESET to Clock † Hold Time                              | 0             |      | 0             |      | ns |

| 51         | TwNMI                 | NMI Width (LOW)                                         | 100           |      | 70            |      | ns |

| 52         | TsNMI(C)              | NMI to Clock † Setup Tim                                | 140           |      | 70            | -    | ns |

| 53         | TsVI(C)               | VI, NVI to Clock † South Ti                             | 110           |      | 50            |      | ns |

| 54         | ThVI(C)               | VI, NVI to Clock Holo Time                              | 20            |      | 20            |      | ns |

| 57         | TsMI(C)               | MI to Clock Setup Time                                  | 180           |      | 110           |      | ns |

| 58         | ThMI(C)               | MI to Clack to time                                     | 0             |      | 0             |      | ns |

| 59         | TdC(MO)               | Clog 1 C Delay                                          |               | 120  |               | 85   | ns |

| 60         | TsSTP(C)              | STOP o lock   Setup Time                                | 140           |      | 80            |      | ns |

| 61         | ThSTP(C)              | STOP to Clock # Hold Time                               | 0             |      | 0             |      | ns |

| 62         | TsWT(C)               | WAIT to Clock 1 Setup Time                              | 50            |      | 30            |      | ns |

| 63         | ThWT(C)               | WAIT to Clock ↓ Hold Time                               | 10            |      | 10            |      | ns |

| 64         | TsBRQ(C)              | BUSRQ to Clock † Setup Time                             | 90            |      | 80            |      | ns |

| 65         | ThBRQ(C)              | BUSRQ to Clock † Hold Time                              | 10            |      | 10            |      | ns |

| 66         | TdC(BAKr)             | Clock 1 to BUSAK 1 Delay                                |               | 100  |               | 75   | ns |

| 67         | TdC(BAKf)             | Clock 1 to BUSAK 1 Delay                                |               | 100  |               | 75   | ns |

| 68         | TwA                   | Address Valid Width (Note 2)                            | 150           |      | 95            |      | ns |

| 69         | TdDS(S)               | DS to STATUS Not Valid (Note 2)                         | 80            |      | 55            |      | ns |

Notes: 1. Clock rise and fall times are intended for design information only; not tested. 2. Not tested.