捷多邦,专业PCB打样

**1K** Commercial

# X2201A

# 1024 x 1 Bit

# Nonvolatile Static RAM

## **FEATURES**

- Single 5V Supply

- Fully TTL Compatible

- Infinite E<sup>2</sup>PROM Array Recall, RAM Read and Write Cycles

- Access Time of 300 ns Max.

- Nonvolatile Store Inhibit: V<sub>CC</sub> = 3V Typical

- High Reliability

- -Store Cycles: 10,000

- -Data Retention: 100 Years

## DESCRIPTION

The Xicor X2201A is a 1024 x 1 NOVRAM featuring a high-speed static RAM overlaid bit-for-bit with a nonvolatile E<sup>2</sup>PROM. The X2201A is fabricated with the same reliable N-channel floating gate MOS technology used in all Xicor 5V nonvolatile memories.

The NOVRAM design allows data to be easily transferred from RAM to E<sup>2</sup>PROM (store) and from E<sup>2</sup>PROM to RAM (recall). The store operation is completed in 10 ms or less and the recall is typically completed in 1 µs.

Xicor NOVRAMs are designed for unlimited write operations to RAM, either from the host or recalls from E<sup>2</sup>PROM. The E<sup>2</sup>PROM array is designed for a minimum 10,000 store cycles and inherent data retention is specified to be greater than 100 years. Refer to RR-520 and RR-515 for details on Xicor nonvolatile memory endurance and data retention characteristics.

#### **ABSOLUTE MAXIMUM RATINGS\***

| Temperature Under Bias  | 10°C to +85°C  |

|-------------------------|----------------|

| Storage Temperature     | 65°C to +150°C |

| Voltage on any Pin with |                |

| Respect to Ground       | 1.0V to +7V    |

| D.C. Output Current     | 5 mA           |

| Lead Temperature        |                |

| (Soldering, 10 Seconds) |                |

### D.C. OPERATING CHARACTERISTICS

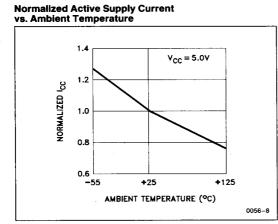

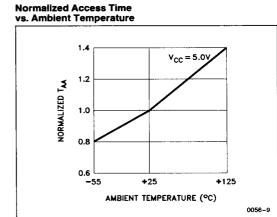

$T_A = 0^{\circ}C$  to +70°C,  $V_{CC} = +5V \pm 10\%$ , unless otherwise specified.

#### \*COMMENT

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and the functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

| Symbol              | Parameter              | Limits |                       | Units | Test Conditions                                   |

|---------------------|------------------------|--------|-----------------------|-------|---------------------------------------------------|

|                     | r aramotor             | Min.   | Max.                  | 01110 |                                                   |

| Icc                 | Power Supply Current   |        | 60                    | mA    | All Inputs = $V_{CC}$<br>$I_{I/O} = 0 \text{ mA}$ |

| I <sub>LI</sub>     | Input Load Current     |        | 10                    | μΑ    | $V_{IN} = GND$ to $V_{CC}$                        |

| LO                  | Output Leakage Current |        | 10                    | μA    | $V_{OUT} = GND to V_{CC}$                         |

| V <sub>IL</sub> (2) | Input Low Voltage      | - 1.0  | 0.8                   | V     |                                                   |

| V <sub>IH</sub> (2) | Input High Voltage     | 2.0    | V <sub>CC</sub> + 1.0 | V     |                                                   |

| VOL                 | Output Low Voltage     |        | 0.4                   | V     | $I_{OL} = 4.2 \text{ mA}$                         |

| VOH                 | Output High Voltage    | 2.4    |                       | v     | $I_{OH} = -2  mA$                                 |

#### ENDURANCE AND DATA RETENTION

| Parameter      | Min.   | Units                | Conditions                                  |

|----------------|--------|----------------------|---------------------------------------------|

| Endurance      | 1,000  | Data Changes Per Bit | Xicor Reliability Reports RR-520 and RR-504 |

| Store Cycles   | 10,000 | Store Cycles         | Xicor Reliability Reports RR-520 and RR-504 |

| Data Retention | 100    | Years                | Xicor Reliability Report RR-515             |

## $\label{eq:capacitance} \textbf{CAPACITANCE} \quad \textbf{T}_{A} \,=\, 25^{\circ}\text{C}, \, \textbf{f} \,=\, 1.0 \,\, \text{MHz}, \, \textbf{V}_{CC} \,=\, 5\text{V}$

| Symbol                         | Test                     | Max. | Units | Conditions     |

|--------------------------------|--------------------------|------|-------|----------------|

| C <sub>I/O</sub> (1)           | Input/Output Capacitance | 8    | pF    | $V_{I/O} = 0V$ |

| C <sub>IN</sub> <sup>(1)</sup> | Input Capacitance        | 6    | pF    | $V_{IN} = 0V$  |

Notes: (1) This parameter is periodically sampled and not 100% tested.

(2)  $V_{\rm IL}$  min. and  $V_{\rm IH}$  max. are for reference only and are not tested.

### A.C. CONDITIONS OF TEST

| Input Pulse Levels                | 0V to 3.0V                            |

|-----------------------------------|---------------------------------------|

| Input Rise and<br>Fall Times      | 10 ns                                 |

| Input and Output<br>Timing Levels | 1.5V                                  |

| Output Load                       | 1 TTL Gate and $C_L = 100 \text{ pF}$ |

## MODE SELECTION

|    | Inputs |              |       | Input Output    | Mode                               |

|----|--------|--------------|-------|-----------------|------------------------------------|

| CS | WE     | ARRAY RECALL | STORE | 1/0             | Mode                               |

| н  | x      | Н            | н     | Output High Z   | Not Selected <sup>(3)</sup>        |

| L  | н      | Н            | н     | Output Data     | Read RAM                           |

| L  | L      | Н            | н     | Input Data High | Write "1" RAM                      |

| L  | L      | Н            | Н     | Input Data Low  | Write "0" RAM                      |

| х  | н      | L            | Н     | Output High Z   | Array Recall                       |

| н  | Х      | L            | н     | Output High Z   | Array Recali                       |

| X  | н      | Н            | L     | Output High Z   | Nonvolatile Storing <sup>(4)</sup> |

| н  | x      | Н            | L     | Output High Z   | Nonvolatile Storing <sup>(4)</sup> |

## A.C. CHARACTERISTICS

$T_{A}$  = 0°C to +70°C,  $V_{CC}$  = +5V  $\pm$ 10%, unless otherwise specified.

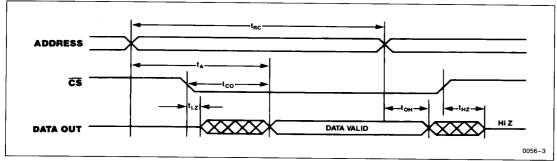

### **Read Cycle Limits**

| Symbol              | Parameter                         | Min. | Max. | Units |

|---------------------|-----------------------------------|------|------|-------|

| t <sub>RC</sub>     | Read Cycle Time                   | 300  |      | ns    |

| t <sub>A</sub>      | Access Time                       |      | 300  | ns    |

| tco                 | Chip Select to Output Valid       |      | 200  | ns    |

| t <sub>OH</sub>     | Output Hold from Address Change   | 50   |      | ns    |

| t <sub>LZ</sub> (5) | Chip Select to Output in Low Z    | 10   |      | ns    |

| t <sub>HZ</sub> (5) | Chip Deselect to Output in High Z | 10   | 100  | ns    |

## **Read Cycle**

Notes: (3) Chip is deselected but may be automatically completing a store cycle.

(4)  $\overline{\text{STORE}} = L$  is required only to initiate the store cycle, after which the store cycle will be automatically completed (STORE = X).

(5)  $t_{LZ}$  min. and  $t_{HZ}$  min. are periodically sampled and not 100% tested.

1

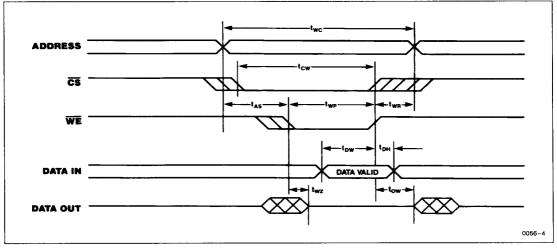

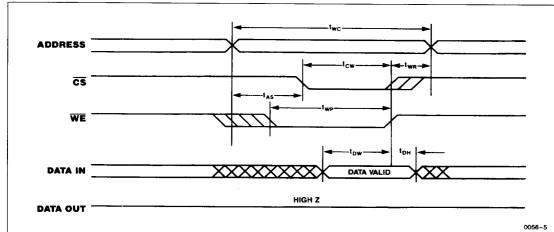

## Write Cycle Limits

| Symbol          | Parameter                        | Min. | Max. | Units |

|-----------------|----------------------------------|------|------|-------|

| twc             | Write Cycle Time                 | 300  |      | ns    |

| tcw             | Chip Select to End of Write      | 150  |      | ns    |

| t <sub>AS</sub> | Address Setup Time               | 50   |      | ns    |

| twp             | Write Pulse Width                | 150  |      | ns    |

| twn             | Write Recovery Time              | 25   |      | ns    |

| t <sub>DW</sub> | Data Valid to End of Write       | 100  |      | ns    |

| t <sub>DH</sub> | Data Hold Time                   | 0    |      | ns    |

| twz             | Write Enable to Output in High Z | 10   | 100  | ns    |

| tow             | Output Active from End of Write  | 10   |      | ns    |

# Write Cycle

# Early Write Cycle

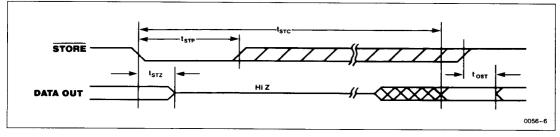

# Store Cycle Limits

| Symbol           | Parameter                       | Min. | Max. | Units |

|------------------|---------------------------------|------|------|-------|

| tstc             | Store Time                      |      | 10   | ms    |

| tSTP             | Store Pulse Width               | 100  |      | ns    |

| t <sub>STZ</sub> | Store to Output in High Z       |      | 500  | ns    |

| t <sub>OST</sub> | Output Active from End of Store | 10   |      | ns    |

# Store Cycle

1

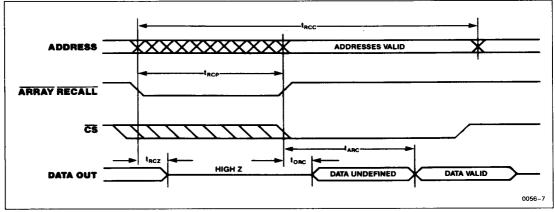

### **Array Recall Cycle Limits**

| Symbol           | Parameter                                    | Min. | Max. | Units |

|------------------|----------------------------------------------|------|------|-------|

| tRCC             | Array Recall Cycle Time                      | 1200 |      | ns    |

| tRCP             | Recall Pulse Width <sup>(6)</sup>            | 450  |      | ns    |

| t <sub>RCZ</sub> | Recall to Output in High Z                   |      | 150  | ns    |

| tORC             | Output Active from End of Recall             | 10   |      | ns    |

| tARC             | Recalled Data Access Time from End of Recall |      | 750  | ns    |

# Array Recall Cycle

Note: (6) Array Recall rise time must be less than 1 µs.

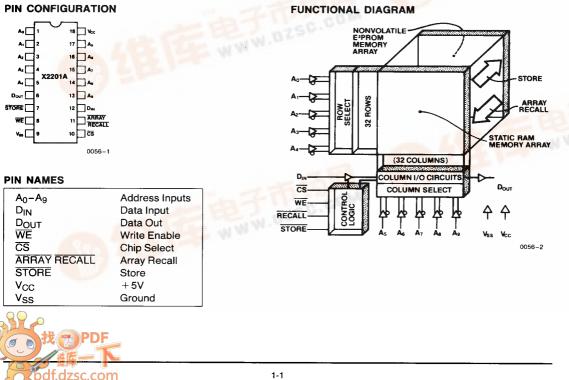

### PIN DESCRIPTIONS AND DEVICE OPERATION

#### Addresses (A<sub>0</sub>-A<sub>9</sub>)

The address inputs select a memory location during a read or write operation.

#### Chip Select (CS)

The Chip Select input must be LOW to enable read/ write operations with the RAM array.  $\overline{CS}$  HIGH will place the D<sub>OUT</sub> in the high impedance state.

#### Write Enable (WE)

The Write Enable input controls the  $D_{OUT}$  buffer, determining whether a RAM read or write operation is enabled. WE HIGH enables a read and WE LOW enables a write.

#### Data In (DIN)

Data is written into the device via the DIN input.

### Data Out (DOUT)

Data from a selected address is output on the  $D_{OUT}$  output. This pin is in the high impedance state when either  $\overline{CS}$  is HIGH or when  $\overline{WE}$  is LOW.

### STORE

The STORE input, when LOW, will initiate the transfer of the entire contents of the RAM array to the E<sup>2</sup>PROM array. The WE and ARRAY RECALL inputs are inhibited during the store cycle. The store operation will be completed in 10 ms or less.

A store operation has priority over RAM read/write operations. If STORE is asserted during a read operation, the read will be discontinued. If STORE is asserted during a RAM write operation, the write will be immediately terminated and the store performed. The data at the RAM address that was being written will be unknown in both the RAM and E<sup>2</sup>PROM.

### ARRAY RECALL

The  $\overline{\text{ARRAY}}$  RECALL input, when LOW, will initiate the transfer of the entire contents of the E<sup>2</sup>PROM array to the RAM array. The transfer of data will typically be completed in 1  $\mu$ s or less.

An array recall has priority over RAM read/write operations and will terminate both operations when ARRAY RECALL is asserted. ARRAY RECALL LOW will also inhibit the STORE input.

### WRITE PROTECTION

The X2201A has three write protect features that are employed to protect the contents of the nonvolatile memory.

- V<sub>CC</sub> Sense—All functions are inhibited when V<sub>CC</sub> is  $\leq$  3V, typically.

- Write Inhibit—Holding either STORE HIGH or ARRAY RECALL LOW during power-up or power-down will prevent an inadvertent store operation and E<sup>2</sup>PROM data integrity will be maintained. It should be noted; whichever method is employed, all control inputs should be stable and the device deselected prior to release of the controlling protection signal.

- Noise Protection—A STORE pulse of less than 20 ns (typical) will *not* initiate a store cycle.

| Part Number | Store Cycles | Data Changes<br>Per Bit |

|-------------|--------------|-------------------------|

| X2201A      | 10,000       | 1,000                   |

#### SYMBOL TABLE

| WAVEFORM | INPUTS<br>Must be<br>steady       | OUTPUTS<br>Will be<br>steady        |

|----------|-----------------------------------|-------------------------------------|

|          | May change<br>from Low to<br>High | Will change<br>from Low to<br>High  |

|          | May change<br>from High to<br>Low | Will change<br>from High to<br>Low  |

| XXXXX    | Don't Care:<br>Changes<br>Allowed | Changing :<br>State Not<br>Known    |

|          | N/A                               | Center Line<br>is High<br>Impedance |