捷多邦·考显PCB升程子科, 24所附加思出资 下-SZ-38

WD7625LP Address, Data,

Hard Disk Buffers and Power

Management Device

**WESTERN DIGITAL**

T-52-38

### Copyright © 1992 Western Digital Corporation All Rights Reserved

Information furnished by Western Digital Corporation is believed to be accurate and reliable. However, no responsibility is assumed by Western Digital Corporation for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Western Digital Corporation. Western Digital Corporation reserves the right to change specifications at any time without notice.

Western Digital, AutoSwitch, and Paradise are registered trademarks and CacheFlow, Caviar, FIT Lab, Hyperseek, Interarchitecture, PinScan, Piranha, SAM, Tidbit, and TrueShade are trademarks of Western Digital Corporation.

Other marks may be mentioned herein that belong to other companies.

### **Western Digital Corporation**

Western Digital Plaza, 8105 Irvine Center Drive, Irvine, CA 92718

### For Service and Literature, call:

(714) 932-4900

| ı | F | T 2 | F | R | N | DТ | 61 | T | ΔI | CORP |

|---|---|-----|---|---|---|----|----|---|----|------|

|   |   |     |   |   |   |    |    |   |    |      |

# 54E D 9718228 0015738 5T7 WWDC TABLE OF CONTENTS T-52-30

| 0       |                                                              | 1-52-38     | _    |

|---------|--------------------------------------------------------------|-------------|------|

| Section | Title                                                        |             | Page |

| 1.0     | INTRODUCTION                                                 |             | . 1  |

|         | 1.1 Document Scope                                           |             | . 1  |

|         | 1.2 Address Buffer Features                                  |             | . 1  |

|         | 1.3 Data Buffer Features                                     |             | . 1  |

|         | 1.4 General Description                                      |             | . 1  |

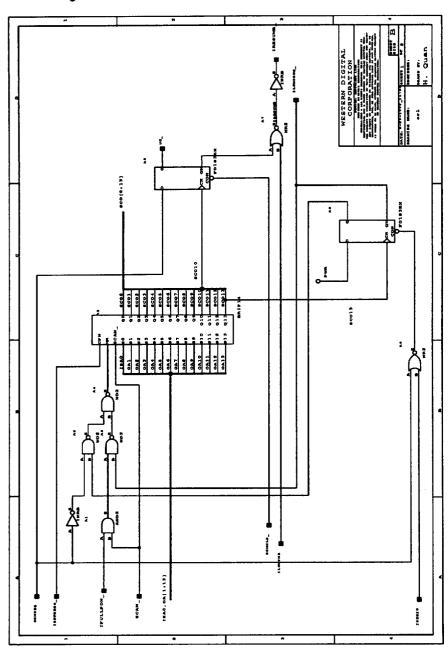

| 2.0     | ARCHITECTURE: ADDRESS BUFFER FUNCTION                        |             | . 3  |

|         | 2.1 AT Address Block                                         |             |      |

|         | 2.2 Power Management Input Multiplexer (PMCIN)               |             | . з  |

|         | 2.3 Power Management Control Register PMCR(0:15)             |             |      |

|         | 2.4 Suspend Resume Logic                                     | . <b></b>   | . 6  |

|         | 2.5 WE Signal Buffering                                      | . <b></b> . | . 6  |

|         | 2.6 Watchdog Timer                                           | . <b></b>   | . 6  |

|         | 2.7 Chip Select Decoding for WD7625LP Data Buffer Function F | Registers   | . 6  |

|         | 2.8 Power On Reset Generation From RSTSW Switch              | . <b></b> . | . 6  |

|         | 2.9 Diagnostic Mode                                          | . <b></b>   | . 6  |

| 3.0     | ARCHITECTURE: DATA BUFFER FUNCTION                           |             | . 7  |

|         | 3.1 AT Data Bus                                              | . <b></b>   | . 7  |

|         | 3.2 DRQ Multiplexing and DACK Demultiplexing                 |             |      |

|         | 3.3 SMEMR, SMEMW Signal Generation                           | . <b></b> . | . 7  |

|         | 3.4 IDE Data Bus Buffer Interface                            |             | . 7  |

|         | 3.5 General Purpose Registers                                | . <b></b>   | . 7  |

|         | 3.6 Mode Control Register                                    | . <b></b>   | . 9  |

|         | 3.6.1 Input Control Signal                                   | . <b></b> . | . 9  |

| 4.0     | STRAPPING OPTION INPUTS                                      | . <b></b> . | . 11 |

| 5.0     | SIGNAL DESCRIPTION                                           |             | . 12 |

|         | 5.1 Address Buffer Function, Mixed Mode Application          |             |      |

|         | 5.2 Address Buffer Function Signal Definition                |             |      |

|         | 5.3 Data Buffer Function, Mixed Mode Application             |             |      |

|         | 5.4 Data Buffer Function Signal Definition                   |             |      |

| 6.0     | POWER SUPPLY MODES                                           |             | . 22 |

|         | 6.1 Input Threshold Adjustment for Different Power Modes     |             |      |

|         | 6.2 Power Supply Consideration and System Power-Down Mod     |             |      |

| WD7625LF               |                                                                                                                                                                                                                         |                                                                                                                     |                                               | T-5 | 52-38                |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|-----|----------------------|

| ESTERN DIGI<br>Section | TAL CORP 54E<br>Title                                                                                                                                                                                                   | D <b>= 9718228</b> C                                                                                                | 1015739                                       | 433 | ■ WDC<br>Page        |

| 7.0                    | DC ELECTRICAL SPECIFICATIO 7.1 Output Valid Times and Volta 7.2 Input Valid Times and Volta 7.3 Output Valid Times and Volta 7.4 Input Valid Voltage Levels a 7.5 5.0 Volt Characteristics 7.6 3.3 Volt Characteristics | tage Levels: Address Buffe<br>ge Levels: Address Buffer<br>tage Levels: Data Buffer Fi<br>and Setup Times: Data Buf | er Function Function . unction . fer Function |     | 23<br>24<br>25<br>26 |

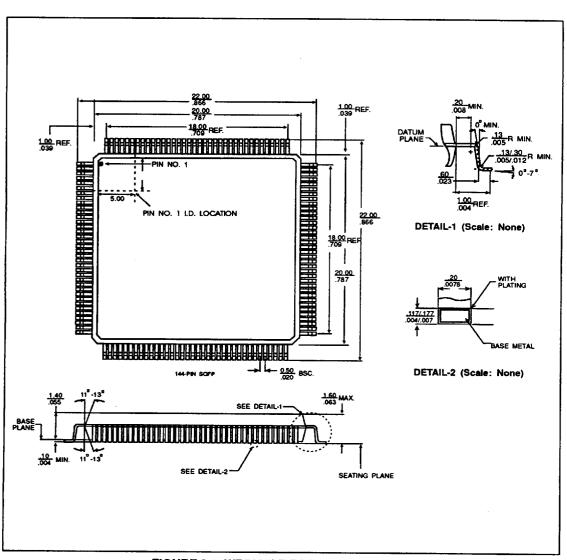

| 8.0                    | PACKAGE DIMENSIONS                                                                                                                                                                                                      |                                                                                                                     |                                               |     | 29                   |

| <b>A.</b> 0            | TEST METHODS  A.1 Tristating the Outputs .                                                                                                                                                                              |                                                                                                                     |                                               |     | 30                   |

| B.0                    | WD7625 PIN ORDER CROSS-RE                                                                                                                                                                                               | FERENCE                                                                                                             |                                               |     | 31                   |

| C.0                    | INPUT THRESHOLD ADJUSTME                                                                                                                                                                                                | NT                                                                                                                  |                                               |     | 36                   |

| D.0                    | I/O REQUIREMENTS  D.1 Address Buffer Mode  D.2 Data Buffer Mode                                                                                                                                                         |                                                                                                                     |                                               |     | 37                   |

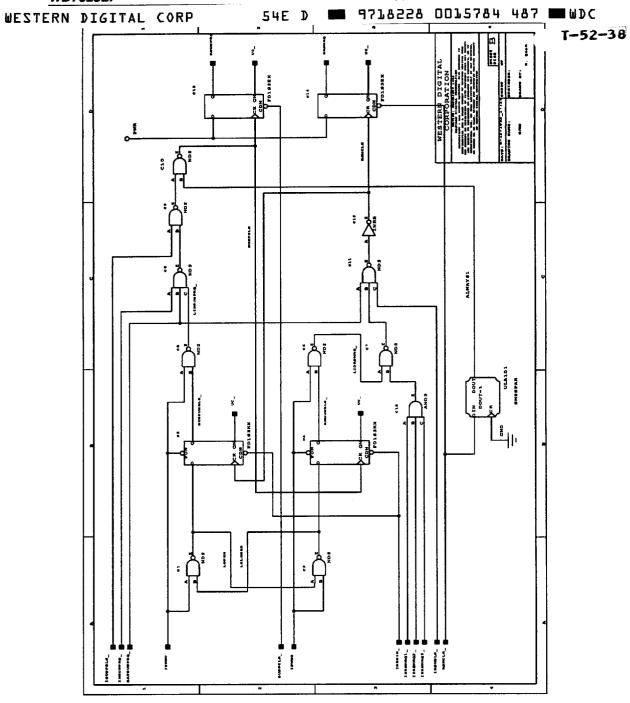

| E.0                    | SUSPEND/RESUME LOGIC SCH                                                                                                                                                                                                | EMATICS                                                                                                             |                                               |     | 42                   |

| F.0                    | REVISION HISTORY                                                                                                                                                                                                        |                                                                                                                     |                                               |     | 45                   |

45

45

F.0

F.1

Initial Release x/x/92

| IJ | Ε | T Z | ERN | DIGI | TAI | CORP |

|----|---|-----|-----|------|-----|------|

|----|---|-----|-----|------|-----|------|

| 54E D 🛮 | 9718228 | 0015740 | 155 | ■ WDC |

|---------|---------|---------|-----|-------|

|---------|---------|---------|-----|-------|

## LIST OF ILLUSTRATIONS

| T | -5 | 2 | -3 | 8 |

|---|----|---|----|---|

|   |    |   |    |   |

| Figure | Page                                  |  |

|--------|---------------------------------------|--|

| 2-1    | WD7625LP Address Buffer Block Diagram |  |

| 3-1    | WD7625LP Data Buffer Block Diagram    |  |

| 5-1    | WD7625LP 144-Pin Diagram              |  |

| 5-2    | WD7625LP 144-Pin Diagram              |  |

| 8-1    | WD7625LP Package Diagram              |  |

### LIST OF TABLES

| Table | Title Page                                          | e |

|-------|-----------------------------------------------------|---|

| 2-1   | Power Management Output Control Register PMCR(7:0)  | 4 |

| 2-2   | Power Management Output Control Register PMCR(15:8) | 4 |

| 2-3   | Power Management Control (Combined)                 | 4 |

| 3-1   |                                                     | 9 |

| 3-2   |                                                     | 9 |

| 5-1   | WD7625LP Pin Assignments (Address Buffer)           | 2 |

| 5-2   | Address Buffer Signal Description                   | 3 |

| 5-3   | WD7625LP Pin Assignments (Data Buffer)              | 8 |

| 5-4   | Data Buffer Signal Description                      | 9 |

| B-1   | WD7625LP Pin Order Cross-Reference                  | 1 |

| C-1   | Input Threshold Adjustment                          | 6 |

| D-1   | I/O Requirements Address Buffer Mode                | 7 |

| D-2   | I/O Requirements Data Buffer Mode                   | - |

T-52-38

### WESTERN DIGITAL CORP

# 1.0 INTRODUCTION

### 1.1 DOCUMENT SCOPE

This document describes the two separate functions: Address Buffer and Data Buffer available in the WD7625LP chip. A strapping input pin selects the Data Buffer Function when strapped low, otherwise it selects the Address Buffer Function.

### 1.2 ADDRESS BUFFER FEATURES

- Allows WD76C10A, WD7855, WD7710, and WD7910 based designs with WD7620/30 for laptop or notebook systems

- Will work in three different power supply modes:

- 3.3V only

- 5V only

- Mix mode 3.3V and 5V

- Direct connect to AT Address Bus SA1:19 and LA17:23 with 24 mA drive

- Power Management Control (PMC) input MUX

- General purpose suspend/resume and power supply control logic

- Fifteen-bit Power Management Control (PMC) output register and control logic

- Low power request and resume signal delay simplify the design of the power supply

- Watchdog timer for system idle detection

- DRAM WE signal from WD7xC10 inversion and buffering

- RESIN output generation from reset switch (RSTSW)

- System Reset generation

- Chip select decoding for registers in the WD7625LP Data Buffer Function

- 144-pin SQFP package

### 1.3 DATA BUFFER FEATURES

- Allows WD76C10A, WD8110, WD7855, WD7710, and WD7910 based designs with WD7620/30 for laptop or notebook systems

- Will work in three different power supply modes:

9718228 0015741 091 **11** WDC

- 3.3V only

- 5V only

54E D

- Mix mode 3.3V and 5V

- Direct connection to AT data bus; 20K integrated pull-up for SD(0:7)

- · Direct connection to IDE data bus

- Two general purpose 8-bit I/O registers:

- Register A

- Register B

- One general purpose 8-bit I/O Register C, with single bit set/reset control

- One general purpose 1-bit I/O Register Y0

- One 4-bit general purpose input only Register Z

- DRQ multiplexing plus 20K integrated pull-down

- DACK demultiplexing

- SMEMR, SMEMW signals plus 22K internal pull-up

- 144-pin SQFP package

#### 1.4 GENERAL DESCRIPTION

The WD7625LP is a combination design which includes two separate functions: Address Buffer and Data Buffer in one chip. A strapping input pin selects the Data Buffer Function if it is strapped low; otherwise, it selects the Address Buffer Function. For designs that use both the data buffer and the address buffer functions, two WD7625LP devices are needed in the system.

In the Address Buffer Function, the WD7625LP is an address buffer and power management chip.

In the Data Buffer Function, the WD7625LP is a data buffer, IDE buffer and I/O register device for the WD7x00 16-bit chip sets.

WESTERN DIGITAL CORP

54E D

When the WD7625LP functions in Address Buffer mode, it replaces 21 "glue"-logic devices in laptop designs with the WD76C20 and WD76C30.

| CHIPS REPLACED | QUANTITY |

|----------------|----------|

| 74ACT573       | 4        |

| 74ACT244       | 3        |

| 74ACT151       | 1        |

| 74HC273        | 2        |

| 74ACT04        | 1        |

| 74HC74         | 2        |

| 74ACT04        | 1        |

| 74HC08         | 1        |

| 74ACT32        | 1        |

| 74ACT125       | 1        |

| 74HC04         | 1        |

| 74ACT14        | 1        |

| 74HC02         | 1        |

| 74HC4020       | 1        |

| TOTAL          | 21 ICS   |

### INTRODUCTION

9718228 0015742 T28 WDC

When the WD7625LP functions in the Data Buffer mode, it it replaces 26 "glue"-logic devices in similar laptop designs.

| CHIPS REPLACED | QUANTITY |

|----------------|----------|

| 74ACT245       | 9        |

| 74ACT373       | 5        |

| 74ACT244       | 4        |

| 74HC151        | 1        |

| 74ACT138       | 3        |

| 74ACT125       | 1        |

| 74ACT273       | 3        |

| TOTAL          | 26 ICS   |

54E D

9718228 0015743 964 WDC

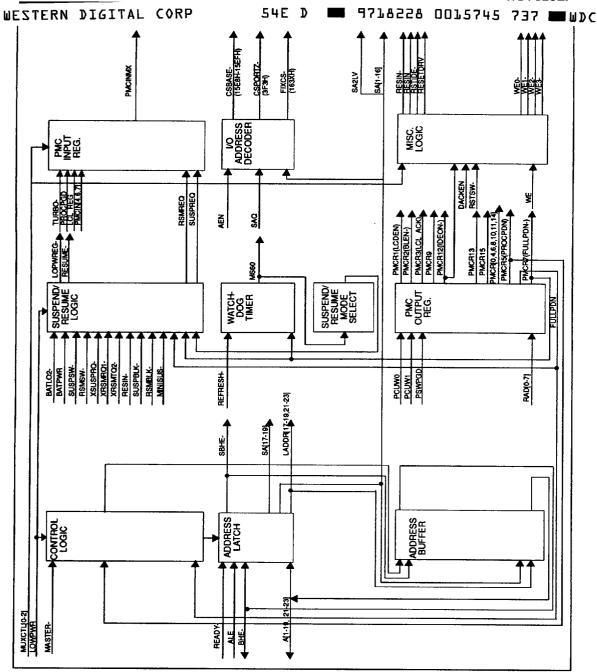

### 2.0 ARCHITECTURE: ADDRESS BUFFER FUNCTION

The following section describes the functions of the various internal blocks in the Address Buffer mode of the WD7625LP as a 144-pin device supporting 16-bit processors.

#### 2.2 **POWER MANAGEMENT INPUT MULTIPLEXER (PMCIN)**

T-52-38

This logic multiplexes the PMCIN signals with the help of MXCTL0:2 according to the following table.

1

PMC(7)

| 2.1 AT ADDRESS BLOCK                                                                                |   | MXCTL2 | 2:0 | SIGNAL  |

|-----------------------------------------------------------------------------------------------------|---|--------|-----|---------|

| This block takes in A1:A23 from the processor                                                       | 0 | 0      | 0   | TURBO   |

| and latches it internally with ALE and READY sig-<br>nals. MASTER, when high, drives the address on | 0 | 0      | 1   | PROCPGD |

| to SA1:SA19 and LA17:23. The buffers on the                                                         | 0 | 1      | 0   | LCL_REQ |

| lines can drive 24 mA for compatibility with the AT address bus. When MASTER is low, the address    |   | 1      | 1   | RESUME  |

| from the AT bus is driven to A1:A23.                                                                | 1 | 0      | 0   | PMC(4)  |

|                                                                                                     | 1 | 0      | 1   | SUSPREQ |

|                                                                                                     | 1 | 1      | 0   | PMC(6)  |

1

1

# T

### WESTERN DIGITAL CORP

54E D

# 2.3 POWER MANAGEMENT CONTROL REGISTER PMCR(0:15)

This is a 16-bit general purpose write only register for power management control. The PCUW0 control signal writes PMCR(0:7) and PCUW1 writes

### ARCHITECTURE: ADDRESS BUFFER FUNCTION

9718228 0015744 8T0 10 0 C

PMCR(8:15) bits. All bits (except Bit 0) of the

PMCR are available on pins of the WD7625LP. A

typical bit assignment for the PMCR register is

shown in the tables below.

T-52-38

| 7       | 6     | 5       | 4     | 3      | 2    | 1     | 0        |

|---------|-------|---------|-------|--------|------|-------|----------|

| FULLPON | PMCR6 | PROCPDN | PMCR4 | PMCR3  | BLEN | LCDEN | Not Used |

|         |       |         |       | LCLACK |      |       |          |

TABLE 2-1. POWER MGMENT OUTPUT CONTROL REGISTER PMCR(7:0)

| 15     | 14     | 13     | 12     | 11     | 10     | 9     | 8     |

|--------|--------|--------|--------|--------|--------|-------|-------|

| PMCR15 | PMCR14 | PMCR13 | IDEON  | PMCR11 | PMCR10 | PMCR9 | PMCR8 |

|        |        |        | PMCR12 |        |        |       |       |

TABLE 2-2.POWER MGMENT OUTPUT CONTROL REGISTER PMCR(15:8)

| PMC<br>PIN | WD7X10<br>SIGNAL      | S/W<br>CTRL    | WD7625<br>SIGNAL | INITIAL<br>STATE |

|------------|-----------------------|----------------|------------------|------------------|

| 0          | CPU Clk Driver Enable | N              | N/A*             | N/A              |

| 1          | LCD Enable            | opt./timer     | LCDEN            | L                |

| 2          | Backlight Enable      | opt./timer     | BLEN             | H**              |

| 3          | LCL_ACK               | N <sub>1</sub> | LCL_ACK          | L                |

| 4          | LCL_ATN               | N              | PMCR4            | L                |

| 5          | Processor Power Down  | N              | PROCPDN          | L                |

| 6          | Gate A20              | N              | PMCR6            | L                |

| 7          | Full Power Down       | N              | FULLPDN          | L                |

| 8          | User Defined          | Υ              | PMCR8            | L                |

| 9          | User Defined          | Υ              | VGADN            | H**              |

| 10         | User Defined          | Υ              | PMCR10           | L                |

| 11         | User Defined          | Υ              | PMCR11           | L                |

| 12         | User Defined          | Υ              | IDEON            | L                |

| 13         | User Defined Y        |                | PMCR13           | L                |

| 14         | User Defined Y        |                | PMCR14           | L                |

| 15         | User Defined          | Υ              | PMCR15           | L                |

### TABLE 2-3. POWER MANAGEMENT CONTROL (COMBINED)

<sup>\*</sup> The 7x10 supports a hardware strap option in place of DRQ4 on the DRQ input multiplexer. This selects whether the CPUCLK pin on the 7x10 is an input or output. If configured as an input, PCMR0(CPU Clock Driver Enable) can be used to change the output mode. PMCR0 tristates the external clock oscillator. In practice, however, no design ever configured CPUCLK as an input. Therefore support for this option was dropped in the WD7625LP so that the PMCR0 pin could be used for other purposes. Thus, PMCR0 is not brought out to a pin in this device.

<sup>\*\*</sup> Note that these outputs have opposite initial polarity from the previous discrete implementation.

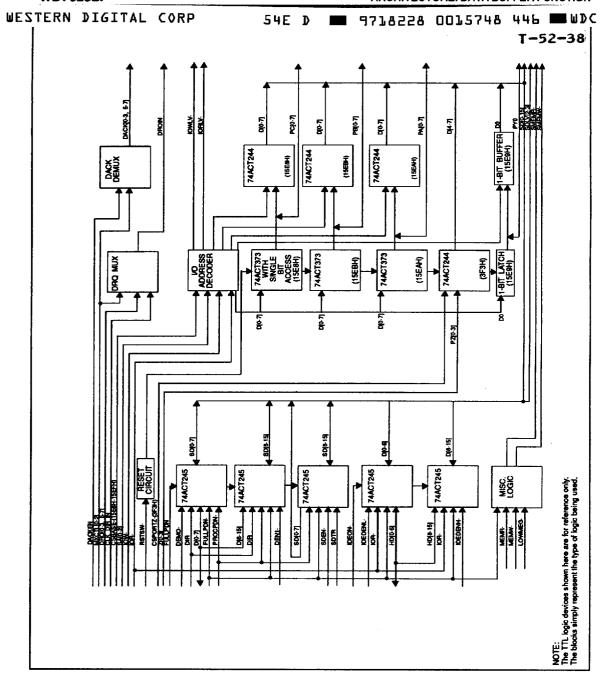

FIGURE 2-1. WD7625LP ADDRESS BUFFER BLOCK DIAGRAM

WESTERN DIGITAL CORP

54E D

### 2.4 SUSPEND/RESUME LOGIC

The suspend/resume logic supports two modes of the circuit. The two modes differ in the way the Suspend/Resume switch is used. One mode allows the switch to be used as a momentary switch to generate Suspend and Resume requests. The other mode allows a two position single-pole, double-throw switch to be used to indicate a lid open or closed condition. The circuits provide all signals necessary for automatically generating suspend/resume requests depending upon signals from the battery and also generate Low Power Request signals to put the power supply in low power mode. See the block diagrams of both modes. The Strap input option generates the signal SRMODESEL which selects one of the two modes.

For a power supply which does not provide a LOWPWR output pin, this input pin to the WD7625LP needs to be tied to ground.

### 2.5 WE SIGNAL BUFFERING

The WD7625LP takes in an active high WE signal from the WD7610A and drives four active low write enable signals for the DRAM banks. WE0, WE1, WE2 and WE3 are designed to drive high capacitance loads of 150 pf. Each can handle two banks of DRAMs.

### 2.6 WATCHDOG TIMER

The watchdog timer is used to detect system inactivity. It is clocked with a refresh signal and generates a 120 millisecond elapsed signal which can be connected to an unused PMCIN mux input. During suspend, this watchdog timer is halted.

The watchdog timer signal is only need with the WD76C10A and similar devices. The WD7855 and new devices do not require a watchdog timer.

ARCHITECTURE: ADDRESS BUFFER FUNCTION

### 9718228 0015746 673 WDC

# 2.7 CHIP SELECT DECODING FOR WD7625LP DATA BUFFER FUNCTION REGISTERS

The chip select decoding generates a chip select base I/O address for the general purpose registers in the WETS25LP Data Buffer Function. The CSBASE (15E3H to 15EFH) is further decoded inside the WD7625LP Data Buffer Function along with SA0, SA1, SA2. The CSPORTZ is another fixed chip select (03F3H) for the register in the WD7625LP Data Buffer Function. FIXCS is decoded for the address range of 1630H to 163FH.

# 2.8 POWER ON RESET GENERATION FROM RSTSW SWITCH

The RSTSW signal has a Schmitt trigger input on the Reset Switch and generates all the active low and active high resets needed in the system.

### 2.9 DIAGNOSTIC MODE

If PMCR[15:8] is set to AA, 55, and AA in coincidence with three reads or writes at address 9872H, the WD7625LP Address Buffer Function is set to diagnostic mode. In this mode eight internal signals can be read at output pin PMCIN as shown in the following table.

|   | MXCTL | SIGNAL |          |

|---|-------|--------|----------|

| 0 | 0     | 0      | RSMCLK   |

| 0 | 0     | 1      | SUSPCLK  |

| 0 | 1     | 0      | RSUSPRQ  |

| 0 | 1     | 1      | RSMREQ   |

| 1 | 0     | 0      | SUSPCLR  |

| 1 | 0     | 1      | RSMCLR   |

| 1 | 1     | 0      | SCAN     |

| 1 | 1     | 1      | ILOWPREQ |

See the appendix for further testing information.

Note: the diggnostic mode is for in-house testing only.

54E D = 9718228 0015747 50T = WDC

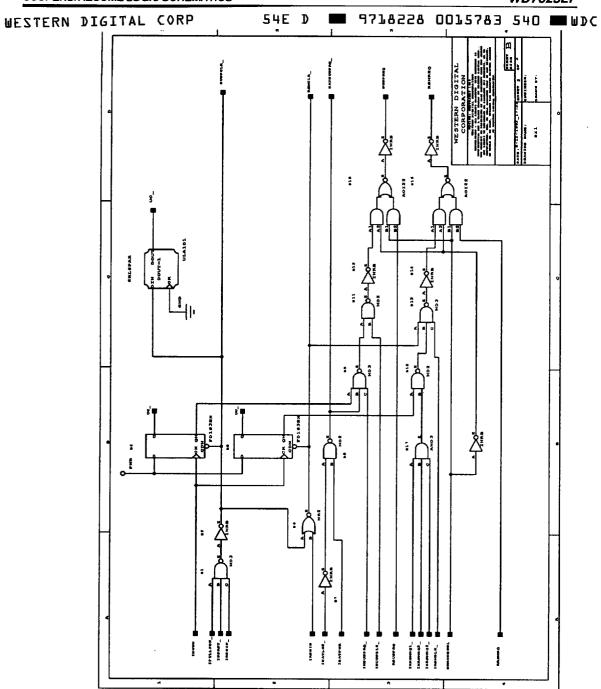

#### **ARCHITECTURE: DATA BUFFER FUNCTION** 3.0

The following section describes the functions of the various internal blocks in the Data Buffer Function of the WD7625LP as a 144-pin device supporting 16-bit processors.

#### 3.1 **AT DATA BUS**

This block takes in D0:15 from the processor and connects it to the SD0:15 AT data bus, the IDE data bus, and the other general purpose registers internally. The buffers on the SD0:15 lines can drive 24 mA for compatibility with an AT address bus. The low order byte SD0:7 has an internal pull-up.

#### DRQ MULTIPLEXING AND DACK 3.2 **DEMULTIPLEXING**

The WD7625LP Data Buffer Function multiplexes the DRQ signals onto DRQIN with MXCTL0:2 signals. Together with the DACKEN signal, the MXCTL0:2 signals are demultiplexed onto the DACK0:3 DACK5:7 signals. The following tables show the multiplexer assignments.

|   | MXCTL | 2:0 | DRQIN SIGNAL |  |  |

|---|-------|-----|--------------|--|--|

| 0 | 0     | 0   | DRQ0         |  |  |

| 0 | 0     | 1   | DRQ1         |  |  |

| 0 | 1     | 0   | DRQ2         |  |  |

| 0 | 1     | 1   | DRQ3         |  |  |

| 1 | 0     | 0   | Logic Low    |  |  |

| 1 | 0     | 1   | DRQ5         |  |  |

| 1 | 1     | 0   | DRQ6         |  |  |

| 1 | 1     | 1   | DRQ7         |  |  |

|   | MXCTL | 2:0 | DACK SIGNAL |

|---|-------|-----|-------------|

| 0 | 0     | 0   | DACKO       |

| 0 | 0     | 1   | DACK1       |

| 0 | 1     | 0   | DACK2       |

| 0 | 1     | 1   | DACK3       |

| 1 | 0     | 0   | NA          |

| 1 | 0     | 1   | DACK5       |

| 1 | 1     | 0   | DACK6       |

| 1 | 1     | 1   | DACK7       |

#### SMEMR, SMEMW SIGNAL 3.3 GENERATION

This logic takes in LOWMEG, MEMR, and MEMW signals. Whenever LOWMEG is low. either SMEMR or SMEMW is driven low depending upon the MEMR or the MEMW signals. The SMEMR and SMEMW signals support a 24 mA drive and can be directly connected to an AT bus.

#### IDE DATA BUS BUFFER INTERFACE 3.4

The IDE data buffer connects the CPU data bus to the IDE data bus and is controlled by the IDEDENL and IDEDENH signals. IDE Bit 7 is muxing with the Disk Change signal of the floppy controller inside the WD7621 and is accessible through bit SD7.

#### GENERAL PURPOSE REGISTERS 3.5

There are four general purpose registers in the WD7625LP Data Buffer Function. Three of them, Register A, Register B, and Register C are 8-bit I/O registers. Register C also has an individual Set/Reset control. Register Y is a 1-bit I/O register.

Register Z is a 4-bit input only register.

There is a mode control register which selects different modes for A and B ports. The mode control register is described in the next section.

FIGURE 3-1. WD7625LP DATA BUFFER FUNCTION BLOCK DIAGRAM

| dE: | STERN DIGITAL CORP                      | 54E D  |     |     | 382 <b>W</b> W | ) C |

|-----|-----------------------------------------|--------|-----|-----|----------------|-----|

|     | REGISTER                                | CSBASE | SA2 | SA1 | SA0            |     |

|     | Mode Control Write Only (15EC)          | 0      | 1   | 0   | 0              |     |

|     | Bit Set/Reset Control-Register C (15ED) | 0      | 1   | 0   | 1              |     |

|     | Reserved                                | 0      | 1   | 1   | 0              |     |

|     | Reserved                                | О      | 1   | 1   | 1              |     |

|     | Register Y Read/Write (15E9)            | 0      | 0   | 0   | 1              |     |

|     | Register A Read / Write (15EA)          | 0      | 0   | 1   | 0              | 1   |

|     | Register B Read / Write (15EB)          | 0      | 0   | 1   | 1              | il. |

|     | Register C Read / Write (15E8)          | 0      | 0   | 0   | 0              | 1   |

**TABLE 3-1. GENERAL PURPOSE REGISTERS**

Port Z address is fixed at 03F3H.

### 3.6 MODE CONTROL REGISTER

| MOD1 | MOD0 | L1H3 | T1 | DIR Y | DIRC | DIR B | DIRA |

|------|------|------|----|-------|------|-------|------|

|      |      |      |    |       |      |       |      |

Bit T1 is the test bit used for fault coverage testing only. Always set this bit to zero when writing this register.

MODE 0: Simple Input/Output mode. All registers A, B, C, and Y are in normal read/write mode and the port pins can be programmed as input or output pins with DIR Y, DIR C, DIR B, and DIR A control bits in the control register. The outputs on the ports are latched and driven onto the pins continuously. The inputs are not latched and directly come from the input pins of the port.

MODE 1: In this mode, Port A (address 15EA) can be programmed as a strobed input or output mode. This configuration provides a means of transferring I/O data to or from a specified port in conjunction with strobes or "handshaking" signals. In this mode Port A uses four lines from Port C PC(0:3) for handshaking.

L1H3: This bit serves the same function as the primary input pin 141 FSAD in the Address Buffer mode. It is used to control the buffer strength of the SD output buffers. On power up reset, this bit is cleared to logic 0, which reduces the SD output buffers to approximately 3/5ths of their maximum strength. By setting this bit to logic 1, the full buffer strength will be achieved. This method of buffer strength setting is very useful in controlling ground bounce and signals overshooting in minimum loaded laptop systems.

### 3.6.1 Input Control Signal

STB: Strobe Input: A low on this input loads data into an input latch. STBA (Port C, Bit 0) and STBB (Port C, Bit 4) are bits defined for Port A and Port B.

IBF: Input buffer full: A high on this output indicates that the data has been loaded into the input latch. IBF is set when the STB input is low and is reset by the rising edge of the IOR signal on the same port. IBFA (Port C, Bit 1) and IBFB (Port C, Bit 5).

| MOD 1 | MOD 0 | MOD#                                  | CONDITION                                 |

|-------|-------|---------------------------------------|-------------------------------------------|

| 0     | 0     | Mode 0                                | Normal Mode                               |

| 0     | 1     | Mode 1 Strobed Input or Output Port A |                                           |

| 1     | 0     | Mode 2 Strobed Input or Output Port B |                                           |

| 1     | 1     | Mode 3                                | Both Port A and Port B are Strobed I or O |

TABLE 3-2. MODE CONTROL REGISTER MODE 1 AND MODE 0

ARCHITECTURE: DATA BUFFER FUNCTION

WESTERN DIGITAL CORP

54E D

OBF: Output buffer full: The OBF output goes low to indicate that the CPU has written data to the port. The OBF flip-flop is set low by the IOW signal to the port and is set high when the ACK input is low. OBFA (Port C, Bit 2) and OBFB (Port C, Bit 6).

ACK: Acknowledge input: A low on this input means that data from the port has been accepted by the device. ACKA (Port C, Bit 3) and ACKB (Port C, Bit 7).

During Mode 1: The Port C bits are as defined above and the DIR C bit in the control word is applicable to the upper nibble only. A read on Port C reflects the following

| Fi |     |    | 1   | AGUA | ODEA | IDEA | STBA |

|----|-----|----|-----|------|------|------|------|

|    | 1/0 | VO | 100 | ACKA | OBFA | IRLA | SIBA |

MODE 2: In this mode, Port B (address 15EB) can be programmed as a strobed input or output mode. This configuration provides a means of transferring I/O data to or from a specified port in conjunction with strobes or "handshaking" signals. In this mode Port B uses four lines from Port C PC(4:7) for handshaking.

During Mode 2: The Port C bits are as defined above and the DIR C bit in the control word affects only the lower nibble. A read on Port C reflects the following

| ACKB | OBFB | IBFB | STBB | 1/0 | 1/0 | 1/0 | 1/0 | l |

|------|------|------|------|-----|-----|-----|-----|---|

MODE 3: Both Port A and Port B are programmed for strobed I/O mode and all bits in Port C are used for control signals for both ports as defined in Mode 1 and Mode 2.

| FA   STBA | IBFA STB | IBFA | OBFA | ACKA   | STBB | IBFB | OBFB | ACKB  |

|-----------|----------|------|------|--------|------|------|------|-------|

|           |          | ĺ    | 1 1  |        |      | l    | l    | l .   |

|           | "        |      |      | ,,,,,, | 0.55 |      | 00.0 | 1,0,0 |

Port Y (address 15E9) always operates in Mode 0 regardless of bits MOD0 and MOD1 in the Mode Control Register. The system will read in Port Y0 through data bits D0. A "0" at DIR Y indicates that Port Y is in input mode.

9718228 0015750 0T4 WDC

The following table shows the direction control bits in mode control.

T-52-38

| С | В | Α | PORT C | PORT B | PORT A |

|---|---|---|--------|--------|--------|

| 0 | 0 | 0 | Input  | Input  | Input  |

| 0 | 0 | 1 | Input  | Input  | Output |

| 0 | 1 | 0 | Input  | Output | Input  |

| 0 | 1 | 1 | Input  | Output | Output |

| 1 | 0 | 0 | Output | Input  | Input  |

| 1 | 0 | 1 | Output | Input  | Output |

| 1 | 1 | 0 | Output | Output | Input  |

| 1 | 1 | 1 | Output | Output | Output |

BIT SET/RESET CONTROL FOR PORT C: There are two ways of programming Port C's bits. One is normal read/write where all eight bits of Port C are written by writing to the port Base address.

The Port C bits can also be written one bit at a time by writing to the port Base + 5 address. The following is the data format for port Base + 5 address:

| X     | X    | X      | X      | Data B*        | BA2    | BA1   | BAO  |

|-------|------|--------|--------|----------------|--------|-------|------|

| *DATA | Bist | he dat | a bein | g written to a | bit as | addre | ssed |

| by BA | 2:0. |        |        |                |        |       |      |

If DATA B = 1, the bit is set. If DATA B = 0 the bit is reset

During Mode 0, all bits 0:7 of Port C can be used for the Bit Set/Reset Function. During Mode 1 or Mode 2, only those bits which are not used for control signals are available for this function.

### 54E D = 9718228 0015751 T30 = WDC

T-52-38

### 4.0 STRAPPING OPTION INPUTS

The WD7625LP operates in two different functions and with up to three voltage supply modes. Therefore it is necessary to select the function in which the chip operates and to provide information to the input/output buffers for the appropriate threshold adjustments required because of the different VDD values.

The WD7625LP has six strapping options. Three of the options are mode specific:

- Two of the options are for the Address Buffer Function mode only. These two options select:

- the Suspend/Resume mode required

- the buffer strength of the SA and LA buses

- Another option is for the Data Buffer Function mode only. This option adjusts the threshold of the hard disk I/O buffers along with the voltage supplied to the IDE.

- The other three options are:1

- Function Address/Data Buffer mode select

- 3.3V only mode

- 5 V only mode

All strapping inputs except the buffer strength select are monitored during power-up reset, and are latched when reset goes away. The strapping input for the buffer strength select is dynamic. If any strapping pin is left unconnected, the input will evaluate high due to an internal pull-up device. The internal pull-up is only active during Reset except for the buffer strength strap.

The table below illustrates all the allowed settings for the strapping signals.

The 3.3 V only mode is not allowed with a 5 V hard disk supply.

To select logic low (0), a 5K to 15K external pull-down resistor is required for each strapping input.

| SIGNAL PINS                                   | LOGIC STATE LOW (0)                            | LOGIC STATE HIGH (1)                     |

|-----------------------------------------------|------------------------------------------------|------------------------------------------|

| Pin 67 (CSBASE)                               | All VDDs are 3.3V                              | Mixed mode supply, if pin 66 is high     |

| Pin 66 (CSPORTZ)                              | All VDDs are 5V                                | Mixed mode supply, if pin 67 is high     |

| Pin 63 (SA2LV/IORLV)                          | Select Data Buffer Function                    | Select Address Buffer Function           |

| Pin 70 (SD2LV)<br>(Data Buffer mode only)     | VDDHD is 3.3V                                  | VDDHD is 5V                              |

| Pin 141 (FSAD)<br>(Address Buffer mode only)  | Select full strength of SA and LA buffers      | Select 3/5 strength of SA and LA buffers |

| Pin 113 (MS120)<br>(Address Buffer mode only) | Use momentary switch type for suspend - resume | Use lid switch type for suspend - resume |

<sup>&</sup>lt;sup>1</sup> Driving the 3.3 V only and 5 V only straps both low is an illegal combination. The WD7625LP assumes a mixed voltage scenario when both of these straps are allow to float to high.

### 5.0 SIGNAL DESCRIPTION

#### ADDRESS BUFFER FUNCTION, MIXED 5.1 **MODE APPLICATION**

In 5V or 3.3V only applications all VDD5 and VDD3 signals are tied to the same power supply plane. In mixed mode applications two different kinds of power supply pins, VDD3 and VDD5 are used. The normal signal pins stay unaffected.

FIGURE 5-1. 144-PIN DIAGRAM

Signals - 122 VDDs - 2 VDD2 - 7 GND

|                    |                  | Signals = 122 VDD5 = | 3 VDD3 = 7 GND = 12 |

|--------------------|------------------|----------------------|---------------------|

| PIN-NAME           | PIN-NAME         | PIN-NAME             | PIN-NAME            |

| 1-PMCR8            | 37-SA11          | 73-XRSMRQ1           | 109-A21             |

| 2-PMCR10           | 38-SA12          | 74-XRSMRQ2           | 110-A22             |

| 3-PMCR11           | 39-SA13          | 75-XRSMRQ3           | 111-A23             |

| 4-PMCR14           | 40-SA14          | 76-RSTSW             | 112-BHE             |

| 5-ALE              | 41-SA15          | 77-READY             | 113-MS120           |

| 6-WE               | 42-SA16          | 78-VSS               | 114-SUSPBLK         |

| 7-VSS              | 43-VSS           | 79-SUSPSW            | 115-RSMBLK          |

| 8-LCDEN            | 44-SA17          | 80-RSMSW             | 116-MINISUS         |

| 9-BLEN             | 45-SA18          | 81-MXCTL0            | 117-P5VPGD          |

| 10-LCL_ACK         | 46-SA19          | 82-MXCTL1            | 118-VDD5            |

| 11-VDD3            | 47-VDD5          | 83-MXCTL2            | 119-RAD0            |

| 12-PMCR9           | 48-SBHE          | 84-VDD3              | 120-VDD3            |

| 13-IDEON/PMCR12    | 49-VSS           | 85-DACKEN            | 121-RAD1            |

| 14-RSTIDE          | 50-RESET         | 86-RESIN             | 122-RAD2            |

| 15-VDD3            | 51-LA17          | 87-VSS               | 123-RAD3            |

| 16-WE0             | 52-LA18          | 88-A1                | 124-RAD4            |

| 17-WE1             | 53-LA19          | 89-A2                | 125-RAD5            |

| 18-WE2             | 54-LA21          | 90-A3                | 126-RAD6            |

| 19- <del>WE3</del> | 55-LA22          | 91- <b>A</b> 4       | 127-RAD7            |

| 20-PMCR13          | 56-LA23          | 92-A5                | 128-PCUW0           |

| 21-PMCR15          | 57-VSS           | 93-A6                | 129-PCUW1           |

| 22-PROCPDN         | 58-SA0           | 94-A7                | 130-TURBO           |

| 23-RESIN           | 59-MASTER        | 95-A8                | 131-VSS             |

| 24-VSS             | 60-AEN           | 96-A9                | 132-PROCPGD         |

| 25-SA1             | 61-REFRESH       | 97-VDD3              | 133-LCL_REQ         |

| 26-SA2             | 62-VSS           | 98-A10               | 134-PMCIN4          |

| 27-SA3             | 63- <u>SA2LV</u> | 99-A11               | 135-PMCIN6          |

| 28-SA4             | 64-LOWPREQ       | 100-A12              | 136-PMCIN7          |

| 29-SA5             | 65-PMCINMX       | 101-A13              | 137-LOWPWR          |

| 30-VSS             | 66-CSPORTZ       | 102-A14              | 138-RESUME          |

| 31-SA6             | 67-CSBASE        | 103-A15              | 139-FIXCS           |

| 32-VDD5            | 68-VDD3          | 104-A16              | 140- <u>VSS</u>     |

| 33-SA7             | 69-BATPWR        | 105-VSS              | 141-FSAD            |

| 34-SA8             | 70-BATLO2        | 106-A17              | 142-VDD3            |

| 35-SA9             | 71-FULLPDN       | 107-A18              | 143-PMCR4           |

| 36-SA10            | 72-XSUSRQ        | 108-A19              | 144-PMCR6           |

TABLE 5-1. WD7625LP PIN ASSIGNMENTS (ADDRESS BUFFER)

SIGNAL DESCRIPTION WD7625LP

WESTERN DIGITAL CORP

5.2 ADDRESS BUFFER FUNCTION

SIGNAL DEFINITION

54E D 9718228 0015753 803 11 WDC

| PIN                                                             | MNEMONIC                   | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                            |

|-----------------------------------------------------------------|----------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 32, 47, 118                                                     | VDD5                       |     | 5V power inputs.                                                                                                                                                                                                                                                                                       |

| 68, 84,<br>120, 142,<br>11, 15                                  | VDD3                       |     | 3.3V power inputs.                                                                                                                                                                                                                                                                                     |

| 24, 30,<br>43, 49,<br>57, 62,<br>78, 87,<br>105, 131,<br>140, 7 | vss                        |     | Ground pins.                                                                                                                                                                                                                                                                                           |

| 85                                                              | DACKEN                     | ļ   | DACK Enable DACK enable input.                                                                                                                                                                                                                                                                         |

| 130                                                             | TURBO                      | l   | TURBO TURBO switch input. Connected to the PMCIN multiplexer Bit 0.                                                                                                                                                                                                                                    |

| 132                                                             | PROCPGD                    | 1   | Processor Power Good Processor Power Good signal indicating that power has been applied to the CPU and it has reached acceptable levels. Connected to the PMCIN multiplexer Bit 1.                                                                                                                     |

| 133                                                             | LCL_REQ                    | I   | Local Access Request Local Access Request from Keyboard controller. Connected to PMCIN mux Bit 2.                                                                                                                                                                                                      |

| 134<br>135<br>136                                               | PMCIN4<br>PMCIN6<br>PMCIN7 | I   | Power Management Control Inputs 4, 6, and 7 General Purpose input for the PMCIN multiplexer connected to bits 4, 6, and 7.                                                                                                                                                                             |

| 113                                                             | MS120                      | 1/0 | 120 Millisecond Watchdog Timer Strobe Output for the watchdog timer MS120 signal. At power-up, this pin is an input whose state determines whether a lid switch type or a momentary switch type will activate the internal suspend/resume circuitry. See Strapping Options Inputs section for details. |

| 65                                                              | PMCINMX                    | 0   | Power Management Control Input Multiplexed This is the output of the PMCIN signals multiplexed with MXCTL0:2. Goes directly to the PMCIN pin of the WD7610.                                                                                                                                            |

| 67                                                              | CSBASE                     | I/O | Chip Select Base The active low Base Chip Select for the general purpose R/W registers of the WD7625LP Data Buffer Function. At Reset, this pin is an input whose state determines whether the chip will operate in a 3.3V system or mixed mode. See Strapping Options Inputs section for details.     |

TABLE 5-2. ADDRESS BUFFER SIGNAL DESCRIPTION

| 54E | D |  | 9718228 | 0015754 | 74T | ■ WDC |

|-----|---|--|---------|---------|-----|-------|

|-----|---|--|---------|---------|-----|-------|

| PIN                                            | MNEMONIC                                                     | l vo l | DESCRIPTION T-52-38                                                                                                                                                                                                                                                                                                                           |

|------------------------------------------------|--------------------------------------------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 66                                             | CSPORTZ                                                      | 0      | Chip Select Port Z  Active chip selects for read only Port Z in the WD7625LP Data  Buffer Function. At power on reset, this pin is an input whose state determines whether the chip will operate in a 5V system or mixed mode. See Strapping Options Inputs section for details                                                               |

| 8<br>9<br>10<br>143<br>22<br>144               | LCDEN BLEN LCL_ACK/ PMCR3 PMCR4 PROCPDN PMCR6 FULLPDN        | 0      | Power Management Control Register Outputs These are general purpose outputs of the Power Management Control Register (PMCR[0:15]). All the bits of the PMCR are available on the pins of the WD7625LP. Since the clock direction is always tied low internally, the output to PMCR0 for OSC control is omitted. LCDEN is the ouput for PMCR1; |

| 71<br>1<br>12<br>2<br>3<br>13<br>20<br>4<br>21 | PMCR8 PMCR9 PMCR10 PMCR11 IDEON/ PMCR12 PMCR13 PMCR14 PMCR15 |        | RSTIDE (pin 14) output is gated by PMCR12/IDEON.                                                                                                                                                                                                                                                                                              |

| 128<br>129                                     | PCUW0<br>PCUW1                                               | ı      | Power Control Unit Write Strobe 0 and 1 Control signal to clock PMCR Register Bits 0:7 and 8:15 as generated by the WD76C20ALV.                                                                                                                                                                                                               |

| 112<br>88-96,<br>98-104,<br>106-111            | BHE<br>A1-19<br>A21-23                                       | 1/0    | Bus High Enable CPU Address 1 to 19 CPU Address 21 to 23 Input from the CPU or DMA when MASTER is high. The CPU address bus A1:19, A21:23 and BHE are directly connected to these pins. The address bus is latched and output onto LA17:23 and SA1:19.                                                                                        |

| 48<br>25-29, 31,<br>33-42                      | SBHE<br>SA1-16                                               | 1/0    | System Bus High Enable System Address 1 to 16 Output to AT address bus when MASTER is high. A1:19, A21:23 and BHE are latched internally with ALE and driven onto these pins.                                                                                                                                                                 |

| 44-46                                          | SA17-19                                                      | 0      | System Address 17 to 19 Output AT address bus in non-master mode.                                                                                                                                                                                                                                                                             |

TABLE 5-2. ADDRESS BUFFER SIGNAL DESCRIPTION (CONTINUED)

MINISUS

WEO

WE1

WE2

WE3

P5VPGD

ı

0

0

0

0

| TERN D               | IGITAL COR                                       |     | 54E D 📟 9718228 0015755 686 🟙 🖦                                                                                                                                                                                         |

|----------------------|--------------------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN                  | MNEMONIC                                         | NO  | DESCRIPTION T-52-3                                                                                                                                                                                                      |

| 51-53,<br>54-56      | LA17-19<br>LA21-23                               | 1/0 | Early Address 17 to 19 Early Address 21 to 23 Output when MASTER is high. A17-A19 and A21-23 are latched with READY signal when low. If MASTER is low, LA17:19, LA21:23 are input and are driven onto A17:19, A21:23.   |

| 77<br>149<br>59      | READY<br>ALE<br>MASTER                           |     | Ready Address Latch Enable Master Control Signals for latching and output enable for latches for the AT Address Bus.                                                                                                    |

| 80                   | RSMSW                                            | 1   | Resume Switch Resume switch input.                                                                                                                                                                                      |

| 72<br>73<br>74<br>75 | XSUSPRQ<br>XRSMRQ1<br>XRSMRQ2<br>XRSMRQ3         | •   | External Suspend Request External Resume Request External suspend request and external resume request. These pins are used in the Suspend/Resume circuit.                                                               |

| 114<br>115           | SUSPBLK<br>RSMBLK                                | 1   | Suspend Request Circuit Block Resume Request Circuit Block These general purpose signals are used in the suspend request circuit to block a suspend request or a resume request from the external circuit, if required. |

| 64                   | LOWPREQ                                          | -   | Low Power Request  Active low output from the suspend resume circuit requesting the power supply to go into low power mode.                                                                                             |

| 69<br>70             | BATPWR<br>BATLO2                                 |     | Battery Power Battery Power Low Inputs to the Suspend/Resume circuitry from the power supply indicating when battery power is being used and if the battery power is low.                                               |

| 81<br>82<br>83       | MXCTL0<br>MXCTL1<br>MXCTL2                       | 1   | Multiplexer Control 0, 1 and 2 PMCIN multiplexer control inputs.                                                                                                                                                        |

|                      | <del>                                     </del> |     |                                                                                                                                                                                                                         |

TABLE 5-2. ADDRESS BUFFER SIGNAL DESCRIPTION (CONTINUED)

Write Enable 0, 1, 2 and 3

Power to 5V Power Good

Each can drive 150 pf.

clears the Suspend/Resume D-flip-flops.

Indicates that power to the 5V power bus is stable.

When active enables resume request flip-flop signal. A toggle also

Active low buffered DRAM Write signal. One signal for each bank.

Mini Suspend

116

16

17

18

19

117

WESTE

| RN DIG         | ITAL CORP      |     | 54E D 📟 9718228 0015756 512 🖦 WDC                                                                                                                                                                                                                                                                       |

|----------------|----------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN            | MNEMONIC       | VO  | DESCRIPTION T-52-38                                                                                                                                                                                                                                                                                     |

| 119<br>121-127 | RAD0:7         | t   | RAM Address Bus RAD0:7 input bus for writing into the PMCR Register.                                                                                                                                                                                                                                    |

| 6              | WE             | 1   | Write Enable Active high WE signal from the WD76C10A for DRAM write. Generates WE0:3.                                                                                                                                                                                                                   |

| 23<br>84       | RESIN<br>RESIN | 0   | System Reset Output Active low RESIN and active high RESIN power on reset signals. Generated from the RSTSW input signal.                                                                                                                                                                               |

| 14             | RSTIDE         | 0   | Reset IDE Open drain Reset IDE signal; it is tristated when PMCR12/IDEON is a one. Must only be pulled up to the lower voltage of a mixed mode setup to avoid latchup.                                                                                                                                  |

| 76             | RSTSW          | i   | Reset Switch Active low Schmitt trigger input for generating power on reset signals.                                                                                                                                                                                                                    |

| 50             | RESET          | 0   | Reset Drive AT bus active high reset.                                                                                                                                                                                                                                                                   |

| 58             | SA0            | 1   | System Address 0 SA0 input for address decoding.                                                                                                                                                                                                                                                        |

| 139            | FIXCS          | 0   | External Chip Select I/O address chip select for address 1630H to 163FH.                                                                                                                                                                                                                                |

| 137            | LOWPWR         | 1   | Low Power Indicates to the system address buffer and suspend resume logic that the system power modules are in low power mode. For a system that does not provide this signal, this pin needs to be tied to ground; otherwise, the internal delay circuit for the system resume will not work properly. |

| 61             | REFRESH        | 1   | Refresh System refresh signal. It is used by the watchdog timer for system idle detection.                                                                                                                                                                                                              |

|                |                | T . |                                                                                                                                                                                                                                                                                                         |

TABLE 5-2. ADDRESS BUFFER SIGNAL DESCRIPTION (CONTINUED)

System Address 2 Low Voltage

Strapping Options Inputs section for details.

System AEN signal. Used in address decode of internal address

3.3V SA2 address output interface with the H8-330. At RESET, this pin is an input whose state determines whether the chip operates in Address Buffer Function or Data Buffer Function. See

Address Enable

registers.

I/O

**AEN**

SA2LV

60

63

SIGNAL DESCRIPTION

WD7625LP

| ı | IESTERN | DIGITAL  | CORP | 54E D 📟 9718228 0015757 459 🖦 WDC                                                                                                                                                 |

|---|---------|----------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | PIN     | MNEMONIC | 1/0  | DESCRIPTION T-52-38                                                                                                                                                               |

|   | 138     | RESUME   | 0    | Resume Output indicating that the system is in resume mode. It is used to wake-up the keyboard controller on resume. Reflects the current state of the PCU input 3.               |

|   | 79      | SUSPSW   |      | Suspend Switch Suspend switch input.                                                                                                                                              |

|   | 141     | FSAD     |      | Full Strength Address Buffer Control This input is used to drive the SA and the LA output buffers to 3/5 strength or full strength. If this pin is floating, the internal pull-up |

TABLE 5-2. ADDRESS BUFFER SIGNAL DESCRIPTION (CONTINUED)

will make it logic 1, which will select the 3/5 strength mode. If it is being pulled down externally through a 15K resistor, the full strength mode is selected.

WESTERN DIGITAL CORP

#### DATA BUFFER FUNCTION, MIXED 5.3 MODE APPLICATION

Signals = 122 VSS VDD3V = 4 VDDHD = 2 VDD5V = 4. VSS = 12

FIGURE 5-2. 144-PIN DIAGRAM

| PIN-NAME | PIN-NAME   | PIN-NAME  | PIN-NAME    |

|----------|------------|-----------|-------------|

| 1-HD3    | 37-SD10    | 73-DEN0   | 109-PA3     |

| 2-HD4    | 38-SD11    | 74-DEN1   | 110-PA4     |

| 3-HD5    | 39-SD12    | 75-SDEN   | 111-PA5     |

| 4-HD6    | 40-SD13    | 76-RESIN  | 112-PA6     |

| 5-HD8    | 41-SD14    | 77-SDTR   | 113-PA7     |

| 6-HD9    | 42-SD15    | 78-VSS    | 114-PZ0     |

| 7-VSS    | 43-VSS     | 79-IDEENL | 115-PZ1     |

| 8-HD10   | 44-DACK1   | 80-IDEENH | 116-PZ2     |

| 9-HD11   | 45-DACK2   | 81-MXCTL0 | 117-PZ3     |

| 10-HD12  | 46-DACK3   | 82-MXCTL1 | 118-VDD5    |

| 11-VDDHD | 47-VDD5    | 83-MXCTL2 | 119-PB0     |

| 12-HD13  | 48-DRQ3    | 84-VDD3   | 120-VDD3    |

| 13-HD14  | 49-VSS     | 85-DACKEN | 121-PB1     |

| 14-HD15  | 50-SMEMW   | 86-DTR    | 122-PB2     |

| 15-VDD5  | 51-DRQ0    | 87-VSS    | 123-PB3     |

| 16-DACKO | 52-DRQ1    | 88-D0     | 124-PB4     |

| 17-DACK5 | 53-DRQ2    | 89-D1     | 125-PB5     |

| 18-DACK6 | 54-DRQ5    | 90-D2     | 126-PB6     |

| 19-DACK7 | 55-DRQ6    | 91-D3     | 127-PB7     |

| 20-SA0   | 56-DRQ7    | 92-D4     | 128-PC0     |

| 21-SA1   | 57-VSS     | 93-D5     | 129-PC1     |

| 22-SA2   | 58-IOR     | 94-D6     | 130-PC2     |

| 23-SMEMR | 59-IOW     | 95-D7     | 131-VSS     |

| 24-VSS   | 60-MEMR    | 96-D8     | 132-PC3     |

| 25-SD0   | 61-MEMW    | 97-VDD3   | 133-PC4     |

| 26-SD1   | 62-VSS     | 98-D9     | 134-PC5     |

| 27-SD2   | 63-IORLV   | 99-D10    | 135-PC6     |

| 28-SD3   | 64-IOWLV   | 100-D11   | 136-PC7     |

| 29-SD4   | 65-DRQIN   | 101-D12   | 137-PY0     |

| 30-VSS   | 66-CSPORTZ | 102-D13   | 138-IDEON   |

| 31-SD5   | 67-CSBASE  | 103-D14   | 139-PROCPDN |

| 32-VDD5  | 68-VDD3    | 104-D15   | 140-VSS     |

| 33-SD6   | 69-SDLV2   | 105-VSS   | 141-HD0     |

| 34-SD7   | 70-SDLV3   | 106-PA0   | 142-VDDHD   |

| 35-SD8   | 71-FULLPDN | 107-PA1   | 143-HD1     |

| 36-SD9   | 72-LOWMEG  | 108-PA2   | 144-HD2     |

TABLE 5-3. WD7625LP PIN ASSIGNMENTS (DATA BUFFER)

WESTERN DIGITAL CORP

5.4 DATA BUFFEH FUNCTION SIGNAL DEFINITION

54E D 9718228 0015759 221 WDC

| PIN                                    | MNEMONIC                                             | I/O   | DESCRIPTION                                                                                                                                                                               |

|----------------------------------------|------------------------------------------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 25-29<br>31<br>33-42                   | SD(0:15)                                             | 1/0   | System Data Bus 16-bit AT data bus.                                                                                                                                                       |

| 71                                     | FULLPDN                                              | 1     | Full Power Down Full Power Down signal from the PMCR Register. Used to isolate input pads from input pins and control programmable pull-down resistors.                                   |

| 70<br>71                               | SD2LV<br>SD3LV                                       | 0 1/0 | Low Voltage SD2, SD3  These are 3V translated outputs for the Video Clock Generator chip. At power on, SD3LV is an input whose state determines whether the hard disk runs at 3.3V or 5V. |

| 73<br>74<br>86                         | DENO<br>DEN1<br>DTR                                  | 1     | Data Bus Enable 0 Data Bus Enable 1 Direction Control Data Enable and Direction control signals for an AT data bus.                                                                       |

| 75<br>77                               | SDEN<br>SDTR                                         | 1     | Swap Data Enable Swap Direction Swap data enable and swap direction signals for an AT data bus.                                                                                           |

| 88-96<br>98-104                        | D(0:15)                                              | 1/0   | Data Bus<br>16-bit CPU data bus.                                                                                                                                                          |

| 141<br>143-144<br>1-6<br>8-10<br>12-14 | HD(0:6)<br>HD(8:15)                                  | 1/0   | Hard Disk Data Bus 15-bit IDE data bus.                                                                                                                                                   |

| 79<br>80                               | IDEDENL<br>IDEDENH                                   | I     | IDE Low Byte Enable IDE High Byte Enable IDE data bus enable control signals.                                                                                                             |

| 51<br>52<br>53<br>48<br>54<br>55<br>56 | DRQ0<br>DRQ1<br>DRQ2<br>DRQ3<br>DRQ5<br>DRQ6<br>DRQ7 | 1 1   | DMA Requests (0-3, 5:7) DRQ inputs, to be multiplexed onto DRQIN. These signals have internal pull-down.                                                                                  |

| 65                                     | DRQIN                                                | 0     | Multiplexed DRQ This outputs the multiplexed DRQ0:7.                                                                                                                                      |

**TABLE 5-4. DATA BUFFER SIGNAL DESCRIPTION**

WESTERN DIGITAL CORP 54E D ■ 9718228 0015760 T43 ■ WDC

| TERN DIGITAL CORP    |                             |     | 346 N == 3179550 007210 143 == 0                                                                                                                                                                                                                                                                                                                                                                        |

|----------------------|-----------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN                  | MNEMONIC                    | VO  | DESCRIPTION T-52-38                                                                                                                                                                                                                                                                                                                                                                                     |

| 81<br>82<br>83       | MXCTL0<br>MXCTL1<br>MXCTL2  | 1   | Multiplexer Control 0, 1 and 2 Control signals for Multiplexing and Demultiplexing of DRQ signals and DACK signals.                                                                                                                                                                                                                                                                                     |

| 128-130<br>132-136   | PC(0:7)                     | 1/0 | General Purpose Port C Signals from the general purpose read write 8-bit register (address 15E8). These bits can be set/reset individually.                                                                                                                                                                                                                                                             |

| 106-113              | PA(0:7)                     | 1/0 | General Purpose Port A 8-bit general purpose R/W register (address 15EA).                                                                                                                                                                                                                                                                                                                               |

| 119<br>102-127       | PB(0:7)                     | 1/0 | General Purpose Port B 8-bit general purpose R/W register (address 15EB).                                                                                                                                                                                                                                                                                                                               |

| 114-117              | PZ(0:3)                     | I   | Register Z 4-bit input only register inputs (address 3F3, bits 4-7).                                                                                                                                                                                                                                                                                                                                    |

| 137                  | PY0                         | 1/0 | Register Y0 1-bit general purpose R/W register (address 15E9, bit 0).                                                                                                                                                                                                                                                                                                                                   |

| 138                  | IDEON                       | _   | IDE Power On Input indicating that the IDE has power on. This signal is used to tristate the IDE buffers during IDE power down. If this signal is not used to indicate IDE power on, then this pin should be pulled low.                                                                                                                                                                                |

| 139                  | PROCPDN                     | 1   | Processor Power Down Input indicating that the processor is powered down. This signal when active will tristate and isolate the D bus.                                                                                                                                                                                                                                                                  |

| 67<br>20<br>21<br>22 | CSBASE<br>SA0<br>SA1<br>SA2 | •   | Chip Select Base System Address 0, 1 and 2 Fully decoded chip selects for general purpose registers in the Data Buffer Function. CSBASE is a base chip select and all internal registers are decoded with SA0, SA1, and SA2. At power on, CSBASE is an input whose state determines whether the WD7625LP operates in 3.3V mode or mixed voltage mode. See Strapping Options Inputs section for details. |

| 66                   | CSPORTZ                     |     | Chip Select Port Z  CSPORTZ is chip select for Port Z. At power on, CSPORTZ is an input whose state determines whether the WD7625LP runs in a 5V system. See Strapping Options Inputs section for details.                                                                                                                                                                                              |

| 72<br>60<br>61       | LOWMEG<br>MEMR<br>MEMW      | -   | First Megabyte Memory Read Memory Write Inputs for generating SMEMR, SMEMW.                                                                                                                                                                                                                                                                                                                             |

| 23<br>50             | SMEMR<br>SMEMW              | 0   | System Memory Read System Memory Write Active low memory control signals of the AT bus.                                                                                                                                                                                                                                                                                                                 |

TABLE 5-4. DATA BUFFER SIGNAL DESCRIPTION (CONTINUED)

MEZ

| STERN D                                                         | IGITAL CO                   | RP<br>I I/O I | 54E D = 9718228 0015761 98T = WDC                                                                                                                                                               |

|-----------------------------------------------------------------|-----------------------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 76                                                              | RESIN                       | 1             | Reset Input  Active low power on reset input. This input buffer has a Schmitt trigger input.                                                                                                    |

| 58<br>59                                                        | IOR<br>IOW                  | 1             | I/O Read I/O Write AT bus IO read and write signals.                                                                                                                                            |

| 64<br>63                                                        | IOWLV<br>IORLV              | 0 &           | I/O Write Low Voltage I/O Read Low Voltage 3.3V translated IOW, IOR. At power on, IORLV is an input whose state determines whether the WD7625LP operates in Address Buffer or Data Buffer mode. |

| 85                                                              | DACKEN                      | _             | DACK Enable DACKEN input, together with MXCTL0:2 demultiplexes the DACK.                                                                                                                        |

| 16<br>44-46<br>17-18<br>19                                      | DACKO DACK1:3 DACK5:6 DACK7 | 00            | DACK0-DACK7 Outputs DACK0 through DACK7 outputs.                                                                                                                                                |

| 24, 30,<br>53, 49,<br>58, 62,<br>78, 87,<br>105, 131,<br>140, 7 | vss                         |               | Ground inputs.                                                                                                                                                                                  |

| 30, 47,<br>118, 15                                              | VDD5                        |               | 4 pins.                                                                                                                                                                                         |