## **AAT4684**

**OVPSwitch™**

## **Over-Voltage Protection Switch**

#### **General Description**

The AAT4684 OVPSwitch™ is a member of AnalogicTech's Application Specific Power MOSFET™ (ASPM™) product family. It is a P-channel MOSFET power switch with precise over-voltage protection control, designed to protect low-voltage systems against high-voltage faults up to +28V. If the input voltage exceeds the programmed over-voltage threshold, the P-channel MOSFET switch will be turned off to prevent damage to the output load circuits. The AAT4684 is available with an internally programmed over-voltage trip point or as an adjustable version programmed by two external resistors.

The AAT4684 also includes an under-voltage lockout (UVLO) protection circuit, which will put the device into sleep mode at low input voltages only consuming  $< 1\mu A$  of current.

The AAT4684 is offered in a small Pb-free, 12-pin TSOPJW package and is specified for operation over the -40°C to +85°C ambient temperature range.

#### **Features**

- Over-Voltage Protection Up to +28V

- Fixed or Adjustable Over-Voltage Protection Threshold

- 3V Under-Voltage Lockout Threshold

- Fast OVP Response:

- 1µs (Max) to Over-Voltage Transient

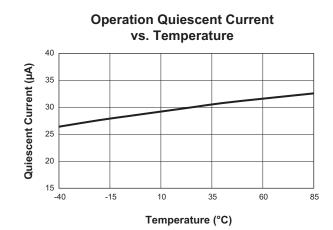

- Low Operation Quiescent Current

- 30µA Typical

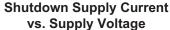

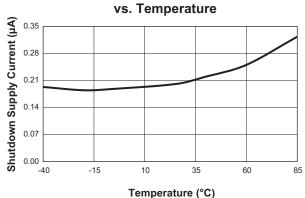

- 1µA Max in Shutdown (Disabled)

- $100m\Omega$  Typical ( $130m\Omega$  max)  $R_{DS(ON)}$  at 4.5V

- 1.8A Maximum Continuous Current

- Temperature Range: -40°C to 85°C

- Available in TSOPJW-12 Package

## **Applications**

- Cell Phones

- Digital Still Cameras

- GPS

- MP3 Players

- Personal Data Assistants (PDAs)

- USB Hot Swap/Live Insertion Device

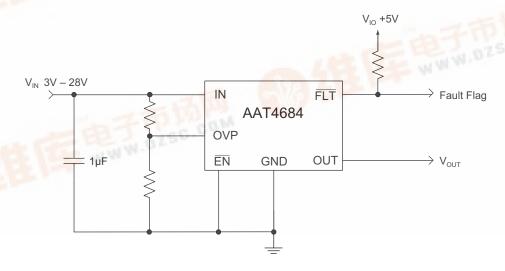

## Typical Application (Adjustable Version)

## **Over-Voltage Protection Switch**

## **Pin Descriptions**

| Pin #           |             |        |                                                                                                                                                                                                                     |  |

|-----------------|-------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Fixed           | Adj.        | Symbol | Function                                                                                                                                                                                                            |  |

| 1, 2, 9, 11, 12 | 1, 2, 9, 12 | N/C    | Not connected.                                                                                                                                                                                                      |  |

| 3               | 3           | FLT    | Over-voltage fault reporting output pin. $\overline{\text{FLT}}$ goes low when input voltage exceeds the over-voltage threshold. An external pull up resistor to $V_{\text{IO}}$ (6.5V max) should be added.        |  |

| 4               | 4           | EN     | Enable pin, active low. An internal pull-down resistor is connected on this pin. Connect to Ground for normal operation. Connect to high (6.5V max) to shut down the device when it draws less than 1µA of current. |  |

| 5, 6            | 5, 6        | OUT    | Output pin. Connect a $0.1\mu\text{F}\sim47\mu\text{F}$ capacitor from OUT to GND.                                                                                                                                  |  |

| 7, 8            | 7, 8        | IN     | Power input pin. Connect 1µF capacitor from IN to GND.                                                                                                                                                              |  |

| 10              | 10          | GND    | Ground connection pin.                                                                                                                                                                                              |  |

| n/a             | 11          | OVP    | Over-voltage protection threshold input pin (Adjustable version only).                                                                                                                                              |  |

## **Pin Configuration**

TSOPJW-12

Fixed Version

(Top View)

N/C

1

N/C

2

FLT

3

EN

4

OUT

5

OUT

6

7

IN

TSOPJW-12 Adjustable Version (Top View)

| N/C | 1 | 12  | N/C |

|-----|---|-----|-----|

| N/C | 2 | 11  | OVP |

| FLT | 3 | 10  | GND |

| ĒΝ  | 4 | 9   | N/C |

| OUT | 5 | 8   | IN  |

| OUT | 6 | 7   | IN  |

|     |   | l . |     |

# **AAT4684**

## **Over-Voltage Protection Switch**

## Absolute Maximum Ratings<sup>1</sup>

| Symbol                          | Description                          | Value                 | Units |

|---------------------------------|--------------------------------------|-----------------------|-------|

| $V_{IN}$                        | IN to GND                            | -0.3 to 30            | V     |

| V <sub>OVP</sub>                | OVP to GND                           | -0.3 to 6.5           | V     |

| $V_{FLT}$ , $V_{\overline{EN}}$ | FLT, EN to GND                       | -0.3 to 6.5           | V     |

| V <sub>OUT</sub>                | OUT to GND                           | V <sub>IN</sub> + 0.3 | V     |

| $I_{MAX}$                       | Maximum Continuous Switch Current    | 1.8                   | Α     |

| T <sub>1</sub>                  | Operating Junction Temperature Range | -40 to 150            | °C    |

## **Thermal Characteristics**

| Symbol         | nbol Description                          |     | Units |

|----------------|-------------------------------------------|-----|-------|

| $\theta_{JA}$  | Maximum Thermal Resistance <sup>2</sup>   | 160 | °C/W  |

| P <sub>D</sub> | Maximum Power Dissipation <sup>2, 3</sup> | 625 | mW    |

Stresses above those listed in Absolute Maximum Ratings may cause permanent damage to the device. Functional operation at conditions other than the operating conditions specified is not implied. Only one Absolute Maximum Rating should be applied at any one time.

Mounted on a FR4 board.

<sup>3.</sup> Derate 6.25mW/°C above 25°C.

## **Over-Voltage Protection Switch**

## **Electrical Characteristics<sup>1</sup>**

$V_{IN}$  = 5V,  $T_A$  = -40°C to 85°C unless otherwise noted. Typical values are at  $T_A$  = 25°C.

| Symbol                  | Description                                             | Conditions                                                                           | Min   | Тур | Max   | Units |

|-------------------------|---------------------------------------------------------|--------------------------------------------------------------------------------------|-------|-----|-------|-------|

| $V_{IN}$                | Normal Operation Voltage Range                          |                                                                                      | 3.0   |     | 14    | V     |

| $I_Q$                   | Operation Quiescent Current                             | $V_{IN} = 5V$ , $\overline{EN} = 0V$ , $I_{OUT} = 0$                                 |       | 30  | 50    | μΑ    |

| I <sub>SD(OFF)</sub>    | Shutdown Supply Current                                 | $\overline{\text{EN}} = \text{IN}, V_{\text{IN}} = 5.5 \text{V}, V_{\text{OUT}} = 0$ |       |     | 1     | μΑ    |

| $V_{\text{UVLO}}$       | Under-Voltage Lockout Threshold                         | Rising Edge                                                                          |       | 3.0 | 3.3   | V     |

| $V_{\text{UVLO\_HYS}}$  | Under-Voltage Lockout Hysteresis                        |                                                                                      |       | 0.1 |       | V     |

| Adjustable              |                                                         |                                                                                      |       |     |       |       |

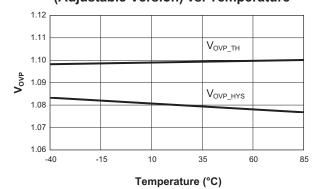

| $V_{OVP\_TH}$           | Over-Voltage Lockout Threshold, OVP Pin                 | Rising Edge                                                                          | 1.084 | 1.1 | 1.117 | V     |

| $V_{OVP\_HYS}$          | Over-Voltage Lockout Threshold Hysteresis, OVP Pin      |                                                                                      |       | 20  |       | mV    |

| Fixed                   |                                                         |                                                                                      |       |     |       |       |

| $V_{IN\_OVP\_TH}$       | Input Over-Voltage Lockout Threshold, IN Pin            | Rising Edge                                                                          |       | 6.5 |       | V     |

| V <sub>IN_OVP_HYS</sub> | Input Over-Voltage Lockout Threshold Hysteresis, IN Pin |                                                                                      |       | 120 |       | mV    |

| MOSFET S                | witch                                                   |                                                                                      |       |     |       |       |

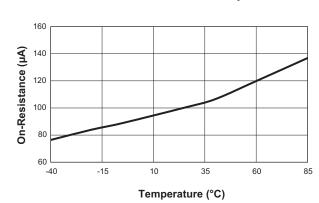

| R <sub>DS(ON)</sub>     | PMOS On-Resistance                                      | $I_{OUT} = 1800 \text{mA}, T_A = 25 ^{\circ}\text{C}$                                |       | 100 | 130   | mΩ    |

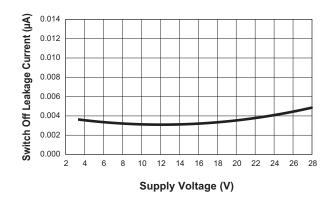

| $I_{D(OFF)}$            | Switch Off-Leakage                                      | $\overline{EN} = V_{IN}$                                                             |       |     | 1     | μΑ    |

| Logic                   |                                                         |                                                                                      |       |     |       |       |

| $V_{EN(L)}$             | EN Input Low Voltage                                    |                                                                                      |       |     | 0.4   | V     |

| V <sub>EN(H)</sub>      | EN Input High Voltage                                   |                                                                                      | 1.6   |     |       | V     |

| $I_{EN}$                | EN Input Leakage                                        | $V_{EN} = 5.5V \text{ or } 0V$                                                       |       | 0.5 | 2.0   | μΑ    |

| FLT <sub>OL</sub>       | FLT Output Voltage Low                                  | $I_{\overline{FLT}} = 1mA$                                                           |       |     | 0.4   | V     |

| FLT <sub>IOL</sub>      | FLT Output Leakage Current                              |                                                                                      |       |     | 1     | μΑ    |

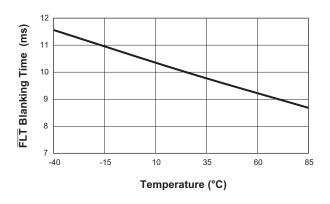

| T <sub>BLK_FLT</sub>    | FLT Blanking Time                                       | From De-assertion of OV                                                              | 5     | 10  | 15    | ms    |

| $T_{D_{FLT}}$           | FLT Assertion Delay Time from Over-Voltage (OV)         | From Assertion of OV                                                                 |       | 1   |       | μs    |

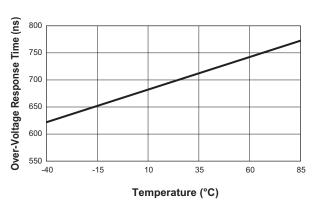

| T <sub>RESP_OV</sub>    | Over-Voltage Response Time                              | $V_{IN} = 5V$ , $V_{OVP}$ Rise to 1.13V from 1.07V in 1ns                            |       | 0.7 |       | μs    |

| T <sub>ON</sub>         | Turn On Delay Time                                      | $V_{IN} = 5V; R_O = 10\Omega; C_O = 1\mu F$                                          |       | 10  |       | ms    |

| T <sub>R</sub>          | Turn On RiseTime                                        | $V_{IN} = 5V; R_O = 10\Omega; C_O = 1\mu F$                                          |       | 1   |       | ms    |

| T <sub>OFF</sub>        | Turn Off Delay Time                                     | $V_{IN} = 5V; R_O = 10\Omega; C_O = 1\mu F$                                          |       | 6   |       | ms    |

| T <sub>F</sub>          | Turn Off Fall Time                                      | $V_{IN} = 5V; R_O = 10\Omega; C_O = 1\mu F$                                          |       | 20  |       | μs    |

<sup>1.</sup> The AAT4684 is guaranteed to meet performance specifications over the -40 to 85°C operating temperature range and is assured by design, characterization and correlation with statistical process controls.

25 20

15 10

> 5 0

3

5

## **Over-Voltage Protection Switch**

## **Typical Characteristics**

**Operation Quiescent Current** vs. Supply Voltage 50 45 Quiescent Current (µA) 40 35 30

Supply Voltage (V)

10

11 12 13

**Shutdown Supply Current**

#### Switch Off Leakage Current vs. Supply Voltage

#### PMOS On-Resistance vs. Temperature

## **Over-Voltage Protection Switch**

## **Typical Characteristics**

#### **FLT** Blanking Time vs. Temperature

#### FLT Blanking Time (V<sub>IN</sub> = 5.0V)

Time (2ms/div)

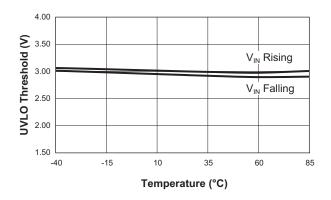

#### Undervoltage Lockout Threshold vs. Temperature

#### Over-Voltage Response Time vs. Temperature

## Over-Voltage Lockout Threshold (Adjustable Version) vs. Temperature

## **Over-Voltage Protection Switch**

## **Typical Characteristics**

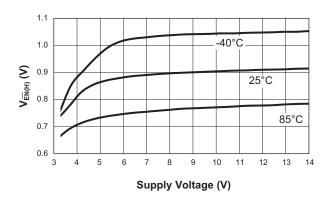

#### **EN** Input High Voltage vs. Supply Voltage

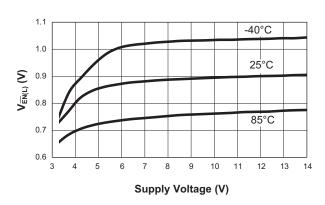

## EN Input Low Voltage vs. Supply Voltage

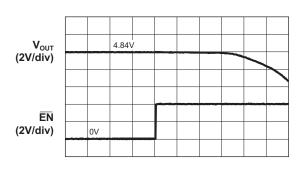

Turn Off Delay Time  $(V_{IN} = 5.0V, R_O = 10\Omega)$

Time (2ms/div)

Turn On Delay Time  $(V_{IN} = 5.0V, R_O = 10\Omega)$

Time (2ms/div)

'PSwitch™

## **Over-Voltage Protection Switch**

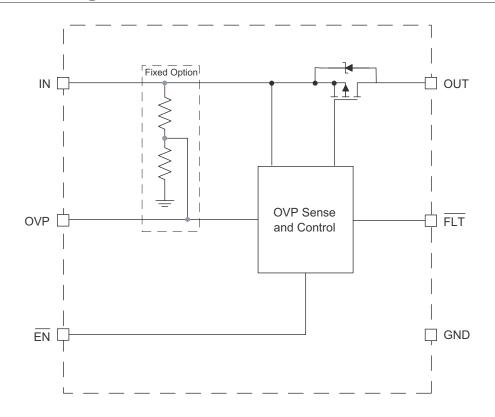

### **Functional Block Diagram**

## **Functional Description**

The AAT4684 provides up to 28V over-voltage protection when powering low-voltage systems such as cell phones, MP3, and PDAs or when charging Lithium-Ion batteries from a badly regulated supply. The AAT4684 is inserted between the power supply or charger source and the load to be protected. The AAT4684 IC consists of a low resistance P channel MOSFET, under-voltage lockout protection, over-voltage monitor, fast shut-down circuitry and a fault output flag.

In normal operation the P channel MOSFET acts as a slew-rate controlled load switch, connecting and disconnecting the power supply from IN to OUT. A low resistance MOSFET is used as to minimize the voltage drop between the voltage source and the load and to reduce the power dissipation. When the voltage on the input

exceeds the over-voltage protection trip voltage (internally set or externally by a voltage divider to the OVP pin), the device immediately turns off the internal P-channel FET, disconnecting the load from the abnormal input and preventing damage to any downstream components. Simultaneously, the fault flag is raised alerting the system to a problem.

If an over-voltage condition is applied at the time of the device enable, then the switch will remain OFF.

#### **Under-Voltage Lockout (UVLO)**

The AAT4684 has a fixed 3.0V under-voltage lockout level (UVLO). When the input voltage is less than the UVLO level, the MOSFET is turned off. 100mV of hysteresis is included to ensure circuit stability.

### **Over-Voltage Protection Switch**

#### **Over-Voltage Protection**

The AAT4684 adjustable version has a 1.1V  $\pm 1.5\%$  overvoltage trip threshold on the OVP pin. With a resistor divider on OVP pin from IN to GND, the over-voltage trip point can be adjusted anywhere within the input voltage range (see Table 1). Once the over-voltage trip level is triggered, the PMOS switch controller will shut off the PMOS in less than 1 $\mu$ s.

The AAT4684 fixed version is also available where the resistor divider is internally integrated with the input voltage trip point at 6.5V. The fixed version of AAT4684 does not have a connection to the internal OVP circuitry and the pin #11 is designed to be not connected.

#### **FLT** Output

The  $\overline{\text{FLT}}$  output is an active-low open-drain fault (OV) reporting output. A pull-up resistor should be connected from  $\overline{\text{FLT}}$  to the logic I/O voltage of the host system.  $\overline{\text{FLT}}$  will be asserted immediately if an over-voltage fault occurs (only about a 1 $\mu$ s inherited internal circuit delay). A 10ms blanking is applied to  $\overline{\text{FLT}}$  signal prior to deassertion.

#### **EN** Input

$\overline{\text{EN}}$  is an active-low enable input. EN is driven low, connected to ground, or left floating for normal device operation. Taking the  $\overline{\text{EN}}$  high turns off the MOSFET. In the case of an over-voltage or UVLO condition toggling the  $\overline{\text{EN}}$  will not override the fault condition and the switch will remain off.

#### **Device Operation**

On initial power-up, if  $V_{\text{IN}} < \text{UVLO}$  or if  $V_{\text{OVP}} > V_{\text{OVP\_TH}}$  (1.1V), the PMOS is held off. If UVLO  $< V_{\text{IN}}$ ,  $V_{\text{OVP}} < V_{\text{OVP\_TH}}$ , and EN is low, the device enters startup after a 10ms internal delay.

#### **Application Information**

#### **Over-Voltage Protection**

The AAT4684 over-voltage protection circuit provides fast protection against transient voltage spikes and short duration spikes of high voltage from the power supply lines. AAT4684 can quickly disconnect the input supply from the load and not cause any damage to sensitive components

In portable product applications, if the user removes the battery pack during charging, this action can create large transients and a high voltage spike can occur which can damage other electronic devices in the product such as the battery charger. A hot plug of the AC/DC wall adapter into the AC outlet can create and release a voltage spike from the transformer. As a result, some sensitive devices within the product can be damaged. With the AAT4684 placed between the power lines and the sensitive devices, the voltage spike can be kept away and the input supply disconnected from other devices in 0.7µs.

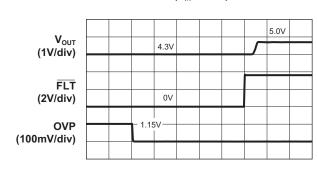

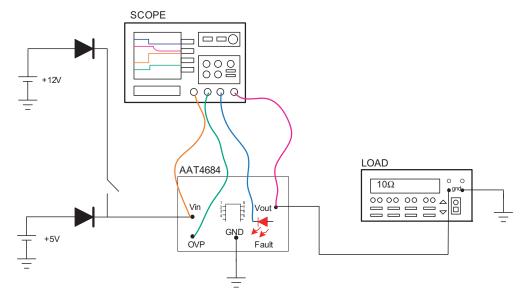

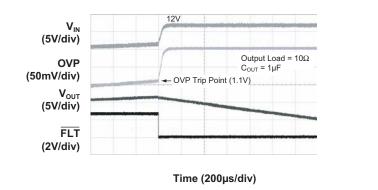

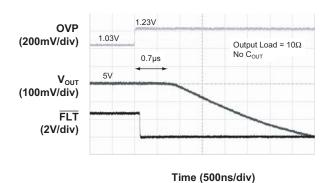

Figure 2 shows the response time of over-voltage protection from the test circuit (Figure 1). The input voltage is rapidly increased from 5V to 12V by a voltage surge or voltage spike. The voltage at the OVP pin is also increased until the trip point is triggered. At this point, the  $\overline{\text{FLT}}$  pin is pulled low and the output voltage starts to fall. Figure 3 shows a zoom-in scope capture of the OVP response time; the output is disconnected from the input in as little as 700ns.

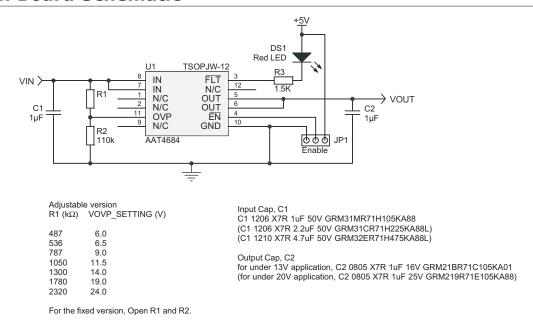

## Adjustable Version - Over-Voltage Protection Resistors

The over-voltage protection threshold is programmed with two resistors, R1 and R2. To limit the current going through the external resistor string while maintaining good noise immunity, use smaller resistor values, such as  $10 K\Omega$  for R2. Using a larger value will further reduce the system current, but will also increase the impedance of the OVP node, making it more sensitive to external noise and interference. A suggested value for R2 is  $110 K\Omega$ . Table 1 summarizes resistor values for various over-voltage settings. Use 1% tolerance metal film resistors for programming the desired OVP setting.

## **Over-Voltage Protection Switch**

| R2 (KΩ) | R1 (KΩ) | V <sub>OVP</sub> Setting (V) |

|---------|---------|------------------------------|

| 110     | 487     | 6.0                          |

| 110     | 536     | 6.5                          |

| 110     | 787     | 9.0                          |

| 110     | 1050    | 11.5                         |

| 110     | 1300    | 14.0                         |

| 110     | 1540    | 16.5                         |

| 110     | 1780    | 19.0                         |

| 110     | 2050    | 21.5                         |

| 110     | 2320    | 24.0                         |

| 110     | 2550    | 26.5                         |

Table 1: Recommended OVP Setting for AAT4684 Adjustable Version1.

Figure 1: Over-Voltage Protection Response Time Test Circuit.

Figure 2: Typical Over-Voltage Response Time.

Figure 3: Typical Over-Voltage Response Time [zoom in].

<sup>1.</sup> Mimimum OVP voltage setting = 5V.

$\mathsf{OVPS}$ witch $^{\scriptscriptstyle\mathsf{TM}}$

## **Over-Voltage Protection Switch**

#### **Input Capacitor**

A 1 $\mu F$  or larger capacitor is typically recommended for  $C_{IN}$ .  $C_{IN}$  should be located as close to the device VIN pin as practically possible. Ceramic, tantalum, or aluminum electrolytic capacitors may be selected for  $C_{IN}$ . There is no specific capacitor equivalent series resistance (ESR) requirement for  $C_{IN}$ . However, for higher current operation, ceramic capacitors are recommended for  $C_{IN}$  due to their inherent capability over tantalum capacitors to withstand input current surges from low impedance sources such as batteries in portable devices.

Capacitors are typically manufactured in different voltage ratings. 16V, 25V, and 50V are good for OVP applications. If the maximum possible surge voltage is known, select capacitors with a voltage rating at least 5V higher than the maximum possible surge voltage. Otherwise, 50V rated capacitors are generally good for most OVP applications to prevent any surge voltage.

#### **Output Capacitor**

In order to insure stability while current limit is active, a small output capacitance of approximately  $1\mu F$  is required at the output. Likewise, with the output capacitor, there is no specific capacitor ESR requirement. If desired,  $C_{\text{OUT}}$  may be increased to accommodate any load transient condition.

#### **FAULT** Flag

A FAULT flag is provided to alert the system if the AAT4684's input voltage has passed the pre-programmed over-voltage trip point. Since the FAULT is open drain pin, it should be pulled up to input/output voltage rail and less than the maximum operating voltage of 6.5V.

#### Thermal Considerations and High Output Current Applications

The AAT4684 is designed to deliver a continuous output load current. The limiting characteristic for maximum safe operating output load current is package power dissipation. In order to obtain high operating currents, careful device layout and circuit operating conditions must be taken into account. The following discussions

will assume the load switch is mounted on a printed circuit board utilizing the minimum recommended footprint as stated in the "Printed Circuit Board Layout Recommendations" section of this datasheet. At any given ambient temperature  $(T_A)$ , the maximum package power dissipation can be determined by the following equation:

$$P_{D(MAX)} = \frac{T_{J(MAX)} - T_A}{\theta_{JA}}$$

Constants for the AAT4684 are maximum junction temperature ( $T_{J(MAX)}=125^{\circ}C$ ) and package thermal resistance ( $\theta_{JA}=160^{\circ}C/W$ ). Worst-case conditions are calculated at the maximum operating temperature,  $T_A=85^{\circ}C$ . Typical conditions are calculated under normal ambient conditions where  $T_A=25^{\circ}C$ . At  $T_A=85^{\circ}C$ ,  $P_{D(MAX)}=250$ mW. At  $T_A=25^{\circ}C$ ,  $P_{D(MAX)}=625$ mW.

The maximum continuous output current for the AAT4684 is a function of the package power dissipation and the  $R_{DS}$  of the MOSFET at  $T_{J(MAX)}.$  The maximum  $R_{DS}$  of the MOSFET at  $T_{J(MAX)}$  is calculated by increasing the maximum room temperature.

For maximum current, refer to the following equation:

$$I_{\text{OUT(MAX)}} = \sqrt{\frac{P_{\text{D(MAX)}}}{R_{\text{DS}}}}$$

## Printed Circuit Board Layout Recommendations

For proper thermal management and to take advantage of the low  $R_{\rm DS(ON)}$  of the AAT4684, certain circuit board layout rules should be followed: VIN and VOUT should be routed using wider than normal traces, and GND should be connected to a ground plane. To maximize package thermal dissipation and power handling capacity of the AAT4684 TSOPJW-12 package, the ground plane area connected to the ground pins should be made as large as possible. For best performance,  $C_{\rm IN}$  and  $C_{\rm OUT}$  should be placed close to the package pins. Refer to Figures 3 and 4.

### **Over-Voltage Protection Switch**

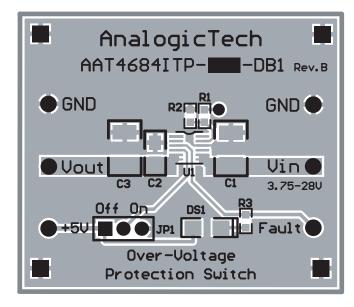

#### **Evaluation Board Schematic**

Figure 3: AAT4684 Evaluation Board Schematic.

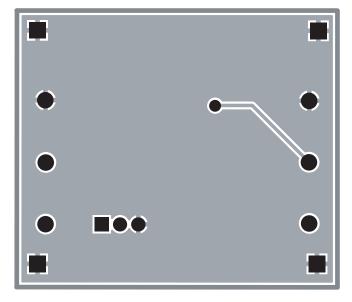

### **Evaluation Board Layout**

Figure 4: AAT4684 Evaluation Board Component Side Layout.

Figure 5: AAT4684 Evaluation Board Solder Side Layout.

#### **Over-Voltage Protection Switch**

#### **Ordering Information**

| Package   | OVP Trip Voltage | Marking | Part Number (Tape and Reel) |

|-----------|------------------|---------|-----------------------------|

| TSOPJW-12 | Adjustable       | YSXYY   | AAT4684ITP-T1               |

| TSOPJW-12 | 6.5V             |         | AAT4684ITP-6.5-T1           |

All AnalogicTech products are offered in Pb-free packaging. The term "Pb-free" means semiconductor products that are in compliance with current RoHS standards, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. For more information, please visit our website at http://www.analogictech.com/pbfree.

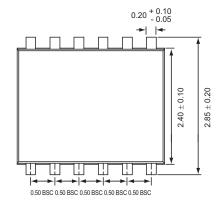

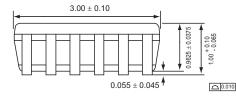

## **Package Information**

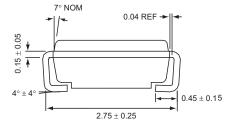

#### TSOPJW-12

All dimensions in millimeters.

#### Advanced Analogic Technologies, Inc.

3230 Scott Boulevard, Santa Clara, CA 95054 Phone (408) 737-4600 Fax (408) 737-4611

© Advanced Analogic Technologies, Inc.

AnalogicTech cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in an AnalogicTech product. No circuit patent licenses, copyrights, mask work rights, or other intellectual property rights are implied. AnalogicTech reserves the right to make changes to their products or specifications or to discontinue any product or service without notice. Except as provided in AnalogicTech's terms and conditions of sale, AnalogicTech assumes no liability whatsoever, and AnalogicTech disclaims any express or implied warranty relating to the sale and/or use of AnalogicTech products including liability or warranties relating to thress for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards. Testing and other quality control techniques are utilized to the extent AnalogicTech deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed. AnalogicTech and the AnalogicTech logo are trademarks of Advanced Analogic Technologies Incorporated. All other brand and product names appearing in this document are registered trademarks of their respective holders.

<sup>1.</sup> XYY = assembly and date code.

<sup>2.</sup> Sample stock is generally held on part numbers listed in **BOLD**.

<sup>©</sup> Advanced Analogic Technologies, Inc.