查询ADA4841-1YRZ-RL供应商

# **ANALOG DEVICES**

# Low Power, Low Noise and Distortion, Rail-to-Rail Output Amplifier

### FEATURES

Low power: 1.1 mA/amp Low wideband noise 2.1 nV/√Hz 1.4 pA/√Hz Low 1/f noise 7 nV/√Hz @ 10 Hz 13 pA/√Hz @ 10 Hz Low distortion: -105 dBc @ 100 kHz, Vo = 2 V p-p **High speed** 80 MHz, -3 dB bandwidth (G = +1) 12 V/µs slew rate 175 ns settling time to 0.1% Low offset voltage: 0.3 mV maximum **Rail-to-rail output Power down** Wide supply range: 2.7 V to 12 V

### **APPLICATIONS**

Low power, low noise signal processing Battery-powered instrumentation 16-bit PulSAR® ADC drivers

### **GENERAL DESCRIPTION**

The ADA4841-1/ADA4841-2 are unity gain stable, low noise and distortion, rail-to-rail output amplifiers that have a quiescent current of 1.5 mA maximum. Despite their low power consumption, these amplifiers offer low wideband voltage noise performance of 2.1 nV/ $\sqrt{\text{Hz}}$  and 1.4 pA/ $\sqrt{\text{Hz}}$  current noise, along with excellent spurious-free dynamic range (SFDR) of -105 dBc at 100 kHz. To maintain a low noise environment at lower frequencies, the amplifiers have low 1/f noise of 7 nV/ $\sqrt{\text{Hz}}$ and 13 pA/ $\sqrt{\text{Hz}}$  at 10 Hz.

The ADA4841-1/ADA4841-2 output can swing to less than 50 mV of either rail. The input common-mode voltage range extends down to the negative supply. The ADA4841-1/ADA4841-2 can drive up to 10 pF of capacitive load with minimal peaking.

The ADA4841-1/ADA4841-2 provide the performance required to efficiently support emerging 16-bit to 18-bit ADCs and are ideal for portable instrumentation, high channel count, industrial measurement, and medical applications. The ADA4841-1/ ADA4841-2 are ideally suited to drive the AD7685/AD7686, 16-bit PulSAR ADCs.

Information functions of the second s

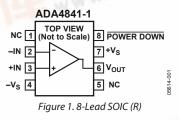

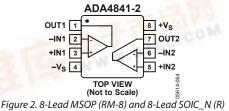

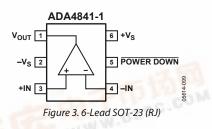

### **CONNECTION DIAGRAMS**

ADA4841-1/ADA4841-2

The ADA4841-1/ADA4841-2 packages feature Pb-free lead finish. The amplifiers are rated to work over the industrial temperature range ( $-40^{\circ}$ C to  $+125^{\circ}$ C).

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 www.analog.com

# **TABLE OF CONTENTS**

| Features 1                                    |

|-----------------------------------------------|

| Applications                                  |

| Connection Diagrams                           |

| General Description 1                         |

| Revision History                              |

| Specifications                                |

| Absolute Maximum Ratings                      |

|                                               |

| Thermal Resistance                            |

| Thermal Resistance    6      ESD Caution    6 |

|                                               |

| ESD Caution                                   |

| ESD Caution                                   |

| ESD Caution                                   |

### **REVISION HISTORY**

| 3/06—Rev. B to Rev. C               |           |

|-------------------------------------|-----------|

| Added SOT-23 Package                | Universal |

| Changes to General Description      | 1         |

| Changes to Table 1                  | 3         |

| Changes to Table 2                  |           |

| Changes to Table 3                  | 5         |

| Changes to Input Protection Section | 15        |

| Changes to Ordering Guide           |           |

#### 10/05—Rev. A to Rev. B

| Added ADA4841-2                                        | Universal    |

|--------------------------------------------------------|--------------|

| Changes to General Description and Features            | 1            |

| Changes to Table 1                                     | 3            |

| Changes to Table 2                                     | 4            |

| Changes to Table 3                                     | 5            |

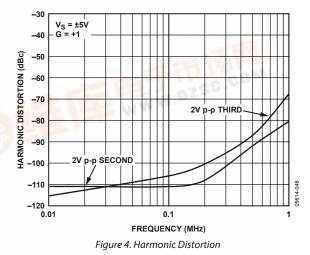

| Changes to Table 4, Table 5, and Figure 4              | <del>6</del> |

| Changes to Figure 6                                    | 7            |

| Changes to Figure 12, Figure 13, Figure 15, and Figure |              |

| Deleted Figure 25; Renumber Sequentially               | 10           |

| Changes to Figure 24 and Figure 28                     |              |

| Changes to Figure 31                                   | 11           |

| Inserted Figure 37; Renumber Sequentially              |              |

| Changes to Amplifier Description Section and Figure 3  |              |

| Headroom Considerations    |  |

|----------------------------|--|

| Capacitance Drive          |  |

| Input Protection           |  |

| Power-Down Operation       |  |

| Applications               |  |

| Typical Performance Values |  |

| 16-Bit ADC Driver          |  |

| Reconstruction Filter      |  |

| Layout Considerations      |  |

| Ground Plane               |  |

| Power Supply Bypassing     |  |

| Outline Dimensions         |  |

| Ordering Guide             |  |

| Changed DC Performance Considerations Section            |    |

|----------------------------------------------------------|----|

| to DC Errors Section                                     | 13 |

| Changes to Noise Considerations Section                  | 14 |

| Changes to Headroom Considerations Section and Figure 39 | 15 |

| Changes to Power-Down Operation Section                  | 16 |

| Changes to 16-Bit ADC Driver Section,                    |    |

| Figure 48, and Figure 49                                 | 17 |

| Changes to Power Supply Bypassing Section                | 18 |

| Updated Outline Dimensions                               | 19 |

| Changes to Ordering Guide                                | 20 |

#### 9/05—Rev. 0 to Rev. A

| Changes to Features                        | 1  |

|--------------------------------------------|----|

| Changes to Figure 2                        | 1  |

| Changes to Figure 12                       | 8  |

| Changes to Figure 40                       | 14 |

| Changes to Headroom Considerations Section | 15 |

### 7/05—Revision 0: Initial Version

### **SPECIFICATIONS**

$T_A = 25^{\circ}$ C,  $V_S = \pm 5$  V,  $R_L = 1$  k $\Omega$ , Gain = +1, unless otherwise noted.

| Parameter                             | Conditions                                                 | Min  | Тур       | Мах | Unit       |

|---------------------------------------|------------------------------------------------------------|------|-----------|-----|------------|

| DYNAMIC PERFORMANCE                   |                                                            |      | 'yp       | Max |            |

| -3 dB Bandwidth                       | $V_{0} = 0.02 V p - p$                                     | 58   | 80        |     | MHz        |

| S db bundwiddi                        | $V_0 = 2.02 \text{ V p - p}$                               | 50   | 3         |     | MHz        |

| Slew Rate                             | $G = +1$ , $V_0 = 9$ V step, $R_L = 1$ k $\Omega$          | 12   | 13        |     | V/µs       |

| Settling Time to 0.1%                 | $G = +1, V_0 = 8 V \text{ step}$                           | 12   | 650       |     | ns         |

| Settling Time to 0.01%                | $G = +1, V_0 = 8 V \text{ step}$                           |      | 1000      |     | ns         |

| NOISE/HARMONIC PERFORMANCE            |                                                            |      | 1000      |     | 115        |

| Harmonic Distortion HD2/HD3           | f <sub>c</sub> = 100 kHz, V <sub>o</sub> = 2 V p-p, G = +1 |      | -111/-105 |     | dBc        |

|                                       | $f_c = 1 \text{ MHz}, V_0 = 2 \text{ V p - p}$             |      | -80/-67   |     | dBc        |

| Input Voltage Noise                   | f = 100  kHz                                               |      | 2.1       |     | nV/√Hz     |

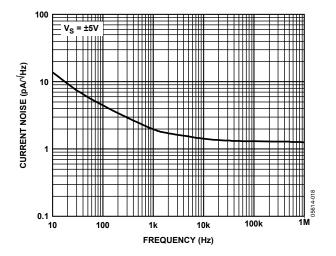

| Input Current Noise                   | f = 100  kHz                                               |      | 1.4       |     | pA/√H      |

| DC PERFORMANCE                        |                                                            |      |           |     | p/ ( ) ( ) |

| Input Offset Voltage                  |                                                            |      | 40        | 300 | μV         |

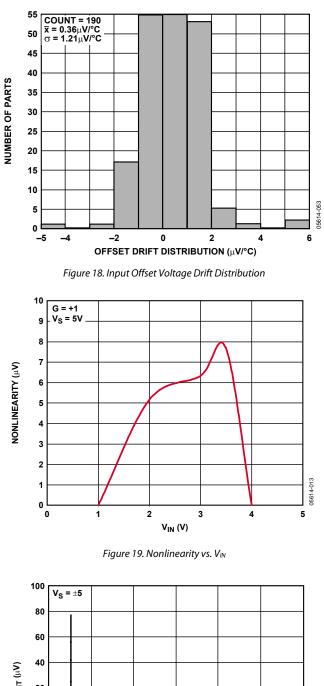

| Input Offset Voltage Drift            |                                                            |      | 1         | 500 | μV/°C      |

| Input Bias Current                    |                                                            |      | 3         | 5.3 | μΑ         |

| Input Offset Current                  |                                                            |      | 0.1       | 0.5 | μΑ         |

| Open-Loop Gain                        | $V_{O} = \pm 4 V$                                          | 103  | 120       | 0.5 | dB         |

|                                       | V0                                                         | 105  | 120       |     | GD         |

| Input Resistance, Common Mode         |                                                            |      | 90        |     | MΩ         |

| Input Resistance, Common Mode         |                                                            |      | 25        |     | kΩ         |

| Input Capacitance, Common Mode        |                                                            |      | 1         |     | pF         |

| Input Capacitance, Differential Mode  |                                                            |      | 3         |     | pF         |

| Input Common-Mode Voltage Range       |                                                            | -5.1 | 5         | +4  | V          |

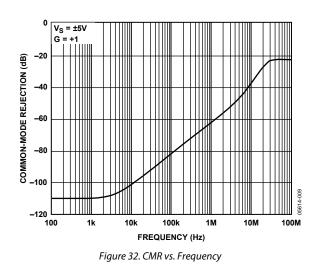

| Common-Mode Rejection Ratio (CMRR)    | $V_{CM} = \Delta 4 V$                                      | 95   | 115       | 14  | dB         |

| MATCHING CHARACTERISTICS (ADA4841-2)  |                                                            |      | 115       |     | ab         |

| Input Offset Voltage                  |                                                            |      | 70        |     | μV         |

| Input Bias Current                    |                                                            |      | 60        |     | nA         |

| POWER DOWN PIN (ADA4841-1)            |                                                            |      | 00        |     | 11/ \      |

| POWER DOWN Voltage                    | Enabled                                                    |      | >3.6      |     | v          |

| POWER DOWN Voltage                    | Power down                                                 |      | <3.2      |     | v          |

| -                                     | Power down                                                 |      | <3.2      |     | v          |

| Input Current                         |                                                            |      |           |     |            |

| Enable                                | POWER DOWN = +5 V                                          |      | 1         | 2   | μA         |

| Power Down                            | $\overline{POWER DOWN} = -5 V$                             |      | -13       | -30 | μΑ         |

| Switching Speed                       |                                                            |      |           |     |            |

| Enable                                |                                                            |      | 1         |     | μs         |

| Power Down                            |                                                            |      | 40        |     | μs         |

| OUTPUT CHARACTERISTICS                |                                                            |      |           |     |            |

| Output Voltage Swing                  | G > +1                                                     | ±4.9 | ±4.955    |     | V          |

| Output Current Limit                  | Sourcing, $V_{IN} = +V_s$ , $R_L = 50 \ \Omega$ to GND     |      | 30        |     | mA         |

|                                       | Sinking, $V_{IN} = -V_S$ , $R_L = 50 \Omega$ to GND        |      | 60        |     | mA         |

| Capacitive Load Drive                 | 30% overshoot                                              |      | 15        |     | pF         |

| POWER SUPPLY                          |                                                            |      |           |     |            |

| Operating Range                       |                                                            | 2.7  |           | 12  | V          |

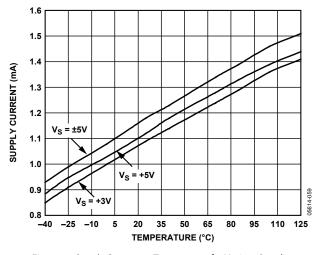

| Quiescent Current/Amplifier           | $\overline{POWER DOWN} = +5 V$                             |      | 1.2       | 1.5 | mA         |

|                                       | $\overline{\text{POWER DOWN}} = -5 \text{ V}$              |      | 40        | 90  | μΑ         |

| Positive Power Supply Rejection Ratio | $+V_{s} = +5 V \text{ to } +6 V, -V_{s} = -5 V$            | 95   | 110       |     | dB         |

| Negative Power Supply Rejection Ratio | $+V_{s} = +5 V, -V_{s} = -5 V to +6 V$                     | 96   | 120       |     | dB         |

$T_{A}$  = 25°C,  $V_{S}$  = 5 V,  $R_{L}$  = 1 kΩ, Gain = +1,  $V_{CM}$  = 2.5 V, unless otherwise noted.

### Table 2.

| Parameter                                    | Conditions                                                                | Min          | Тур            | Max | Unit     |

|----------------------------------------------|---------------------------------------------------------------------------|--------------|----------------|-----|----------|

| DYNAMIC PERFORMANCE                          |                                                                           |              |                |     |          |

| –3 dB Bandwidth                              | $V_0 = 0.02 V p - p$                                                      | 54           | 80             |     | MHz      |

|                                              | $V_0 = 2 V p - p$                                                         |              | 3              |     | MHz      |

| Slew Rate                                    | $G = +1$ , $V_0 = 4$ V step, $R_L = 1$ k $\Omega$                         | 10           | 12             |     | V/µs     |

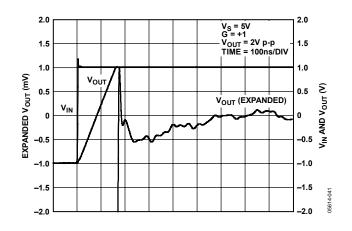

| Settling Time to 0.1%                        | $G = +1, V_0 = 2 V step$                                                  |              | 175            |     | ns       |

| Settling Time to 0.01%                       | $G = +1, V_0 = 2 V step$                                                  |              | 550            |     | ns       |

| NOISE/HARMONIC PERFORMANCE                   |                                                                           |              |                |     |          |

| Harmonic Distortion HD2/HD3                  | $f_c = 100 \text{ kHz}, V_0 = 2 \text{ V p-p}$                            |              | -109/-105      |     | dBc      |

|                                              | $f_{c} = 1 \text{ MHz}, V_{o} = 2 \text{ V } p-p$                         |              | -78/-66        |     | dBc      |

| Input Voltage Noise                          | f = 100 kHz                                                               |              | 2.1            |     | nV/√Hz   |

| Input Current Noise                          | f = 100 kHz                                                               |              | 1.4            |     | pA/√Hz   |

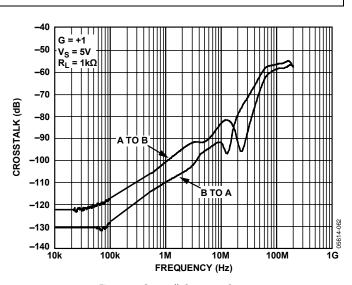

| Crosstalk                                    | f = 100 kHz                                                               |              | –117           |     | dB       |

| DC PERFORMANCE                               |                                                                           |              |                |     |          |

| Input Offset Voltage                         |                                                                           |              | 40             | 300 | μV       |

| Input Offset Voltage Drift                   |                                                                           |              | 1              |     | μV/°C    |

| Input Bias Current                           |                                                                           |              | 3              | 5.3 | μΑ       |

| Input Offset Current                         |                                                                           |              | 0.1            | 0.4 | μΑ       |

| Open-Loop Gain                               | $V_0 = 0.5 V$ to 4.5 V                                                    | 103          | 124            |     | dB       |

| INPUT CHARACTERISTICS                        |                                                                           |              |                |     |          |

| Input Resistance, Common Mode                |                                                                           |              | 90             |     | MΩ       |

| Input Resistance, Differential Mode          |                                                                           |              | 25             |     | kΩ       |

| Input Capacitance, Common Mode               |                                                                           |              | 1              |     | pF       |

| Input Capacitance, Differential Mode         |                                                                           |              | 3              |     | pF       |

| Input Common-Mode Voltage Range              |                                                                           | -0.1         |                | +4  | V        |

| Common-Mode Rejection Ratio (CMRR)           | $V_{CM} = \Delta 1.5 V$                                                   | 88           | 115            |     | dB       |

| MATCHING CHARACTERISTICS (ADA4841-2)         |                                                                           |              |                |     |          |

| Input Offset Voltage                         |                                                                           |              | 70             |     | μV       |

| Input Bias Current                           |                                                                           |              | 70             |     | nA       |

| POWER DOWN PIN (ADA4841-1)                   |                                                                           |              |                |     |          |

| POWER DOWN Voltage                           | Enabled                                                                   |              | >3.6           |     |          |

| POWER DOWN Voltage                           | Power down                                                                |              | <3.2           |     | v        |

| Input Current                                |                                                                           |              |                |     |          |

| Enable                                       | $\overline{\text{POWER DOWN}} = 5 \text{ V}$                              |              | 1              | 2   | μA       |

| Power Down                                   | $\overline{POWER DOWN} = 0 V$                                             |              | -13            | -30 | μA       |

| Switching Speed                              |                                                                           |              |                | 50  | μ        |

| Enable                                       |                                                                           |              | 1              |     | 116      |

| Power Down                                   |                                                                           |              | 40             |     | μs<br>μs |

| OUTPUT CHARACTERISTICS                       |                                                                           |              | 40             |     | μs       |

| Output Voltage Swing                         | G > +1                                                                    | 0.08 to 4.92 | 0.029 to 4.974 |     | v        |

| Output Voltage Swing<br>Output Current Limit | Sourcing, $V_{IN} = +V_s$ , $R_L = 50 \Omega$ to $V_{CM}$                 | 0.00 10 4.92 | 30             |     | mA       |

| Output current Linit                         | _                                                                         |              |                |     |          |

| Capacitive Load Drive                        | Sinking, $V_{IN} = -V_S$ , $R_L = 50 \Omega$ to $V_{CM}$<br>30% overshoot |              | 60<br>15       |     | mA<br>pF |

| Capacitive Load Drive                        | 50% OVEISHOOL                                                             |              | 15             |     | рг       |

| POWER SUPPLY                                 |                                                                           | 2.7          |                | 10  |          |

| Operating Range                              |                                                                           | 2.7          | 1 1            | 12  | V        |

| Quiescent Current/Amplifier                  | POWER DOWN = 5 V                                                          |              | 1.1            | 1.4 | mA       |

|                                              | $\overline{POWER DOWN} = 0 V$                                             |              | 35             | 70  | μA       |

| Positive Power Supply Rejection Ratio        | $+V_{s} = +5 V \text{ to } +6 V, -V_{s} = 0 V$                            | 95           | 110            |     | dB       |

| Negative Power Supply Rejection Ratio        | $+V_{s} = +5 V, -V_{s} = 0 V \text{ to } -1 V$                            | 96           | 120            |     | dB       |

$T_A = 25^{\circ}$ C,  $V_S = 3$  V,  $R_L = 1$  k $\Omega$ , Gain =+1,  $V_{CM} = 1.5$  V, unless otherwise noted.

Table 3. Parameter Conditions Min Тур Max Unit DYNAMIC PERFORMANCE -3 dB Bandwidth  $V_0 = 0.02 V p - p$ 52 80 MHz Slew Rate G = +1,  $V_0 = 2 V$  step,  $R_L = 1 k\Omega$ 10 12 V/µs Settling Time to 0.1%  $G = +1, V_0 = 1 V step$ 120 ns Settling Time to 0.01%  $G = +1, V_0 = 1 V step$ 250 ns NOISE/HARMONIC PERFORMANCE Harmonic Distortion HD2/HD3  $f_{c} = 100 \text{ kHz}, V_{0} = 1 \text{ V p-p}$ -97/-100 dBc  $f_{c} = 1 \text{ MHz}, V_{o} = 1 \text{ V p-p}$ -79/-80 dBc Input Voltage Noise f = 100 kHz2.1 nV/√Hz Input Current Noise f = 100 kHzpA/√Hz 1.4 DC PERFORMANCE Input Offset Voltage 40 300 μV μV/°C Input Offset Voltage Drift 1 Input Bias Current 3 5.3 μΑ Input Offset Current 0.5 0.1 μA 101 dB **Open-Loop Gain**  $V_0 = 0.5 V$  to 2.5 V 123 INPUT CHARACTERISTICS Input Resistance, Common Mode 90 MΩ Input Resistance, Differential Mode 25 kΩ рF Input Capacitance, Common Mode 1 рF Input Capacitance, Differential Mode 3 Input Common-Mode Voltage Range -0.1 +2 V 86 Common-Mode Rejection Ratio (CMRR)  $V_{CM} = \Delta 0.4 V$ 115 dB MATCHING CHARACTERISTICS (ADA4841-2) Input Offset Voltage 70 μV Input Bias Current 60 nA POWER DOWN PIN (ADA4841-1) POWER DOWN Voltage Enabled >1.6 **POWER DOWN** Voltage Power down <1.2 ٧ Input Current  $\overline{POWFRDOWN} = 3V$ Enable 1 2 μΑ POWER DOWN = 0 V Power Down -10 -30 μΑ Switching Speed Enable 1 μs Power Down 40 μs OUTPUT CHARACTERISTICS v **Output Voltage Swing** G > +1 0.045 to 2.955 0.023 to 2.988 **Output Current Limit** Sourcing,  $V_{IN} = +V_S$ ,  $R_L = 50 \ \Omega$  to  $V_{CM}$ 30 mΑ Sinking,  $V_{IN} = -V_S$ ,  $R_L = 50 \Omega$  to  $V_{CM}$ 60 mΑ 30% overshoot Capacitive Load Drive 30 рF POWER SUPPLY 2.7 V **Operating Range** 12 Quiescent Current/Amplifier POWER DOWN = 3 V 1.1 1.3 mΑ POWER DOWN = 0 V 25 60 μΑ  $+V_{s} = +3 V \text{ to } +4 V, -V_{s} = 0 V$ 95 dB **Positive Power Supply Rejection Ratio** 110 Negative Power Supply Rejection Ratio  $+V_{s} = +3 V, -V_{s} = 0 V to -1 V$ 96 120 dB

### **ABSOLUTE MAXIMUM RATINGS**

Table 4.

| Parameter                   | Rating                               |

|-----------------------------|--------------------------------------|

| Supply Voltage              | 12.6 V                               |

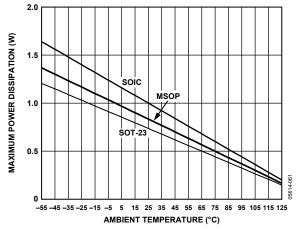

| Power Dissipation           | See Figure 5                         |

| Common-Mode Input Voltage   | $-V_{s} - 0.5 V$ to $+V_{s} + 0.5 V$ |

| Differential Input Voltage  | ±1.8 V                               |

| Storage Temperature Range   | –65°C to +125°C                      |

| Operating Temperature Range | –40°C to +85°C                       |

| Lead Temperature            | JEDEC J-STD-20                       |

| Junction Temperature        | 150°C                                |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### THERMAL RESISTANCE

$\theta_{JA}$  is specified for the worst-case conditions, that is,  $\theta_{JA}$  is specified for device soldered in circuit board for surface-mount packages.

**Table 5. Thermal Resistance**

| Package Type  | θ」Α | Unit |

|---------------|-----|------|

| 8-lead SOIC_N | 125 | °C/W |

| 8-lead MSOP   | 130 | °C/W |

| 6-Lead SOT-23 | 170 | °C/W |

#### Maximum Power Dissipation

The maximum safe power dissipation for the ADA4841-1/ ADA4841-2 is limited by the associated rise in junction temperature (T<sub>J</sub>) on the die. At approximately 150°C, which is the glass transition temperature, the plastic changes its properties. Even temporarily exceeding this temperature limit may change the stresses that the package exerts on the die, permanently shifting the parametric performance of the amplifiers. Exceeding a junction temperature of 150°C for an extended period can result in changes in silicon devices, potentially causing degradation or loss of functionality. The power dissipated in the package ( $P_D$ ) is the sum of the quiescent power dissipation and the power dissipated in the die due to the amplifier's drive at the output. The quiescent power is the voltage between the supply pins ( $V_s$ ) times the quiescent current ( $I_s$ ).

$P_D$  = Quiescent Power + (Total Drive Power – Load Power)

$$P_D = \left(V_S \times I_S\right) + \left(\frac{V_S}{2} \times \frac{V_{OUT}}{R_L}\right) - \frac{V_{OUT}^2}{R_L}$$

RMS output voltages should be considered. If  $R_L$  is referenced to  $-V_s$ , as in single-supply operation, the total drive power is  $V_s \times I_{OUT}$ . If the rms signal levels are indeterminate, consider the worst case, when  $V_{OUT} = V_s/4$  for  $R_L$  to midsupply.

$$P_D = \left(V_S \times I_S\right) + \frac{\left(V_S/4\right)^2}{R_L}$$

In single-supply operation with  $R_L$  referenced to  $-V_s$ , worst case is  $V_{OUT} = V_s/2$ .

Airflow increases heat dissipation, effectively reducing  $\theta_{JA}$ . In addition, more metal directly in contact with the package leads and through holes under the device reduces  $\theta_{JA}$ .

Figure 5 shows the maximum safe power dissipation in the package vs. the ambient temperature for the 8-lead MSOP (145°C/W), 8-lead SOIC\_N (125°C/W) and the 6-lead SOT-23 (170°C/W) on a JEDEC standard 4-layer board.  $\theta_{JA}$  values are approximations.

Figure 5. Maximum Power Dissipation vs. Temperature for a 4-Layer Board

#### **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although this product features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

# **TYPICAL PERFORMANCE CHARACTERISTICS**

$R_L = 1 \text{ k}\Omega$ , unless otherwise noted.

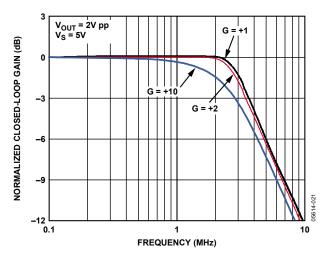

Figure 6. Large Signal Frequency Response vs. Gain

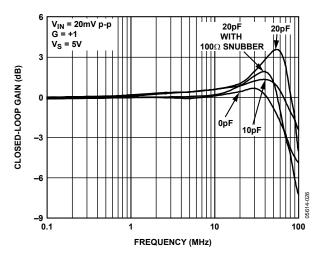

Figure 7. Small Signal Frequency Response vs. Capacitive Load

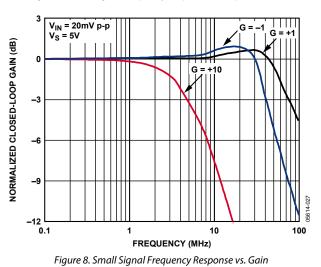

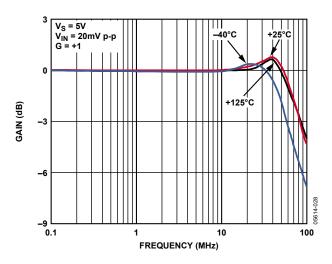

Figure 9. Small Signal Frequency Response vs. Temperature

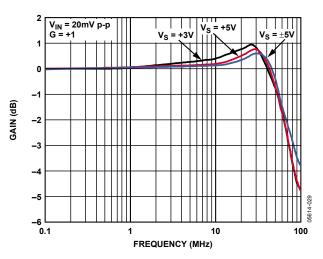

Figure 10. Small Signal Frequency Response vs. Supply Voltage

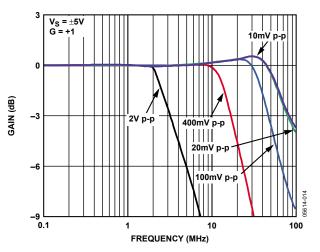

Figure 11. Frequency Response for Various VOUT

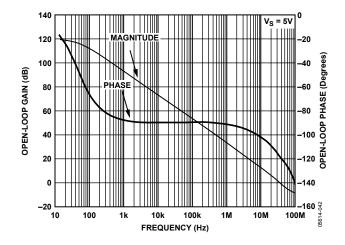

Figure 12. Open-Loop Gain and Phase vs. Frequency

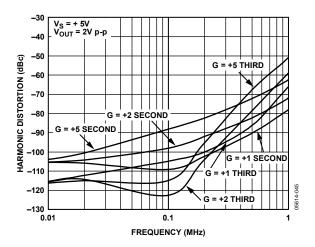

Figure 13. Harmonic Distortion vs. Frequency for Various Gains

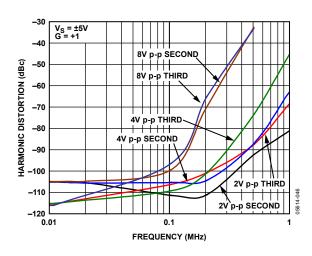

Figure 14. Harmonic Distortion vs. Frequency for Various Output Voltages

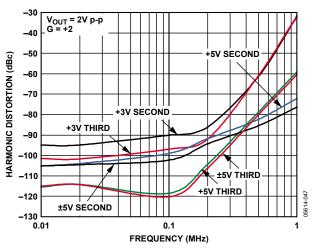

Figure 15. Harmonic Distortion vs. Frequency for Various Supplies

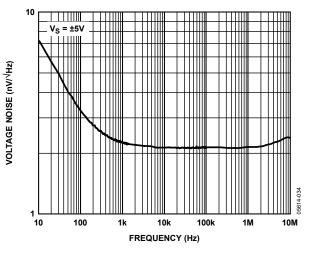

Figure 16. Voltage Noise vs. Frequency

Figure 17. Current Noise vs. Frequency

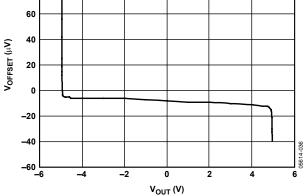

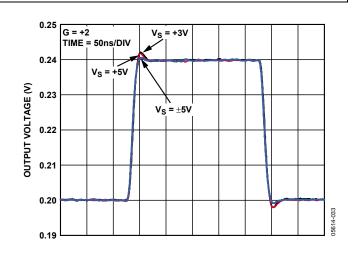

Figure 20. Input Error Voltage vs. Output Voltage

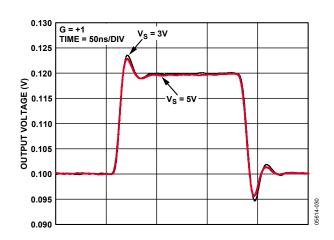

Figure 21. Small Signal Transient Response for Various Supplies

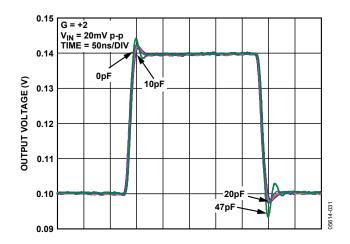

Figure 22. Small Signal Transient Response for Various Capacitive Loads

Figure 23. Small Signal Transient Response for Various Supplies

Figure 24. Input Overdrive Recovery

Figure 25. Output Overdrive Recovery

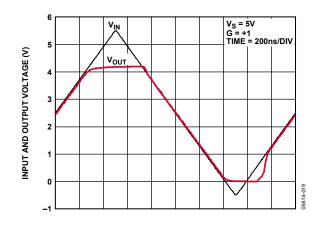

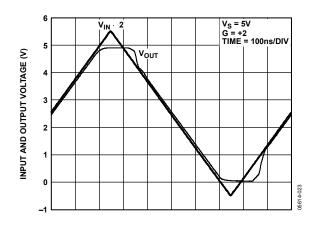

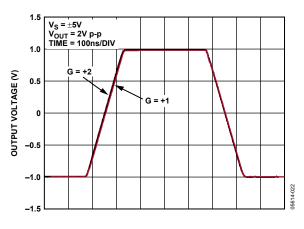

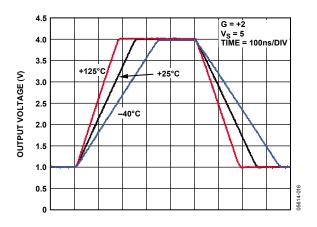

Figure 26. Large Signal Transient Response for Various Gains

Figure 27. Slew Rate vs. Temperature

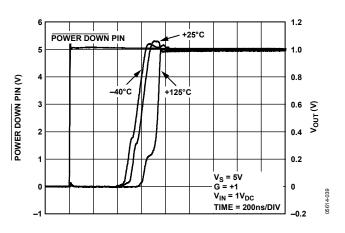

Figure 29. Power-Up Time vs. Temperature

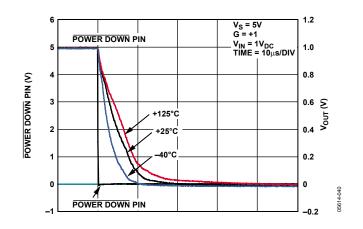

Figure 30. POWER DOWN Time vs. Temperature

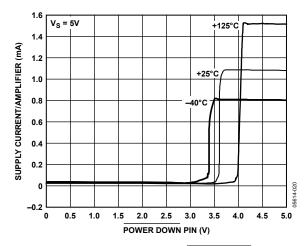

Figure 31. Supply Current per Amplifier vs. POWER DOWN Pin Voltage

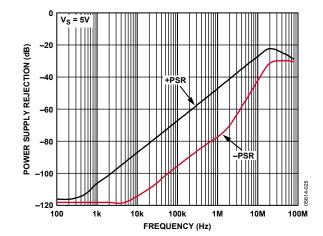

Figure 33. PSR vs. Frequency

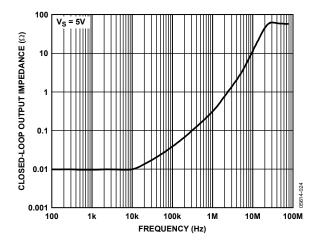

Figure 34. Output Impedance vs. Frequency

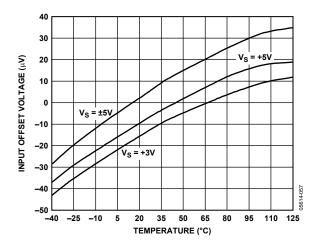

Figure 35. Input Offset Voltage vs. Temperature for Various Supplies

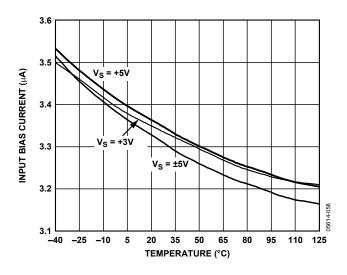

Figure 36. Input Bias Current vs. Temperature for Various Supplies

Figure 37. Supply Current vs. Temperature for Various Supplies

Figure 38. Crosstalk Output to Output

### THEORY OF OPERATION AMPLIFIER DESCRIPTION

The ADA4841-1/ADA4841-2 are low power, low noise, precision voltage-feedback op amps for single or dual voltage supply operation. The ADA4841-1/ADA4841-2 are fabricated on ADI's second generation XFCB process and feature trimmed supply current and offset voltage. The 2.1 nV/ $\sqrt{\text{Hz}}$  voltage noise (very low for a 1.1 mA supply current amplifier), 40  $\mu$ V offset voltage, and sub 1 µV/°C offset drift is accomplished with an input stage made of an undegenerated PNP input pair driving a symmetrical folded cascode. A rail-to-rail output stage provides the maximum linear signal range possible on low voltage supplies and has the current drive capability needed for the relatively low resistance feedback networks required for low noise operation. CMRR, PSRR, and open-loop gain are all typically above 100 dB, preserving the precision performance in a variety of configurations. Gain bandwidth is kept high for this power level to preserve the outstanding linearity performance for frequencies up to 100 kHz. The ADA4841-1 has a powerdown function to further reduce power consumption. All this results in a low noise, power efficient, precision amplifier that is well-suited for high resolution and precision applications.

#### **DC ERRORS**

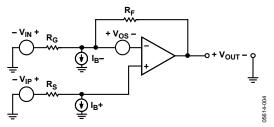

Figure 39 shows a typical connection diagram and the major dc error sources. The ideal transfer function (all error sources set to 0 and infinite dc gain) can be written as

$$V_{OUT} = \left(1 + \frac{R_F}{R_G}\right) \times V_{IP} - \left(\frac{R_F}{R_G}\right) \times V_{IN}$$

(1)

Figure 39. Typical Connection Diagram and DC Error Sources

This reduces to the familiar forms for inverting and noninverting op amp gain expressions

$$V_{OUT} = \left(1 + \frac{R_F}{R_G}\right) \times V_{IP} \tag{2}$$

(Noninverting gain,  $V_{IN} = 0 V$ )

$$V_{OUT} = \left(\frac{-R_F}{R_G}\right) \times V_{IN} \tag{3}$$

(Inverting gain,  $V_{IP} = 0 V$ )

The total output voltage error is the sum of errors due to the amplifier offset voltage and input currents. The output error due to the offset voltage can be estimated as

$$V_{OUT_{ERROR}} = \left(V_{OFFSET_{NOM}} + \frac{VCM}{CMRR} + \frac{V_P - V_{PNOM}}{PSRR} + \frac{V_{OUT}}{A}\right) \times \left(1 + \frac{R_F}{R_G}\right)$$

(4)

where:

$V_{OFFSET_{NOM}}$  is the offset voltage at the specified supply voltage. This is measured with the input and output at midsupply.

VCM is the common-mode voltage.

$V_P$  is the power supply voltage.

$V_{P_{NOM}}$  is the specified power supply voltage.

CMRR is the common-mode rejection ratio.

PSRR is the power supply rejection ratio.

A is the dc open-loop gain.

The output error due to the input currents can be estimated as

$$V_{OUT_{ERROR}} = (R_F || R_G) \times \left(1 + \frac{R_F}{R_G}\right) I_{B-} - R_S \times \left(1 + \frac{R_F}{R_G}\right) \times I_{B+}$$

(5)

Note that setting  $R_s$  equal to  $R_F || R_G$  compensates for the voltage error due to the input bias current.

#### NOISE CONSIDERATIONS

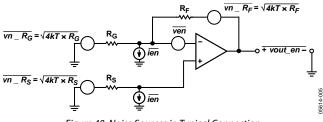

Figure 40 illustrates the primary noise contributors for the typical gain configurations. The total rms output noise is the root-mean-square of all the contributions.

Figure 40. Noise Sources in Typical Connection

The output noise spectral density can be calculated by

$$\overline{vout\_en} = \sqrt{4kTRf + \left(1 + \frac{R_F}{R_G}\right)^2 \left[4kTRs + \overline{ien}^2 R_S^2 + \overline{ven}^2\right] + \left(\frac{R_F}{R_G}\right)^2 4kTRg + \overline{ien}^2 R_F^2}$$

(6)

where:

k is Boltzmann's Constant.

${\it T}$  is the absolute temperature, degrees Kelvin.

*ien* is the amplifier input current noise spectral density,  $pA/\sqrt{Hz}$ .

*ven* is the amplifier input voltage spectral density,  $nV/\sqrt{Hz}$ .

$R_s$  is the source resistance as shown in Figure 40.

$R_F$  and  $R_G$  are the feedback network resistances, as shown in Figure 40.

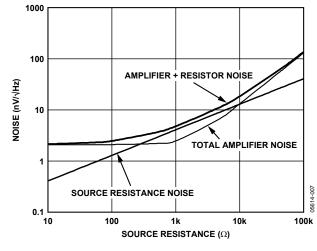

Source resistance noise, amplifier voltage noise (ven), and the voltage noise from the amplifier current noise (ien × R<sub>s</sub>) are all subject to the noise gain term (1 + R<sub>F</sub>/R<sub>G</sub>). Note that with a 2.1 nV/ $\sqrt{Hz}$  input voltage noise and 1.4 pA/ $\sqrt{Hz}$  input current, the noise contributions of the amplifier are relatively small for source resistances between approximately 200  $\Omega$  and 30 k $\Omega$ . Figure 41 shows the total RTI noise due to the amplifier vs. the source resistance. In addition, the value of the feedback resistors used impacts the noise. It is recommended to keep the value of feedback resistors between 250  $\Omega$  and 1 k $\Omega$  to keep the total noise low.

Figure 41. RTI Noise vs. Source Resistance

### **HEADROOM CONSIDERATIONS**

The ADA4841-1/ADA4841-2 are designed to provide maximum input and output signal ranges with 16-bit to 18-bit dc linearity. As the input or output headroom limits are reached, the signal linearity degrades.

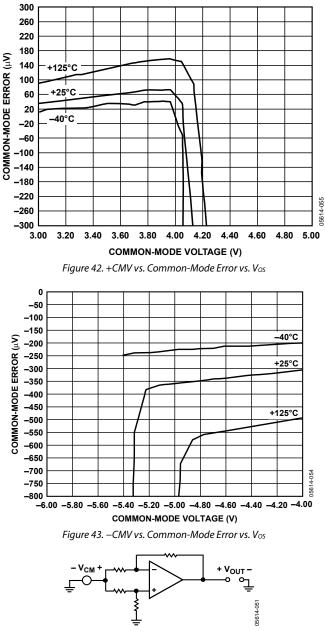

The input stage positive limit is almost exactly a volt below the positive supply at room temperature. Input voltages above that start to show clipping behavior. The positive input voltage limit increases with temperature with a coefficient of about 2 mV/°C. The lower supply limit is nominally below the minus supply; therefore, in a standard gain configuration, the output stage limits the signal headroom on the negative supply side. Figure 42 and Figure 43 show the nominal CMRR behavior at the limits of the input headroom for three temperatures—this is generated using the subtractor topology shown in Figure 44, which avoids the output stage limitation.

Figure 44. Common-Range Subtractor

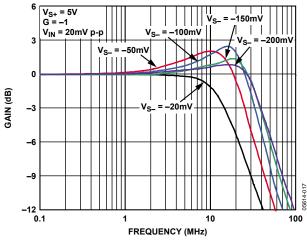

Figure 45 shows the amplifier frequency response as a G = -1 inverter with the input and output stage biased near the negative supply rail.

Figure 45. Small Signal Frequency Response vs. Negative Supply Bias

The input voltage ( $V_{IN}$ ) and reference voltage ( $V_{IP}$ ) are both at 0 V, (see Figure 39). + $V_S$  is biased at +5 V, and - $V_S$  is swept from -200 mV to -20 mV. With the input and output voltages biased 200 mV above the bottom rail, the G = -1 inverter frequency response is not much different from what is seen with the input and output voltages biased near midsupply. At 150 mV bias, the frequency response starts to decrease and at 20 mV, the inverter bandwidth is less than half its nominal value.

### **CAPACITANCE DRIVE**

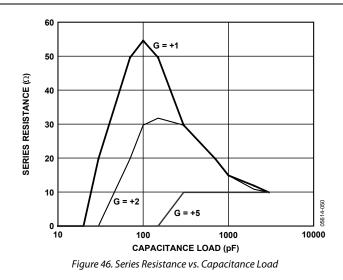

Capacitance at the output of an amplifier creates a delay within the feedback path that, if within the bandwidth of the loop, can create excessive ringing and oscillation. The G = +1 follower topology has the highest loop bandwidth of any typical configuration and, therefore, is the most vulnerable to the effects of capacitance load.

A small resistor in series with the amplifier output and the capacitive load mitigates the problem. Figure 46 plots the recommended series resistance vs. capacitance for gains of +1, +2, and +5.

#### INPUT PROTECTION

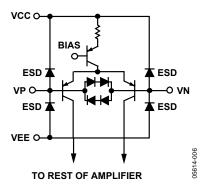

The ADA4841-1/ADA4841-2 are fully protected from ESD events, withstanding human body model ESD events of 2.5 keV and charge device model events of 1 keV with no measured performance degradation. The precision input is protected with an ESD network between the power supplies and diode clamps across the input device pair, as shown in Figure 47.

Figure 47. Input Stage and Protection Diodes

For differential voltages above approximately 1.4 V, the diode clamps start to conduct. Too much current can cause damage due to excessive heating. If large differential voltages need to be sustained across the input terminals, it is recommended that the current through the input clamps be limited to below 150 mA. Series input resistors sized appropriately for the expected differential overvoltage provide the needed protection.

The ESD clamps start to conduct for input voltages more than 0.7 V above the positive supply and input voltages more than 0.7 V below the negative supply. It is recommended that the fault current be limited to less than 150 mA if an overvoltage condition is expected.

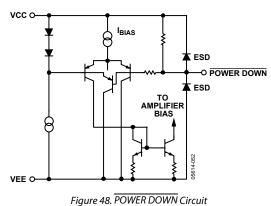

### **POWER-DOWN OPERATION**

Figure 48 shows the ADA4841-1 power-down circuitry. If the POWER DOWN pin is left unconnected, then the base of the input PNP transistor is pulled high through the internal pull-up resistor to the positive supply, and the part is turned on. Pulling the POWER DOWN pin approximately 1.7 V below the positive supply turns the part off, reducing the supply current to approximately 40  $\mu$ A.

The POWER DOWN pin is protected with ESD clamps, as shown in Figure 48. Voltages beyond the power supplies cause these diodes to conduct. The guidelines for limiting the overload current in the input protection section should also be followed for the POWER DOWN pin.

### **APPLICATIONS** Typical performance values

To reduce design time and eliminate uncertainty Table 6 provides a convenient reference for typical gains, component values, and performance parameters.

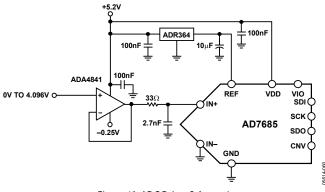

### **16-BIT ADC DRIVER**

The combination of low noise, low power, and high speed make the ADA4841-1/ADA4841-2 the perfect driver solution for low power, 16-bit ADCs, such as the AD7685. Figure 49 shows a typical 16-bit single-supply application.

There are different challenges to a single-supply, high resolution design, and the ADA4841-1/ADA4841-2 address these nicely. In a single-supply system, a main challenge is using the amplifier in buffer mode with the lowest output noise and preserving linearity compatible with the ADC.

Rail-to-rail input amplifiers are usually higher noise than the ADA4841-1/ADA4841-2 and cannot be used in this mode because of the nonlinear region around the crossover point of their input stages. The ADA4841-1/ADA4841-2, which have no crossover region but have a wide linear input range from 100 mV below ground to 1 V below positive rail, solve this problem, as shown in Figure 49. The amplifier, when configured as a follower, has a linear signal range from 0.25 V above the minus supply voltage (limited by the amplifier's output stage) to 1 V below the positive supply (limited by the amplifier input stage). A 0 V to +4.096 V signal range can be accommodated with a positive supply as low as +5.2 V and a negative power supply of -0.25 V. The 5.2 V supply also allows the use of a small, low dropout, low temperature drift ADR364 reference voltage. If ground is used as the amplifier negative supply, then note that at the low end of the input range close to ground, the ADA4841-1/ ADA4841-2 exhibit substantial nonlinearity, as any rail-to-rail output amplifier. The ADA4841-1/ADA4841-2 drive a onepole, low-pass filter. This filter limits the already very low noise contribution from the amplifier to the AD7685.

Figure 49. ADC Driver Schematic

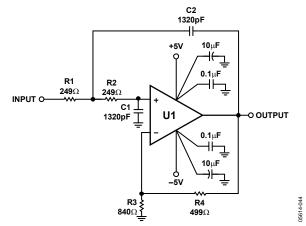

### **RECONSTRUCTION FILTER**

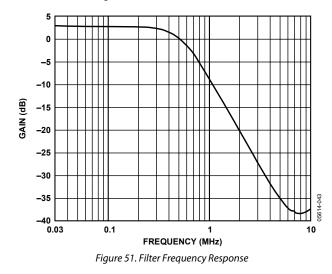

The ADA4841-1/ADA4841-2 can also be used as a reconstruction filter at the output of DACs for suppression of the sampling frequency. The filter shown in Figure 50 is a two-pole, 500 kHz Sallen-Key LPF with a fixed gain of G = +1.6.

Figure 50. Two-Pole 500 kHz Reconstruction Filter Schematic

Setting the resistors and capacitors equal to each other greatly simplifies the design equations for the Sallen-Key filter. The corner frequency, or -3 dB frequency, can be described by the equation

$$f_C = \frac{1}{2\pi R 1 C 1}$$

The quality factor, or Q, is shown in the equation

$$Q = \frac{1}{3 - K}$$

For minimum peaking, set Q equal to 0.707.

The gain, or *K*, of the amplifier is

$$K = \frac{R4}{R3} + 1$$

Resistor values are kept low for minimal noise contribution, offset voltage, and optimal frequency response.

| Gain | R <sub>F</sub> (Ω) | R <sub>G</sub> (Ω) | –3 dB BW (MHz) | Slew Rate (V/µs) | Peaking<br>(dB) | Output Noise ADA4841-1/<br>ADA4841-2 Only (nV/√Hz) | Total Output Noise Including<br>Resistors (nV/√Hz) |

|------|--------------------|--------------------|----------------|------------------|-----------------|----------------------------------------------------|----------------------------------------------------|

| +1   | 0                  | N/A                | 77             | 12.5             | 0.9             | 2                                                  | 2                                                  |

| +2   | 499                | 499                | 34             | 12.5             | 0.3             | 4                                                  | 5.73                                               |

| -1   | 499                | 499                | 38             | 12.5             | 0.4             | 4                                                  | 5.73                                               |

| +5   | 499                | 124                | 11             | 12               | 0               | 10                                                 | 11.9                                               |

| +10  | 499                | 54.9               | 5              | 12               | 0               | 20                                                 | 21.1                                               |

| +20  | 499                | 26.1               | 2.3            | 11.2             | 0               | 40                                                 | 42.2                                               |

#### Table 6. Recommended Values and Typical Performance

Capacitor selection is critical for optimal filter performance. Capacitors with low temperature coefficients, such as NPO ceramic capacitors, are good choices for filter elements. Figure 51 shows the filter response.

#### LAYOUT CONSIDERATIONS

To ensure optimal performance, careful and deliberate attention must be paid to the board layout, signal routing, power supply bypassing, and grounding.

### **GROUND PLANE**

It is important to avoid ground in the areas under and around the input and output of the ADA4841-1/ADA4841-2. Stray capacitance created between the ground plane and the input and output pads of a device are detrimental to high speed amplifier performance. Stray capacitance at the inverting input, along with the amplifier input capacitance, lowers the phase margin and can cause instability. Stray capacitance at the output creates a pole in the feedback loop. This can reduce phase margin and can cause the circuit to become unstable.

### **POWER SUPPLY BYPASSING**

Power supply bypassing is a critical aspect in the performance of the ADA4841-1/ADA4841-2. A parallel connection of capacitors from each of the power supply pins to ground works best. A typical connection is shown in Figure 50. Smaller value capacitors offer better high frequency response where larger value electrolytics offer better low frequency performance. Paralleling different values and sizes of capacitors helps to ensure that the power supply pins are provided a low ac impedance across a wide band of frequencies. This is important for minimizing the coupling of noise into the amplifier. This can be especially important when the amplifier PSR is starting to roll off—the bypass capacitors can help lessen the degradation in PSR performance.

Starting directly at the ADA4841-1/ADA4841-2 power supply pins, the smallest value capacitor should be placed on the same side of the board as the amplifier, and as close as possible to the amplifier power supply pin. The ground end of the capacitor should be connected directly to the ground plane. Keeping the capacitors' distance short but equal from the load is important and can improve distortion performance. This process should be repeated for the next largest value capacitor.

It is recommended that a 0.1  $\mu$ F ceramic 0508 case be used. The 0508 case size offers low series inductance and excellent high frequency performance. A 10  $\mu$ F electrolytic capacitor should be placed in parallel with the 0.1  $\mu$ F capacitor. Depending on the circuit parameters, some enhancement to performance can be realized by adding additional capacitors. Each circuit is different and should be individually analyzed for optimal performance.

### **OUTLINE DIMENSIONS**

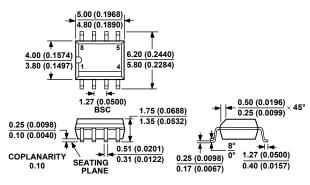

COMPLIANT TO JEDEC STANDARDS MS-012-AA CONTROLLING DIMENSIONS ARE IN MILLIMETERS; INCH DIMENSIONS (IN PARENTHESES) ARE ROUNDED-OFF MILLIMETER EQUIVALENTS FOR REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN.

Figure 52. 8-Lead Standard Small Outline Package [SOIC\_N] Narrow Body (R-8) Dimensions shown in millimeters and (inches)

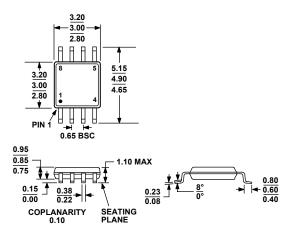

COMPLIANT TO JEDEC STANDARDS MO-187-AA Figure 53. 8-Lead Mini Small Outline Package [MSOP] (RM-8) Dimensions shown in millimeters

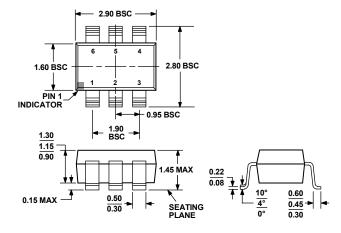

COMPLIANT TO JEDEC STANDARDS MO-178-AB

Figure 54. 6-Lead Small Outline Transistor Package [SOT-23] (RJ-6) Dimensions shown in millimeters

### **ORDERING GUIDE**

| Model                         | Temperature Range | Package Description | Package Option | Ordering Quantity | Branding |

|-------------------------------|-------------------|---------------------|----------------|-------------------|----------|

| ADA4841-1YRZ <sup>1</sup>     | -40°C to +125°C   | 8-Lead SOIC_N       | R-8            | 1                 |          |

| ADA4841-1YRZ-R71              | -40°C to +125°C   | 8-Lead SOIC_N       | R-8            | 1,000             |          |

| ADA4841-1YRZ-RL <sup>1</sup>  | -40°C to +125°C   | 8-Lead SOIC_N       | R-8            | 2,500             |          |

| ADA4841-1YRJZ-R2 <sup>1</sup> | -40°C to +125°C   | 6-Lead SOT-23       | RJ-6           | 250               | HQB      |

| ADA4841-1YRJZ-R71             | -40°C to +125°C   | 6-Lead SOT-23       | RJ-6           | 3,000             | HQB      |

| ADA4841-1YRJZ-RL <sup>1</sup> | -40°C to +125°C   | 6-Lead SOT-23       | RJ-6           | 10,000            | HQB      |

| ADA4841-2YRMZ <sup>1</sup>    | -40°C to +125°C   | 8-Lead MSOP         | RM-8           | 1                 | HRB      |

| ADA4841-2YRMZ-R71             | -40°C to +125°C   | 8-Lead MSOP         | RM-8           | 1,000             | HRB      |

| ADA4841-2YRMZ-RL <sup>1</sup> | -40°C to +125°C   | 8-Lead MSOP         | RM-8           | 3,000             | HRB      |

| ADA4841-2YRZ <sup>1</sup>     | -40°C to +125°C   | 8-Lead SOIC_N       | R-8            | 1                 |          |

| ADA4841-2YRZ-R71              | -40°C to +125°C   | 8-Lead SOIC_N       | R-8            | 1,000             |          |

| ADA4841-2YRZ-RL <sup>1</sup>  | -40°C to +125°C   | 8-Lead SOIC_N       | R-8            | 2,500             |          |

$^{1}$  Z = Pb-free part.