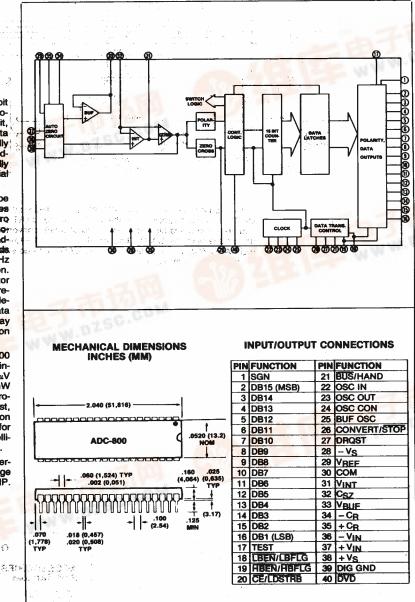

# ADC-800 适询ADC-800供应商 15-Bit Plus Sign A/D。Convertor with Microprocessor Interface

### FEATURES

- 15-Bits Plus Sign Bit

- · Parallel or Serial Bus Interface

- Three State Outputs

- High Impedance Differential Input

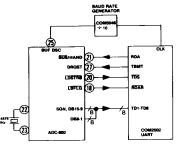

- UART Control Signals

- Low Noise

### **GENERAL DESCRIPTION**

DATEL's ADC-800 is a low power. 15-bit plus sign integrating AD converter. Microprocessor interface signals allow 16-bit, single byte or 8-bit, two byte parallel data transfer or data may be transmitted serially via industry standard UART in the "handshake" mode. Conversion time is typically 2.5 conv/sec with a maximum differential linearity error of  $\pm \frac{1}{2}$  LSB.

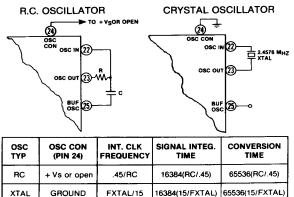

The ADC-800 uses an improved dual slope conversion technique which incorporates system zero and integrator output?iztero phases. Offset error sources are!iautermatically zeroed. The externally adjustable clock allows integration pariods which are integral multiples of 50 or 60 Hz for maximum power-line noise rejection. By using the 2.4576 MHz crystal oscillator mode, 50, 60 and 400 Hz signals are rejected. A serial count output can be derived by gating the clock signal with data valid (DVD). The count output pulses may be used in serial fiber optic transmission systems.

Other important features of the ADC-800 include: high impedance differential inputs, 5 pA typical input bias current, 15  $\mu$ V peak-to-peak typical input noise, 20 mW power dissipation and static discharge protected inputs. the combination of low cost, high accuracy and low power consumption make the ADC-800 an ideal choice for process control, data logging and intelligent measurement system applications.

The ADC-800 operates over the commercial, 0°C to +70°C temperature range and is packaged in a 40-pin plastic DIP.

ALLESS TO BE DREADERO

S. Shaway

二二人 经有限部件

in the states

utosen to

PDF

t.dzsc.com

专业P

急出货

EXTEL Ind. 14 Cabot Boulevard, Mansfield, MA 02048-1194/TEL (508) 339-3000/TLX 174388/FAX (508) 339-8356

D/ATEL

| ABSOLUTE MAXIMUM RATINGS           Positive Supply Voltage (+ Vs to gnd)           Negative Supply Voltage (- Vs to gnd)           Analog Input Voltage Range (+ or - Vin)           Reference Input Voltage Range (Vref)           Digital Input Voltage Range           Power Dissipation (package) | -9.0V<br>+ V <sub>S</sub> to - V <sub>S</sub><br>+ V <sub>S</sub> to - V <sub>S</sub><br>+ V <sub>S</sub> + 0.3V to gnd0.3V |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

#### FUNCTIONAL SPECIFICATIONS

Typical at 25°C, ±5V supplies, 2.5 conv/sec. conversion speed, 2.4576 MHz crystal, 3.2768V full-scale voltage unless otherwise noted.

| ANALOG INPUTS                                                                                                                                                                                                                                                 |                                                            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|

|                                                                                                                                                                                                                                                               | Differential                                               |

| Ype Analog Input<br>ero-Scale Error, max.1                                                                                                                                                                                                                    | ± 0.5 LSB                                                  |

|                                                                                                                                                                                                                                                               | 15 pA                                                      |

| ommon Mode Input Range                                                                                                                                                                                                                                        | $-V_{S} + 1.5V \text{ to } + V_{S} - 1.0V$<br>80 $\mu$ V/V |

| common Mode Rejection Ratio <sup>3</sup>                                                                                                                                                                                                                      | 80 µV/V                                                    |

| nput Noise <sup>4</sup>                                                                                                                                                                                                                                       | 15 μV peak-to-peak                                         |

| IGITAL INPUTS                                                                                                                                                                                                                                                 |                                                            |

| control Input Pull-Up Current <sup>5</sup>                                                                                                                                                                                                                    | 5 µA                                                       |

| nput Voltage, (Pins 18-21, 26, 27)                                                                                                                                                                                                                            |                                                            |

| Lich Nin                                                                                                                                                                                                                                                      | 2.5V                                                       |

| Low Max.<br>put Pull-up Current <sup>s</sup> (pins 26, 27)                                                                                                                                                                                                    | 2V                                                         |

| put Pull-up Current <sup>e</sup> (pins 26, 27)                                                                                                                                                                                                                | 5 µA                                                       |

| (pins 17, 24)                                                                                                                                                                                                                                                 | 25 µA                                                      |

| put Pin Pulldown Current <sup>7</sup> (pin 21)                                                                                                                                                                                                                | 5 µA                                                       |

| put Capacitance, max. (pins 18, 19)                                                                                                                                                                                                                           | 50 pF<br>70 nsec.                                          |

| nput Pin Pulldown Current? (pins 17, 24)<br>iput Capacitance, max. (pins 18, 19)<br>US/Hand Control Pulse Width, min. <sup>6</sup>                                                                                                                            | 350 nsec.                                                  |

| yte Enable Pulse Width, min.                                                                                                                                                                                                                                  | 500 nsec.                                                  |

| hip Enable Pulse width, min.*                                                                                                                                                                                                                                 | 350 nsec.                                                  |

| Vie Enable Access Time, max."                                                                                                                                                                                                                                 | 400 nsec.                                                  |

| hip Enable Access Time, max.*                                                                                                                                                                                                                                 | 300 nsec.                                                  |

| US/Hand Control Pulse Width, min.*<br>tyte Enable Pulse Width, min.*<br>hip Enable Pulse Width, min.*<br>yie Enable Access Time, max.*<br>hip Enable Access Time, max.*<br>ata Hold from Byte Enable Change, max.*<br>ata Hold from Chip Enable Change, max.* | 400 nsec.                                                  |

| DUTPUTS                                                                                                                                                                                                                                                       |                                                            |

|                                                                                                                                                                                                                                                               | 3.5V at 100 mA                                             |

| Output Voltage, nigh min.                                                                                                                                                                                                                                     | 0.4V at 1.6 mA                                             |

| low max. <sup>9</sup> .<br>Jourput Leakage Current (high Z state), max.<br>Deciliator Output Current, ( $V_0 = 2.5V$ )                                                                                                                                        | 1 μA                                                       |

| Jutput Leakage Current (nigh 2 state), max                                                                                                                                                                                                                    | 1 mA                                                       |

| Suffered Oscillator Output Current, $(V_0 = 2.5V)$                                                                                                                                                                                                            | 5 mA                                                       |

| PERFORMANCE                                                                                                                                                                                                                                                   |                                                            |

|                                                                                                                                                                                                                                                               | 15-bits plus sign                                          |

| Resolution                                                                                                                                                                                                                                                    | 2 LSB                                                      |

| Differential Linearity, max.                                                                                                                                                                                                                                  | ±0.5 LSB                                                   |

| Conversion Time                                                                                                                                                                                                                                               | 2.5 conv/sec. (400 msec.)                                  |

| Full-Scale Gain Tempco <sup>11</sup> max                                                                                                                                                                                                                      | 5 ppm/°C                                                   |

| Zero-Scale Error Tempco, max.                                                                                                                                                                                                                                 | 2 µV/°C                                                    |

| Full-Scale Magnitude Symmetry Error, max. <sup>12</sup>                                                                                                                                                                                                       | 2 LSB                                                      |

| POWER REQUIREMENTS                                                                                                                                                                                                                                            |                                                            |

| Supply Voltage                                                                                                                                                                                                                                                | ±5V                                                        |

| Supply Current, max                                                                                                                                                                                                                                           | ± 3.5 mA                                                   |

| typical                                                                                                                                                                                                                                                       | ±2.0 mA                                                    |

| PHYSICAL/ENVIRONMENTAL                                                                                                                                                                                                                                        | <u> </u>                                                   |

| Operating Temperature Range                                                                                                                                                                                                                                   | 0°C to +70°C                                               |

| Storage Temperature Range                                                                                                                                                                                                                                     | - 55°C to + 150°C                                          |

| _ead Temperature (soldering 60 sec)                                                                                                                                                                                                                           | + 300 °C                                                   |

| Package                                                                                                                                                                                                                                                       | 40-pin Plastic DIP                                         |

| OOTNOTES:                                                                                                                                                                                                                                                     |                                                            |

| 1. Vin = 0V                                                                                                                                                                                                                                                   |                                                            |

| 2. At 25°C, Vin = 0V. For 0°C to +70°C, lin = 125 pA.                                                                                                                                                                                                         |                                                            |

| 3. $Vcm = \pm 1V$ .                                                                                                                                                                                                                                           |                                                            |

| <ol><li>Not exceeded 95% of the time.</li></ol>                                                                                                                                                                                                               |                                                            |

| <ol> <li>Pin 18, 19, 20, 21 = 0V. Vout = 2V.</li> </ol>                                                                                                                                                                                                       |                                                            |

| 6. $V = 2V$ .                                                                                                                                                                                                                                                 |                                                            |

| 7. V = 3V.                                                                                                                                                                                                                                                    |                                                            |

| <ol><li>Parallel data transfer. (BUS/Hand = 0)</li></ol>                                                                                                                                                                                                      |                                                            |

| <ol> <li>For pins 18, 19, 20. lout = 750 µA.</li> </ol>                                                                                                                                                                                                       |                                                            |

| a. Foi pins 18, 14, 20. lout = 700 pr.                                                                                                                                                                                                                        |                                                            |

| 10 - F.S. < Vin < + F.S., best straight line. End point is typically                                                                                                                                                                                          | C.0 COD.                                                   |

| 10 F.S. $\leq$ Vin $\leq$ + F.S., best straight line. End point is typically<br>11. External Reference Tempco = 0 ppm/°C 0°C $\leq$ T <sub>A</sub> $\leq$ +70°                                                                                                | PC.                                                        |

| 10 - F.S. < Vin < + F.S., best straight line. End point is typically                                                                                                                                                                                          | <i>и</i> с.                                                |

# **ADC-800**

# **TECHNICAL NOTES**

- 1. The internal class A output stage amplifiers will supply a 20 µA drive current with minimal linearity error. RINT is calculated for a 20  $\mu$ A full-scale current using the following expression: RINT (MΩ) = Full-Scale Input Voltage (V)/20.

- 2. The integrating capacitor should be selected to give the maximum integrator output voltage swing without saturating the integrator (approximately 0.4V from either supply). With a 20  $\mu\text{A}$  fullscale buffer output current, the integrating capacitor (CINT) is calculated as follows:  $\dot{C}_{INT}$  ( $\mu F$ ) = 16.384 (1/F<sub>CLK</sub> (kHz) (20 µA)/Integrator Output Voltage Swing (V). With an external 2.4576 MHz crystal, the clock frequency will be 163.8 kHz and conversion time is 2.5 CONV/SEC. A 0.47 µF CINT is recommended with low dielectric absorption such as polypropylene to prevent rollover errors. The outer foil of CINT should be connected to Pin 31.

- 3. A 1.0 µF polypropylene capacitor is recommended for CSZ. (System Zero Capacitor.) The inner foil should be connected to Pin 32.

- 4. For the reference capacitor, a 1.0 μF is recommended. Larger values may be used to limit roll-over errors. Low leakage capacitors, such as polypropylene should be used.

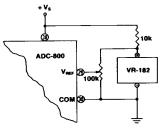

- 5. The analog input required to generate the 32,768 8 full-scale count is 2 VREF. The reference voltage source should be selected for temperature stability. The ADC-800 will provide 30 ppm resolution. With a 5 ppm/°C reference, a 6° change in temperature will introduce a 1-bit absolute error. A stable reference must be used where ambient temperature is controlled and accurate absolute measurements are needed. The reference voltage input must be a positive voltage with respect to analog common. A reference circuit is shown below.

- 6. The R<sub>S</sub> (delay resistor) in combination with CINT compensate for comparator delay time. With a 0.47 µF CINT, a 200 series resistor is recommended.

### **REFERENCE VOLTAGE CIRCUIT**

1

# D/ANEL

# **PIN DESCRIPTION**

| Sec. 2 |        | B. S. S. S. |  |

|--------|--------|-------------|--|

|        | <br>17 | ha          |  |

| PIN | SYMBOL                       | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | SGN                          | Sign Bit: Logic "1" indicates positive input. Input<br>signal polarity is determined at the end of the<br>signal integrate phase.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 2   | DB15 (MSB)                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 3   | DB14                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 4   | DB13                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5   | DB12                         | and the second state of th |

| 6   | DB11                         | and the second sec                                                                                                                                                                                                                                             |

| 7   | DB10                         | the second se<br>Second second                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 8   | D <b>B</b> 9                 | Data Bits. Three-State Outputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 9   | DB8                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 10  | DB7                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 11  | DB6                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 12  | DB5                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 13  | DB4                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 14  | DB3                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 15  | DB2                          | المراجع المراجع<br>المراجع المراجع                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 16  | DB1 (LSB)                    | and the growth of the second                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 17  | TEST                         | Test: Logic "0" forces data bits to Logic "1" and<br>disables clock. Logic "1" enables counter<br>latches.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 18  | LBEN/LBFLG<br>(Input/Output) | Low data byte enable input or flag output depend-<br>ing on BUS/HAND (Pin 21) status.<br>With BUS/HAND (Pin 21) low and CE/LDSTRB<br>(Pin 20) low, DBB through DB1 (low data byte)<br>are output, when input LBEN is low.<br>With BUS/HAND high, valid data (DB8-DB1) is<br>indicated by the Bag output LBFLG when<br>low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 19  | HBEN/HBFLG<br>(Input/Output) | High data byte enable input or flag output<br>depending on BUS/HAND (Pin 21) status.<br>With BUS/HAND (Pin 21) low and CE/LDSTRB<br>low, the sign bit and DB15-DB9 (high data<br>byte) are output, when input HBEN is low.<br>With BUS/HAND (Pin 21) high, valid data (sign<br>and DB15-DB9) is indicated by the flag output<br>HBFLG, when low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 20  | CE/LDSTRB<br>(Input/Output)  | With BUSHAND (Pin 21) low, CE (Pin 20) is<br>the master, CHIP ENABLE. When CE input is<br>high; the sign bit and DB15-DB1 are in the high<br>impedance state. With CE low, data is trans-<br>ferred under control of LBEN and HBEN input<br>signals as follows:           CE LBEN HBEN FUNCTION           0         1         Low data byte output           0         1         Low data byte output           0         1         Low data byte output           0         0         Low data byte output           0         0         Low and high data byte output           0         1         High impedance state           With BUS/HAND high (Pin 21). LDSTRB         Pin 20) is a load strobe output sign and a low out-<br>put signal instructs the receiving device to accept data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| PIN | SYMBOL            | DESCRIPTION                                                                                                                                                                                                                                           |  |

|-----|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 21  | BUS/HAND          | Input low, yields parallel output data mode.<br>The CE, HBEN and LBEN (Pins 20, 19, 18)<br>are inputs and directly control the 16 data<br>bits.                                                                                                       |  |

|     |                   | Input pulsed HIGH causes immediate entry<br>into handshake data transfer mode for<br>UART interfacing. LDSTRB, LBFLG and<br>HBFLG are TTL compatible outputs in this<br>mode.                                                                         |  |

| 22  | OSC IN            | Oscillator Input                                                                                                                                                                                                                                      |  |

| 23  | OSC OUT           | Oscillator Output                                                                                                                                                                                                                                     |  |

| 24  | OSC CON           | Selects internal oscillator structure. Input<br>high: RC oscillator. Internal clock frequency<br>is same frequency and duty cycle as BUF<br>OSC (Pin 25).<br>Input Low: Crystal oscillator. Internal clock<br>frequency is frequency at BUS OSC + 15. |  |

| 25  | BUF OSC           | Buffered oscillator output                                                                                                                                                                                                                            |  |

| 26  | CONVERT/STOP      | Input high: Performs continuous conversion.<br>Input low: Stops conversion process 7<br>counts before entering signal integrate<br>phase. Conversion in progress is completed.                                                                        |  |

| 27  | DRQST             | Data output request signal. Input used in the handshake mode to indicate an external device is ready to accept data.                                                                                                                                  |  |

| 28  | -V <sub>s</sub>   | Negative supply (-5V)                                                                                                                                                                                                                                 |  |

| 29  | V <sub>REF</sub>  | Voltage reference input                                                                                                                                                                                                                               |  |

| 30  | СОМ               | Analog common. The device is auto-zeroed to the analog common potential.                                                                                                                                                                              |  |

| 31  | V <sub>INT</sub>  | Integrator output                                                                                                                                                                                                                                     |  |

| 32  | C <sub>SZ</sub>   | System zero capacitor                                                                                                                                                                                                                                 |  |

| 33  | V <sub>BUF</sub>  | Input signal buffer output                                                                                                                                                                                                                            |  |

| 34  | -CR               | Negative reference capacitor connection                                                                                                                                                                                                               |  |

| 35  | +CR               | Positive reference capacitor connection                                                                                                                                                                                                               |  |

| 36  | – V <sub>IN</sub> | Negative differential analog input                                                                                                                                                                                                                    |  |

| 37  | +V <sub>IN</sub>  | Positive differential analog input                                                                                                                                                                                                                    |  |

| 38  | + V <sub>S</sub>  | Positive supply (+.5V)                                                                                                                                                                                                                                |  |

| 39  | DIG GND           | Ground return for all digital logic                                                                                                                                                                                                                   |  |

| 40  | DVD               | Data valid signal: high during signal inte-<br>grate and reference integrate phases until<br>data is tatched. Low when in auto zero<br>phase. Data does not change when<br>$\overline{DVD} = 0$                                                       |  |

# D/ANEL

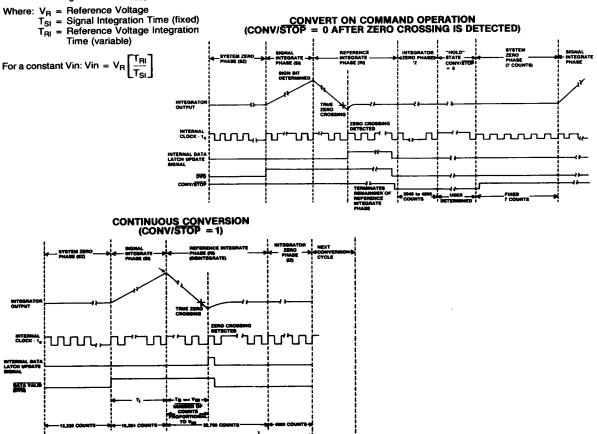

## TIMING AND OPERATION

# THE CONVERSION PROCESS

The conventional dual-slope converter measurement cycle has two distinct phases: Input signal Integration, and Reference Voltage Integration (deintegration).

The analog input signal is integrated for a fixed time period which is measured by counting clock pulses. An opposite polarity constant reference voltage is then integrated until the integrator output returns to zero. The reference voltage integration time is directly proportional to the input signal. A complete conversion requires the integrator output to "rampup" and "ramp-down".

The ADC-800's accuracy is unrelated to the integrating resistor and capacitor values as long as they are stable during a measurement cycle. An inherent advantage in the dual-slope converter is noise immunity. Noise spikes are integrated or averaged to zero during the integration periods.

The following equation relates the input signal, reference voltage and integration time:

$$\frac{1}{RC} \int_{0}^{T_{SI}} \frac{V_{R} T_{RI}}{RC} = \frac{V_{R} T_{RI}}{RC}$$

## ANALOG INPUT DESCRIPTION

System Zero Phase: Errors due to buffer, integrator and comparator offset voltages are compensated for by charging C<sub>SZ</sub> with a compensating error voltage.

Input Signal Integration Phase: The differential voltage between the inputs is integrated. The differential voltage must be within the specified common-mode range. The input signal is integrated for 16,384 clock cycles. The polarity is determined at the end of the phase.

Reference Voltage Integration: CR (Reference Capacitor), which was previously charged is connected with proper polarity to ramp the integrator output back to zero. The time for the output to return to zero is proportional to the input signal magnitude. This phase lasts for a maximum of 32,768 clock periods.

Integrator Output Zero: This phase guarantees the integrator output is at zero volts when the system zero phase is entered and that the true system offset voltages are compensated for. This phase lasts for 4096 clock cycles.

**ADC-800**

# D/ANEL

## TIMING AND OPERATION (CONT.)

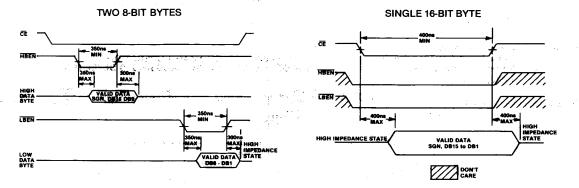

### PARALLEL MODE DATA TRANSFER

With BUS/HAND at logic "0", the sign and data bits are controlled by the CE/LOSTRB (Pin 20), LBEN/LBFLG (Pin 18) and HBEN/HBFLG (Pin 19) inputs. These inputs include internal pull-up resistors. Inactive data bits are in the high impedance state.

The HBEN/HBFLG signal controls the most significant data byte (SGN, DB15-DB9) and LBEN/LBFLG (Pin 18) controls the least significant data byte (DB8-DB1). See adjacent TRUTH TABLE.

These input signals are asynchronous with the internal clock. Output data is immediately available. To avoid accessing data as it is updated, the DATA VALID (Pin 40) can be used to control data access. Data will not change if DVD = 0.

## TRUTH TABLE

| CE/LDSTRB<br>(Pin 20) | HBEN/HBFLG<br>(Pin 19) | (Pin 18) | HIGH DATA BYTE<br>(SGN,DB15-DB9) | LOW DATA BYTE<br>(D68-DB1) |

|-----------------------|------------------------|----------|----------------------------------|----------------------------|

| 1                     | X                      | X        | Inactive                         | Inactive                   |

| 0                     | 0                      | .0 .     | Active                           | Active                     |

| 0                     | .0                     | 1        | Active                           | Inactive                   |

| 0                     | i.                     | 0        | Inactive                         | Active                     |

| 0                     | 1                      | , 1,     | Inactive                         | Inactive                   |

|                       |                        |          |                                  |                            |

Inactive = High "Z" state

"X" = 1 or 0

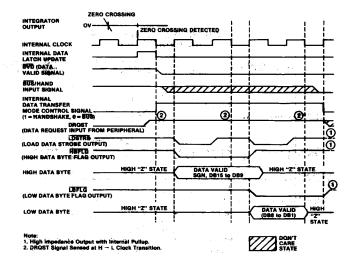

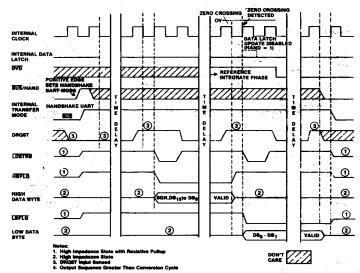

### PARALLEL DATA TRANSFER

### HANDSHAKE MODE DATA TRANSFER

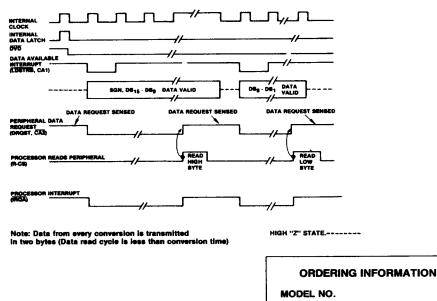

The ADC-800 actively controls the data transfer to peripherals through the handshake data transfer mode. In this mode LBEN/LBFLG, HBEN/HBFLG and CE/LDSTRB (Pins 18, 19, 20) are TTL compatible outputs. The LDSTRB signal indicates valid data is available for the peripheral. The LBFLG and HBFLG signals indicate which data byte is being transferred. DRQST (Pin 27) informs the A/D that a peripheral is ready to accept data. A complete cycle transfers two 8-bit bytes.

A logic "1" on BUS/HAND (Pin 21) enters the handshake mode after data is stored in the output data latches. Once the handshake mode internal latch is set, the BUS/HAND signal is ignored, the DRQST signal controls data transfer to the external requesting peripheral. (See adjacent diagram.)

This diagram shows the timing for the data transfer with BUS/HAND at logic "1" (throughout the transfer). Note that the DRQST is at logic "1" throughout the transfer. The transfer rate is set by the internal clock. A complete data transfer occurs in 4 clock periods after a DRQST logic "1" is detected on a high to low clock edge transition.

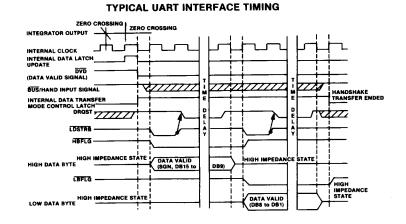

# TIMING AND OPERATION (CONT.)

For peripherals that are unable to accept data at the ADC-800 clock rate, the DRQST input signal can be used to delay the transmit sequence. This mode is useful in interfacing to UART's. (See above Timing Diagram.)

The UART data transfer sequence begins with a logic "1" on DRQST. This indicates the UART transmitter buffer register is empty (TBMT = 1). LDSTRB and HBFLG become active when DRQST is sensed synchronously. The high order data byte is stored in the UART transmitter buffer register when LDSTRB is logic "1". This occurs one clock period after DRQST is sensed. The DRQST signal (TBMT) goes low, stopping the cycle with the SGN and DB15-DB9 data bits active. After the UART transfers the received data to the transmitter register, the DRQST input (TBMT) again goes high. On the first high to low internal clock period later HBFLG goes to logic "1". Concurrently, LDSTRB is logic "0" and DB8-DB1 become active. One clock pulse later, LDSTRB is logic "1" and the low data byte is clocked into the UART transmitter buffer register. DRQST goes low.