查询ADE7768AR供应商

# **ANALOG DEVICES**

# Energy Metering IC with Integrated Oscillator and Positive Power Accumulation

# ADE7768

### **FEATURES**

On-chip oscillator as clock source

- High accuracy, supports 50 Hz/60 Hz IEC62053-21

- Less than 0.1% error over a dynamic range of 500 to 1

- Supplies positive-only average real power on frequency outputs F1 and F2

- High frequency output CF calibrates and supplies instantaneous, positive-only real power

- Logic output REVP indicates potential miswiring or negative power

- Direct drive for electromechanical counters and 2-phase stepper motors (F1 and F2)

- Proprietary ADCs and DSPs provide high accuracy over large variations in environmental conditions and time

- On-chip power supply monitoring

- On-chip creep protection (no-load threshold)

- On-chip reference 2.45 V (20 ppm/°C typical) with external overdrive capability

- Single 5 V supply, low power (20 mW typical) Low cost CMOS process

### **GENERAL DESCRIPTION**

Rev-A

The ADE7768<sup>1</sup> is a high accuracy, electrical energy metering IC. It is a pin reduction version of the ADE7755, enhanced with a precise oscillator circuit that serves as a clock source to the chip. The ADE7768 eliminates the cost of an external crystal or resonator, thus reducing the overall cost of a meter built with this IC. The chip directly interfaces with the shunt resistor.

<sup>1</sup>U.S. Patents 5,745,323; 5,760,617; 5,862,069; 5,872,469; others pending.

The ADE7768 specifications surpass the accuracy requirements of the IEC62053-21 standard. The AN-679 Application Note can be used as a basis for a description of an IEC61036 (equivalent to IEC62053-21) low cost, watt-hour meter reference design.

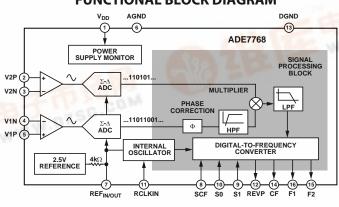

The only analog circuitry used in the ADE7768 is in the  $\Sigma$ - $\Delta$  ADCs and reference circuit. All other signal processing, such as multiplication and filtering, is carried out in the digital domain. This approach provides superior stability and accuracy over time and extreme environmental conditions.

The ADE7768 supplies positive-only average real power information on the low frequency outputs, F1 and F2. These outputs can be used to directly drive an electromechanical counter or interface with an MCU. The high frequency CF logic output, ideal for calibration purposes, provides instantaneous positive-only, real power information.

The ADE7768 includes a power supply monitoring circuit on the  $V_{DD}$  supply pin. The ADE7768 remains inactive until the supply voltage on  $V_{DD}$  reaches approximately 4 V. If the supply falls below 4 V, the ADE7768 also remains inactive and the F1, F2, and CF outputs are in their nonactive modes.

Internal phase matching circuitry ensures that the voltage and current channels are phase matched, while the HPF in the current channel eliminates dc offsets. An internal no-load threshold ensures that the ADE7768 does not exhibit creep when no load is present. When REVP is logic high, the ADE7768 does not generate any pulse on F1, F2, and CF.

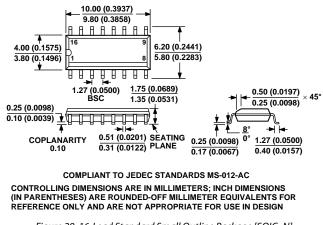

The ADE7768 comes in a 16-lead, narrow body SOIC package.

### FUNCTIONAL BLOCK DIAGRAM

#### Figure 1.

#### Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infiningements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and resistence trademarks are the parameter the properties of the

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 www.analog.com

# TABLE OF CONTENTS

| Specifications                               |

|----------------------------------------------|

| Timing Characteristics 4                     |

| Absolute Maximum Ratings                     |

| ESD Caution                                  |

| Terminology                                  |

| Pin Configuration and Function Descriptions7 |

| Typical Performance Characteristics          |

| Functional Description                       |

| Theory of Operation10                        |

| Analog Inputs11                              |

| Power Supply Monitor                     |                   |

|------------------------------------------|-------------------|

| Internal Oscillator (OSC)                |                   |

| Transfer Function                        |                   |

| Selecting a Frequency for an Energy Mete | er Application 15 |

| No-Load Threshold                        |                   |

| Negative Power Information               |                   |

| Evaluation Board and Reference Design E  | Board 16          |

| Outline Dimensions                       |                   |

| Ordering Guide                           |                   |

### **Revision History**

8/05—Sp0 to Rev. A

## **SPECIFICATIONS**

$V_{DD}$  = 5 V ± 5%, AGND = DGND = 0 V, on-chip reference, RCLKIN = 6.2 kΩ, 0.5% ± 50 ppm/°C,  $T_{MIN}$  to  $T_{MAX}$  = -40°C to +85°C, unless otherwise noted.

Table 1.

| Parameter                                   | Value | Unit            | Test Conditions/Comments                                                                                                       |

|---------------------------------------------|-------|-----------------|--------------------------------------------------------------------------------------------------------------------------------|

| ACCURACY <sup>1, 2</sup>                    |       |                 |                                                                                                                                |

| Measurement Error on Channel V1             | 0.1   | % reading typ   | Channel V2 with full-scale signal ( $\pm$ 165 mV),<br>25°C over a dynamic range 500 to 1,<br>line frequency = 45 Hz to 65 Hz   |

| Phase Error <sup>1</sup> Between Channels   |       |                 |                                                                                                                                |

| V1 Phase Lead 37° (PF = 0.8 Capacitive)     | ±0.1  | Degrees (°) max |                                                                                                                                |

| V1 Phase Lag 60° (PF = 0.5 Inductive)       | ±0.1  | Degrees (°) max |                                                                                                                                |

| AC Power Supply Rejection <sup>1</sup>      |       |                 |                                                                                                                                |

| Output Frequency Variation (CF)             | 0.2   | % reading typ   | S0 = S1 = 1, V1 = 21.2  mV rms, V2 = 116.7  mV rms @<br>50 Hz, ripple on V <sub>DD</sub> of 200 mV rms @ 100 Hz                |

| DC Power Supply Rejection <sup>1</sup>      |       |                 |                                                                                                                                |

| Output Frequency Variation (CF)             | ±0.3  | % reading typ   | $S0 = S1 = 1, V1 = 21.2 \text{ mV rms}, V2 = 116.7 \text{ mV rms}, V_{DD} = 5 \text{ V} \pm 250 \text{ mV}$                    |

| ANALOG INPUTS                               |       |                 | See the Analog Inputs section                                                                                                  |

| Channel V1 Maximum Signal Level             | ±30   | mV max          | V1P and V1N to AGND                                                                                                            |

| Channel V2 Maximum Signal Level             | ±165  | mV max          | V2P and V2N to AGND                                                                                                            |

| Input Impedance (DC)                        | 320   | kΩ min          | $OSC = 450 \text{ kHz}$ , $RCLKIN = 6.2 \text{ k}\Omega$ , $0.5\% \pm 50 \text{ ppm/°C}$                                       |

| Bandwidth (–3 dB)                           | 7     | kHz nominal     | $OSC = 450 \text{ kHz}$ , $RCLKIN = 6.2 \text{ k}\Omega$ , $0.5\% \pm 50 \text{ ppm/°C}$                                       |

| ADC Offset Error <sup>1, 2</sup>            | ±18   | mV max          | See the Terminology and the Typical Performance<br>Characteristics sections                                                    |

| Gain Error <sup>1</sup>                     | ±4    | % ideal typ     | External 2.5 V reference, $V1 = 21.2 \text{ mV rms}$ , $V2 = 116.7 \text{ mV rms}$                                             |

| OSCILLATOR FREQUENCY (OSC)                  | 450   | kHz nominal     | RCLKIN = 6.2 kΩ, 0.5% ± 50 ppm/°C                                                                                              |

| Oscillator Frequency Tolerance <sup>1</sup> | ±12   | % reading typ   |                                                                                                                                |

| Oscillator Frequency Stability <sup>1</sup> | ±30   | ppm/°C typ      |                                                                                                                                |

| REFERENCE INPUT                             |       |                 |                                                                                                                                |

| REFIN/OUT Input Voltage Range               | 2.65  | V max           | 2.45 V nominal                                                                                                                 |

|                                             | 2.25  | V min           | 2.45 V nominal                                                                                                                 |

| Input Capacitance                           | 10    | pF max          |                                                                                                                                |

| ON-CHIP REFERENCE                           |       |                 | 2.45 V nominal                                                                                                                 |

| Reference Error                             | ±200  | mV max          |                                                                                                                                |

| Temperature Coefficient                     | ±20   | ppm/°C typ      |                                                                                                                                |

| LOGIC INPUTS <sup>3</sup>                   |       |                 |                                                                                                                                |

| SCF, S0, S1                                 |       |                 |                                                                                                                                |

| Input High Voltage, V <sub>INH</sub>        | 2.4   | V min           | $V_{DD} = 5 V \pm 5\%$                                                                                                         |

| Input Low Voltage, VINL                     | 0.8   | V max           | $V_{DD} = 5 \text{ V} \pm 5\%$                                                                                                 |

| Input Current, I <sub>IN</sub>              | ±1    | μA max          | Typically 10 nA, $V_{IN} = 0$ V to $V_{DD}$                                                                                    |

| Input Capacitance, C <sub>IN</sub>          | 10    | pF max          |                                                                                                                                |

| LOGIC OUTPUTS <sup>3</sup>                  |       |                 |                                                                                                                                |

| F1 and F2                                   |       |                 |                                                                                                                                |

| Output High Voltage, V <sub>он</sub>        | 4.5   | V min           | $I_{\text{SOURCE}} = 10 \text{ mA}, V_{\text{DD}} = 5 \text{ V}, I_{\text{SINK}} = 10 \text{ mA}, V_{\text{DD}} = 5 \text{ V}$ |

| Output Low Voltage, Vol                     | 0.5   | V max           |                                                                                                                                |

| CF                                          |       |                 |                                                                                                                                |

| Output High Voltage, V <sub>он</sub>        | 4     | V min           | $I_{SOURCE} = 5 \text{ mA}, V_{DD} = 5 \text{ V}, I_{SINK} = 5 \text{ mA}, V_{DD} = 5 \text{ V}$                               |

| Output Low Voltage, Vol                     | 0.5   | V max           |                                                                                                                                |

| Frequency Output Error <sup>1, 2</sup> (CF) | ±10   | % ideal typ     | External 2.5 V reference, V1 = 21.2 mV rms,<br>V2 = 116.7 mV rms                                                               |

| Parameter       | Value | Unit   | Test Conditions/Comments  |  |

|-----------------|-------|--------|---------------------------|--|

| POWER SUPPLY    |       |        | For specified performance |  |

| V <sub>DD</sub> | 4.75  | V min  | 5 V – 5%                  |  |

|                 | 5.25  | V max  | 5 V + 5%                  |  |

| IDD             | 5     | mA max | Typically 4 mA            |  |

<sup>1</sup> See the Terminology section for an explanation of specifications.

<sup>2</sup> See the figures in the Typical Performance Characteristics section.

<sup>3</sup> Sample tested during initial release and after any redesign or process change that may affect this parameter.

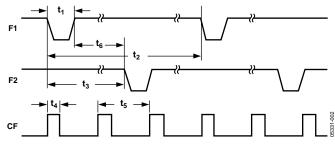

### **TIMING CHARACTERISTICS**

$V_{DD} = 5 \text{ V} \pm 5\%$ , AGND = DGND = 0 V, on-chip reference, RCLKIN = 6.2 k $\Omega$ , 0.5%  $\pm$  50 ppm/°C, T<sub>MIN</sub> to T<sub>MAX</sub> = -40°C to +85°C, unless otherwise noted. Sample tested during initial release and after any redesign or process change that may affect this parameter. See Figure 2.

#### Table 2.

| Parameter          | Specifications     | Unit | Test Conditions/Comments                                |

|--------------------|--------------------|------|---------------------------------------------------------|

| t1 <sup>1</sup>    | 120                | ms   | F1 and F2 pulse width (logic low)                       |

| t <sub>2</sub>     | See Table 6        | sec  | Output pulse period. See the Transfer Function section. |

| t <sub>3</sub>     | 1/2 t <sub>2</sub> | sec  | Time between the F1 and F2 falling edges.               |

| t4 <sup>1, 2</sup> | 90                 | ms   | CF pulse width (logic high).                            |

| t <sub>5</sub>     | See Table 7        | sec  | CF pulse period. See the Transfer Function section.     |

| t <sub>6</sub>     | 2                  | μs   | Minimum time between the F1 and F2 pulses.              |

<sup>1</sup> The pulse widths of F1, F2, and CF are not fixed for higher output frequencies. See the Frequency Outputs section.

<sup>2</sup> The CF pulse is always 35 µs in high frequency mode. See the Frequency Outputs section and Table 7.

Figure 2. Timing Diagram for Frequency Outputs

### **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25^{\circ}C$ , unless otherwise noted.

### Table 3.

| Parameter                                      | Value                             |

|------------------------------------------------|-----------------------------------|

| V <sub>DD</sub> to AGND                        | –0.3 V to +7 V                    |

| V <sub>DD</sub> to DGND                        | –0.3 V to +7 V                    |

| Analog Input Voltage to AGND,                  |                                   |

| V1P, V1N, V2P, and V2N                         | –6 V to +6 V                      |

| Reference Input Voltage to AGND                | -0.3 V to V <sub>DD</sub> + 0.3 V |

| Digital Input Voltage to DGND                  | -0.3 V to V <sub>DD</sub> + 0.3 V |

| Digital Output Voltage to DGND                 | -0.3 V to V <sub>DD</sub> + 0.3 V |

| Operating Temperature Range                    | -40°C to +85°C                    |

| Storage Temperature Range                      | –65°C to +150°C                   |

| Junction Temperature                           | 150°C                             |

| 16-Lead Plastic SOIC, Power Dissipation        | 350 mW                            |

| θ <sub>JA</sub> Thermal Impedance <sup>1</sup> | 124.9°C/W                         |

| Package Temperature Soldering                  | See J-STD-20                      |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

<sup>1</sup> JEDEC 1S standard (2-layer) board data.

### **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although this product features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

# TERMINOLOGY

### Measurement Error

The error associated with the energy measurement made by the ADE7768 is defined by the following formula:

$\% Error = \frac{Energy \ Registered \ by \ ADE7768 - True \ Energy}{True \ Energy} \times 100\%$

### Phase Error Between Channels

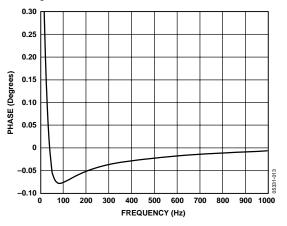

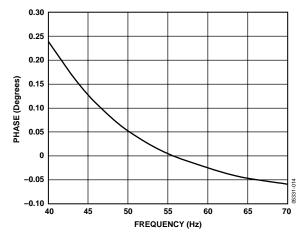

The high-pass filter (HPF) in the current channel (Channel V1) has a phase-lead response. To offset this phase response and equalize the phase response between channels, a phase-correction network is also placed in Channel V1. The phase-correction network matches the phase to within 0.1° over a range of 45 Hz to 65 Hz, and 0.2° over a range 40 Hz to 1 kHz (see Figure 24 and Figure 25).

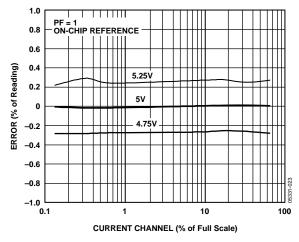

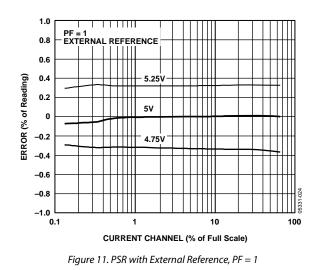

### Power Supply Rejection (PSR)

This quantifies the ADE7768 measurement error as a percentage of reading when the power supplies are varied.

For the ac PSR measurement, a reading at nominal supplies (5 V) is taken. A 200 mV rms/100 Hz signal is then introduced onto the supplies and a second reading is obtained under the same input signal levels. Any error introduced is expressed as a percentage of reading—see the Measurement Error definition.

For the dc PSR measurement, a reading at nominal supplies (5 V) is taken. The supplies are then varied 5% and a second reading is obtained with the same input signal levels. Any error introduced is again expressed as a percentage of the reading.

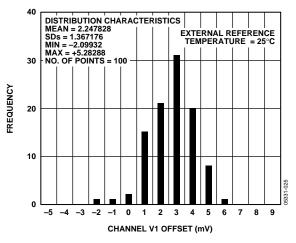

### ADC Offset Error

This refers to the small dc signal (offset) associated with the analog inputs to the ADCs. However, the HPF in Channel V1 eliminates the offset in the circuitry. Therefore, the power calculation is not affected by this offset.

### Frequency Output Error (CF)

The frequency output error of the ADE7768 is defined as the difference between the measured output frequency (minus the offset) and the ideal output frequency. The difference is expressed as a percentage of the ideal frequency. The ideal frequency is obtained from the ADE7768 transfer function.

### **Gain Error**

The gain error of the ADE7768 is defined as the difference between the measured output of the ADCs (minus the offset) and the ideal output of the ADCs. The difference is expressed as a percentage of the ideal of the ADCs.

### **Oscillator Frequency Tolerance**

The oscillator frequency tolerance of the ADE7768 is defined as the part-to-part frequency variation in terms of percentage at room temperature (25°C). It is measured by taking the difference between the measured oscillator frequency and the nominal frequency defined in the Specifications section.

### **Oscillator Frequency Stability**

Oscillator frequency stability is defined as frequency variation in terms of the parts-per-million drift over the operating temperature range. In a metering application, the temperature range is  $-40^{\circ}$ C to  $+85^{\circ}$ C. Oscillator frequency stability is measured by taking the difference between the measured oscillator frequency at  $-40^{\circ}$ C and  $+85^{\circ}$ C and the measured oscillator frequency at  $+25^{\circ}$ C.

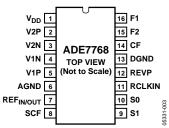

## **PIN CONFIGURATION AND FUNCTION DESCRIPTIONS**

Figure 3. Pin Configuration

| Pin No. | Mnemonic              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | V <sub>DD</sub>       | Power Supply. This pin provides the supply voltage for the circuitry in the ADE7768. The supply voltage should be maintained at 5 V $\pm$ 5% for specified operation. This pin should be decoupled with a 10 $\mu$ F capacitor in parallel with a 100 nF ceramic capacitor.                                                                                                                                                                                                                                                                                   |

| 2, 3    | V2P, V2N              | Analog Inputs for Channel V2 (Voltage Channel). These inputs provide a fully differential input pair. The maximum differential input voltage is $\pm 165$ mV for specified operation. Both inputs have internal ESD protection circuitry; an overvoltage of $\pm 6$ V can be sustained on these inputs without risk of permanent damage.                                                                                                                                                                                                                      |

| 4, 5    | V1N, V1P              | Analog Inputs for Channel V1 (Current Channel). These inputs are fully differential voltage inputs with a maximum signal level of $\pm 30$ mV with respect to the V1N pin for specified operation. Both inputs have internal ESD protection circuitry and, in addition, an overvoltage of $\pm 6$ V can be sustained on these inputs without risk of permanent damage.                                                                                                                                                                                        |

| 6       | AGND                  | This pin provides the ground reference for the analog circuitry in the ADE7768, that is, the ADCs and reference. This pin should be tied to the analog ground plane of the PCB. The analog ground plane is the ground reference for all analog circuitry, such as antialiasing filters, current and voltage sensors, and so forth. For accurate noise suppression, the analog ground plane should be connected to the digital ground plane at only one point. A star ground configuration helps to keep noisy digital currents away from the analog circuits. |

| 7       | REF <sub>IN/OUT</sub> | This pin provides access to the on-chip voltage reference. The on-chip reference has a nominal value of 2.45 V and a typical temperature coefficient of 20 ppm/°C. An external reference source may also be connected at this pin. In either case, this pin should be decoupled to AGND with a 1 µF tantalum capacitor and a 100 nF ceramic capacitor. The internal reference cannot be used to drive an external load.                                                                                                                                       |

| 8       | SCF                   | Select Calibration Frequency. This logic input is used to select the frequency on the calibration output CF. See Table 7.                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 9, 10   | S1, S0                | These logic inputs are used to select one of four possible frequencies for the digital-to-frequency conversion.<br>With this logic input, designers have greater flexibility when designing an energy meter. See the Selecting a<br>Frequency for an Energy Meter Application section.                                                                                                                                                                                                                                                                        |

| 11      | RCLKIN                | To enable the internal oscillator as a clock source to the chip, a precise low temperature drift resistor at a nominal value of 6.2 k $\Omega$ must be connected from this pin to DGND.                                                                                                                                                                                                                                                                                                                                                                       |

| 12      | REVP                  | This logic output goes high when negative power is detected, that is, when the phase angle between the voltage and current signals is greater than 90°. This output is not latched and is reset when positive power is once again detected. The output goes high or low at the same time that a pulse is issued on CF.                                                                                                                                                                                                                                        |

| 13      | DGND                  | This pin provides the ground reference for the digital circuitry in the ADE7768, that is, the multiplier, filters, and digital-to-frequency converter. This pin should be tied to the digital ground plane of the PCB. The digital ground plane is the ground reference for all digital circuitry, such as counters (mechanical and digital), MCUs, and indicator LEDs. For accurate noise suppression, the analog ground plane should be connected to the digital ground plane at one point only—a star ground.                                              |

| 14      | CF                    | Calibration Frequency Logic Output. The CF logic output provides instantaneous, positive-only real power information. This output is intended for calibration purposes. See the SCF pin description.                                                                                                                                                                                                                                                                                                                                                          |

| 15, 16  | F2, F1                | Low Frequency Logic Outputs. F1 and F2 supply average positive-only real power information. The logic outputs can be used to directly drive electromechanical counters and 2-phase stepper motors. See the Transfer Function section.                                                                                                                                                                                                                                                                                                                         |

### **TYPICAL PERFORMANCE CHARACTERISTICS**

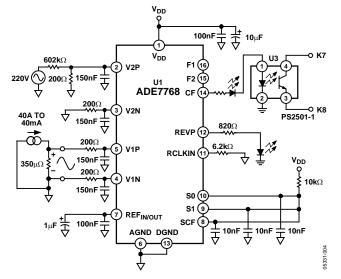

Figure 4. Test Circuit for Performance Curves

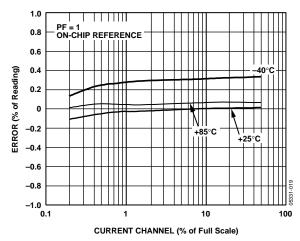

Figure 5. Error as a % of Reading over Temperature with On-Chip Reference (PF = 1)

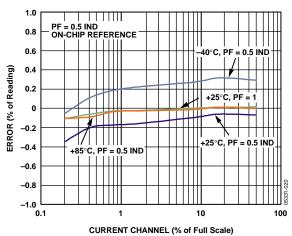

Figure 6. Error as a % of Reading over Temperature with On-Chip Reference (PF = 0.5 IND)

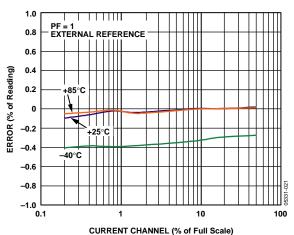

Figure 7. Error as a % of Reading over Temperature with External Reference (PF = 1)

CURRENT CHANNEL (% of Full Scale)

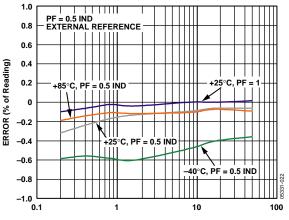

Figure 8. Error as a % of Reading over Temperature with External Reference (PF = 0.5 IND)

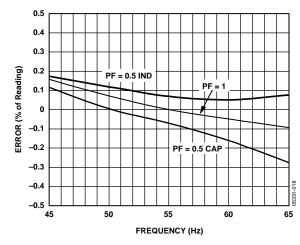

Figure 9. Error as a % of Reading over Input Frequency

Figure 10. PSR with On-Chip Reference, PF = 1

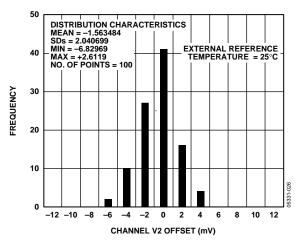

Figure 12. Channel V1 Offset Distribution

Figure 13. Channel V2 Offset Distribution

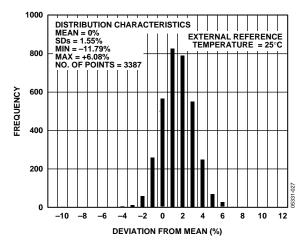

Figure 14. Part-to-Part CF Deviation from Mean

### FUNCTIONAL DESCRIPTION THEORY OF OPERATION

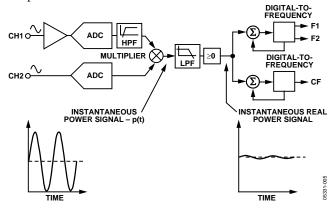

The two ADCs in the ADE7768 digitize the voltage signals from the current and voltage sensors. These ADCs are 16-bit  $\Sigma$ - $\Delta$ s with an oversampling rate of 450 kHz. This analog input structure greatly simplifies sensor interfacing by providing a wide dynamic range for direct connection to the sensor and by simplifying the antialiasing filter design. A high-pass filter in the current channel removes any dc component from the current signal. This eliminates any inaccuracies in the real power calculation due to offsets in the voltage or current signals.

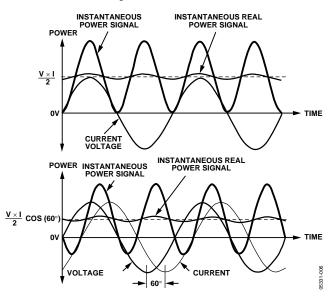

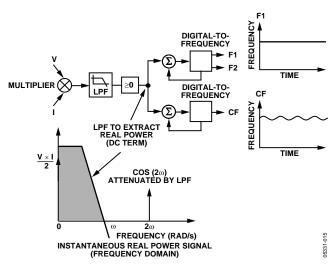

The real power calculation is derived from the instantaneous power signal. The instantaneous power signal is generated by a direct multiplication of the current and voltage signals. To extract the real power component (the dc component), the instantaneous power signal is low-pass filtered. Figure 15 illustrates the instantaneous real power signal and shows how the real power information can be extracted by low-pass filtering the instantaneous power signal. In the ADE7768, this signal is compared to 0 and only positive real power is accumulated for F1, F2, and CF pulse outputs. This scheme correctly calculates real power for sinusoidal current and voltage waveforms at all power factors. All signal processing is carried out in the digital domain for superior stability over temperature and time.

Figure 15. Signal Processing Block Diagram

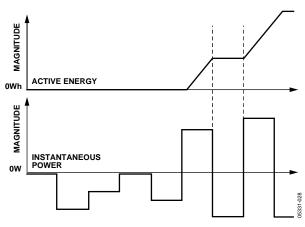

The low frequency outputs (F1 and F2) are generated by accumulating positive-only real power information. This low frequency inherently means a long accumulation time between output pulses. Consequently, the resulting output frequency is proportional to the average positive-only real power. This average positive-only real power information is then accumulated (by a counter) to generate real energy information (see Figure 16). Conversely, due to its high output frequency and shorter integration time, the CF output frequency is proportional to the instantaneous positive-only real power. This is useful for system calibration, which can be done faster under steady load conditions.

Figure 16. Positive-Only Energy Accumulation

#### **Power Factor Considerations**

The method used to extract the real power information from the instantaneous power signal (that is, by low-pass filtering) is still valid even when the voltage and current signals are not in phase. Figure 17 displays the unity power factor condition and a displacement power factor (DPF) = 0.5 (a current signal lagging the voltage by  $60^\circ$ ). Assuming that the voltage and current waveforms are sinusoidal, the real power component of the instantaneous power signal (that is, the dc term) is given by

$$\left(\frac{V \times I}{2}\right) \times \cos\left(60^{\circ}\right) \tag{1}$$

This is the correct real power calculation.

Figure 17. DC Component of Instantaneous Power Signal Conveys Real Power Information, PF < 1

#### Nonsinusoidal Voltage and Current

The real power calculation method also holds true for nonsinusoidal current and voltage waveforms. All voltage and current waveforms in practical applications have some harmonic content. Using the Fourier transform, instantaneous voltage and current waveforms can be expressed in terms of their harmonic content.

$$v(t) = V_0 + \sqrt{2 \times \sum_{h \neq 0}^{\infty} V_h} \times \sin(h\omega t + \alpha_h)$$

<sup>(2)</sup>

where:

v(t) is the instantaneous voltage.

$V_0$  is the average value.

$V_h$  is the rms value of voltage harmonic h.

$\alpha_h$  is the phase angle of the voltage harmonic.

$$i(t) = I_O + \sqrt{2} \times \sum_{h \neq o}^{\infty} I_h \times \sin(h\omega t + \beta_h)$$

(3)

where:

*i*(*t*) is the instantaneous current.*I*<sub>0</sub> is the dc component.*I*<sub>h</sub> is the rms value of current harmonic h.

$\beta_h$  is the phase angle of the current harmonic.

Using Equations 2 and 3, the real power (P) can be expressed in terms of its fundamental real power (P<sub>1</sub>) and harmonic real power (P<sub>H</sub>) as  $P = P_1 + P_H$

where:

$$P_I = V_I \times I_I \cos \phi_1 \tag{4}$$

$$\phi_I = \alpha_I - \beta_I$$

and

$$P_{H} = \sum_{h \neq l}^{\infty} V_{h} \times I_{h} \cos \phi_{h}$$

(5)

$$\phi_h = \alpha_h - \beta_h$$

In Equation 5, a harmonic real power component is generated for every harmonic, provided that harmonic is present in both the voltage and current waveforms. The power factor calculation has previously been shown to be accurate in a pure sinusoid. Therefore, the harmonic real power must also correctly account for the power factor, because it is made up of a series of pure sinusoids.

Note that the input bandwidth of the analog inputs is 7 kHz at the nominal internal oscillator frequency of 450 kHz.

### ANALOG INPUTS

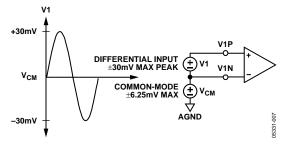

### **Channel V1 (Current Channel)**

The voltage output from the current sensor is connected to the ADE7768 here. Channel V1 is a fully differential voltage input. V1P is the positive input with respect to V1N.

The maximum peak differential signal on Channel V1 should be less than  $\pm 30$  mV (21 mV rms for a pure sinusoidal signal) for specified operation.

Figure 18. Maximum Signal Levels, Channel V1

Figure 18 shows the maximum signal levels on V1P and V1N. The maximum differential voltage is  $\pm 30$  mV. The differential voltage signal on the inputs must be referenced to a common mode, such as AGND. The maximum common-mode signal is  $\pm 6.25$  mV.

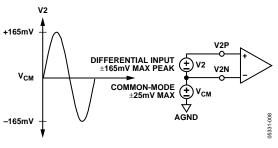

#### Channel V2 (Voltage Channel)

The output of the line voltage sensor is connected to the device at this analog input. Channel V2 is a fully differential voltage input with a maximum peak differential signal of  $\pm 165$  mV. Figure 19 shows the maximum signal levels that can be connected to the ADE7768 Channel V2.

Figure 19. Maximum Signal Levels, Channel V2

Channel V2 is usually driven from a common-mode voltage, that is, the differential voltage signal on the input is referenced to a common mode (usually AGND). The analog inputs of the ADE7768 can be driven with common-mode voltages of up to 25 mV with respect to AGND. However, best results are achieved using a common mode equal to AGND.

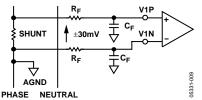

### **Typical Connection Diagrams**

Figure 20 shows a typical connection diagram for Channel V1. A shunt is the current sensor selected for this example because of its low cost compared to other current sensors, such as the current transformer (CT). This IC is ideal for low current meters.

Figure 20. Typical Connection for Channel V1

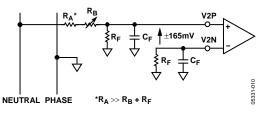

Figure 21 shows a typical connection for Channel V2. Typically, the ADE7768 is biased around the phase wire, and a resistor divider is used to provide a voltage signal that is proportional to the line voltage. Adjusting the ratio of  $R_{\text{A}},\,R_{\text{B}},\,\text{and}\,R_{\text{F}}$  is also a convenient way of carrying out a gain calibration on a meter.

Figure 21. Typical Connections for Channel V2

### **POWER SUPPLY MONITOR**

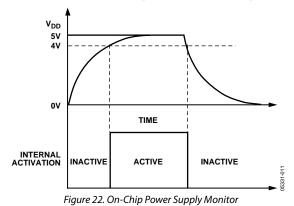

The ADE7768 contains an on-chip power supply monitor. The power supply (V<sub>DD</sub>) is continuously monitored by the ADE7768. If the supply is less than 4 V, the ADE7768 becomes inactive. This is useful to ensure proper device operation at power-up and power-down. The power supply monitor has built-in hysteresis and filtering, which provide a high degree of immunity to false triggering from noisy supplies.

In Figure 22, the trigger level is nominally set at 4 V. The tolerance on this trigger level is within  $\pm 5\%$ . The power supply and decoupling for the part should be such that the ripple at  $V_{\text{DD}}$ does not exceed 5 V  $\pm$  5%, as specified for normal operation.

### **HPF and Offset Effects**

Figure 23 shows the effect of offsets on the real power calculation. As can be seen, offsets on Channel V1 and Channel V2 contribute a dc component after multiplication. Because this dc component is extracted by the LPF and used to generate the real power information, the offsets contribute a constant error to the real power calculation. This problem is easily avoided by the built-in HPF in Channel V1. By removing the offsets from at least one channel, no error component can be generated at dc by the multiplication. Error terms at the line frequency ( $\omega$ ) are removed by the LPF and the digital-to-frequency conversion (see the Digital-to-Frequency Conversion section).

Equation 6 shows how the power calculation is affected by the dc offsets in the current and voltage channels. 1

$$\{V \cos(\omega t) + V_{OS}\} \times \{I \cos(\omega t) + I_{OS}\}$$

(6)

$$= \frac{V \times I}{2} + V_{OS} \times I_{OS} + V_{OS} \times I \cos(\omega t) + I_{OS} \times V \cos(\omega t)$$

$$+ \frac{V \times I}{2} \times \cos(2\omega t)$$

$$V_{OS} \times I_{OS}$$

$$\frac{V \times I}{2}$$

$$\frac{V \times I}{V_{OS} \times I}$$

$$\frac{V \times I}{2}$$

$$\frac{V \times I}{V_{OS} \times I}$$

$$\frac{V \times I}{2}$$

$$\frac{V \times I}{V_{OS} \times I}$$

$$\frac{V \times I}{V_{OS} \times I}$$

Figure 23. Effect of Channel Offset on the Real Power Calculation

The HPF in Channel V1 has an associated phase response that is compensated for on chip. Figure 24 and Figure 25 show the phase error between channels with the compensation network activated. The ADE7768 is phase compensated up to 1 kHz as shown. This ensures correct active harmonic power calculation even at low power factors.

Figure 24. Phase Error Between Channels (0 Hz to 1 kHz)

Figure 25. Phase Error Between Channels (40 Hz to 70 Hz)

### Digital-to-Frequency Conversion

As previously described, the digital output of the low-pass filter after multiplication contains the positive-only real power information. However, because this LPF is not an ideal brick wall filter implementation, the output signal also contains attenuated components at the line frequency and its harmonics, that is,  $\cos(h\omega t)$  where h = 1, 2, 3, ... and so on.

The magnitude response of the filter is given by

$$\left|H(f)\right| = \frac{1}{\sqrt{1 + \frac{f^2}{4.45^2}}}$$

(7)

For a line frequency of 50 Hz, this gives an attenuation of the  $2\omega$  (100 Hz) component of approximately 22 dB. The dominating harmonic is twice the line frequency ( $2\omega$ ) due to the instantaneous power calculation.

Figure 26 shows the instantaneous positive-only real power signal at the output of the LPF that still contains a significant amount of instantaneous power information, that is, cos(2 $\omega$ t). This signal is then passed to the digital-to-frequency converter where it is compared to 0 and only positive real power is integrated (accumulated) over time to produce an output frequency. The accumulation of the signal suppresses or averages out any non-dc components in the instantaneous positive-only real power signal. The average value of a sinusoidal signal is 0. Thus, the frequency generated by the ADE7768 is proportional to the average positive-only real power. Figure 26 shows the digital-to-frequency conversion for steady load conditions, that is, the constant voltage and current.

Figure 26. Positive-Only, Real Power-to-Frequency Conversion

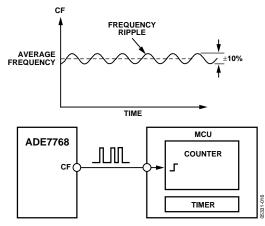

In Figure 26, the frequency output CF varies over time, even under steady load conditions. This frequency variation is primarily due to the  $cos(2\omega t)$  component in the instantaneous positive-only real power signal. The output frequency on CF can be up to 2048 times higher than the frequency on F1 and F2. This higher output frequency is generated by accumulating the instantaneous positive-only real power signal over a much shorter time while converting it to a frequency. This shorter accumulation period means less averaging of the  $cos(2\omega t)$ component. Consequently, some of this instantaneous power signal passes through the digital-to-frequency conversion. This is not a problem in the application. Where CF is used for calibration purposes, the frequency should be averaged by the frequency counter, which removes any ripple. If CF is used to measure energy, such as in a microprocessor-based application, the CF output should also be averaged to calculate power.

Because the F1 and F2 outputs operate at a much lower frequency, much more averaging of the instantaneous positiveonly real power signal is carried out. The result is a greatly attenuated sinusoidal content and a virtually ripple-free frequency output.

### Connecting to a Microcontroller for Energy Measurement

The easiest way to interface the ADE7768 to a microcontroller is to use the CF high frequency output with the output frequency scaling set to  $2048 \times F1$ , F2. This is done by setting SCF = 0 and S0 = S1 = 1 (see Table 7). With full-scale ac signals on the analog inputs, the output frequency on CF is approximately 2.867 kHz. Figure 27 illustrates one scheme that could be used to digitize the output frequency and carry out the necessary averaging mentioned in the previous section.

Figure 27. Interfacing the ADE7768 to an MCU

As shown in Figure 27, the frequency output CF is connected to an MCU counter or port. This counts the number of pulses in a given integration time, which is determined by an MCU internal timer. The average power proportional to the average frequency is given by

Average Frequency = Average Power =

$$\frac{Counter}{Time}$$

(8)

The energy consumed during an integration period is given by

$$Energy = Average \ Power \times Time = \frac{Counter}{Time} \times Time = Counter \ (9)$$

For the purpose of calibration, this integration time could be 10 seconds to 20 seconds, to accumulate enough pulses to ensure correct averaging of the frequency. In normal operation, the integration time could be reduced to 1 second or 2 seconds, depending, for example, on the required update rate of a display. With shorter integration times on the MCU, the amount of energy in each update may still have some small amount of ripple, even under steady load conditions. However, over a minute or more the measured energy has no ripple.

### **Power Measurement Considerations**

Calculating and displaying power information always has some associated ripple, which depends on the integration period used in the MCU to determine average power and also on the load. For example, at light loads, the output frequency may be 10 Hz. With an integration period of 2 seconds, only about 20 pulses are counted. The possibility of missing one pulse always exists, because the ADE7768 output frequency is running asynchronously to the MCU timer. This results in a 1-in-20 or 5% error in the power measurement. When REVP is logic high, the ADE7768 does not generate any pulse on F1, F2, and CF.

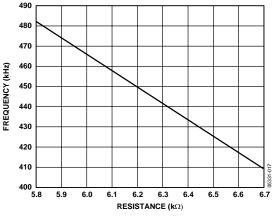

### **INTERNAL OSCILLATOR (OSC)**

The nominal internal oscillator frequency is 450 kHz when used with RCLKIN, with a nominal value of 6.2 k $\Omega$ . The frequency outputs are directly proportional to the oscillator frequency, thus RCLKIN must have low tolerance and low temperature drift to ensure stability and linearity of the chip. The oscillator frequency is inversely proportional to the RCLKIN, as shown in Figure 28. Although the internal oscillator operates when used with RCLKIN values between 5.5 k $\Omega$  and 20 k $\Omega$ , choosing a value within the range of the nominal value, as shown in Figure 28, is recommended.

Figure 28. Effect of RCLKIN on Internal Oscillator Frequency (OSC)

### **TRANSFER FUNCTION**

### Frequency Outputs F1 and F2

The ADE7768 calculates the product of two voltage signals (on Channel V1 and Channel V2) and then low-pass filters this product to extract positive-only real power information. This positive-only real power information is then converted to a frequency. The frequency information is output on F1 and F2 in the form of active low pulses. The pulse rate at these outputs is relatively low—for example, 0.175 Hz maximum for ac signals with S0 = S1 = 0 (see Table 6). This means that the frequency at these outputs is generated from positive-only real power information accumulated over a relatively long period of time. The result is an output frequency that is proportional to the average positive-only real power. The averaging of the positiveonly real power signal is implicit to the digital-to-frequency conversion. The output frequency or pulse rate is related to the input voltage signals by the following equation:

$$Freq = \frac{494.75 \times V I_{rms} \times V 2_{rms} \times F_{I-4}}{V_{REF}^{2}}$$

(10)

where:

Freq is the output frequency on F1 and F2 (Hz).

$V1_{rms}$  is the differential rms voltage signal on Channel V1 (V).  $V2_{rms}$  is the differential rms voltage signal on Channel V2 (V).  $V_{REF}$  is the reference voltage (2.45 V ± 200 mV) (V).  $F_{1-4}$  are one of four possible frequencies selected by using the S0 and S1 logic inputs (see Table 5).

| Table 5. F <sub>1-4</sub> Frequency Selection |            |                           |                                                   |  |  |

|-----------------------------------------------|------------|---------------------------|---------------------------------------------------|--|--|

| <b>S</b> 1                                    | <b>S</b> 0 | OSC Relation <sup>1</sup> | F <sub>1-4</sub> at Nominal OSC (Hz) <sup>2</sup> |  |  |

| 0                                             | 0          | OSC/2 <sub>19</sub>       | 0.86                                              |  |  |

| 0                                             | 1          | OSC/218                   | 1.72                                              |  |  |

| 1                                             | 0          | OSC/217                   | 3.43                                              |  |  |

| 1                                             | 1          | OSC/2 <sup>16</sup>       | 6.86                                              |  |  |

$^1F_{1\!-\!4}$  is a binary fraction of the internal oscillator frequency.  $^2Values$  are generated using the nominal frequency of 450 kHz.

#### Example

In this example, with ac voltages of  $\pm 30 \text{ mV}$  peak applied to V1 and  $\pm 165 \text{ mV}$  peak applied to V2, the expected output frequency is calculated as follows:

$F_{1-4} = OSC/2^{19} \text{ Hz}, S0 = S1 = 0$   $VI_{rms} = 0.03/\sqrt{2} \text{ V}$   $V2_{rms} = 0.165/\sqrt{2} \text{ V}$  $V_{REF} = 2.45 \text{ V}$  (nominal reference value)

Note that if the on-chip reference is used, actual output frequencies may vary from device to device due to the reference tolerance of  $\pm 200$  mV.

$$Freq = \frac{494.75 \times 0.03 \times 0.165 \times F_{I}}{\sqrt{2} \times \sqrt{2} \times 2.45^{2}} = 0.204 \times F_{I} = 0.175$$

(11)

#### Table 6. Maximum Output Frequency on F1 and F2

| S1 | <b>SO</b> | <b>OSC Relation</b> | Max Frequency <sup>1</sup> or AC Inputs (Hz) |

|----|-----------|---------------------|----------------------------------------------|

| 0  | 0         | $0.204 \times F_1$  | 0.175                                        |

| 0  | 1         | $0.204 \times F_2$  | 0.35                                         |

| 1  | 0         | $0.204 \times F_3$  | 0.70                                         |

| 1  | 1         | $0.204 \times F_4$  | 1.40                                         |

<sup>1</sup>Values are generated using the nominal frequency of 450 kHz.

### Frequency Output CF

The pulse output CF (calibration frequency) is intended for calibration purposes. The output pulse rate on CF can be up to 2048 times the pulse rate on F1 and F2. The lower the  $F_{1-4}$ frequency selected, the higher the CF scaling (except for the high frequency mode SCF = 0, S1 = S0 = 1). Table 7 shows how the two frequencies are related, depending on the states of the logic inputs S0, S1, and SCF. Due to its relatively high pulse rate, the frequency at the CF logic output is proportional to the instantaneous positive-only real power. As with F1 and F2, CF is derived from the output of the low-pass filter after multiplication. However, because the output frequency is high, this positive-only real power information is accumulated over a much shorter time. Therefore, less averaging is carried out in the digital-to-frequency conversion. With much less averaging of the positive-only real power signal, the CF output is much more responsive to power fluctuations (see the signal processing block diagram in Figure 15).

### Table 7. Maximum Output Frequency on CF

| Tuble / Huminum Sulput Frequency on Cl |            |            |                                         |

|----------------------------------------|------------|------------|-----------------------------------------|

| SCF                                    | <b>S</b> 1 | <b>S</b> 0 | CF Max for AC Signals (Hz) <sup>1</sup> |

| 1                                      | 0          | 0          | 128 × F1, F2 = 22.4                     |

| 0                                      | 0          | 0          | 64 × F1, F2 = 11.2                      |

| 1                                      | 0          | 1          | 64 × F1, F2 = 22.4                      |

| 0                                      | 0          | 1          | $32 \times F1, F2 = 11.2$               |

| 1                                      | 1          | 0          | $32 \times F1, F2 = 22.4$               |

| 0                                      | 1          | 0          | 16 × F1, F2 = 11.2                      |

| 1                                      | 1          | 1          | 16 × F1, F2 = 22.4                      |

| 0                                      | 1          | 1          | 2048 × F1, F2 = 2.867 kHz               |

<sup>1</sup> Values are generated using the nominal frequency of 450 kHz.

# SELECTING A FREQUENCY FOR AN ENERGY METER APPLICATION

As shown in Table 5, the user can select one of four frequencies. This frequency selection determines the maximum frequency on F1 and F2. These outputs are intended for driving an energy register (electromechanical or other). Because only four different output frequencies can be selected, the available frequency selection has been optimized for a meter constant of 100 imp/kWh with a maximum current of between 10 A and 120 A. Table 8 shows the output frequency for several maximum currents ( $I_{MAX}$ ) with a line voltage of 220 V. In all cases, the meter constant is 100 imp/kWh.

### Table 8. F1 and F2 Frequency at 100 imp/kWh

| I <sub>MAX</sub> (А) | F1 and F2 (Hz) |

|----------------------|----------------|

| 12.5                 | 0.076          |

| 25.0                 | 0.153          |

| 40.0                 | 0.244          |

| 60.0                 | 0.367          |

| 80.0                 | 0.489          |

| 120.0                | 0.733          |

The  $F_{1-4}$  frequencies allow complete coverage of this range of output frequencies (F1, F2). When designing an energy meter, the nominal design voltage on Channel V2 (voltage) should be set to half-scale to allow calibration of the meter constant. The current channel should also be no more than half scale when the meter sees maximum load. This allows overcurrent signals and signals with high crest factors to be accommodated. Table 9 shows the output frequency on F1 and F2 when both analog inputs are half scale. The frequencies in Table 9 align very well with those in Table 8 for maximum load.

| <b>S</b> 1 | <b>S</b> 0 | F <sub>1-4</sub> (Hz) | Frequency on F1 and F2—<br>CH1 and CH2 Half-Scale AC Input <sup>1</sup> |          |

|------------|------------|-----------------------|-------------------------------------------------------------------------|----------|

| 0          | 0          | 0.86                  | $0.051 \times F_1$                                                      | 0.044 Hz |

| 0          | 1          | 1.72                  | $0.051 \times F_2$                                                      | 0.088 Hz |

| 1          | 0          | 3.43                  | $0.051 \times F_3$                                                      | 0.176 Hz |

| 1          | 1          | 6.86                  | $0.051 	imes F_4$                                                       | 0.352 Hz |

<sup>1</sup>Values are generated using the nominal frequency of 450 kHz.

When selecting a suitable  $F_{1-4}$  frequency for a meter design, the frequency output at  $I_{MAX}$  (maximum load) with a meter constant of 100 imp/kWh should be compared with Column 4 of Table 9. The closest frequency in Table 9 determines the best choice of frequency ( $F_{1-4}$ ). For example, if a meter with a maximum current of 25 A is being designed, the output frequency on F1 and F2 with a meter constant of 100 imp/kWh is 0.153 Hz at 25 A and 220 V (from Table 8). In Table 9, the closest frequency to 0.153 Hz in Column 4 is 0.176 Hz. Therefore, as shown in Table 5, F3 (3.43 Hz) is selected for this design.

### **Frequency Outputs**

Figure 2 shows a timing diagram for the various frequency outputs. The F1 and F2 outputs are the low frequency outputs that can be used to directly drive a stepper motor or electromechanical impulse counter. The F1 and F2 outputs provide two alternating low frequency pulses. The F1 and F2 pulse widths ( $t_1$ ) are set such that if they fall below 240 ms (0.24 Hz), they are set to half of their period. The maximum output frequencies for F1 and F2 are shown in Table 6.

The high frequency CF output is intended for communications and calibration purposes. CF produces a 90-ms-wide active high pulse ( $t_4$ ) at a frequency proportional to active power. The CF output frequencies are given in Table 7. As with F1 and F2, if the period of CF ( $t_5$ ) falls below 180 ms, the CF pulse width is set to half the period. For example, if the CF frequency is 20 Hz, the CF pulse width is 25 ms.

When high frequency mode is selected (SCF = 0, S1 = S0 = 1), the CF pulse width is fixed at 35  $\mu$ s. Therefore, t<sub>4</sub> is always 35  $\mu$ s, regardless of output frequency on CF.

### **NO-LOAD THRESHOLD**

The ADE7768 includes a no-load threshold and start-up current feature that eliminates any creep effects in the meter. The ADE7768 is designed to issue a minimum output frequency. Any load generating a frequency lower than this minimum frequency does not cause a pulse to be issued on F1, F2, or CF. The minimum output frequency is given as 0.00244% for each of the  $F_{1-4}$  frequency selections (see Table 5).

For example, for an energy meter with a meter constant of 100 imp/kWh on F1, F2 using F<sub>3</sub> (3.43 Hz), the minimum output frequency at F1 or F2 would be 0.00244% of 3.43 Hz or  $8.38 \times 10^{-5}$  Hz. This would be  $2.68 \times 10^{-3}$  Hz at CF (32 × F1 Hz) when SCF = S0 = 1, S1 = 0. In this example, the no-load threshold would be equivalent to 3 W of load or a start-up current of 13.72 mA at 220 V. Compare this value to the IEC62053-21 specification which states that the meter must start up with a load equal to or less than 0.4% Ib. For a 5 A (Ib) meter, 0.4% of Ib is equivalent to 20 mA.

### **NEGATIVE POWER INFORMATION**

The ADE7768 detects when the current and voltage channels have a phase shift greater than 90°. This mechanism can detect an incorrect meter connection or the generation of negative power. The REVP pin output goes active high when negative power is detected and active low if positive power is detected. The REVP pin output changes state as a pulse is issued on CF.

# EVALUATION BOARD AND REFERENCE DESIGN BOARD

An evaluation board can be used to verify the functionality and the performance of the ADE7768. Download documentation for the board from http://www.analog.com/ADE7768.

In addition, the reference design board ADE7768ARN-REF and Application Note AN-679 can be used in the design of a low cost watt-hour meter that surpasses IEC62053-21 accuracy specifications. Download the application note from http://www.analog.com/ADE7768.

## **OUTLINE DIMENSIONS**

Figure 29. 16-Lead Standard Small Outline Package [SOIC\_N] Narrow Body (R-16) Dimensions shown in millimeters and (inches)

### **ORDERING GUIDE**

| Model                      | Temperature Range | Package Description                                  | Package Option |

|----------------------------|-------------------|------------------------------------------------------|----------------|

| ADE7768AR                  | -40°C to +85°C    | 16-Lead Standard Small Outline Package [SOIC_N]      | R-16           |

| ADE7768AR-RL               | -40°C to +85°C    | 16-Lead Standard Small Outline Package [SOIC_N] REEL | R-16           |

| ADE7768ARZ <sup>1</sup>    | -40°C to +85°C    | 16-Lead Standard Small Outline Package [SOIC_N]      | R-16           |

| ADE7768ARZ-RL <sup>1</sup> | -40°C to +85°C    | 16-Lead Standard Small Outline Package [SOIC_N] REEL | R-16           |

| ADE7768AR-REF              |                   | Reference Board                                      |                |

| EVAL-ADE7768EB             |                   | Evaluation Board                                     |                |

$^{1}$  Z = Pb-free part.

# NOTES

# NOTES

# NOTES

© 2005 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. D05331–0–8/05(A)

www.analog.com

Pov Al Page 20 of 20