查询ADG604YRUZ-REEL7供应商

# 1 pC Charge Injection, 100 pA Leakage CMOS $\pm 5$ V/5 V/3 V 4-Channel Multiplexer

# ADG604

#### FEATURES

1 pC Charge Injection (Over the Full Signal Range)  $\pm 2.7$  V to  $\pm 5.5$  V Dual Supply 2.7 V to 5.5 V Single Supply Automotive Temperature Range:  $-40^{\circ}$ C to  $+125^{\circ}$ C 100 pA Max @ 25°C Leakage Currents 85  $\Omega$  Typ On Resistance Rail-to-Rail Operation Fast Switching Times Typical Power Consumption (<0.1  $\mu$ W) TTL/CMOS Compatible Inputs 14-Lead TSSOP Package

#### APPLICATIONS Automatic Test Equipment

Data Acquisition Systems Battery-Powered Instruments Communication Systems Sample and Hold Systems Remote-Powered Equipment Audio and Video Signal Routing Relay Replacement Avionics

#### **GENERAL DESCRIPTION**

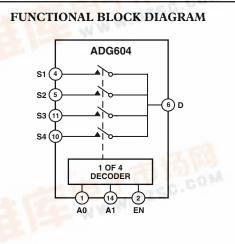

The ADG604 is a CMOS analog multiplexer, comprising four single channels. It operates from a dual supply of  $\pm 2.7$  V to  $\pm 5.5$  V, or from a single supply of 2.7 V to 5.5 V.

The ADG604 switches one of four inputs to a common output, D, as determined by the 3-bit binary address lines, A0, A1, and EN. A Logic "0" on the EN pin disables the device.

The ADG604 offers ultralow charge injection of  $\pm 1.5$  pC over the entire signal range and leakage currents of 10 pA typical at 25°C. It offers on resistance of 85  $\Omega$  typ, which is matched to within 2  $\Omega$  between channels. The ADG604 also has low power dissipation yet gives high switching speeds. The ADG604 is available in a 14-lead TSSOP package.

#### **PRODUCT HIGHLIGHTS**

- 1. Ultralow Charge Injection (Q<sub>INJ</sub>: ±1.5 pC Typ over the Full Signal Range)

- 2. Leakage Current <0.5 nA max @ 85°C

- 3. Dual  $\pm 2.7$  V to  $\pm 5.5$  V or Single 2.7 V to 5.5 V Supply

- 4. Fully Specified to 125°C

- 5. Small 14-Lead TSSOP Package

Formation furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use norfor any infringements of patents or other rights of third parties that may result from its use. No license is granted by implication or otherwise

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781/329-4700 www.analog.com

# ADG604-SPECIFICATIONS

# **DUAL SUPPLY**<sup>1</sup> ( $V_{DD} = +5 V \pm 10\%$ , $V_{SS} = -5 V \pm 10\%$ , GND = 0 V. All specifications -40°C to +125°C unless otherwise noted.)

| V <sub>SS</sub> to V <sub>DD</sub><br>.60<br>5.5<br>50 | V<br>Ω Typ<br>Ω Max<br>Ω Typ<br>Ω Max<br>Ω Typ<br>Ω Max | $V_{DD} = +4.5 \text{ V}, V_{SS} = -4.5 \text{ V}$<br>$V_S = \pm 3 \text{ V}, I_S = -1 \text{ mA},$<br>Test Circuit 1<br>$V_S = \pm 3 \text{ V}, I_S = -1 \text{ mA}$<br>$V_S = \pm 3 \text{ V}, I_S = -1 \text{ mA}$ |

|--------------------------------------------------------|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.5<br>50                                              | Ω Max<br>Ω Typ<br>Ω Max<br>Ω Typ                        | $V_S = \pm 3 V$ , $I_S = -1 mA$ ,<br>Test Circuit 1<br>$V_S = \pm 3 V$ , $I_S = -1 mA$                                                                                                                                |

| 50                                                     | Ω Typ<br>Ω Max<br>Ω Typ                                 |                                                                                                                                                                                                                       |

|                                                        |                                                         |                                                                                                                                                                                                                       |

| :4                                                     |                                                         |                                                                                                                                                                                                                       |

|                                                        | nA Typ<br>nA Max                                        | $V_{DD}$ = +5.5 V, $V_{SS}$ = -5.5 V<br>V <sub>S</sub> = ±4.5 V, $V_D$ = ∓4.5 V,<br>Test Circuit 2                                                                                                                    |

| -8                                                     | nA Typ<br>nA Max<br>nA Typ                              | $V_S = \pm 4.5 V, V_D = \mp 4.5 V,$<br>Test Circuit 2<br>$V_S = V_D = \pm 4.5 V,$ Test Circuit 3                                                                                                                      |

| 10                                                     | nA Max                                                  |                                                                                                                                                                                                                       |

| 2.4<br>0.8                                             | V Min<br>V Max                                          |                                                                                                                                                                                                                       |

| :0.1                                                   | μΑ Τγρ<br>μΑ Μax<br>pF Τγp                              | $V_{IN} = V_{INL}$ or $V_{INH}$                                                                                                                                                                                       |

|                                                        | rJr                                                     |                                                                                                                                                                                                                       |

| .50                                                    | ns Typ<br>ns Max                                        | $V_{S1}$ = +3 V, $V_{S4}$ = -3 V, $R_L$ = 300 Ω,<br>$C_L$ = 35 pF, Test Circuit 4                                                                                                                                     |

| 50                                                     | ns Max                                                  | $R_{L} = 300 \ \Omega, C_{L} = 35 \text{ pF}$<br>$V_{S} = 3 \text{ V}, \text{ Test Circuit 6}$<br>$R_{L} = 300 \ \Omega, C_{L} = 35 \text{ pF}$                                                                       |

| 55                                                     | ns Max<br>ns Typ                                        | $V_s = 3 V$ , Test Circuit 6<br>$R_L = 300 \Omega$ , $C_L = 35 pF$ ,                                                                                                                                                  |

| .0                                                     | ns Min<br>pC Typ<br>dB Typ                              | $V_{S1} = V_{S2} = 3 V, \text{ Test Circuit 5}$<br>$V_S = 0 V, R_S = 0 \Omega, C_L = 1 nF, \text{ Test Circuit 7}$<br>$R_L = 50 \Omega, C_L = 5 pF, f = 10 \text{ MHz},$                                              |

|                                                        | dB Typ                                                  | Test Circuit 8<br>$R_L = 50 \Omega$ , $C_L = 5 pF$ , $f = 10 MHz$ ,<br>Test Circuit 10                                                                                                                                |

|                                                        | MHz Typ<br>pF Typ<br>pF Typ<br>pF Typ                   | $R_{L} = 50 \Omega, C_{L} = 5 \text{ pF, Test Circuit 9}$<br>f = 1 MHz<br>f = 1 MHz<br>f = 1 MHz                                                                                                                      |

|                                                        | μА Тур                                                  | $V_{DD}$ = +5.5 V, $V_{SS}$ = -5.5 V<br>Digital Inputs = 0 V or 5.5 V                                                                                                                                                 |

|                                                        | µA Max                                                  |                                                                                                                                                                                                                       |

| .5<br>55                                               | 50<br>5                                                 | i0 ns Max<br>ns Typ<br>i0 ns Max<br>ns Typ<br>is Max<br>ns Typ<br>ns Max<br>ns Typ<br>ns Min<br>pC Typ<br>dB Typ<br>dB Typ<br>dB Typ<br>MHz Typ<br>pF Typ<br>pF Typ<br>pF Typ                                         |

NOTES

<sup>1</sup>Y Version Temperature Range: -40°C to +125°C

<sup>2</sup>Guaranteed by design, not subject to production test.

Specifications subject to change without notice.

#### -40°C to -40°C to 25°C +85°C +125°C Unit **Test Conditions/Comments** Parameter ANALOG SWITCH V Analog Signal Range 0 V to $V_{DD}$ $V_{DD} = 4.5 V, V_{SS} = 0 V$ $V_{\rm S}$ = 3.5 V, $I_{\rm S}$ = -1 mA, On Resistance (R<sub>ON</sub>) 210 ΩTyp 290 350 380 $\Omega$ Max Test Circuit 1 On Resistance Match Between 3 ΩTyp $V_{S} = 3.5 V, I_{S} = -1 mA$ Channels ( $\Delta R_{ON}$ ) 12 13 $\Omega$ Max $V_{DD}$ = 5.5 V LEAKAGE CURRENTS $V_{\rm S} = 1 \text{ V}/4.5 \text{ V}, V_{\rm D} = 4.5 \text{ V}/1 \text{ V},$ Source OFF Leakage $I_S$ (OFF) $\pm 0.01$ nA Typ $\pm 0.1$ $\pm 0.25$ $\pm 4$ nA Max Test Circuit 2 $V_{\rm S} = 1 \text{ V}/4.5 \text{ V}, V_{\rm D} = 4.5 \text{ V}/1 \text{ V},$ Drain OFF Leakage I<sub>D</sub> (OFF) $\pm 0.01$ nA Typ nA Max Test Circuit 2 $\pm 0.1$ $\pm 0.5$ $\pm 8$ Channel ON Leakage I<sub>D</sub>, I<sub>S</sub> (ON) nA Typ $V_{\rm S} = V_{\rm D} = 4.5 \text{ V/1 V},$ $\pm 0.01$ nA Max Test Circuit 3 $\pm 0.1$ $\pm 0.5$ 10 DIGITAL INPUTS Input High Voltage, V<sub>INH</sub> V Min 2.4Input Low Voltage, VINL V Max 0.8 Input Current $V_{IN} = V_{INL}$ or $V_{INH}$ I<sub>INL</sub> or I<sub>INH</sub> 0.005 uA Typ $\pm 0.1$ µA Max C<sub>IN</sub>, Digital Input Capacitance 2 pF Typ DYNAMIC CHARACTERISTICS<sup>2</sup> Transition Time 90 ns Typ $V_{S1} = 3 V, V_{S4} = 0 V, R_L = 300 \Omega$ , $C_L = 35 \text{ pF}$ , Test Circuit 4 150 185 210 ns Max ton Enable 105 ns Typ $R_L = 300 \Omega$ , $C_L = 35 pF$ $V_8 = 3 V$ , Test Circuit 6 150 190 220 ns Max 45 ns Typ $R_L$ = 300 $\Omega$ , $C_L$ = 35 pF toFF Enable 70 80 90 $V_s = 3 V$ , Test Circuit 6 ns Max Break-Before-Make Time Delay, t<sub>BBM</sub> 30 $R_{L} = 300 \Omega, C_{L} = 35 pF,$ ns Typ $V_{S1} = V_{S2} = 3 V$ , Test Circuit 5 10 ns Min Charge Injection 0.3 pC Typ $V_{S} = 0 V$ , $R_{S} = 0 \Omega$ , $C_{L} = 1 nF$ , Test Circuit 7

dB Typ

dB Typ

pF Typ

pF Typ

pF Typ

uA Typ

uA Max

1.0

MHz Typ

$R_L = 50 \Omega$ ,  $C_L = 5 pF$ , f = 10 MHz,

$R_{L} = 50 \Omega, C_{L} = 5 pF, f = 10 MHz,$

$R_L = 50 \Omega$ ,  $C_L = 5 pF$ , Test Circuit 9

Digital Inputs = 0 V or 5.5 V

Test Circuit 8

Test Circuit 10

f = 1 MHz

f = 1 MHzf = 1 MHz

$V_{DD} = 5.5 V$

# **SINGLE SUPPLY**<sup>1</sup> ( $V_{DD} = 5 V \pm 10\%$ , $V_{SS} = 0 V$ , GND = 0 V. All specifications -40°C to +125°C unless otherwise noted.)

POWER REQUIREMENTS

Channel-to-Channel Crosstalk

**Off** Isolation

C<sub>S</sub> (OFF)

C<sub>D</sub> (OFF)

$C_D, C_S(ON)$

Bandwidth -3 dB

NOTES

$\mathbf{I}_{\mathrm{DD}}$

<sup>1</sup>Y Version Temperature Range: -40°C to +125°C

<sup>2</sup>Guaranteed by design, not subject to production test.

-65

-70

250

5

17

18

0.001

Specifications subject to change without notice.

# ADG604-SPECIFICATIONS

**SINGLE SUPPLY<sup>1</sup>** ( $V_{DD} = 3 V \pm 10\%$ ,  $V_{SS} = 0 V$ , GND = 0 V. All specifications -40°C to +125°C unless otherwise noted.)

| Parameter                                                   | 25°C      | -40°C to<br>+85°C | -40°C to<br>+125°C | Unit    | Test Conditions/Comments                                                            |

|-------------------------------------------------------------|-----------|-------------------|--------------------|---------|-------------------------------------------------------------------------------------|

| ANALOG SWITCH                                               |           |                   |                    |         |                                                                                     |

| Analog Signal Range                                         |           |                   | 0 V to $V_{DD}$    | V       |                                                                                     |

| On Resistance (R <sub>ON</sub> )                            | 380       | 420               | 460                | ΩТур    | $V_{DD} = 2.7 V, V_{SS} = 0 V$<br>$V_{S} = 1.5 V, I_{S} = -1 mA,$<br>Test Circuit 1 |

| On Resistance Match Between<br>Channels ( $\Delta R_{ON}$ ) |           |                   | 5                  | ΩТур    | $V_{S} = 1.5 V, I_{S} = -1 mA$                                                      |

| LEAKAGE CURRENTS                                            |           |                   |                    |         | $V_{DD} = 3.3 V$                                                                    |

| Source OFF Leakage I <sub>S</sub> (OFF)                     | ±0.01     |                   |                    | nA Typ  | $V_{\rm S} = 1 \text{ V/3 V}, V_{\rm D} = 3 \text{ V/1 V},$                         |

|                                                             | ±0.1      | $\pm 0.25$        | $\pm 4$            | nA Max  | Test Circuit 2                                                                      |

| Drain OFF Leakage I <sub>D</sub> (OFF)                      | ±0.01     |                   |                    | nA Typ  | $V_{\rm S} = 1 \text{ V}/3 \text{ V}, V_{\rm D} = 3 \text{ V}/1 \text{ V},$         |

|                                                             | ±0.1      | $\pm 0.5$         | $\pm 8$            | nA Max  | Test Circuit 2                                                                      |

| Channel ON Leakage I <sub>D</sub> , I <sub>S</sub> (ON)     | ±0.01     |                   |                    | nA Typ  | $V_{\rm S} = V_{\rm D} = 1 \text{ V/3 V},$                                          |

|                                                             | $\pm 0.1$ | $\pm 0.5$         | $\pm 10$           | nA Max  | Test Circuit 3                                                                      |

| DIGITAL INPUTS                                              |           |                   |                    |         |                                                                                     |

| Input High Voltage, V <sub>INH</sub>                        |           |                   | 2.0                | V Min   |                                                                                     |

| Input Low Voltage, V <sub>INL</sub>                         |           |                   | 0.8                | V Max   |                                                                                     |

| Input Current                                               |           |                   |                    |         |                                                                                     |

| I <sub>INL</sub> or I <sub>INH</sub>                        | 0.005     |                   |                    | μА Тур  | $V_{IN} = V_{INL}$ or $V_{INH}$                                                     |

|                                                             |           |                   | $\pm 0.1$          | µA Max  |                                                                                     |

| C <sub>IN</sub> , Digital Input Capacitance                 | 2         |                   |                    | pF Typ  |                                                                                     |

| DYNAMIC CHARACTERISTICS <sup>2</sup>                        |           |                   |                    |         |                                                                                     |

| Transition Time                                             | 170       |                   |                    | ns Typ  | $V_{S1} = 2 V, V_{S4} = 0 V, R_L = 300 \Omega,$                                     |

|                                                             | 320       | 390               | 450                | ns Max  | $C_{L} = 35 \text{ pF}, \text{ Test Circuit 4}$                                     |

| t <sub>on</sub> Enable                                      | 180       | 550               | 130                | ns Typ  | $R_L = 300 \Omega, C_L = 35 \text{ pF}$                                             |

|                                                             | 250       | 265               | 390                | ns Max  | $V_{\rm S} = 2$ V, Test Circuit 6                                                   |

| t <sub>OFF</sub> Enable                                     | 100       |                   |                    | ns Typ  | $R_{L} = 300 \Omega, C_{L} = 35 pF$                                                 |

|                                                             | 160       | 205               | 225                | ns Max  | $V_s = 2 V$ , Test Circuit 6                                                        |

| Break-Before-Make Time Delay, t <sub>BBM</sub>              | 100       |                   |                    | ns Typ  | $R_{\rm L} = 300 \ \Omega, C_{\rm L} = 35 \ \text{pF},$                             |

|                                                             |           |                   | 10                 | ns Min  | $V_{S1} = V_{S2} = 2 V$ , Test Circuit 5                                            |

| Charge Injection                                            | 0.3       |                   |                    | рС Тур  | $V_{\rm S} = 0$ V to 3.3 V, $R_{\rm S} = 0$ $\Omega$ , $C_{\rm L} = 1$ $\mu$ F,     |

|                                                             |           |                   |                    |         | Test Circuit 7                                                                      |

| Off Isolation                                               | -65       |                   |                    | dB Typ  | $R_L = 50 \Omega$ , $C_L = 5 pF$ , $f = 10 MHz$ ,                                   |

|                                                             |           |                   |                    |         | Test Circuit 8                                                                      |

| Channel-to-Channel Crosstalk                                | 70        |                   |                    | dB Typ  | $R_L = 50 \Omega$ , $C_L = 5 pF$ , $f = 10 MHz$ ,                                   |

|                                                             |           |                   |                    |         | Test Circuit 10                                                                     |

| Bandwidth –3 dB                                             | 250       |                   |                    | MHz Typ | $R_L = 50 \Omega, C_L = 5 pF$ , Test Circuit 9                                      |

| $C_{S}(OFF)$                                                | 5         |                   |                    | pF Typ  | f = 1 MHz                                                                           |

| $C_{\rm D}$ (OFF)                                           | 17        |                   |                    | pF Typ  | f = 1 MHz                                                                           |

| $C_D, C_S(ON)$                                              | 18        |                   |                    | pF Typ  | f = 1 MHz                                                                           |

| POWER REQUIREMENTS                                          |           |                   |                    |         | $V_{DD} = 3.3 V$<br>Digital Inputs = 0 V or 3.3 V                                   |

| I <sub>DD</sub>                                             | 0.001     |                   |                    | μА Тур  |                                                                                     |

|                                                             |           |                   | 1.0                | µA Max  |                                                                                     |

NOTES

<sup>1</sup>Y Version Temperature Range: -40°C to +125°C

<sup>2</sup>Guaranteed by design, not subject to production test.

Specifications subject to change without notice.

#### ABSOLUTE MAXIMUM RATINGS<sup>1</sup>

| $(T_A = 25^{\circ}C \text{ unless otherwise noted})$                                                                                               |

|----------------------------------------------------------------------------------------------------------------------------------------------------|

| $V_{DD}$ to $V_{SS}$                                                                                                                               |

| $V_{DD}$ to GND $\ldots \ldots -0.3$ V to +6.5 V |

| $V_{SS}$ to GND +0.3 V to -6.5 V                                                                                                                   |

| Analog Inputs <sup>2</sup> $V_{SS}$ –0.3 V to $V_{DD}$ + 0.3 V                                                                                     |

| Digital Inputs <sup>2</sup> $-0.3$ V to V <sub>DD</sub> + 0.3 V or                                                                                 |

| 30 mA, Whichever Occurs First                                                                                                                      |

| Peak Current, S or D 20 mA                                                                                                                         |

| (Pulsed at 1 ms, 10% Duty Cycle Max)                                                                                                               |

| Continuous Current, S or D 10 mA                                                                                                                   |

| Operating Temperature Range                                                                                                                        |

| Automotive (Y Version)40°C to +125°C                                                                                                               |

| Storage Temperature Range65°C to +150°C                                                                                                            |

| Junction Temperature 150°C                     |

|------------------------------------------------|

| TSSOP Package                                  |

| $\theta_{JA}$ Thermal Impedance 150°C/W        |

| $\theta_{\rm IC}$ Thermal Impedance            |

| Lead Temperature, Soldering (10 seconds) 300°C |

| IR Reflow, Peak Temperature 220°C              |

#### NOTES

<sup>1</sup>Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those listed in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Only one absolute maximum rating may be applied at any one time.

<sup>2</sup>Overvoltages at EN, A0, A1, S, or D will be clamped by internal diodes. Current should be limited to the maximum ratings given.

#### **ORDERING GUIDE**

| Model Option | Temperature Range | Package Description               | Package |

|--------------|-------------------|-----------------------------------|---------|

| ADG604YRU    | –40°C to +125°C   | Thin Shrink Small Outline (TSSOP) | RU-14   |

#### PIN CONFIGURATION

#### Table I. Truth Table

| A1 | A0 | EN | ON Switch |

|----|----|----|-----------|

| X  | X  | 0  | None      |

| 0  | 0  | 1  | 1         |

| 0  | 1  | 1  | 2         |

| 1  | 0  | 1  | 3         |

| 1  | 1  | 1  | 4         |

|    |    |    |           |

#### CAUTION\_

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the ADG604 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high-energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

#### TERMINOLOGY

| V <sub>DD</sub>             | Most Positive Power Supply Potential                                                                                  |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------------|

| V <sub>SS</sub>             | Most Negative Power Supply in a Dual Supply Application. In single supply applications, this should be tied to        |

|                             | ground at the device.                                                                                                 |

| GND                         | Ground (0 V) Reference                                                                                                |

| I <sub>DD</sub>             | Positive Supply Current                                                                                               |

| I <sub>SS</sub>             | Negative Supply Current                                                                                               |

| S                           | Source Terminal. May be an input or output.                                                                           |

| D                           | Drain Terminal. May be an input or output.                                                                            |

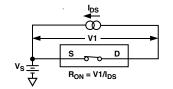

| R <sub>ON</sub>             | Ohmic Resistance between D and S                                                                                      |

| $\Delta R_{ON}$             | On Resistance Match between any two channels, i.e., R <sub>ON</sub> Max – R <sub>ON</sub> Min                         |

| R <sub>FLAT(ON)</sub>       | Flatness is defined as the difference between the maximum and minimum value of On resistance as measured              |

|                             | over the specified analog signal range.                                                                               |

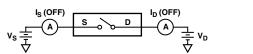

| I <sub>S</sub> (OFF)        | Source Leakage Current with the Switch "OFF"                                                                          |

| I <sub>D</sub> (OFF)        | Drain Leakage Current with the Switch "OFF"                                                                           |

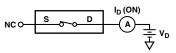

| $I_{\rm D}, I_{\rm S}$ (ON) | Channel Leakage Current with the Switch "ON"                                                                          |

| $V_D, V_S$                  | Analog Voltage on Terminals D, S                                                                                      |

| V <sub>INL</sub>            | Maximum Input Voltage for Logic "0"                                                                                   |

| V <sub>INH</sub>            | Minimum Input Voltage for Logic "1"                                                                                   |

| $I_{INL}$ ( $I_{INH}$ )     | Input Current of the Digital Input                                                                                    |

| C <sub>S</sub> (OFF)        | Channel Input Capacitance for "OFF" Condition                                                                         |

| C <sub>D</sub> (OFF)        | Channel Output Capacitance for "OFF" Condition                                                                        |

| $C_D, C_S (ON)$             | "On" Switch Capacitance                                                                                               |

| C <sub>IN</sub>             | Digital Input Capacitance                                                                                             |

| t <sub>ON</sub> (EN)        | Delay time between the 50% and 90% points of the digital input and switch "ON" condition.                             |

| t <sub>OFF</sub> (EN)       | Delay time between the 50% and 90% points of the digital input and switch "OFF" condition.                            |

| t <sub>TRANSITION</sub>     | Delay time between the 50% and 90% points of the digital input and switch "ON" condition when switching               |

|                             | from one address state to another.                                                                                    |

| t <sub>BBM</sub>            | "OFF" time or "ON" time measured between the 80% points of both switches, when switching from one addres              |

|                             | state to another.                                                                                                     |

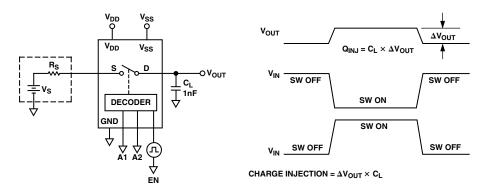

| Charge Injection            | A measure of the glitch impulse transferred from the digital input to the analog output during switching.             |

| Crosstalk                   | A measure of unwanted signal that is coupled through from one channel to another as a result of parasitic capacitance |

| Off Isolation               | A measure of unwanted signal coupling through an "On" switch.                                                         |

| Bandwidth                   | Frequency Response of the "On" Switch                                                                                 |

| Insertion Loss              | Loss Due to the On Resistance of the Switch                                                                           |

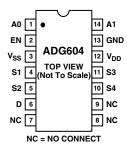

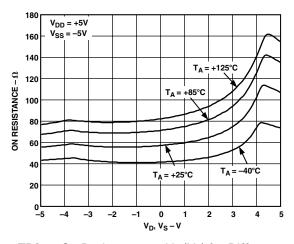

TPC 1. On Resistance vs. V<sub>D</sub> (V<sub>S</sub>), Dual Supply

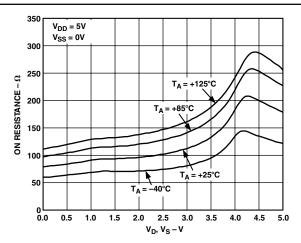

TPC 2. On Resistance vs.  $V_D$  ( $V_S$ ), Single Supply

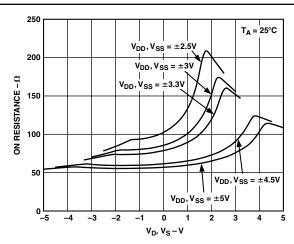

TPC 3. On Resistance vs.  $V_D$  ( $V_S$ ) for Different Temperatures, Dual Supply

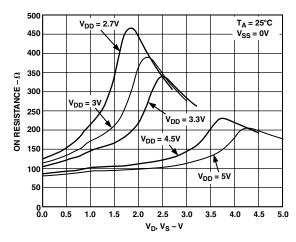

## **Typical Performance Characteristics-ADG604**

TPC 4. On Resistance vs.  $V_D$  ( $V_S$ ) for Different Temperatures, Single Supply

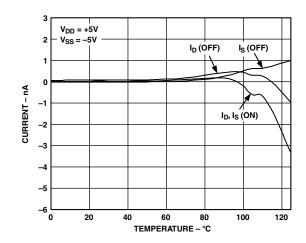

TPC 5. Leakage Currents vs. Temperature, Dual Supply

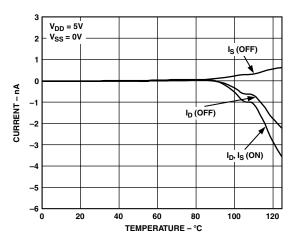

TPC 6. Leakage Currents vs. Temperature, Single Supply

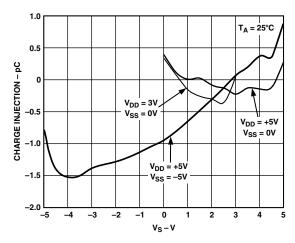

TPC 7. Charge Injection vs. Source Voltage

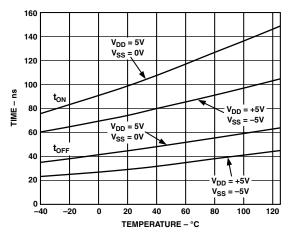

TPC 8. t<sub>ON</sub>/t<sub>OFF</sub> Times vs. Temperature

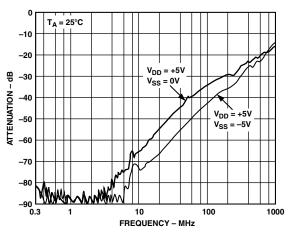

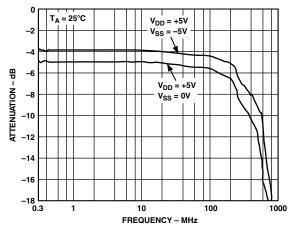

TPC 9. Off Isolation vs. Frequency

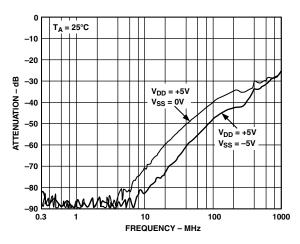

TPC 10. Crosstalk vs. Frequency

TPC 11. On Response vs. Frequency

# **Test Circuits**

Test Circuit 1. On Resistance

Test Circuit 3. On Leakage

Test Circuit 2. Off Leakage

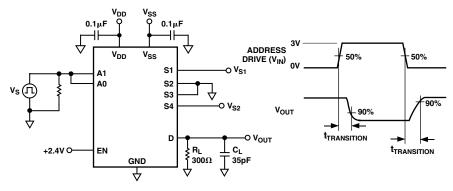

Test Circuit 4. Switching Time of Multiplexer, t<sub>TRANSITION</sub>

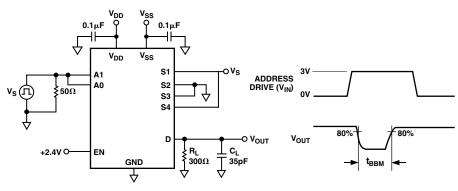

Test Circuit 5. Break-Before-Make Delay, t<sub>BBM</sub>

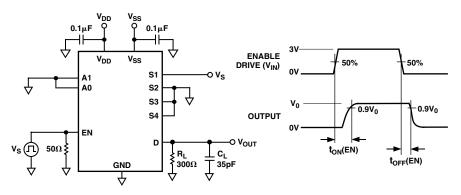

Test Circuit 6. Enable Delay, t<sub>ON</sub> (EN), t<sub>OFF</sub> (EN)

Test Circuit 7. Charge Injection

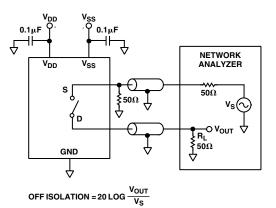

Test Circuit 8. Off Isolation

0.1μF 0.1μF NETWORK ANALYZER  $V_{DD}$ V<sub>SS</sub> <u>\$1</u>0 V<sub>OUT</sub> O 4 D 50Ω S2 50Ω GND v₅(∿ Ą CHANNEL-TO-CHANNEL CROSSTALK = 20 LOG  $\frac{V_{OUT}}{V_S}$

Test Circuit 10. Channel-to-Channel Crosstalk

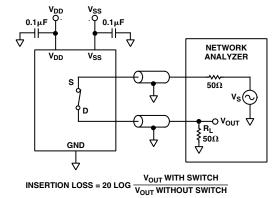

Test Circuit 9. Bandwidth

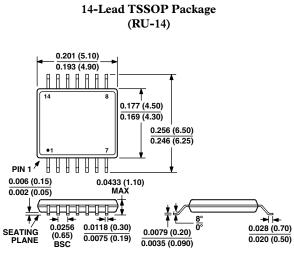

**OUTLINE DIMENSIONS** Dimensions shown in inches and (mm).

C02752-0-2/02(0)