### ADM 8511

Pegasus II

### **USB / Fast Ethernet with MII Interface**

### General Description

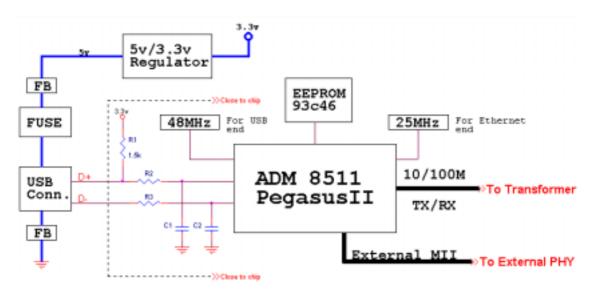

The ADM 8511, USB based chipset, provides desktop, notebook and computer peripherial with greater connectivity to ethernet and home network. In the meantime, the ADM 8511 also combined a low power and small package design which is ideal for power and space constrained environment. Then, it can reduced the external component BOM cost to a minimum.

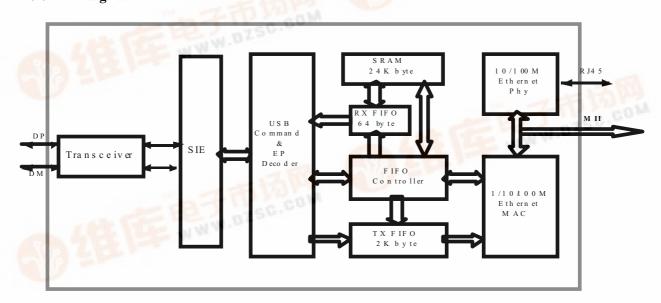

The ADM 8511 device combines a on-chip USB command & EP decoder used for USB interface through SIE (Series Interface Engine), FIFO controller with 24 K SRAM, 64 byte and 2K byte buffers, 10/100 Mbps ethernet physical layer (PHY) and 10M HomePNA interface 10M8. The 10M HomePNA interface is MII is the same as the ethernet MAC interface. The ADM8511 is fully compliant with the IEEE 802.3u

The ADM 8511 is capable of providing a easy, universal connectivity to computer peripherals with USB. The transfer rate of USB interface is 12 Mbps belonging to a high speed USB device. The ADM 8511 supports all USB commands, 4 endpoints and suspend/resume function.

The ADM 8511's LAN PHY supports 100 Base TX (100 Mbps mode) and 10 Base T (10Mbps mode) full-duplex operations. It uses the auto-negotiation function to optimize the network traffic and the built-in 24K bytes SRAM for receiving buffer, especially for 100Mbps. Through FIFO controller, data can communicate influ rently

between buffers and external device. To obtain the signal quality, the PHY wave-shaper, filter and adaptive equalizer to reach. By using diagnostic mechanism (loop-back mode), the data correctness will be increased. The Lan PHY external transmit/receive supports transformer turn ratio 1:1. The ADM8511 chipset can be programmed MAC analysis and provides MII interface for external PHY, such as 10M8 interface for 10Mbps HomePNA. In system application, EEPROM is essential that it needs to load device ID, vendor ID automatically. So for ADM 8511, serial interface is applied for EEPROM communication including read/write function. Furthermore, system statuses are reported by some LED pins.

ADM 8511 is ideally suited for USB adapter and intelligent networked peripheral design. By fiber media, ADM 8511 can associate with fiber tranceiver & PHY through MII interface to network in fiber network. In HomePAN application, ADM 8511 can provide 10M8 (MII interface) associated with external 10M Home PHY for 10Mbps network. ADM 8511 can't apply only in LAN( Local Area Network) but also in WAN( Wide Area Network), such as xDSL, Cable Modem, and router ... e.t.c.. In IA ( Information Appliance ) application, Set-Top box is an example of ADM 8511 application. ADM 8511 also provide serial interface for

### Block Diagram

### Pegasus II USB / Fast Ethernet with MII Interface

EEPROM storing default values, e.g. vendor ID, Product ID, ...e.t.c.(EEPROM Access Program). Specially, ADM 8511 can be tested by test program (MFG) in the less time for mass production of system board level. This chip provides 3.3V/5V I/Otolerance, and 100 pin LQFP package

In software, ADM 8511 provides a fully software support, NDIS 5 driver, Linux driver, WinCE 4.0, EEPROM burn-in program and MFG program. The NDIS 5 and Linux drivers are windows netware drivers. EEPROM burn-in program is convenient for customers to implement. The MFG program is a powerful tool in mass – production.

### ADM 8511

### **USB / Fast Ethernet with MII Interface**

### **Features**

Pegasus II

### • Industry Standard

- IEEE802.3u 100BASE-TX and IEEE802.3 10BASE-T compliant

- Support for IEEE 802.3x flow control

- IEEE802.3u Auto-Negotiation support for 10BASE-T and 100BASE-TX

- USB specification 1.0 and 1.1 compliant

#### • USB I/F

- Full-Speed USB Device

- Supports 1 USB configuration and 1 interface

- Supports all USB standard commands

- Supports two vendor specific commands

- Supports USB Suspend/Resume detection logic

- Supports 4 endpoints: 1 control endpoint with maximum 8-byte packet, 1 bulk IN endpoint with maximum 64-byte packet, 1 bulk OUT endpoint with maximum 64-byte packet and 1 interrupt IN endpoint with maximum 8-byte packet

### MAC/Phy

- Integrates the whole physical layer functions of 100BASE-TX and 10BASE-T by using phy address 1

- Be programmed to isolate the internal PHY, the I/F to external PHY could be either IEEE 802.3 MII (10M8 for HomePNA 2.0). Supports configurable threshold for transmitting PAUSE frame

- Supports wakeup frame, link status change and magic packet wake-up

- Provides full-duplex operation on both 100Mbps and 10Mbps Ethernet modes

- Provides Auto-negotiation(NWAY) function of full/half duplex operation for both 10/100 Mbps

- Provides transmit wave-shaper, receive filters, and adaptive equalizer

- Provides MLT-3 transceiver with DC restoration for Base-Line Wander compensation

- Provides MAC and Transceiver loop-back modes for diagnostic

- Supports external transmit transformer with turn ratio 1:1

- Supports external receive transformer with turn ratio 1:1

#### • EEPROM I/F

- Provides serial interface for read/write 93C46 EEPROM

- Automatically loads device ID, vendor ID from EEPROM after power-on reset

#### FIFO

- Supports internal 2K bytes SRAM for transmission

- Supports internal 24K bytes synchronous SRAM for receiving.

- Supports "receive 32 packets" or "receive 16 packets" queue in the receive buffer

### LED Display

• Provide LEDs many display mode

#### Miscellaneous

- Support 6 GPIO pins

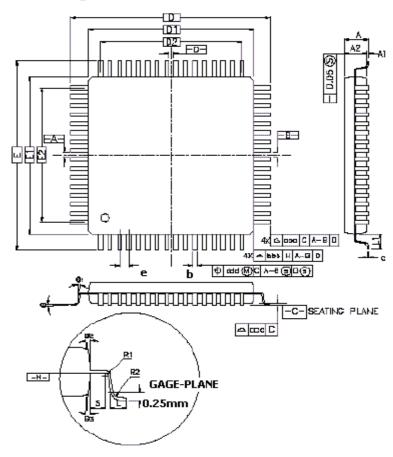

- Provides 100-pin LQFP package

- 3.3V power supply with 5V/3.3V I/O tolerance

### ADM 8511

Pegasus II USB / Fast Ethernet with MII Interface

• LAN Driver Support

• Windows Networks : NDIS 5.0

- Linux

- WinCE 4.0

- Utility

- EEPROM burn-in program

- MFG testing program

Pegasus II

### **Revision History**

| <b>Release Date</b> | Revision | Description                                                                                               |

|---------------------|----------|-----------------------------------------------------------------------------------------------------------|

| July<br>2000        | 0.1      | Draft product spec for review                                                                             |

| September<br>2000   | 1.0      | Rearrange                                                                                                 |

| October<br>2000     | 2.0      | add appendix                                                                                              |

| December<br>2000    | 2.01     | P.62 Appendix 5/item 7/item b/item ii/ TXER change to RXER                                                |

| December<br>2000    | 2.02     | Add max. power consumption                                                                                |

| 2000                |          | P.1 I <sup>2</sup> C change to serial                                                                     |

| April<br>2002       | 2.04     | Add Appendix 1 / item 3/ item (6)                                                                         |

| 2002                |          | No connection in external SRAM interface. They are pin 27,28,30,32~36,38,39,41,42,44~48,50,51,53~55,57~60 |

|                     |          | No connection in test pins. They are pin 5,9.                                                             |

|                     |          | Power consumption change at P.38                                                                          |

|                     |          | Add LED operation mode at P.11                                                                            |

|                     |          | Add EEPROM 0B[7:6] for LED mode setting at P.51                                                           |

|                     |          | Remove all of HomePNA(1M8) description                                                                    |

|                     |          | Remove all of external SRAM interface description                                                         |

|                     |          | Remove Phy transceiver reg. After reg. 6                                                                  |

|                     |          | Modify Phy transceiver reg. 0~6 description                                                               |

|                     |          | Modify EEPROM content in EEPROM example                                                                   |

|                     |          | Add "25MHz crystal and Ribb still need" in Appendix 5                                                     |

### ADM 8511

### Pegasus II

### **USB / Fast Ethernet with MII Interface**

| General Desc      | cription                                                      | 1  |  |  |  |  |  |

|-------------------|---------------------------------------------------------------|----|--|--|--|--|--|

| Block Diagra      | nm                                                            | 1  |  |  |  |  |  |

| Features          |                                                               | 3  |  |  |  |  |  |

| <b>LAN Driver</b> | Support                                                       | 4  |  |  |  |  |  |

| Utility           |                                                               | 4  |  |  |  |  |  |

| Pin Assignm       | ent Diagram                                                   | 7  |  |  |  |  |  |

| Pin Descript      | ions                                                          | 8  |  |  |  |  |  |

| Functional D      | escriptions                                                   | 14 |  |  |  |  |  |

| USB Int           | erface                                                        | 14 |  |  |  |  |  |

| MAC In            | terface                                                       | 14 |  |  |  |  |  |

| FIFO C            | ontroller                                                     | 16 |  |  |  |  |  |

| TX FIF            | O and RX FIFO                                                 | 17 |  |  |  |  |  |

| 1/10/100          | 1/10/100 Ethernet MAC 17                                      |    |  |  |  |  |  |

| 10/100N           | 10/100M Ethernet PHY 17                                       |    |  |  |  |  |  |

| Register Des      | criptions                                                     | 18 |  |  |  |  |  |

| System            | register set                                                  | 18 |  |  |  |  |  |

| Transce           | iver register set                                             | 28 |  |  |  |  |  |

| Electrical Sp     | ecifications and Timings                                      | 28 |  |  |  |  |  |

| Package           |                                                               | 40 |  |  |  |  |  |

| Appendix 1        | Layout Guide                                                  | 42 |  |  |  |  |  |

| Appendix 2        | EEPROM Interface & Example                                    | 46 |  |  |  |  |  |

| Appendix 3        | USB Device Operation                                          | 49 |  |  |  |  |  |

| Appendix 4        | USB Command                                                   | 51 |  |  |  |  |  |

| Appendix 5        | ppendix 5 Application Notes for Ethernet & MII Application 57 |    |  |  |  |  |  |

Pegasus II

**USB / Fast Ethernet with MII Interface**

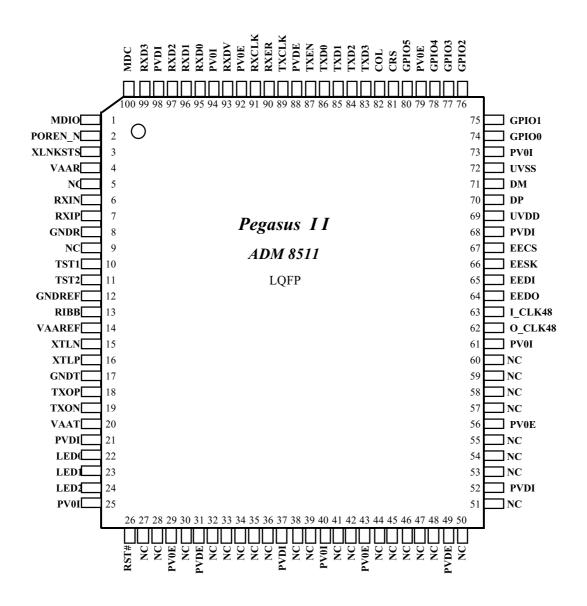

### Pin Assignment Diagram

### Pegasus II

### **USB / Fast Ethernet with MII Interface**

### • Pin Description

|   | Pin Name              | Pin# | Type | Pin Description                               |

|---|-----------------------|------|------|-----------------------------------------------|

| • | <b>Host Interface</b> |      |      |                                               |

|   | I_CLK48               | 63   | I    | 48Mhz Clock Input from crystal or oscillator. |

|   | O_CLK48               | 62   | О    | Output for crystal.                           |

|   | RST#                  | 26   | I    | External Hardware Reset Input                 |

|   | DM                    | 71   | I/O  | USB Data Minus pin.                           |

|   | DP                    | 70   | I/O  | USB Data Plus pin.                            |

### MII Interface (Program ADM8511 as MAC-only mode, set 81h[4:2]=001b and 01h bit 2 = 0)

|     |     | <b>Collision Detected</b>                                                                                                                                                                            |

|-----|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 82  | I   | This signal is asserted high asynchronously by<br>the external physical unit upon detection of a<br>collision on the medium. It will remain asserted<br>as long as the collision condition persists. |

|     |     | Carrier Sense                                                                                                                                                                                        |

| 81  | I   | This signal is asserted high asynchronously by<br>the external physical unit upon detection of a<br>non-idle medium.                                                                                 |

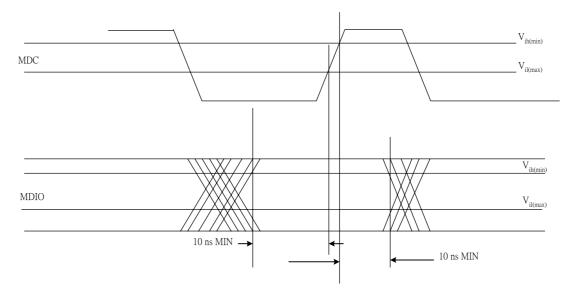

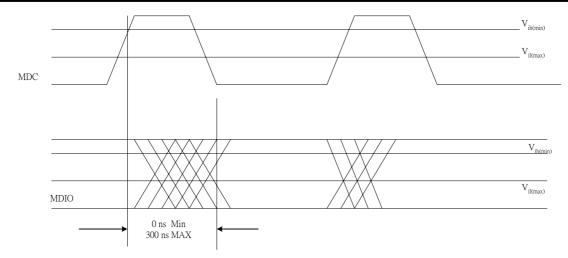

|     |     | Management Data Clock                                                                                                                                                                                |

| 100 | О   | Clock signal with a maximum rate of 2.5MHz used to transfer management data for the external PMD on the MDIO pin.                                                                                    |

|     |     | Management Data I/O                                                                                                                                                                                  |

| 1   | I/O | Bi-directional signal used to transfer management information for the external PMD. Requires external 1.5k pull-up resistor.                                                                         |

|     |     | Receive Clock                                                                                                                                                                                        |

| 91  | I   | A continuous clock that is recovered from the incoming data. During 100Mb/s operation RXCLK is 25MHz, during 10Mb/s this is 2.5MHz and during 1Mb/s operation this is 0.25MHz.                       |

|     | 100 | 81 I 100 O 1 I/O                                                                                                                                                                                     |

### ADM 8511

### Pegasus II

### **USB / Fast Ethernet with MII Interface**

|          |                 |   | Receive Data                                                                                                                                                                                                                                                                                                                       |

|----------|-----------------|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RXD[3:0] | 95-97,<br>99    | I | This is a group of 4 data signals aligned on nibble boundary which are driven synchronou to the RXCLK by the external physical unit. RXD[3] is the most significant bit and RXD[0 is the least significant bit.                                                                                                                    |

|          |                 |   | Receive Data Valid                                                                                                                                                                                                                                                                                                                 |

| RXDV     | 93              | I | This indicates that the external physical unit is presenting recovered and decoded nibbles on the RXD[3:0] and that RXCLK is synchronout to the recovered data.                                                                                                                                                                    |

|          |                 |   | Receive Error                                                                                                                                                                                                                                                                                                                      |

| RXER     | 90              | I | This signal is asserted high synchronously by the external physical unit whenever it detects media error and RXDV is asserted.  If no used, it should be grounded, e.g. isolate internal phy and use external phy. However, it the external phy has RXER pin, the RXER of ADM8511 should connect to this RXER of the external phy. |

|          |                 |   | Transmit Clock                                                                                                                                                                                                                                                                                                                     |

| TXCLK    | 89              | I | A continuous clock that is source by the physical layer. During 100 Mb/s operation this is 25MHz ±100 ppm. During 10 Mb/s operation this clock is 2.5MHz ±100 ppm. During 1 Mb/s operation this clock is 0.25MHz ±100 ppm.                                                                                                         |

|          |                 |   | Transmit Data                                                                                                                                                                                                                                                                                                                      |

| TXD[3:0] | 83,84,<br>85,86 | О | This is a group of 4 data signals which driven synchronously to the TXCLK for transmission to the external physical unit. TXD[3] is the most significant bit and TXD[0] is the least significant bit.                                                                                                                              |

|          |                 |   | Transmit Enable                                                                                                                                                                                                                                                                                                                    |

| TXEN     | 87              | O | This signal is synchronous to TXCLK and provides precise framing for data carried on TXD[3:0]. It is asserted when TX[3:0] contain valid data to be transmitted. Require external pull-down resistor 4.7K if external phy is used                                                                                                  |

### ADM 8511

Pegasus II

### **USB / Fast Ethernet with MII Interface**

|                 |          |   | Link Status Indication                                                                                                                            |

|-----------------|----------|---|---------------------------------------------------------------------------------------------------------------------------------------------------|

| XLNKSTS         | 3        | I | Link status indication External PHY reports link status information to system and level change trigger. Pull-down to low if external phy is used. |

| Physical Inter- | face     |   |                                                                                                                                                   |

| XTLP, XTLN      | 16, 15   | I | Crystal inputs. To be connected to a 25MHz crystal.                                                                                               |

| RXIN, RXIP      | 6, 7     | I | The differential receive inputs of 100BASE-TX or 10BASE-T, these pins directly input from Magnetic.                                               |

| TXOP, TXON      | 18, 19   | О | The differential Transmit outputs of 100BASE-TX or 10BASE-T, these pins directly output to Magnetic.                                              |

| RIBB            | 13       | I | Reference Bias Resistor. To be tied to an external 10.0K (1%) resistor which should be connected to the analog ground at the other end.           |

| TST1, TST2      | 10, 11   | О | Test pin                                                                                                                                          |

| • LED display   | <b>.</b> |   |                                                                                                                                                   |

| LED0            | 22       | О | LED display for 100M b/s or 10M b/s speed.<br>Active low indicates 100Base-TX, active high indicates 10 BaseT.<br>2mA @5V                         |

| LED1            | 23       | 0 | LED display for link and activity status. Active low when link is established. 2mA @5V                                                            |

| LED2            | 24       | О | LED display for Full Duplex or Collision status. Active low indicates full duplex, high indicates collision in half duplex.  2mA @5V              |

Pegasus II

### **USB / Fast Ethernet with MII Interface**

#### Note

The LED interface is EEPROM-programmable, 2 bit EEPROM control bit, Address 0B[7:6] at EEPROM, is used to select LED mode, the default setting are:

- (1) LED0: 100Mbps(on, drive '0') or 10Mbps(off, drive '1')

- (2) LED1: link (keeps on when link ok) or activity (blink with 10Hz when Pegasus II is receiving or transmitting but not collision)

- (3) LED2: full duplex (keeps on when in full duplex mode) or collision (blink with 20Hz when colliding)

- (4) All LED pins will be tri-state when using external PHY (offset 81h with bit[4:2] = 3'b001)

Mapping between LED action and EEPROM 0B[7:6] setting:

| EEPROM 0B | LED  | Action                              |

|-----------|------|-------------------------------------|

| [7:6]     |      |                                     |

|           | LED0 | 10/100(OFF/ON)                      |

| 0,0       | LED1 | LINK/ACTIVITY (ON / Flash)          |

|           | LED2 | FULL DUP/COL (ON / Flash)           |

|           | LED0 | ACTIVITY when LINK (Flash)          |

| 0,1       | LED1 | LINK 10(ON)                         |

|           | LED2 | LINK 100(ON                         |

|           | LED0 | On: 100M, Off:10M                   |

| 1,0       | LED1 | Flash: Activity                     |

|           | LED2 | Flash : Liink                       |

|           | LED0 | On: 10M Link, Flash: 10M Activity   |

| 1,1       | LED1 | On: 100M Link, Flash: 100M Activity |

|           | LED2 | Full                                |

### No connection

|      | 48, 50, | No connection |

|------|---------|---------------|

|      | 51, 53, |               |

|      | 54, 55, |               |

| NC   | 57, 58, |               |

| INC  | 30, 32, |               |

|      | 35, 33, |               |

|      | 59, 28, |               |

|      | 60      |               |

|      | 47, 46, | No connection |

| NC   | 45, 44, |               |

| INC. | 42, 41, |               |

|      | 39, 38  |               |

ADMtek Incorporated 2F, No2, Li-Hsin Road Science-Based Industrial Park 300 Hsinchu, Taiwan, R.O.C. Tel:886-3-5788879 Fax: 886-3-5788871 ADMtek Incorporated Confidential http://www.admtek.com.tw

Version: 2.04

11

### ADM 8511

### Pegasus II USB / Fast Ethernet with MII Interface

| NC                                | 36                           |     | No connection                                                                                                                                                                 |

|-----------------------------------|------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NC                                | 34                           |     | No connection                                                                                                                                                                 |

|                                   |                              |     |                                                                                                                                                                               |

| NC                                | 27                           |     | No connection                                                                                                                                                                 |

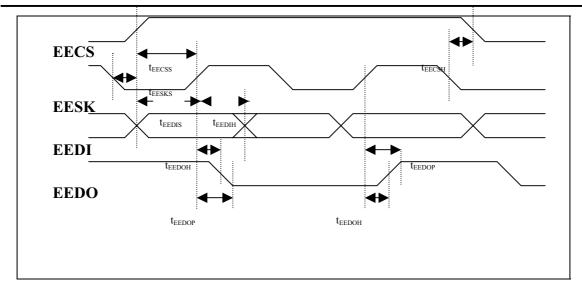

| • EEPROM Inte                     | erface                       |     |                                                                                                                                                                               |

|                                   |                              |     | EEPROM Chip Select                                                                                                                                                            |

| EECS                              | 67                           | О   | This enables the EEPROM during loading of the Ethernet configuration data.                                                                                                    |

|                                   |                              |     | EEPROM Data In                                                                                                                                                                |

| EEDI                              | 65                           | О   | The MAC will use this pin to serially write opcodes, addresses and data into the serial EEPROM.                                                                               |

|                                   |                              |     | EEPROM Data Out                                                                                                                                                               |

| EEDO                              | 64                           | I   | The MAC will read the contents of the EEPROM serially through this pin.                                                                                                       |

| EESK                              | 66                           | О   | EEPROM Clock                                                                                                                                                                  |

|                                   |                              |     | After reset, the MAC if configured, will read the contents of the EEPROM using EESK, EEDO, and EEDI. This pin provides the clock for the EEPROM.                              |

| <ul> <li>Miscellaneous</li> </ul> |                              |     |                                                                                                                                                                               |

| GPIO[5:0]                         | 80, 78,<br>77, 76,<br>75, 74 | I/O | These pins are used as general purpose Input/Output pins and offset $0A[1] = 0$ in EEPROM.  Default is internal pull-low $4mA@5V$                                             |

| POREN_N                           | 2                            | I   | Internal Power On Reset Logic Enable. Default is enable and internal pull - low. When external hardware reset is used, this pin should be connected to Vcc via 4.7k resistor. |

| • Power Pins                      |                              |     |                                                                                                                                                                               |

| PVDI                              | 21, 37,<br>52, 68,<br>98     | P   | 3.3v power supply for core.                                                                                                                                                   |

| PVDE                              | 31, 49,<br>88                | P   | 3.3v power supply for pads.                                                                                                                                                   |

### ADM 8511

### Pegasus II USB / Fast Ethernet with MII Interface

|               | 25, 40, |   | Ground for PVDI                       |

|---------------|---------|---|---------------------------------------|

| PV0I          | 61, 73, | P |                                       |

|               | 94      |   |                                       |

|               | 29, 43, |   | Ground for PVDE                       |

| PV0E          | 56, 79, | P |                                       |

|               | 92      |   |                                       |

| UVDD          | 69      | P | 3.3v power supply for USB transceiver |

| UVSS          | 72      | P | Ground for UVDD                       |

| VAAR, VAAREF, | 4, 14,  | P | Analog Power Pins, 3.3v               |

| VAAT          | 20      | r |                                       |

| GNDR, GNDREF, | 8, 12,  | Р | Analog Ground Pins                    |

| GNDT          | 17      | r |                                       |

Pegasus II

**USB / Fast Ethernet with MII Interface**

### **Function Descriptions**

### • USB Interface

USB is likely solution any time you want to use a computer to communication with devices outside the computer. The interface is suitable for one-of-kind and small-scale designs as well as mass-produced, standard peripheral. The benefits to USB are ease of use, fast and reliable data transfers, flexibility, low cost and power conservation. **SIE**

SIE (Serial Interface Engine) is to control USB communications and check USB protocol, then transfer protocol to EP decoder. The SIE and USB transceivers, which provide the hardware interface to the USB cable, together comprise the USB engine.

#### **USB Command & EP Decoder**

The detail description is in Appendix 4.

#### • MAC Interface

#### MII

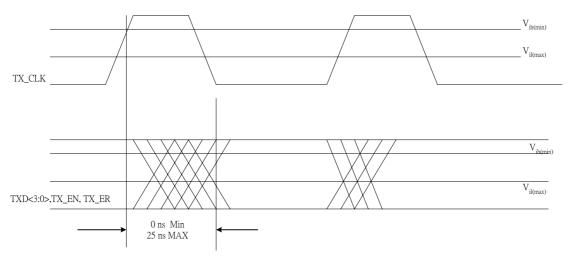

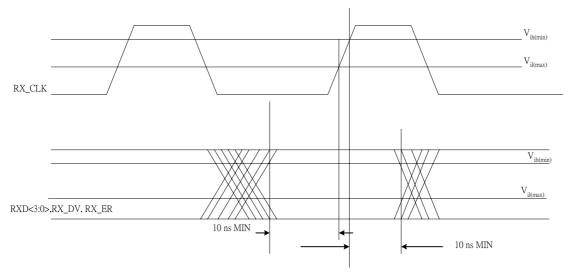

The Media Independent Interface (MII) is an 18 wire MAC/Phy interface described in 802.3u. The purpose of the interface is to allow MAC layer devices to attach to a variety of Physical Layer devices through a common interface. MII operates at either 100Mbps or 10Mbps, dependant on the speed of the Physical Layer. With clocks running at either 25 MHz or 2.5 MHz, 4 bit data is clocked between the MAC and Phy, synchronous with Enable and Error signals.

On receipt of valid data from the wire interface, RX\_DV will go active signaling to the MAC that the valid data will be presented on the RXD[3:0] pins at the speed of the RX CLK.

On transmission of data from the MAC, TX\_EN is presented to the phy indicating the presence of valid data on TXD[3:0]. TXD[3:0] are sampled by the phy synchronous to TX\_CLK during the time that TX\_EN is valid.

### **Adaptive Equalizer**

The amplitude and phase distortion from cable cause inter-symbol interference (ISI) which makes clock and data recovery difficult. The adaptive equalizer is designed to closely match the inverse transfer function of the twisted-pairs cable. The equalizer has the ability to change its equalizer frequency response according to the cable length. The

Pegasus II USB / Fast Ethernet with MII Interface

equalizer will tune itself automatically fo any cable, compensating for the amplitude and phase distortion introduced by the cable.

#### **LEDs**

Individual LED output are available to indicate Speed, Duplex, Collision, Transmit, and Link. These multi-function pins are inputs during reset and LED output pins thereafter. The level of these pins during reset determines their active output states. If a multi-function pin is pulled up during reset to select a particular function, then that LED output would become active low, and the LED circuit must be designed accordingly, and vice versa.

### Jabber and SQE

After the MAC transmitter exceeds the jabber timer, the transmit and loopback functions will be disable and COL signal get asserted. After TX\_EN goes low for more than 500ms, the TP transmitter will reactivate and COL gets de-asserted. Setting Jabber Disable will disable the jabber function.

When the SQE test is enabled, a COL pulse is asserted after each transmitted packet. SQE is enabled in 10Base-T by default.

### **Auto Polarity**

Certain cable plants have crossed wiring on the twisted pairs; the reversal of TXIN and TXIP. Under normal circumstances this would cause the receive circuitry to reject all data. When the Auto Polarity Disable bit is cleared, the Phy has the ability to detect the fact that either 8 NLPs (normal link pulse) or a burst of FLPs are inverted and automatically reverse the receiver's polarity. The polarity state is store is atoreed in the Reverse Polarity bit.

### **Auto-Negotiation**

It provides a linked device with the capability to detect the abilities (modes of operation) supported by the device at the other end of the link, determine common abilities, and configure for joint operation. Auto-Negotiation is performed out-of-band using a pulse code sequence that is compatible with the 10BASE-T link integrity test sequence.

### Pegasus II

**USB / Fast Ethernet with MII Interface**

### **Baseline Wander Compensation**

The 100BASE-TX data stream is not always DC balanced. The transformer blocks the DC components of the incoming signal, thus the DC offset of the differential receive inputs can drift. The shifting of the signal level, coupled with non-zero rise and fall times of the serial stream can cause pulse-width distortion. This creates jitter and possible increase in the bit error rates. Therefore, a DC restoration circuit is needed to compensate for the attenuation of the DC component. Unlike the traditional implementation, the circuit does not need the feedback information from the slicer or the clock recovery circuit. The design simplifies the circuit design. In 10BASE-T, the baseline wander correction circuit is not required.

#### • FIFO Controller

FIFO Controller in receive path is in charge of:

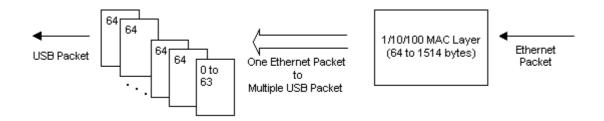

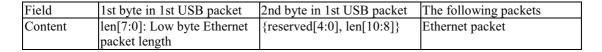

- (1) Store received Ethernet packets to SRAM (internal 24Kbyte) and total 32 (or 16) packets can be stored to SRAM. If more than maximum packet counts are received or total packet size is more than 32K (or 24K for internal SRAM) bytes, the subsequent coming Ethernet packet will be discarded.

- (2) FIFO controller will load data from SRAM to internal RX FIFO then inform EP Decoder that 64-byte data or a packet is ready in RX FIFO. Before FIFO controller inform this, any USB access to bulk IN endpoint will return NAK. This is to maintain the data transfer on USB bus via bulk IN transfer is continuous, thus a 64-byte internal RX FIFO is needed.

- (3) If an Ethernet packet is being received and loading into SRAM while FIFO Controller is moving data from SRAM to internal RX FIFO, writing the Ethernet packet to SRAM will get the higher priority.

FIFO Controller in transmit path is in charge of:

- (1) Store each individual USB packet to internal TX FIFO. When EP decoder informs end of packet, a complete Ethernet packet is stored in TX FIFO. FIFO Controller then informs MAC to transmit this packet.

- (2) Total 4 Ethernet packets can be stored in TX FIFO. If all 4 Ethernet packet are stored in TX FIFO or total packet size is more than 2K bytes, FIFO Controller will inform EP Decoder that TX FIFO is full and EP Decoder will return NAK if accessing to bulk OUT endpoint is invoked. Thus additional USB packet won't be written into TX FIFO until TX FIFO has free space.

### Pegasus II

### **USB / Fast Ethernet with MII Interface**

#### TX FIFO and RX FIFO

RX FIFO is a one-port 64-byte FIFO and TX FIFO is a two-port 2K-byte FIFO.

#### • 1/10/100 Ethernet MAC

The MAC controller takes in charge of

- (1) Generate CRC then transmit Ethernet packet.

- (2) Check CRC for received packet CRC, filter the received packets.

- (3) Polling PHY status.

- (4) Magic packet detection.

- (5) Automatically transmit PAUSE frame when received status meets the flow control criteria.

- (6) Late collision transmit packets will be discarded.

#### • 10/100M Ethernet PHY

The internal Ethernet PHY is compliant to IEEE 802.3u 100BASE-TX and IEEE802.3 10BASE-T. It provides the whole physical layer functions for both 10M and 100M Ethernet speed. The internal PHY can be isolated by programming register offset 7Bh, bit 1.

### ADM 8511

### Pegasus II USB / Fast Ethernet with MII Interface

### • Register Descriptions

• System Register Table

| System Register | 14.71                                             |

|-----------------|---------------------------------------------------|

| Offset          | Register                                          |

| 00-02h          | Ethernet control registers                        |

| 03-07h          | Reserved                                          |

| 08-0Fh          | Multicast address table registers                 |

| 10-15h          | Ethernet ID registers                             |

| 16-17h          | Reserved                                          |

| 18-19h          | Pause_timer registers                             |

| 1Ah             | Receive packet number based flow control register |

| 1Bh             | Occupied receive FIFO based flow control register |

| 1Ch             | EP1 control register                              |

| 1Dh             | RX FIFO control register                          |

| 1Eh             | BIST control register                             |

| 1Fh             | Reserved                                          |

| 20h             | EEPROM offset register                            |

| 21-22h          | EEPROM data registers                             |

| 23h             | EEPROM access control register                    |

| 24h             | Reserved                                          |

| 25h             | PHY address register                              |

| 26-27h          | PHY data registers                                |

| 28h             | PHY access control register                       |

| 29h             | Reserved                                          |

| 2Ah             | USB status register                               |

| 2B-2Ch          | Ethernet transmit status registers                |

| 2Dh             | Ethernet receive status register                  |

| 2E-2Fh          | Ethernet receive lost packet count register       |

| 30-3Fh          | Wakeup frame 0 mask registers                     |

| 40h             | Wakeup frame0 offset register                     |

| 41-42h          | Wakeup frame0 CRC registers                       |

| 43-47h          | Reserved                                          |

| 48-57h          | Wakeup frame 1 mask registers                     |

| 58h             | Wakeup frame 1 offset register                    |

| 59-5Ah          | Wakeup frame 1 CRC registers                      |

| 5B-5Fh          | Reserved                                          |

| 60-6Fh          | Wakeup frame 2 mask registers                     |

| 70h             | Wakeup frame 2 offset register                    |

| 71-72h          | Wakeup frame 2 CRC registers                      |

| 73-77h          | Reserved                                          |

| 78h             | Wakeup control register                           |

| 79h             | Reserved                                          |

| 7Ah             | Wakeup status register                            |

| 7Bh             | Internal PHY control register                     |

| 7Ch             | GPIO[5:4] control register                        |

| 7Dh             | Reserved                                          |

| 7Eh             | GPIO[1:0] control register                        |

| 7Fh             | GPIO[3:2] control register                        |

| 80h             | TEST register                                     |

| 81h             | Test mode register                                |

| 82-FFh          | Reserved                                          |

### ADM 8511

### Pegasus II

### **USB / Fast Ethernet with MII Interface**

### • Offset 00h: Ethernet control\_0

| Bit | Field            | HW     | SW     | Default | Description                                                     |

|-----|------------------|--------|--------|---------|-----------------------------------------------------------------|

|     |                  | Access | access | value   |                                                                 |

| 7   | tx_en            | R      | R/W    | 0       | Enable Ethernet transmission.                                   |

| 6   | rx_en            | R      | R/W    | 0       | Enable Ethernet receive.                                        |

| 5   | rx_flowctl_en    | R      | R/W    | 0       | Enable receive pause frame.                                     |

| 4   | wakeon_en        | R      | R/W    | 0       | Enable wake-on-LAN mode.                                        |

| 3   | rxstatus_append  | R      | R/W    | 1       | Enable status append at the end of received packet.             |

| 2   | stop_back_off    | R      | R/W    | 0       | 1: back-off counter stop when carrier is active and resume when |

|     |                  |        |        |         | carrier drop.                                                   |

|     |                  |        |        |         | 0: back-off counter isn't affected by carrier.                  |

| 1   | rx_multicast_all | R      | R/W    | 0       | Receive all multicast packet                                    |

| 0   | rx crc sent      | R      | R/W    | 1       | Include CRC in receive packet.                                  |

### • Offset 01h: Ethernet control\_1

| Bit | Field        | HW     | SW     | Default | Description                                                       |

|-----|--------------|--------|--------|---------|-------------------------------------------------------------------|

|     |              | access | access | value   |                                                                   |

| 7   | reserved     |        |        |         |                                                                   |

| 6   | Reserved     |        |        | 0       |                                                                   |

| 5   | full_duplex  | R      | R/W    | 0       | 1: full-duplex mode.                                              |

|     |              |        |        |         | 0: half-duplex mode.                                              |

| 4   | 10mode       | R      | R/W    | 0       | 0: 10Base-T mode.                                                 |

|     |              |        |        |         | 1: 100Base-T mode.                                                |

| 3   | reset_mac    | R      | R/W    | 0       | Reset MAC, After write 1, HW will clear this bit after MAC reset. |

| 2   | homelan_mode | R      | R/W    | 0       | 0: MII I/F to external PHY                                        |

| 0-1 | reserved     |        |        |         |                                                                   |

### • Offset 02h: Ethernet control\_2

| Bit | Field          | HW     | SW     | Default | Description                                                    |

|-----|----------------|--------|--------|---------|----------------------------------------------------------------|

|     |                | access | access | value   |                                                                |

| 7-6 | reserved       |        |        |         |                                                                |

| 5   | load EEPROM    | R      | R/W    | 0       | When this bit is written with 1, HW will start to load EEPROM. |

|     | start          |        |        |         |                                                                |

| 4   | EEPROM write   | R      | R/W    | 0       | 1: EEPROM write command                                        |

|     | enable/disable |        |        |         | 0: EEPROM write enable/disable command                         |

| 3   | loop_back      | R      | R/W    | 0       | Enable MAC loop back mode                                      |

| 2   | promiscuous    | R      | R/W    | 0       | 1: receive any packet.                                         |

|     |                |        |        |         | 0: receive packets which pass the address filter.              |

| 1   | rx_bad_pkt     | R      | R/W    | 0       | 1: receive bad packets which pass the address filter.          |

|     |                |        |        |         | 0: filter all bad packet                                       |

| 0   | Ep3_rd_clr/    | R      | R/W    | 0       | 1: Once EP3 is accessed, those registers(2B-2F, 7A) will be    |

|     |                |        |        |         | cleared.                                                       |

|     |                |        |        |         | 0: Access EP3, no effect to those registers.                   |

19

### Pegasus II

### **USB / Fast Ethernet with MII Interface**

• Offset 03-07h: reserved

### • Multicast address

| offset | Bit | Field      | HW     | SW     | Default | Description                                   |

|--------|-----|------------|--------|--------|---------|-----------------------------------------------|

|        |     |            | access | access | value   |                                               |

| 08h    | 7-0 | Multicast0 | R      | R/W    | 0       | Multicast address byte 0 (hash table[7:0]).   |

| 09h    | 7-0 | Multicast1 | R      | R/W    | 0       | Multicast address byte 1 (hash table[15:8]).  |

| 0Ah    | 7-0 | Multicast2 | R      | R/W    | 0       | Multicast address byte 2 (hash table[23:16]). |

| 0Bh    | 7-0 | Multicast3 | R      | R/W    | 0       | Multicast address byte 3 (hash table[31:24]). |

| 0Ch    | 7-0 | Multicast4 | R      | R/W    | 0       | Multicast address byte 4 (hash table[39:32]). |

| 0Dh    | 7-0 | Multicast5 | R      | R/W    | 0       | Multicast address byte 5 (hash table[47:40]). |

| 0Eh    | 7-0 | Multicast6 | R      | R/W    | 0       | Multicast address byte 6 (hash table[55:48]). |

| 0Fh    | 7-0 | Multicast7 | R      | R/W    | 0       | Multicast address byte 7 (hash table[63:56]). |

### • Ethernet ID

| Offset | Bit | Field    | HW     | SW     | Default | Description                                  |

|--------|-----|----------|--------|--------|---------|----------------------------------------------|

|        |     |          | access | access | value   |                                              |

| 10h    | 7-0 | Etherid0 | R/W    | R/W    | 0       | The 1st byte of ethernet ID is automatically |

|        |     |          |        |        |         | loaded from EEPROM after HW reset.           |

| 11h    | 7-0 | Etherid1 | R/W    | R/W    | 0       | The 2nd byte of ethernet ID.                 |

| 12h    | 7-0 | Etherid2 | R/W    | R/W    | 0       | The 3rd byte of ethernet ID.                 |

| 13h    | 7-0 | Etherid3 | R/W    | R/W    | 0       | The 4th byte of ethernet ID.                 |

| 14h    | 7-0 | Etherid4 | R/W    | R/W    | 0       | The 5th byte of ethernet ID.                 |

| 15h    | 7-0 | Etherid5 | R/W    | R/W    | 0       | The 6th byte of ethernet ID.                 |

• Offset 16-17h: reserved

• Offset 18h: pause\_timer low

| Bit | Field       | HW     | SW     | Default | Description                                  |

|-----|-------------|--------|--------|---------|----------------------------------------------|

|     |             | access | access | value   |                                              |

| 7-0 | pause_timer | R      | R/W    | 0F      | The [11:4] of pause time in the PAUSE frame. |

• Offset 19h: reserved

### • Offset 1Ah: receive packet number based flow control

| Bit | Field       | HW     | SW     | Default | Description                                                     |

|-----|-------------|--------|--------|---------|-----------------------------------------------------------------|

|     |             | access | access | value   |                                                                 |

| 7   | reserved    |        |        |         |                                                                 |

| 6-1 | pkt_no      | R      | R/W    | 6'h0F   | This field specifies the threshold for transmitting the PAUSE   |

|     |             |        |        |         | frame. As the received packet number is more than or equal to   |

|     |             |        |        |         | this field, the PAUSE frame is sent automatically by HW.        |

| 0   | flowctl_pkt | R      | R/W    | 0       | Enable pause frame transmission bases on receive packet number. |

ADMtek Incorporated 2F, No2, Li-Hsin Road Science-Based Industrial Park 300 Hsinchu, Taiwan, R.O.C. Tel:886-3-5788879 Fax: 886-3-5788871 ADMtek Incorporated Confidential http://www.admtek.com.tw

Version: 2.04

20

### Pegasus II

### **USB / Fast Ethernet with MII Interface**

### • Offset 1Bh: occupied receive FIFO based flow control

| Bit | Field          | HW<br>access | SW access | Default<br>value | Description                                                                                                                                                                                                                                                                                         |

|-----|----------------|--------------|-----------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | reserved       |              |           |                  |                                                                                                                                                                                                                                                                                                     |

| 6-1 | rxsize         | R            | R/W       |                  | This field specifies the K byte threshold for transmitting the PAUSE frame. As the received FIFO is occupied than or equal to this field, the PAUSE frame is sent automatically by HW. If this field =2, as receive FIFO is occupied more than or equal to 2K byte, the PAUSE frame is transmitted. |

| 0   | flowctl_rxsize | R            | R/W       | 0                | Enable pause frame transmission bases on occupied receive FIFO size.                                                                                                                                                                                                                                |

### • Offset 1Ch: EP1 Control

| Bit | Field        | HW     | SW     | Default | Description                                                  |

|-----|--------------|--------|--------|---------|--------------------------------------------------------------|

|     |              | access | access | value   |                                                              |

| 7   | ep1_send0_en | R      | R/W    | 0       | 1: enable EP1 send 1-byte 00 when more than frame_interval's |

|     |              |        |        |         | NAK is received                                              |

|     |              |        |        |         | 0: disable EP1 send 1-byte 00 function                       |

| 6-5 | test_itvl_a  | R      | R/W    | 2'd0    | This value are used for internal test mode.                  |

| 4-0 | test itvl b  | R      | R/W    | 5'd0    | This value are used for internal test mode.                  |

### • Offset 1Dh: RX FIFO Control

| Bit | Field    | HW     | SW     | Default | Description                                   |

|-----|----------|--------|--------|---------|-----------------------------------------------|

|     |          | Access | access | value   |                                               |

| 7-2 | reserved |        |        |         |                                               |

| 1   | reserved |        |        | 0       | 0: supports internal 24K-byte SRAM            |

| 0   | rx32pkt  | R      | R/W    | 0       | 1: support maximum 32 packets in receive FIFO |

|     |          |        |        |         | 0: support maximum 16 packets in receive FIFO |

### • Offset 1Eh: BIST control

| Bit | Field          | HW     | SW     | Default | Description                                                                                                                                                              |

|-----|----------------|--------|--------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |                | Access | access | value   |                                                                                                                                                                          |

| 7-3 | reserved       |        |        |         |                                                                                                                                                                          |

| 2   | bist_result    | R/W    | R      | 0       | This bit indicated the bist result and is valid when "bist_test_done" is '1'. This bit also reflects the value of "pass_or_fail" signal in BIST module.  1: pass 0: fail |

| 1   | bist_test_done | R/W    | R      | 0       | This bit indicates the completion of bist. The bist completes if this bit is '1'. This bit also reflects the value of "test_done" signal in BIST module.                 |

| 0   | bist_en_n      | R      | R/W    | 1       | This bit enable the BIST function and also drives the "reset" signal in BIST module.  1: disable BIST function  0: enable BIST function                                  |

### Pegasus II

### **USB / Fast Ethernet with MII Interface**

### • Offset 20h: EEPROM offset

| Bit | Field      | HW<br>access | SW<br>access | Default<br>value | Description                                  |

|-----|------------|--------------|--------------|------------------|----------------------------------------------|

| 7-6 | reserved   |              |              | ,                |                                              |

| 5-0 | rom_offset | R            | R/W          | 0                | SW sets this register when access to EEPROM. |

### • Offset 21h: EEPROM data low

| Bit | Field      | HW     | SW     | Default | Description                                       |

|-----|------------|--------|--------|---------|---------------------------------------------------|

|     |            | access | access | value   |                                                   |

| 7-0 | romdata_lo | R/W    | R/W    | 0       | SW sets this register when writes to EEPROM.      |

|     |            |        |        |         | HW sets this register when read data from EEPROM. |

### • Offset 22h: EEPROM data high

| Bit | Field      | HW     | $\mathbf{SW}$ | Default | Description                                        |

|-----|------------|--------|---------------|---------|----------------------------------------------------|

|     |            | access | access        | value   |                                                    |

| 7-0 | romdata_hi | R/W    | R/W           | 0       | SW sets this register when writes to EEPROM.       |

|     |            |        |               |         | HW sets this register when reads data from EEPROM. |

### • Offset 23h: EEPROM access control

| Bit | Field     | HW     | SW     | Default | Description                                                      |

|-----|-----------|--------|--------|---------|------------------------------------------------------------------|

|     |           | access | access | value   |                                                                  |

| 7-3 | reserved  |        |        |         |                                                                  |

| 2   | done      | R/W    | R/W    | 0       | Set by HW to indicate successful completion of EEPROM access.    |

|     |           |        |        |         | Clear by SW when initiate a new access to EEPROM                 |

| 1   | rd_eeprom | R      | R/W    | 0       | Set by SW to initiate a read access to EEPROM. SW sets this bit  |

|     |           |        |        |         | after it well setting the rom_offset.                            |

| 0   | wr_eeprom | R      | R/W    | 0       | Set by SW to initiate a write access to EEPROM. SW set this bit  |

|     |           |        |        |         | after it well setting the rom_offset, romdata_lo and romdata_hi. |

#### • Offset 24h: reserved

### • Offset 25h: PHY address

| Bit | Field    | HW<br>access | SW<br>access | Default value | Description      |

|-----|----------|--------------|--------------|---------------|------------------|

| 7-5 | reserved |              |              |               |                  |

| 4-0 | phy addr | R            | R/W          | 0             | MII PHY address. |

### • Offset 26h: PHY data low

| Bit | Field       | HW<br>access | SW<br>access | Default<br>value | Description                                                                                              |

|-----|-------------|--------------|--------------|------------------|----------------------------------------------------------------------------------------------------------|

| 7-0 | phydata_low | R/W          | R/W          | 0                | SW set this register when write to phy registers. HW set this register when read data from PHY register. |

ADMtek Incorporated 2F, No2, Li-Hsin Road Science-Based Industrial Park 300 Hsinchu, Taiwan, R.O.C. Tel:886-3-5788879 Fax: 886-3-5788871

ADMtek Incorporated Confidential

2.04 http://www.admtek.com.tw

Version: 2.04

22

### Pegasus II

### **USB / Fast Ethernet with MII Interface**

### • Offset 27h: PHY data high

| Bit | Field        | HW<br>access | SW access | Default<br>value | Description                                            |

|-----|--------------|--------------|-----------|------------------|--------------------------------------------------------|

| 7-0 | phydata_high | R/W          | R/W       | 0                | SW set this register when write to phy registers.      |

|     |              |              |           |                  | HW set this register when read data from PHY register. |

### • Offset 28h: PHY access control

| Bit | Field       | HW     | SW     | Default | Description                                                       |

|-----|-------------|--------|--------|---------|-------------------------------------------------------------------|

|     |             | access | access | value   |                                                                   |

| 7   | done        | R/W    | R/W    | 0       | Set by HW to indicate successful completion of PHY access.        |

|     |             |        |        |         | Clear by SW when initiate a new access to PHY.                    |

| 6   | rd_phy      | R      | R/W    | 0       | Set by SW to initiate a read access to PHY register. SW set this  |

|     |             |        |        |         | bit after it well setting the phy_addr and phyreg_addr.           |

| 5   | wr_phy      | R      | R/W    | 0       | Set by SW to initiate a write access to PHY register. SW set this |

|     |             |        |        |         | bit after it well setting the phy_addr, phyreg_addr and           |

|     |             |        |        |         | phyreg_data.                                                      |

| 4-0 | phyreg_addr | R      | R/W    | 0       | PHY register address.                                             |

### • Offset 29h: reserved

### • Offset 2Ah: usb bus status

| Bit | Field       | HW     | SW     | Default | Description                                                                     |

|-----|-------------|--------|--------|---------|---------------------------------------------------------------------------------|

|     |             | access | access | value   |                                                                                 |

| 7-2 | reserved    |        |        |         |                                                                                 |

| 1   | usb_resume  | R/W    | R/W    |         | Set by HW to indicate usb bus in resume state. Clear by SW read this register.  |

| 0   | usb_suspend | R/W    | R/W    |         | Set by HW to indicate usb bus in suspend state. Clear by SW read this register. |

### • Offset 2Bh: transmit status\_1

| Bit | Field          | HW     | SW     | Default | Description                                              |

|-----|----------------|--------|--------|---------|----------------------------------------------------------|

|     |                | access | access | value   |                                                          |

| 7   | txunderrun     | R/W    | R      | 0       | Set by HW to indicate tx underrun error.                 |

|     |                |        |        |         | Clear by SW read this register or after EP3 is accessed. |

| 6   | excessive_col  | R/W    | R      | 0       | Set by HW to indicate excessive collision.               |

|     |                |        |        |         | Clear by SW read this register or after EP3 is accessed. |

| 5   | late_col       | R/W    | R      | 0       | Set by HW to indicate late collision error.              |

|     |                |        |        |         | Clear by SW read this register or after EP3 is accessed. |

| 4   | no_carrier     | R/W    | R      | 0       | Set by HW to indicate no carrier.                        |

|     |                |        |        |         | Clear by SW read this register or after EP3 is accessed. |

| 3   | loss_carrier   | R/W    | R      | 0       | Set by HW to indicate carrier loss.                      |

|     |                |        |        |         | Clear by SW read this register or after EP3 is accessed. |

| 2   | jabber_timeout | R/W    | R      | 0       | Set by HW to indicate jabber time out.                   |

|     |                |        |        |         | Clear by SW read this register or after EP3 is accessed. |

| 1-0 | reserved       |        |        |         |                                                          |

Version: 2.04

23

### Pegasus II

### **USB / Fast Ethernet with MII Interface**

### • Offset 2Ch: transmit status\_2

| Bit | Field        | HW     | SW     | Default | Description                                                        |

|-----|--------------|--------|--------|---------|--------------------------------------------------------------------|

|     |              | access | access | value   |                                                                    |

| 7   | txfifo_full  | R/W    | R      | 0       | Set by HW to indicate tx fifo full.                                |

|     |              |        |        |         | Clear by SW read this register or after EP3 is accessed.           |

| 6   | txfifo_empty | R/W    | R      | 0       | Set by HW to indicate tx fifo empty.                               |

|     |              |        |        |         | Clear by SW read this register or after EP3 is accessed.           |

| 5-4 | reserved     |        |        |         |                                                                    |

| 3-0 | txpkt_cnt    | R/W    | R      |         | Set by HW to indicate Ethernet transmit packet count every         |

|     |              |        |        |         | interrupt EP polling. If more than 15 packets have been            |

|     |              |        |        |         | transmitted, this value will keep as 15. Clear by SW read or after |

|     |              |        |        |         | EP3 is accessed.                                                   |

### • Offset 2Dh: receive status

| Bit | Field       | HW     | SW     | Default | Description                                              |

|-----|-------------|--------|--------|---------|----------------------------------------------------------|

|     |             | access | access | value   |                                                          |

| 7-2 | reserved    |        |        |         |                                                          |

| 1   | rx_pause    | R/W    | R/W    | 0       | Set by HW to indicate a PAUSE frame is received.         |

|     |             |        |        |         | Clear by SW read this register or after EP3 is accessed. |

| 0   | rx_overflow | R/W    | R      | 0       | Clear by SW read this register or after EP3 is accessed. |

### • Offset 2Eh: receive lost packet count high

| Bit | Field      | HW     | SW     | Default | Description                                                    |

|-----|------------|--------|--------|---------|----------------------------------------------------------------|

|     |            | access | access | value   |                                                                |

| 7   | Lostpkt_   | R/W    | R/W    | 0       |                                                                |

| 6-0 | rx_lostpkt | R/W    | R/W    | 0       | The [14:8] of lost packet counts due to receive FIFO overflow. |

|     |            |        |        |         | Clear by SW read this register or after EP3 is accessed.       |

### • Offset 2Eh: receive lost packet count low

| Bit | Field      | HW<br>access | SW<br>access | Default<br>value | Description                                                                                                            |

|-----|------------|--------------|--------------|------------------|------------------------------------------------------------------------------------------------------------------------|

| 7-0 | rx_lostpkt | R/W          | R/W          | 0                | The [7:0] of lost packet counts due to receive FIFO overflow. Clear by SW read this register or after EP3 is accessed. |

### • Wake-up frames

| Offset | Bit | Field      | HW     | SW     | Default | Description                              |

|--------|-----|------------|--------|--------|---------|------------------------------------------|

|        |     |            | access | access | value   |                                          |

| 30-3Fh |     | f0_mask    |        |        |         | The 128 mask bits for fram0.             |

| 40h    | 7-0 | f0_offset  | R      | R/W    | 0       | Offset for wakeup frame0.                |

| 41h    | 7-0 | f0_crc_low | R      | R/W    | 0       | The low byte of CRC16 match for frame 0. |

### ADM 8511

### Pegasus II USB / Fast Ethernet with MII Interface

| 42h    | 7-0 | f0_crc_hi  | R | R/W | 0 | The high byte of CRC16 match for frame 0. |

|--------|-----|------------|---|-----|---|-------------------------------------------|

| 43-47h |     | reserved   |   |     |   |                                           |

| 48-57h |     | f1_mask    |   |     |   | The 128 mask bits for fram1.              |

| 58h    | 7-0 | fl_offset  | R | R/W | 0 | Offset for wakeup frame1.                 |

| 59h    | 7-0 | fl_crc_low | R | R/W | 0 | The low byte of CRC16 match for frame 1.  |

| 5Ah    | 7-0 | fl_crc_hi  | R | R/W | 0 | The high byte of CRC16 match for frame 1. |

| 5B-5Fh |     | reserved   |   |     |   |                                           |

| 60-6Fh |     | f2_mask    |   |     |   | The 128 mask bits for fram2.              |

| 70h    | 7-0 | f2_offset  | R | R/W | 0 | Offset for wakeup frame2.                 |

| 71h    | 7-0 | f2_crc_low | R | R/W | 0 | The low byte of CRC16 match for frame 2.  |

| 72h    | 7-0 | f2_crc_hi  | R | R/W | 0 | The high byte of CRC16 match for frame 2. |

| 73-77h |     | reserved   |   |     |   |                                           |

### • Offset 78h: wake-up control

| Bit | Field         | HW     | SW     | Default | Description                                        |

|-----|---------------|--------|--------|---------|----------------------------------------------------|

|     |               | access | access | value   |                                                    |

| 7   | mgcpkt_en     | R      | R/W    | 0       | Set by SW to enable magic packet wakeup function.  |

| 6   | link_en       | R      | R/W    | 0       | Set by SW to enable link status wakeup function.   |

| 5   | wakeframe0_en | R      | R/W    | 0       | Set by SW to enable wakeup frame0 wakeup function. |

| 4   | wakeframe1_en | R      | R/W    | 0       | Set by SW to enable wakeup frame1 wakeup function. |

| 3   | wakeframe2_en | R      | R/W    | 0       | Set by SW to enable wakeup frame2 wakeup function. |

| 2   | crc16type     | R      | R/W    | 1       | 0: CRC-16 initial contents = 0000h                 |

|     |               |        |        |         | 1: CRC-16 initial contents = ffffh                 |

| 1-0 | reserved      |        |        |         |                                                    |

### • Offset 79h: reserved

### • Offset 7Ah: wake-up status

| Bit | Field        | HW     | SW     | Default | Description                                                      |

|-----|--------------|--------|--------|---------|------------------------------------------------------------------|

|     |              | access | access | value   |                                                                  |

| 7   | rx_mgcpkt    | R/W    | R      | 0       | Set by HW when receive a magic packet.                           |

|     |              |        |        |         | Clear by SW read this register.                                  |

| 6   | link_wake    | R/W    | R      | 0       | Set by HW when link status change.                               |

|     | _            |        |        |         | Clear by SW read this register.                                  |

| 5   | rx_wakeframe | R/W    | R      | 0       | Set by HW when receive a wakeup frame.                           |

|     | _            |        |        |         | Clear by SW read this register.                                  |

| 4-1 | reserved     |        |        |         |                                                                  |

| 0   | link_sts     | R/W    | R      | 0       | Indicate the current link status, 1 for link on, 0 for link off. |

### • Offset 7B: internal PHY control

| Bit | Field         | HW     | SW     | Default | Description                                                         |

|-----|---------------|--------|--------|---------|---------------------------------------------------------------------|

|     |               | access | access | value   |                                                                     |

| 7-2 | reserved      |        |        |         |                                                                     |

| 1   | power_down_ph | R      | R/W    | 0       | 0: power down internal 10/100 PHY                                   |

|     | у             |        |        |         | 1: enable internal 10/100 PHY                                       |

| 0   | phyrst        | R      | R/W    | 0       | 1: Reset internal PHY                                               |

|     |               |        |        |         | The internal PHY is reset when this bit is written with 1 and stops |

|     |               |        |        |         | reset when this bit is written with 0.                              |

25

### Pegasus II

### **USB / Fast Ethernet with MII Interface**

### • Offset 7Ch: GPIO[5:4]

| Bit | Field    | HW     | SW     | Default | Description                                                     |

|-----|----------|--------|--------|---------|-----------------------------------------------------------------|

|     |          | access | access | value   |                                                                 |

| 7-6 | reserved |        |        |         |                                                                 |

| 5   | GPIO5_oe | R      | R/W    | 0       | GPIO5 output enable.                                            |

|     |          |        |        |         | 1: GPIO5 is used for output                                     |

|     |          |        |        |         | 0: GPIO5 is used for input                                      |

| 4   | GPIO5_o  | R      | R/W    | 0       | GPIO5 output value.                                             |

|     |          |        |        |         | When GPIO5 is used for output, this value is driven to GPIO5    |

|     |          |        |        |         | pin. Set by SW.                                                 |

| 3   | GPIO5_i  | R/W    | R      |         | GPIO5 input value.                                              |

|     |          |        |        |         | When GPIO5 is used for input, this field reflects the status of |

|     |          |        |        |         | GPIO5. Default is pulled-down.                                  |

| 2   | GPIO4_oe | R      | R/W    | 0       | GPIO4 output enable.                                            |

|     |          |        |        |         | 1: GPIO4 is used for output                                     |

|     |          |        |        |         | 0: GPIO4 is used for input                                      |

| 1   | GPIO4_o  | R      | R/W    | 0       | GPIO4 output value.                                             |

|     |          |        |        |         | When GPIO4 is used for output, this value id driven to GPIO4    |

|     |          |        |        |         | pin. Set by SW.                                                 |

| 0   | GPIO4_i  | R/W    | R      |         | GPIO4 input value.                                              |

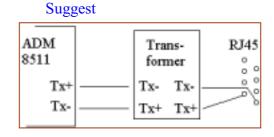

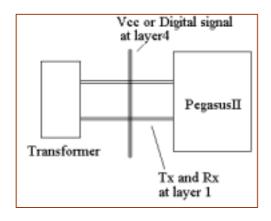

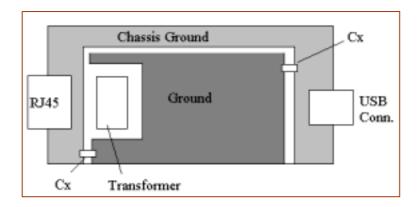

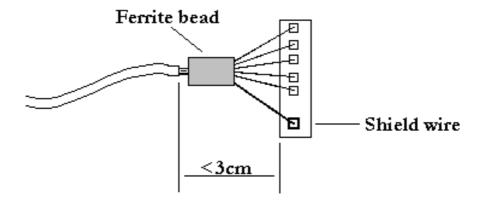

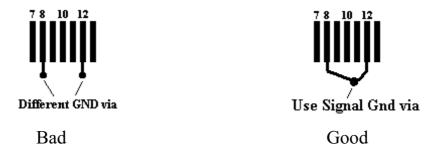

|     |          |        |        |         | When GPIO4 is used for input, this field reflects the status of |