查询ADS1158IRTCTG4供应商

ADS1158

www.ti.com

SBAS429A-JUNE 2008-REVISED JUNE 2008

# 16-Channel, 16-Bit Analog-to-Digital Converter

# FEATURES

TEXAS

16 Bits, No Missing Codes •

NSTRUMENTS

- **Fixed-Channel or Automatic Channel Scan**

- Fixed-Channel Data Rate: 125kSPS

- Auto-Scan Data Rate: 23.7kSPS/Channel

- **Single-Conversion Settled Data**

- 16 Single-Ended or 8 Differential Inputs

- Unipolar (+5V) or Bipolar (±2.5V) Operation .

- 0.3LSB (INL)

- DC Stability: 0.02µV/°C Offset Drift, 0.4ppm/°C Gain Drift

- **Open-Sensor Detection**

- **Conversion Control Pin**

- **Multiplexer Output for External Signal** Conditioning

- On-Chip Temperature, Reference, Offset, Gain, and Supply Voltage Readback

- 42mW Power Dissipation

- Standby, Sleep, and Power-Down Modes

- Eight General-Purpose Inputs/Outputs (GPIO)

- 32.768kHz Crystal Oscillator or External Clock

# **APPLICATIONS**

- Medical, Avionics, and Process Control

- Machine and System Monitoring

- Fast Scan Multi-Channel Instrumentation

- Industrial Systems

- Test and Measurement Systems

# DESCRIPTION

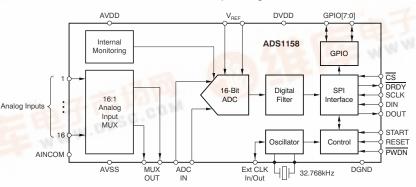

The ADS1158 is a 16-channel (multiplexed), low-noise, 16-bit, delta-sigma ( $\Delta\Sigma$ ) analog-to-digital converter (ADC) that provides single-cycle settled data at channel scan rates from 1.8k to 23.7k samples per second (SPS) per channel. A flexible input multiplexer accepts combinations of eight differential or 16 single-ended inputs with a full-scale differential range of 5V or true bipolar range of ±2.5V when operating with a 5V reference. The fourth-order delta-sigma modulator is followed by a fifth-order sinc digital filter optimized for low-noise performance.

The differential output of the multiplexer is accessible to allow signal conditioning before the input of the ADC. Internal system monitor registers provide supply voltage, temperature, reference voltage, gain, and offset data.

An onboard PLL generates the system clock from a 32.768kHz crystal, or can be overridden by an external clock source. A buffered system clock output (15.7MHz) is provided to drive a microcontroller or additional converters.

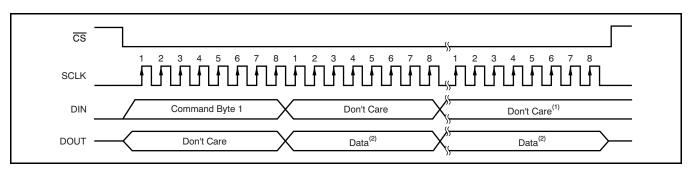

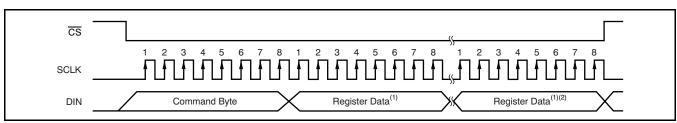

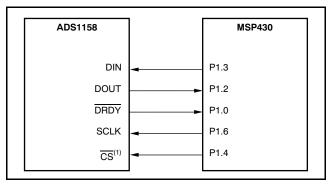

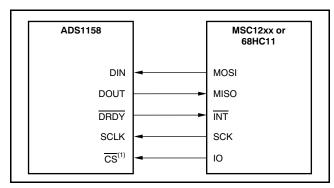

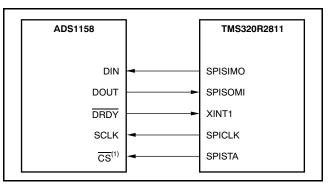

Serial digital communication is handled via an SPI<sup>™</sup>-compatible interface. A simple command word structure controls channel configuration, data rates, digital I/O, monitor functions, etc.

Programmable sensor bias current sources can be used to bias sensors or verify sensor integrity.

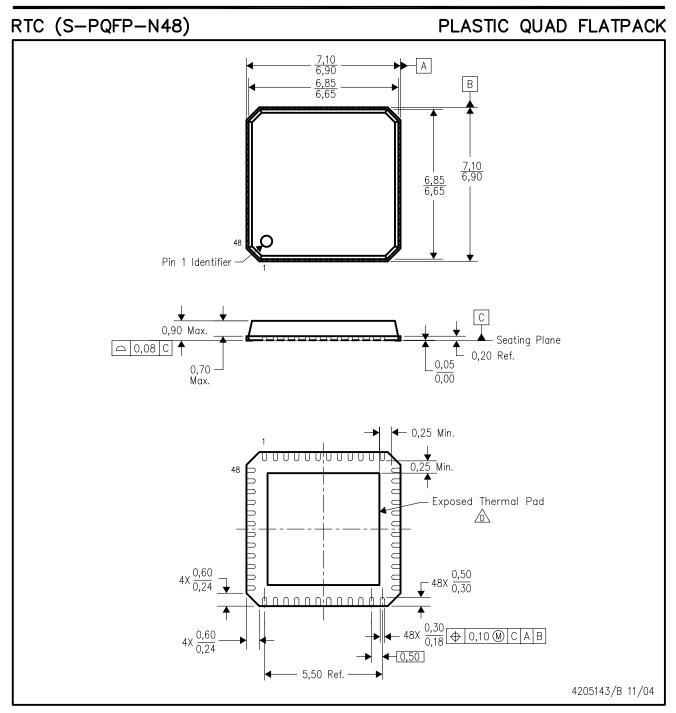

The ADS1158 operates from a unipolar +5V or bipolar  $\pm 2.5V$  analog supply and a digital supply compatible with interfaces ranging from 2.7V to 5.25V. The ADS1158 is available in a QFN-48 package.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Pinstruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

SPI is a trademark of Motorola, Inc. All other trademarks are the property of their respective owners.

PRODUCTION DATA information is current as of publication date. per the terr

# ADS1158

#### SBAS429A-JUNE 2008-REVISED JUNE 2008

www.ti.com

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

# **ORDERING INFORMATION**

For the most current package and ordering information see the Package Option Addendum at the end of this document, or see the TI web site at www.ti.com.

### **ABSOLUTE MAXIMUM RATINGS**

Over operating free-air temperature range, unless otherwise noted.<sup>(1)</sup>

|                               | ADS1158                    | UNIT |

|-------------------------------|----------------------------|------|

| AVDD to AVSS                  | -0.3 to +5.5               | V    |

| AVSS to DGND                  | -2.8 to +0.3               | V    |

| DVDD to DGND                  | -0.3 to +5.5               | V    |

| Input current                 | 100, momentary             | mA   |

| Input current                 | 10, continuous             | mA   |

| Analog input voltage          | AVSS – 0.3 to AVDD + 0.3 V |      |

| Digital input voltage to DGND | -0.3 to DVDD + 0.3         | V    |

| Maximum junction temperature  | +150                       | °C   |

| Operating temperature range   | -40 to +105                | °C   |

| Storage temperature range     | -60 to +150                | °C   |

(1) Stresses above these ratings may cause permanent damage. Exposure to absolute maximum conditions for extended periods may degrade device reliability. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those specified is not implied.

# **ELECTRICAL CHARACTERISTICS**

All specifications at  $T_A = -40^{\circ}$ C to +105°C, AVDD = +2.5V, AVSS = -2.5V, DVDD = +3.3V,  $f_{CLK} = 16$ MHz (external clock) or  $f_{CLK} = 15.729$ MHz (internal clock), OPA227 buffer between MUX outputs and ADC inputs,  $V_{REF} = +4.096V$ , and VREFN = -2.5V, unless otherwise noted.

|                                            |                                            |                        | ADS1158      |                              |              |                    |

|--------------------------------------------|--------------------------------------------|------------------------|--------------|------------------------------|--------------|--------------------|

| PARAMETER                                  |                                            | CONDITIONS             | MIN          | TYP                          | MAX          | UNIT               |

| Analog Multiplexer Inputs                  |                                            |                        |              |                              |              |                    |

| Absolute input voltage                     | AIN0–AIN15,<br>AINCOM with respect to DGND |                        | AVSS – 100mV |                              | AVDD + 100mV | V                  |

| On-channel resistance                      | -                                          |                        |              | 80                           |              | Ω                  |

| Crosstalk                                  |                                            | f <sub>IN</sub> = 1kHz |              | -110                         |              | dB                 |

| Sensor bias (current source)               |                                            | SBCS[1:0] = 01         |              | 1.5                          |              | ۵                  |

|                                            |                                            | SBCS[1:0] = 11         |              | 24                           |              | μA                 |

| 1.5µA:24µA ratio error                     |                                            |                        |              | 1                            |              | %                  |

| ADC Input                                  |                                            |                        |              |                              |              |                    |

| Full-scale input voltage                   | (V <sub>IN</sub> = ADCINP – ADCINN)        |                        |              | $\pm 1.0\overline{6}V_{REF}$ |              | V                  |

| Absolute input voltage                     | (ADCINP, ADCINN)                           |                        | AVSS - 100mV |                              | AVDD + 100mV | V                  |

| Differential input impedance               |                                            |                        |              | 65                           |              | kΩ                 |

| System Performance                         |                                            |                        |              |                              |              |                    |

| Resolution                                 |                                            | No missing codes       | 16           |                              |              | Bits               |

| Data rate, fixed-channel mode              |                                            |                        | 1.953        |                              | 125          | kSPS               |

| Data rate, auto-scan mode                  |                                            |                        | 1.805        |                              | 23.739       | kSPS               |

| Integral nonlinearity (INL) <sup>(1)</sup> |                                            | Differential input     |              | 0.3                          | 1            | LSB <sup>(2</sup>  |

| Offset error                               | Chopping on                                | Shorted inputs         | -1           | -0.5 <sup>(3)</sup>          | 0            | LSB                |

| Offset drift                               |                                            | Shorted inputs         |              | 1                            |              | μV/°C              |

| Gain error                                 |                                            |                        |              | 0.1                          | 0.5          | %                  |

| Gain drift                                 |                                            |                        |              | 2                            |              | ppm/°              |

| Noise                                      |                                            |                        |              | 0.6                          |              | LSB ( <sub>P</sub> |

| Common-mode rejection                      |                                            | $f_{CM} = 60Hz$        |              | 100                          |              | dB                 |

| Davida averalis actions                    | AVDD, AVSS                                 | £ 0011-                |              | 85                           |              | dB                 |

| Power-supply rejection                     | DVDD                                       | $f_{PS} = 60Hz$        | 95           | 95                           |              |                    |

| Voltage Reference Input                    |                                            |                        |              |                              |              |                    |

| Reference input voltage                    | $(V_{REF} = VREFP - VREFN)$                |                        | 0.5          | 4.096                        | AVDD – AVSS  | V                  |

| Negative reference input (VREI             | =N)                                        |                        | AVSS-0.1V    |                              | VREFP – 0.5  | V                  |

| Positive reference input (VREF             | P)                                         |                        | VREFN + 0.5  |                              | AVDD + 0.1V  | V                  |

| Reference input impedance                  |                                            |                        |              | 40                           |              | kΩ                 |

| System Parameters                          |                                            |                        |              |                              |              |                    |

| External reference reading error           |                                            |                        |              | 1                            | 3            | %                  |

| Analog supply reading error                |                                            |                        |              | 1                            | 5            | %                  |

| Tomporatura access reading                 | Voltage                                    | $T_A = +25^{\circ}C$   |              | 168                          |              | mV                 |

| Temperature sensor reading                 | Coefficient                                |                        |              | 394                          |              | μV/°C              |

(1) Best straight line fit method.

FSR = Full-scale range =  $2.13V_{REF}$ . Systematic -0.5LSB in reading code. (2) (3)

SBAS429A-JUNE 2008-REVISED JUNE 2008

# ELECTRICAL CHARACTERISTICS (continued)

All specifications at  $T_A = -40^{\circ}$ C to +105°C, AVDD = +2.5V, AVSS = -2.5V, DVDD = +3.3V,  $f_{CLK} = 16$ MHz (external clock) or  $f_{CLK} = 15.729$ MHz (internal clock), OPA227 buffer between MUX outputs and ADC inputs,  $V_{REF} = +4.096$ V, and VREFN = -2.5V, unless otherwise noted.

|                                  |                                    |                                                                          | ADS1158     |        |             |      |

|----------------------------------|------------------------------------|--------------------------------------------------------------------------|-------------|--------|-------------|------|

| PARAMETER                        |                                    | CONDITIONS                                                               | MIN         | TYP    | MAX         | UNIT |

| Digital Input/Output             |                                    |                                                                          |             |        |             |      |

|                                  | V <sub>IH</sub>                    |                                                                          | 0.7DVDD     |        | DVDD        | V    |

| Logic levels                     | VIL                                |                                                                          | DGND        |        | 0.3DVDD     | V    |

| Logic levels                     | V <sub>OH</sub>                    | $I_{OH} = 2mA$                                                           | 0.8DVDD     |        | DVDD        | V    |

|                                  | V <sub>OL</sub>                    | $I_{OL} = 2mA$                                                           | DGND        |        | 0.2DVDD     | V    |

| Input leakage                    |                                    | $V_{IN} = DVDD, GND$                                                     |             |        | 10          | μΑ   |

| Master clock input (CLKIO)       | Frequency                          |                                                                          | 0.1         |        | 16          | MHz  |

|                                  | Duty cycle                         |                                                                          | 40          |        | 60          | %    |

|                                  | Crystal frequency                  |                                                                          |             | 32.768 |             | kHz  |

| Crystal oscillator               | Clock output frequency             |                                                                          |             | 15.729 |             | MHz  |

| (see Crystal Oscillator section) | Start-up time (clock output valid) |                                                                          |             | 150    |             | ms   |

|                                  | Clock output duty cycle            |                                                                          | 40          |        | 60          | %    |

| Power Supply                     |                                    |                                                                          |             |        |             |      |

| DVDD                             |                                    |                                                                          | 2.7         |        | 5.25        | V    |

| AVSS                             |                                    |                                                                          | -2.6        |        | 0           | V    |

| AVDD                             |                                    |                                                                          | AVSS + 4.75 |        | AVSS + 5.25 | V    |

|                                  |                                    | External clock<br>operation                                              |             | 0.25   | 0.6         | mA   |

| DVDD supply current              |                                    | Internal oscillator<br>operation, clock<br>output disabled               |             | 0.04   |             | mA   |

|                                  |                                    | Internal oscillator<br>operation, clock<br>output enabled <sup>(4)</sup> |             | 1.4    |             | mA   |

|                                  |                                    | Power-down <sup>(5)</sup>                                                |             | 1      | 25          | μA   |

|                                  |                                    | Converting                                                               |             | 8.2    | 12          | mA   |

|                                  |                                    | Standby                                                                  |             | 5.6    |             | mA   |

| AVDD, AVSS supply current        |                                    | Sleep                                                                    |             | 2.1    |             | mA   |

|                                  |                                    | Power-down                                                               |             | 2      | 200         | μA   |

|                                  |                                    | Converting                                                               |             | 42     | 62          | mW   |

| Power dissipation                |                                    | Standby                                                                  |             | 29     |             | mW   |

|                                  |                                    | Sleep                                                                    |             | 11     |             | mW   |

|                                  |                                    | Power-down                                                               |             | 14     |             | μW   |

(4) CLKIO load = 20pF.(5) No clock applied to CLKIO.

4

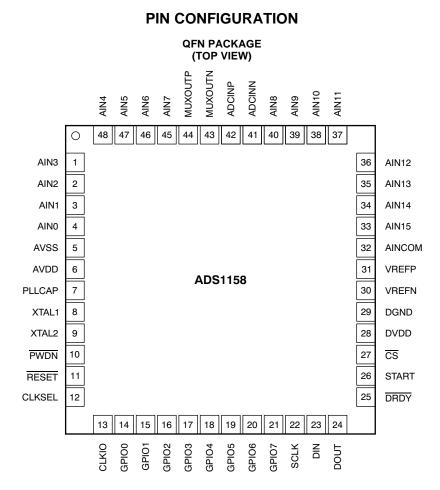

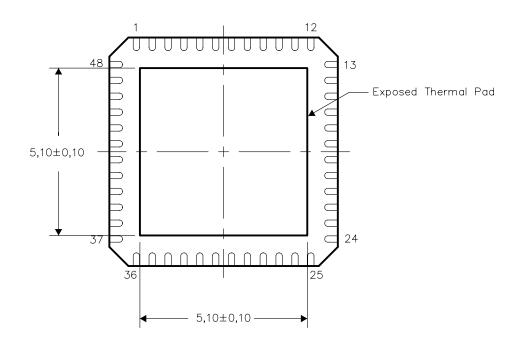

#### **PIN ASSIGNMENTS**

| PIN # | NAME   | ANALOG/DIGITAL<br>INPUT/OUTPUT | DESCRIPTION                                                                                                                                            |

|-------|--------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | AIN3   | Analog input                   | Analog input 3: single-ended channel 3, differential channel 1 (-)                                                                                     |

| 2     | AIN2   | Analog input                   | Analog input 2: single-ended channel 2, differential channel 1 (+)                                                                                     |

| 3     | AIN1   | Analog input                   | Analog input 1: single-ended channel 1, differential channel 0 (-)                                                                                     |

| 4     | AIN0   | Analog input                   | Analog input 0: single-ended channel 0, differential channel 0 (+)                                                                                     |

| 5     | AVSS   | Analog                         | Negative analog power supply: 0V for unipolar operation, –2.5V for bipolar operation.<br>(Internally connected to exposed thermal pad of QFN package.) |

| 6     | AVDD   | Analog                         | Positive analog power supply: +5V for unipolar operation, +2.5V for bipolar operation.                                                                 |

| 7     | PLLCAP | Analog                         | PLL bypass capacitor: connect 22nF capacitor to AVSS when using crystal oscillator.                                                                    |

| 8     | XTAL1  | Analog                         | 32.768kHz crystal oscillator input 1; see Crystal Oscillator section.                                                                                  |

| 9     | XTAL2  | Analog                         | 32.768kHz crystal oscillator input 2; see Crystal Oscillator section.                                                                                  |

| 10    | PWDN   | Digital input                  | Power-down input: hold low for minimum of two $f_{CLK}$ cycles to engage low-power mode.                                                               |

| 11    | RESET  | Digital input                  | Reset input: hold low for minimum of two $f_{CLK}$ cycles to reset the device.                                                                         |

| 12    | CLKSEL | Digital input                  | Clock select input: Low = activates crystal oscillator, $f_{CLK}$ output on CLKIO.<br>High = disables crystal oscillator, apply $f_{CLK}$ to CLKIO.    |

| 13    | CLKIO  | Digital I/O                    | System clock input/output (see CLKSEL pin)                                                                                                             |

| 14    | GPIO0  | Digital I/O                    | General-purpose digital input/output 0                                                                                                                 |

| 15    | GPIO1  | Digital I/O                    | General-purpose digital input/output 1                                                                                                                 |

| 16    | GPIO2  | Digital I/O                    | General-purpose digital input/output 2                                                                                                                 |

| 17    | GPIO3  | Digital I/O                    | General-purpose digital input/output 3                                                                                                                 |

| 18    | GPIO4  | Digital I/O                    | General-purpose digital input/output 4                                                                                                                 |

| 19    | GPIO5  | Digital I/O                    | General-purpose digital input/output 5                                                                                                                 |

| 20    | GPIO6  | Digital I/O                    | General-purpose digital input/output 6                                                                                                                 |

# ADS1158

www.ti.com

SBAS429A-JUNE 2008-REVISED JUNE 2008

# PIN ASSIGNMENTS (continued)

| PIN # | NAME    | ANALOG/DIGITAL<br>INPUT/OUTPUT | DESCRIPTION                                                                             |

|-------|---------|--------------------------------|-----------------------------------------------------------------------------------------|

| 21    | GPIO7   | Digital I/O                    | General-purpose digital input/output 7                                                  |

| 22    | SCLK    | Digital input                  | SPI interface clock input: data clocked in on rising edge, clocked out on falling edge. |

| 23    | DIN     | Digital input                  | SPI interface data input: data are input to the device.                                 |

| 24    | DOUT    | Digital output                 | SPI interface data output: data are output from the device.                             |

| 25    | DRDY    | Digital output                 | Data ready output: active low.                                                          |

| 26    | START   | Digital input                  | Start conversion input: active high.                                                    |

| 27    | CS      | Digital input                  | SPI interface chip select input: active low.                                            |

| 28    | DVDD    | Digital                        | Digital power supply: 2.7V to 5.25V                                                     |

| 29    | DGND    | Digital                        | Digital ground                                                                          |

| 30    | VREFN   | Analog input                   | Reference input negative                                                                |

| 31    | VREFP   | Analog input                   | Reference input positive                                                                |

| 32    | AINCOM  | Analog input                   | Analog input common: common input pin to all single-ended inputs.                       |

| 33    | AIN15   | Analog input                   | Analog input 15: single-ended channel 15, differential channel 7 (-)                    |

| 34    | AIN14   | Analog input                   | Analog input 14: single-ended channel 14, differential channel 7 (+)                    |

| 35    | AIN13   | Analog input                   | Analog input 13: single-ended channel 13, differential channel 6 (-)                    |

| 36    | AIN12   | Analog input                   | Analog input 12: single-ended channel 12, differential channel 6 (+)                    |

| 37    | AIN11   | Analog input                   | Analog input 11: single-ended channel 11, differential channel 5 (-)                    |

| 38    | AIN10   | Analog input                   | Analog input 10: single-ended channel 10, differential channel 5 (+)                    |

| 39    | AIN9    | Analog input                   | Analog input 9: single-ended channel 9, differential channel 4 (-)                      |

| 40    | AIN8    | Analog input                   | Analog input 8: single-ended channel 8, differential channel 4 (+)                      |

| 41    | ADCINN  | Analog input                   | ADC differential input (-)                                                              |

| 42    | ADCINP  | Analog input                   | ADC differential input (+)                                                              |

| 43    | MUXOUTN | Analog output                  | Multiplexer differential output (-)                                                     |

| 44    | MUXOUTP | Analog output                  | Multiplexer differential output (+)                                                     |

| 45    | AIN7    | Analog input                   | Analog input 7: single-ended channel 7, differential channel 3 (-)                      |

| 46    | AIN6    | Analog input                   | Analog input 6 : single-ended channel 6, differential channel 3 (+)                     |

| 47    | AIN5    | Analog input                   | Analog input 5: single-ended channel 5, differential channel 2 (-)                      |

| 48    | AIN4    | Analog input                   | Analog input 4: single-ended channel 4, differential channel 2 (+)                      |

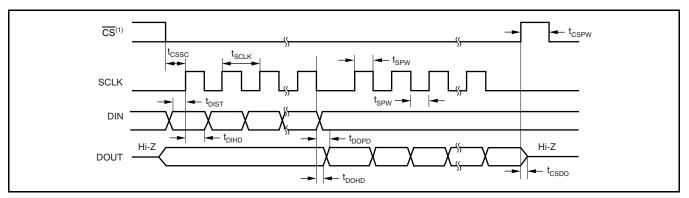

# PARAMETER MEASUREMENT INFORMATION

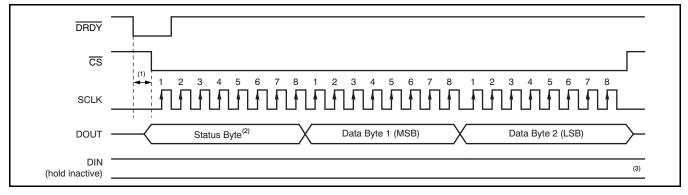

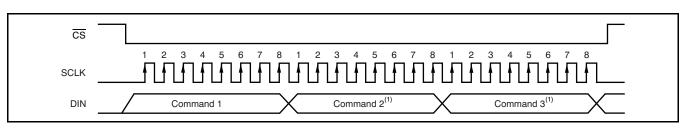

(1)  $\overline{\text{CS}}$  can be tied low.

# Figure 1. Serial Interface Timing

### SERIAL INTERFACE TIMING CHARACTERISTICS

## At $T_A$ = -40°C to +105°C and DVDD = 2.7V to 5.25V, unless otherwise noted.

| SYMBOL            | DESCRIPTION                                                           | MIN | MAX                 | UNITS              |

|-------------------|-----------------------------------------------------------------------|-----|---------------------|--------------------|

| t <sub>SCLK</sub> | SCLK period                                                           | 2   |                     | $\tau_{CLK}^{(1)}$ |

| t <sub>SPW</sub>  | SCLK high or low pulse width (exceeding max resets SPI interface)     | 0.8 | 4096 <sup>(2)</sup> | τ <sub>CLK</sub>   |

| t <sub>CSSC</sub> | CS low to first SCLK: setup time <sup>(3)</sup>                       | 2.5 |                     | τ <sub>CLK</sub>   |

| t <sub>DIST</sub> | Valid DIN to SCLK rising edge: setup time                             | 10  |                     | ns                 |

| t <sub>DIHD</sub> | Valid DIN to SCLK rising edge: hold time                              | 5   |                     | ns                 |

| t <sub>DOPD</sub> | SCLK falling edge to valid new DOUT: propagation delay <sup>(4)</sup> |     | 20                  | ns                 |

| t <sub>DOHD</sub> | SCLK falling edge to old DOUT invalid: hold time                      | 0   |                     | ns                 |

| t <sub>CSDO</sub> | CS high to DOUT invalid (3-state)                                     |     | 5                   | τ <sub>CLK</sub>   |

| t <sub>CSPW</sub> | CS pulse width high                                                   | 2   |                     | τ <sub>CLK</sub>   |

$\tau_{CLK}$  = master clock period = 1/f<sub>CLK</sub>. <u>Programmable to 256</u>  $\tau_{CLK}$ . (1)

(2)

(3) (4) CS can be tied low.

DOUT load =  $20pF \parallel 100k\Omega$  to DGND.

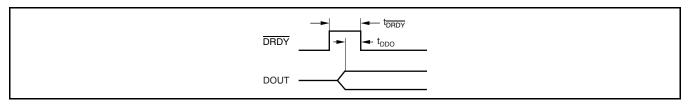

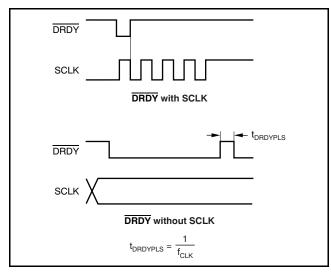

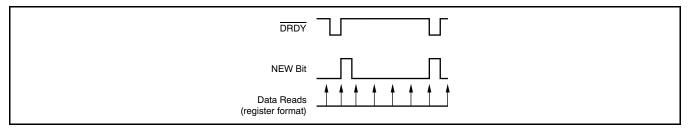

# Figure 2. DRDY Update Timing

# **DRDY UPDATE TIMING CHARACTERISTICS**

| SYMBOL            | DESCRIPTION                                                          | ТҮР | UNITS            |

|-------------------|----------------------------------------------------------------------|-----|------------------|

| t <sub>DRDY</sub> | DRDY high pulse width without data read                              | 1   | τ <sub>CLK</sub> |

| t <sub>DDO</sub>  | Valid DOUT to $\overline{DRDY}$ falling edge ( $\overline{CS} = 0$ ) | 0.5 | τ <sub>CLK</sub> |

TEXAS INSTRUMENTS

SBAS429A-JUNE 2008-REVISED JUNE 2008

www.ti.com

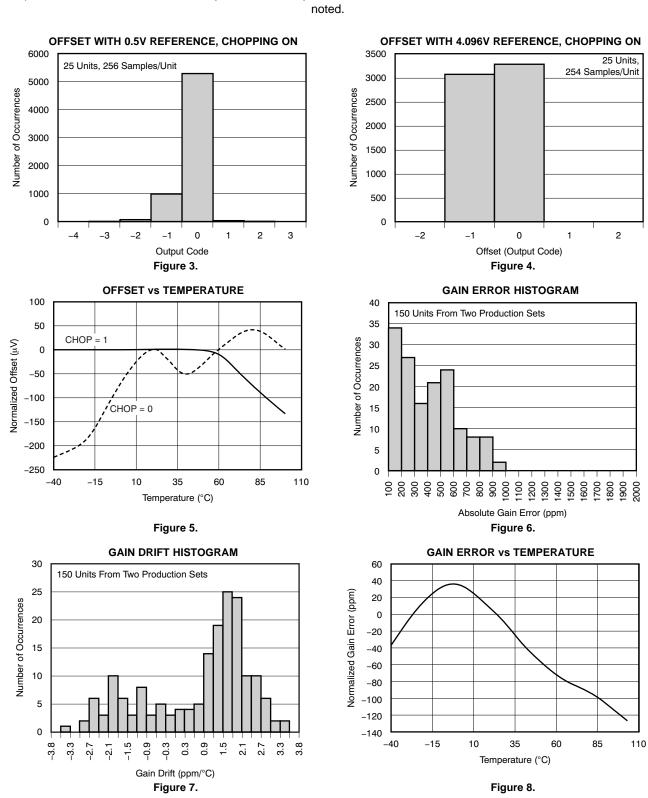

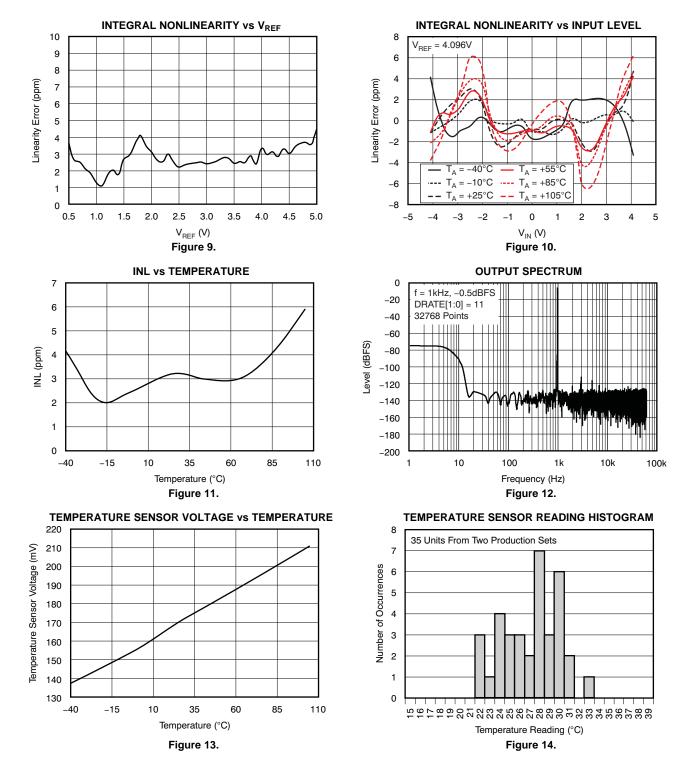

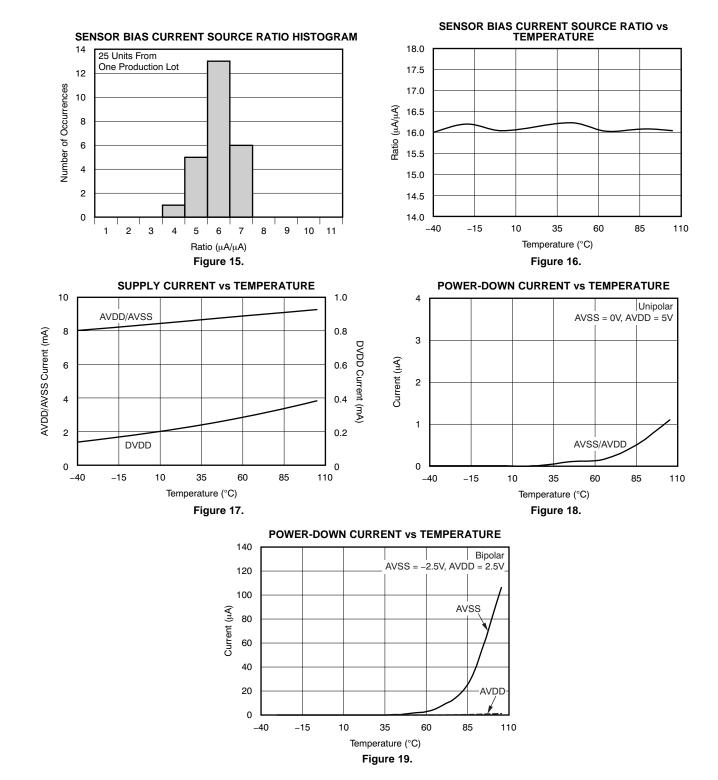

# TYPICAL CHARACTERISTICS

At  $T_A = +25^{\circ}$ C, AVDD = +2.5V, AVSS = -2.5V, DVDD = +3.3V,  $f_{CLK} = 16$ MHz (external clock) or  $f_{CLK} = 15.729$ MHz (internal clock), OPA227 buffer between MUX outputs and ADC inputs, VREFP = +2.048V, and VREFN = -2.048V, unless otherwise noted.

Submit Documentation Feedback

8

Copyright © 2008, Texas Instruments Incorporated

# **TYPICAL CHARACTERISTICS (continued)**

At  $T_A = +25^{\circ}$ C, AVDD = +2.5V, AVSS = -2.5V, DVDD = +3.3V,  $f_{CLK} = 16$ MHz (external clock) or  $f_{CLK} = 15.729$ MHz (internal clock), OPA227 buffer between MUX outputs and ADC inputs, VREFP = +2.048V, and VREFN = -2.048V, unless otherwise noted.

# ADS1158

www.ti.com

SBAS429A-JUNE 2008-REVISED JUNE 2008

# **TYPICAL CHARACTERISTICS (continued)**

At  $T_A = +25^{\circ}C$ , AVDD = +2.5V, AVSS = -2.5V, DVDD = +3.3V,  $f_{CLK} = 16$ MHz (external clock) or  $f_{CLK} = 15.729$ MHz (internal clock), OPA227 buffer between MUX outputs and ADC inputs, VREFP = +2.048V, and VREFN = -2.048V, unless otherwise noted.

# OVERVIEW

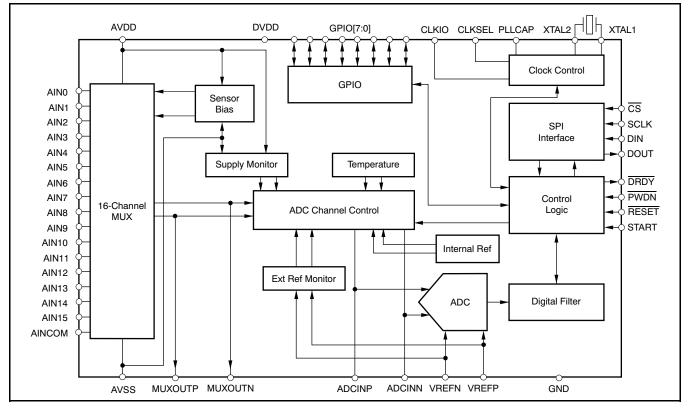

The ADS1158 is a flexible, 16-bit, low-noise ADC optimized for fast multi-channel, high-resolution measurement systems. The converter provides a maximum channel scan rate of 23.7kSPS, giving a complete 16-channel scan in less than 700µs.

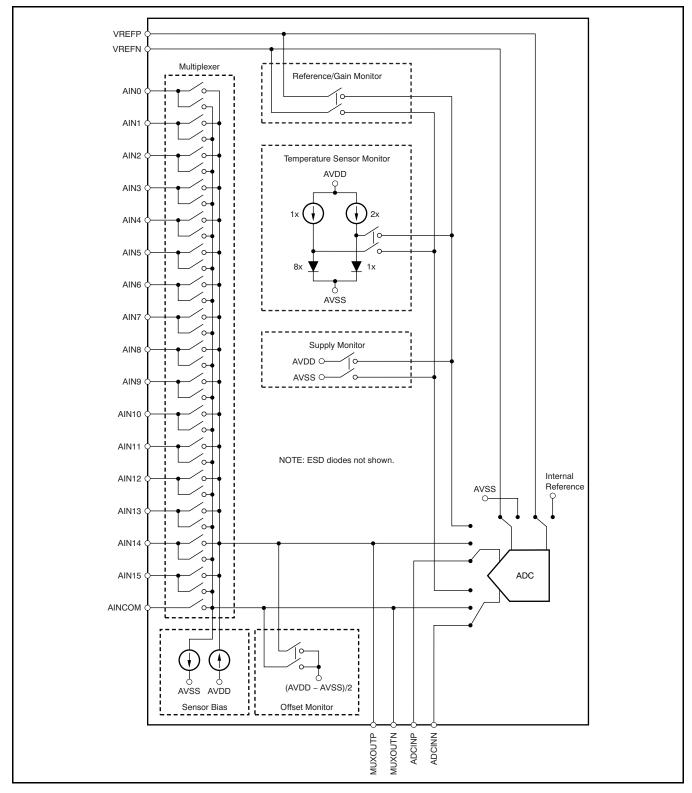

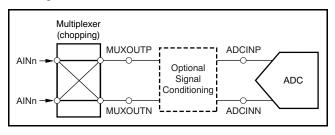

Figure 20 shows the block diagram of the ADS1158. The input multiplexer selects which analog input pins multiplexer connect to the output pins (MUXOUTP/MUXOUTN). External signal conditioning can be used between the multiplexer output pins and the ADC input pins (ADCINP/ADCINN) or the multiplexer output can be routed internally to the ADC inputs without external circuitry. Selectable current sources within the input multiplexer can be used to bias sensors or detect for a failed sensor. On-chip system function readings provide readback of temperature, supply voltage, gain, offset, and external reference.

The ADS1158 converter consists of a fourth-order, delta-sigma modulator followed by a programmable digital filter. The modulator measures the differential input signal,  $V_{IN} = (ADCINP - ADCINN)$ , against the differential reference input,  $V_{REF} = (VREFP - VREFN)$ . The digital filter receives the modulator signal and provides a low-noise digital output. The ADC channel block controls the multiplexer Auto-Scan feature. Channel Auto-Scan occurs at a maximum rate of 23.7kSPS. Slower scan rates can be used with corresponding increases in resolution.

Communication is handled over an SPI-compatible serial interface with a set of simple commands to control the ADS1158. Onboard registers store the various settings for the input multiplexer, sensor detect bias, data rate selection, etc. Either an external 32.768kHz crystal, connected to pins XTAL1 and XTAL2, or an external clock applied to pin CLKIO can be used as the clock source. When using the external crystal oscillator, the system clock is available as an output for driving other devices or controllers. General-purpose digital I/Os (GPIO) provide input and output control of eight pins.

Figure 20. ADS1158 Block Diagram

11

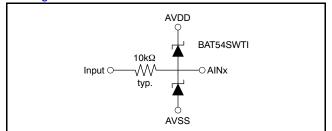

### MULTIPLEXER INPUTS

A simplified diagram of the input multiplexer is illustrated in Figure 22. The multiplexer connects one of 16 single-ended external inputs, one of eight differential external inputs, or one of the on-chip internal variables to the ADC inputs. The output of the channel multiplexer can be routed to external pins and then to the input of the ADC. This flexibility allows for use of external signal conditioning. See the *External Multiplexer Loop* section.

Electrostatic discharge (ESD) diodes protect the analog inputs. To keep these diodes from turning on, make sure the voltages on the input pins do not go below AVSS by more than 100mV, and likewise do not exceed AVDD by more than 100mV:

AVSS – 100mV < (Analog Inputs) < AVDD + 100mV.

Overdriving the multiplexer inputs may affect the conversions of other channels. See the *Input Overload Protection* description in the *Hardware Considerations* segment of the *Applications* section.

The converter supports two modes of channel access through the multiplexer: the Auto-Scan mode and the Fixed-Channel mode. These modes are selected by the MUXMOD bit of register CONFIGO. The Auto-Scan mode scans through the selected channels automatically, with break-before-make switching. The Fixed-Channel mode requires the user to set the channel address for each channel measured.

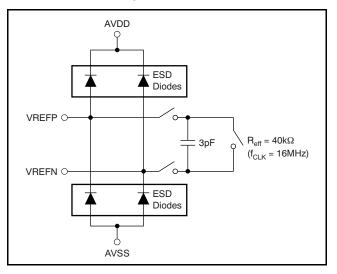

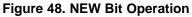

#### VOLTAGE REFERENCE INPUTS (VREFP, VREFN)

The voltage reference for the ADS1158 ADC is the differential voltage between VREFP and VREFN:  $V_{REF} = VREFP - VREFN$ . The reference inputs use a structure similar to that of the analog inputs with the circuitry on the reference inputs shown in Figure 21.

The load presented by the switched capacitor can be modeled with an effective resistance ( $R_{eff}$ ) of 40k $\Omega$  for  $f_{CLK}$  = 16MHz. Note that the effective impedance of the reference inputs loads an external reference with a non-zero source impedance.

Figure 21. Simplified Reference Input Circuit

ESD diodes protect the reference inputs. To keep these diodes from turning on, make sure the voltages on the reference pins do not go below AVSS by more than 100mV, and likewise do not exceed AVDD by 100mV:

AVSS – 100mV < (VREFP or VREFN) < AVDD + 100mV

A high-quality reference voltage is essential to achieve the best performance from the ADS1158. Noise and drift on the reference degrade overall system performance. It is especially critical that special care be given to the circuitry that generates the reference voltages and the layout when operating in the low-noise settings (that is, with low data rates) to prevent the voltage reference from limiting performance. See the *Reference Inputs* description in the *Hardware Considerations* segment of the *Applications* section.

TEXAS INSTRUMENTS

#### www.ti.com

SBAS429A-JUNE 2008-REVISED JUNE 2008

Figure 22. Input Multiplexer

13

# ADS1158

SBAS429A-JUNE 2008-REVISED JUNE 2008

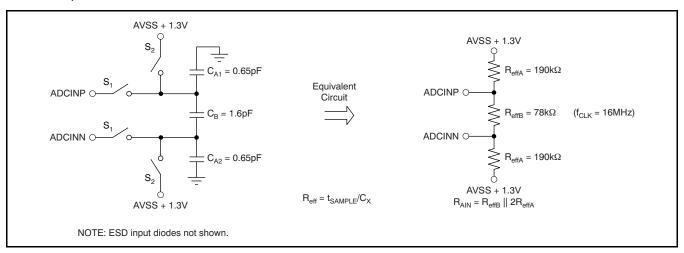

#### ADC INPUTS

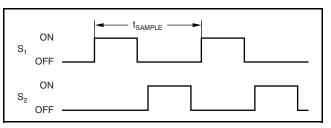

The ADS1158 ADC inputs (ADCINP, ADCINN) measure the input signal using internal capacitors that are continuously charged and discharged. The left side of Figure 24 shows a simplified schematic of the ADC input circuitry; the right side of Figure 24 shows the input circuitry with the capacitors and switches replaced by an equivalent circuit. Figure 23 shows the ON/OFF timings of the switches shown in Figure 24. S<sub>1</sub> switches close during the input sampling phase. With S<sub>1</sub> closed, C<sub>A1</sub> charges to ADCINP, C<sub>A2</sub> charges to ADCINN, and C<sub>B</sub> charges to (ADCINP – ADCINN). For the discharge phase, S<sub>1</sub> opens first and then S<sub>2</sub> closes. C<sub>A1</sub> and C<sub>A2</sub> discharge to approximately AVSS + 1.3V and C<sub>B</sub> discharges to OV. This two-phase sample/discharge cycle repeats with a period of t<sub>SAMPLE</sub> =  $2/f_{CLK}$ .

The charging of the input capacitors draws a transient current from the source driving the ADS1158 ADC inputs. The average value of this current can be used to calculate an effective impedance ( $R_{eff}$ ) where  $R_{eff} = V_{IN}/I_{AVERAGE}$ . These impedances scale inversely with  $f_{CLK}$ . For example, if  $f_{CLK}$  is reduced by a factor of two, the impedances will double.

As with the multiplexer and reference inputs, ESD diodes protect the ADC inputs. To keep these diodes from turning on, make sure the voltages on the input pins do not go below AVSS by more than 100mV, and likewise do not exceed AVDD by more than 100mV.

Figure 23. S<sub>1</sub> and S<sub>2</sub> Switch Timing for Figure 24

Figure 24. Simplified ADC Input Structure

# ADS1158

#### www.ti.com

# MASTER CLOCK (f<sub>CLK</sub>)

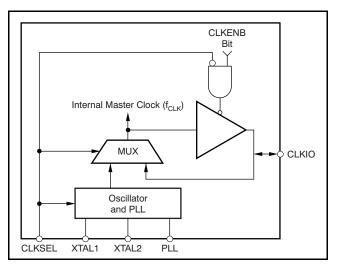

The ADS1158 oversamples the analog input at a high rate. This oversampling requires a high-frequency master clock to be supplied to the converter. As shown in Figure 25, the clock comes from either an internal oscillator (with external crystal), or an external clock source.

Figure 25. Clock Generation Block Diagram

The CLKSEL pin determines the source of the system clock, as shown in Table 1. The CLKIO pin functions as an input or as an output. When the CLKSEL pin is set to '1', CLKIO is configured as an input to receive the master clock. When the CLKSEL pin is set to '0', the crystal oscillator generates the clock. The CLKIO pin can then be configured to output the master clock. When the clock output is not needed, it can be disabled to reduce device power consumption.

# **Crystal Oscillator**

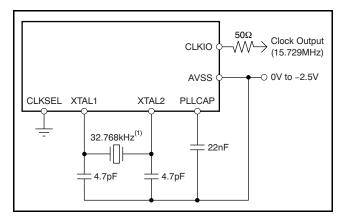

An on-chip oscillator and phase-locked loop (PLL) together with an external crystal can be used to generate the system clock. For this mode, tie the CLKSEL pin low. A 22nF PLL filter capacitor, connected from the PLLCAP pin to the AVSS pin, is required. The internal clock of the PLL can be output to the CLKIO to drive other converters or controllers. If not used, disable the clock output to reduce device power consumption; see Table 1 for settings. The clock output is enabled by a register bit setting (default is ON). Figure 26 shows the oscillator connections. Place these components as close to the pins as possible to avoid interference and coupling. Do not connect XTAL1 or XTAL2 to any other logic. The oscillator start-up time may vary, depending on the crystal and ambient temperature. The user should verify the oscillator start-up time.

SBAS429A-JUNE 2008-REVISED JUNE 2008

(1) Parallel resonant type.  $C_L$  = 12.5pF, ESR = 35k $\Omega$  (max). Place the crystal and load capacitors as close as possible to the device pins.

#### Figure 26. Crystal Oscillator Connection

#### Table 1. System Clock Source

| CLKSEL<br>PIN | CLOCK SOURCE                    | CLKENB<br>BIT | CLKIO FUNCTION                    |

|---------------|---------------------------------|---------------|-----------------------------------|

| 0             | 32.768kHz<br>crystal oscillator | 0             | Disabled<br>(internally grounded) |

| 0             | 32.768kHz<br>crystal oscillator | 1             | Output (15.729MHz)                |

| 1             | External clock input            | Х             | Input (16MHz)                     |

**Table 2. Approved Crystal Vendors**

| VENDOR | CRYSTAL PRODUCT |

|--------|-----------------|

| Epson  | C-001R          |

#### **External Clock Input**

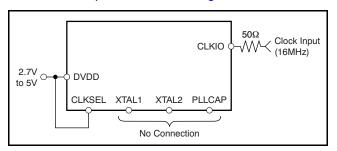

When using an external clock to operate the device, apply the master clock to the CLKIO pin. For this mode, the CLKSEL pin is tied high. CLKIO then becomes an input, as shown in Figure 27.

Figure 27. External Clock Connection

Make sure to use a clock source clean from jitter or interference. Ringing or under/overshoot should be avoided. A 50 $\Omega$  resistor in series with the CLKIO pin (placed close to the source) can often help.

## ADC

The ADC block of the ADS1158 is composed of two blocks: a modulator and a digital filter.

### Modulator

The modulator converts the analog input voltage into a pulse code modulated (PCM) data stream. When the level of differential analog input (ADCINP – ADCINN) is near the level of the reference voltage, the '1' density of the PCM data stream is at its highest. When the level of the differential analog input is near zero, the PCM '0' and '1' densities are nearly equal. The fourth-order modulator shifts the quantization noise to a high frequency (out of the passband) where the digital filter can easily remove it.

The modulator continuously chops the input, resulting in excellent offset and offset drift performance. It is important to note that offset or offset drift that originates from the external circuitry is not removed by the modulator chopping. These errors can be effectively removed by using the external chopping feature of the ADS1158 (see the *External Chopping* section).

# **Digital Filter**

The programmable low-pass digital filter receives the modulator output and produces a high-resolution digital output. By adjusting the amount of filtering, tradeoffs can be made between resolution and data rate—filter more for higher resolution, filter less for higher data rate. The filter consists of two sections, a fixed filter followed by a programmable filter.

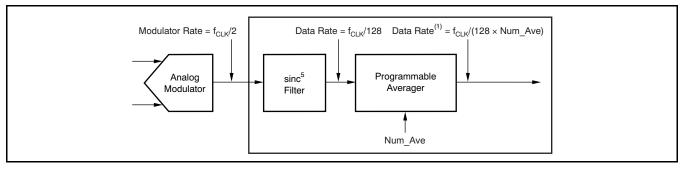

Figure 28 shows the block diagram of the filter. Data are supplied to the filter from the analog modulator at a rate of  $f_{CLK}/2$ . The fixed filter is a fifth-order sinc filter with a decimation value of 64 that outputs data at a rate of  $f_{CLK}/128$ . The second stage of the filter is a programmable averager (first-order sinc filter) with the number of averages set by the DRATE[1:0] bits.

The data rate depends upon the system clock frequency ( $f_{CLK}$ ) and the converter configuration. The data rate can be computed by Equation 1 or Equation 2:

Data rate (Auto-Scan):

$$\frac{f_{CLK}}{128(4^{11b-DR} + 4.26525 + TD) \times 2^{CHOP}}$$

(1)

Data rate (Fixed-Channel mode):

$$\frac{I_{CLK}}{128[4^{11b-DR} + CHOP(4.26525 + TD)] \times 2^{CHOP}}$$

(2)

Where:

DR = DRATE[1:0] register bits (binary).

CHOP = Chop register bit.

TD = time delay value given in Table 4 from the DLY[2:0] register bits  $(128/f_{CLK} \text{ periods})$ .

(1) Data rate for Fixed-Channel mode, Chop = 0, Delay = 0.

Figure 28. Block Diagram of Digital Filter

Table 3 shows a listing of the averaging and data rates for each of the four DRATE[1:0] register settings for the Auto-Scan and Fixed-Channel modes, with CHOP, DLY = 0. Note that the data rate scales directly with  $f_{CLK}$ . For example, reducing  $f_{CLK}$  by 2x reduces the maximum data rate by 2x.

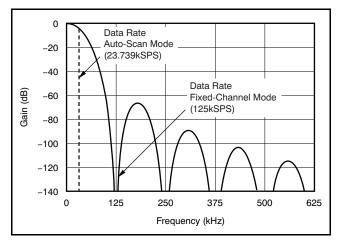

# FREQUENCY RESPONSE

The low-pass digital filter sets the overall frequency response for the ADS1158. The filter response is the product of the responses of the fixed and programmable filter sections and is given by Equation 3:

$$\begin{aligned} |\mathsf{H}_{(\mathsf{f})}| &= |\mathsf{H}_{\mathsf{sinc}}^{5}(\mathsf{f})| \times |\mathsf{H}_{\mathsf{Averager}}(\mathsf{f})| = \\ \\ \frac{\sin\left(\frac{128\pi \times \mathsf{f}}{\mathsf{f}_{\mathsf{CLK}}}\right)}{64 \times \sin\left(\frac{2\pi \times \mathsf{f}}{\mathsf{f}_{\mathsf{CLK}}}\right)} \begin{vmatrix} \mathsf{s} \\ \times \end{vmatrix} \frac{\sin\left(\frac{128\pi \times \mathsf{Num}_{\mathsf{Ave}} \times \mathsf{f}}{\mathsf{f}_{\mathsf{CLK}}}\right)}{\mathsf{Num}_{\mathsf{Ave}} \times \sin\left(\frac{128\pi \times \mathsf{f}}{\mathsf{f}_{\mathsf{CLK}}}\right)} \end{aligned}$$

The digital filter attenuates noise on the modulator output, including noise from within the ADS1158 and external noise present within the ADS1158 input signal. Adjusting the filtering by changing the number of averages used in the programmable filter changes the filter bandwidth. With a higher number of averages, the bandwidth is reduced and more noise is attenuated.

The low-pass filter has notches (or *zeros*) at the data output rate and multiples thereof. The sinc<sup>5</sup> part of the filter produces wide notches at  $f_{CLK}/128$  and multiples thereof. At these frequencies, the filter has zero gain. Figure 29 shows the response with no post averaging. Note that in Auto-Scan mode, the data rate is reduced while retaining the same frequency response as in Fixed-Channel mode.

With programmable averaging, the wide notches produced by the sinc<sup>5</sup> filter remain, but a number of narrow notches are superimposed in the response. The number of the superimposed notches is determined by the number of readings averaged (minus one).

#### SBAS429A-JUNE 2008-REVISED JUNE 2008

Figure 30 shows the response with averaging set to 4 (DRATE[1:0] = 10). 4-reading, post-averaging produces three equally-spaced notches between each main notch of the sinc<sup>5</sup> filter. The frequency response of DRATE[1:0] = 01 and 00 follows a similar pattern, but with 15 and 63 equally-spaced notches between the main sinc<sup>5</sup> notches, respectively.

Figure 29. Frequency Response, DRATE[1:0] = 11

Figure 30. Frequency Response, DRATE[1:0] = 10

| Table | 3. | Data | Rates <sup>(1)</sup> |

|-------|----|------|----------------------|

|-------|----|------|----------------------|

| DRATE[1:0] | Num_Ave <sup>(2)</sup> | DATA RATE AUTO-SCAN<br>MODE (SPS) <sup>(3)</sup> | DATA RATE FIXED-CHANNEL<br>MODE (SPS) | –3dB BANDWIDTH<br>(Hz) |

|------------|------------------------|--------------------------------------------------|---------------------------------------|------------------------|

| 11         | 1                      | 23739                                            | 125000                                | 25390                  |

| 10         | 4                      | 15123                                            | 31250                                 | 12402                  |

| 01         | 16                     | 6168                                             | 7813                                  | 3418                   |

| 00         | 64                     | 1831                                             | 1953                                  | 869                    |

(1)  $f_{CLK} = 16MHz$ , Chop = 0, and Delay = 0.

(2) Num\_Ave is the number of averages performed by the digital filter second stage.

(3) In Auto-Scan mode, the data rate listed is for a single channel; the effective data rate for multiple channels (on a per-channel basis) is the value shown in Figure 29 and Figure 30 divided by the number of active channels in a scan loop.

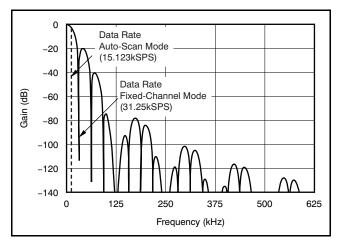

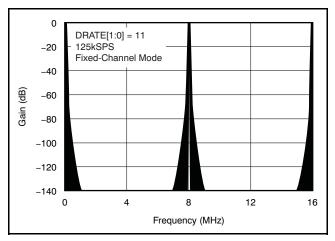

### ALIASING

The digital filter low-pass characteristic repeats at multiples of the modulator rate of  $f_{CLK}/2$ . Figure 31 shows the response plotted out to 16MHz at the data rate of 125kSPS (Fixed-Channel mode). Notice how the responses near dc, 8MHz, and 16MHz are the same. The digital filter attenuates high-frequency noise on the ADS1158 inputs up to the frequency where the response repeats. However, noise or frequency components present on the analog input where the response repeats alias into the passband. For most applications, an anti-alias filter is recommended to remove this noise. A simple first-order input filter with a pole at 200kHz provides –34dB rejection at the first image frequency.

Figure 31. Frequency Response Out to 16MHz

Referring to Figure 29 and Figure 30, frequencies present on the analog input above the Nyquist rate (sample rate/2) are first attenuated by the digital filter and then aliased into the passband.

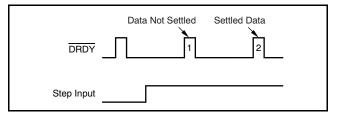

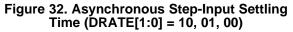

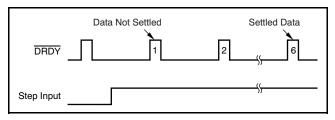

#### SETTLING TIME

The design of the ADS1158 provides fully-settled data when scanning through the input channels in Auto-Scan mode. The DRDY flag asserts low when the data for each channel are ready. It may be necessary to use the automatic switch time delay feature to provide time for settling of the external buffer and associated components after channel switching. When the converter is started (START pin transitions high or Start Command) with stable inputs,

the first converter output is fully settled. When applying asynchronous step inputs, the settling time is somewhat different. The step-input settling time diagrams (Figure 32 and Figure 33) show the converter step response with an asynchronous step input. For most modes of operation, the analog input must be stable for one complete conversion cycle to provide settled data. In Fixed-Channel mode (DRATE[1:0] = 11), the input must be stable for five complete conversion cycles.

| Table 4. Effective Data Rates with Switch-Time |

|------------------------------------------------|

| Delay (Auto-Scan Mode) <sup>(1)</sup>          |

| DLY<br>[2:0] | TIME<br>DELAY<br>(128/f <sub>CLK</sub><br>periods) | TIME<br>DELAY<br>(μS) | DRATE<br>[1:0] =<br>11 | DRATE<br>[1:0] =<br>10 | DRATE<br>[1:0] =<br>01 | DRATE<br>[1:0] =<br>00 |

|--------------|----------------------------------------------------|-----------------------|------------------------|------------------------|------------------------|------------------------|

| 000          | 0                                                  | 0                     | 23739                  | 15123                  | 6168                   | 1831                   |

| 001          | 1                                                  | 8                     | 19950                  | 13491                  | 5878                   | 1805                   |

| 010          | 2                                                  | 16                    | 17204                  | 12177                  | 5614                   | 1779                   |

| 011          | 4                                                  | 32                    | 13491                  | 10191                  | 5151                   | 1730                   |

| 100          | 8                                                  | 64                    | 9423                   | 7685                   | 4422                   | 1639                   |

| 101          | 16                                                 | 128                   | 5878                   | 5151                   | 3447                   | 1483                   |

| 110          | 32                                                 | 256                   | 3354                   | 3104                   | 2392                   | 1247                   |

| 111          | 48                                                 | 384                   | 2347                   | 2222                   | 1831                   | 1075                   |

<sup>(1)</sup> Time delay and data rates scale with  $f_{CLK}$ . If Chop = 1, the data rates are half those shown.  $f_{CLK}$  = 16MHz, Auto-Scan mode.

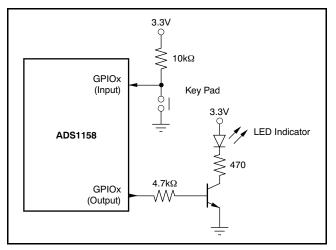

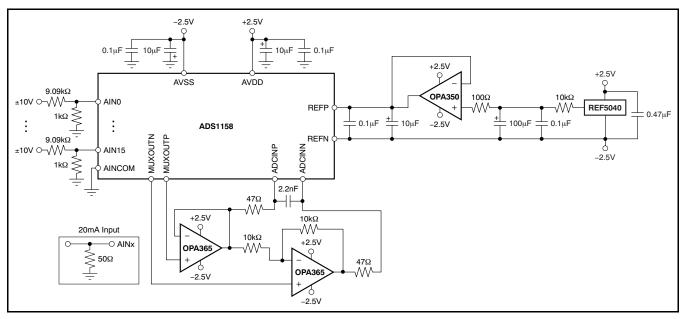

#### EXTERNAL MULTIPLEXER LOOP

The external multiplexer loop consists of two differential multiplexer output pins and two differential ADC input pins. The user may use external components (buffering/filtering, single-ended to differential conversion, etc.) to form a signal conditioning loop. For best performance, the ADC input should be buffered and driven differentially.

To bypass the external multiplexer loop, connect the ADC input pins directly to the multiplexer output pins, or select internal bypass connection (BYPASS = 0 of CONFIGO). Note that the multiplexer output pins are active regardless of the bypass setting.

#### SWITCH TIME DELAY

When using the ADS1158 in the Auto-Scan mode, where the converter automatically switches from one channel to the next, the settling time of the external signal conditioning circuit becomes important. If the channel does not fully settle after the multiplexer channel is switched, the data may not be correct. The ADS1158 provides a switch time delay feature which automatically provides a delay after channel switching to allow the channel to settle before taking a reading. The amount of time delay required depends primarily on the settling time of the external signal conditioning. Additional consideration may be needed to account for the settling of the input source arising from the transient generated from channel switching. Use of the switch time delay register reduces the effective channel data rate. Table 4 shows the actual data rates derived from Equation 1, when using the switch time delay feature.

When pulse converting, where one channel is converted with each START pin pulse or each pulse command, the application software may provide the required time delay between pulses. However, with Chop = 1, the switch time delay feature may continue to be necessary to allow for settling.

In estimating the time delay that may be required, Table 5 lists the time delay-to-time constant ratio  $(t/\tau)$  and the corresponding final settled data in % and number of bits.

|                    | •                     |                          |  |  |  |

|--------------------|-----------------------|--------------------------|--|--|--|

| t/τ <sup>(1)</sup> | FINAL SETTLING<br>(%) | FINAL SETTLING<br>(Bits) |  |  |  |

| 1                  | 63                    | 2                        |  |  |  |

| 3                  | 95                    | 5                        |  |  |  |

| 5                  | 99.3                  | 7                        |  |  |  |

| 7                  | 99.9                  | 10                       |  |  |  |

| 10                 | 99.995                | 14                       |  |  |  |

| 15                 | 99.998                | 16                       |  |  |  |

|                    |                       |                          |  |  |  |

Table 5. Settling Time

(1) Multiple time constants can be approximated by:  $(\tau_1^2 + \tau_2^2 + ...)^=$ .

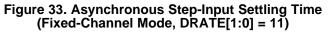

### **SENSOR BIAS**

An integrated current source provides a means to bias an external sensor (for example, a diode junction); or, it verifies the integrity of a sensor or sensor connection. When the sensor fails to an open condition, the current sources drive the inputs of the converter to positive full-scale. The biasing is in the form of differential currents (programmable  $1.5\mu A$  or  $24\mu A$ ), connected to the output of the multiplexer.

Figure 34 shows a simplified diagram of ADS1158 input structure with the external sensor modeled as a resistance  $R_{\text{S}}$  between two input pins. The two  $80\Omega$ series resistors, R<sub>MUX</sub>, model the ADS1158 internal resistances. R<sub>I</sub> represents the effective input resistance of the ADC input or external buffer. When the sensor bias is enabled, they source I<sub>SDC</sub> to one selected input pin (connected to the MUXOUTP channel) and sink ISDC from the other selected input pin (connected to the MUXOUTN channel). The signal measured with the biasing enabled equals the total IR drop:  $I_{SDC}[(2R_{MUX} + R_S) \parallel R_L]$ . Note that when the sensor is a direct short (that is,  $R_S = 0$ ), there continues to be a small signal measured by the ADS1158 when the biasing is enabled: ISDC[2R<sub>MUX</sub> II  $R_L$ ].

Figure 34. Sensor Bias Structure

The current source is connected to the output of the multiplexer. For unselected channels, the current source is not connected. This configuration means that when a new channel is selected, the current source charges stray sensor capacitance, which may slow the rise of the sensor voltage. The automatic switch time delay feature can be used to apply an appropriate time delay before a conversion is started to provide fully settled data (see the *Switch Time Delay* section).

The time to charge the external capacitance is given in Equation 4:

$$\frac{dV}{dt} = \frac{I_{SDC}}{C}$$

(4)

It is also important to note that the low impedance  $(65k\Omega)$  of the direct ADC inputs or the impedance of the external signal conditioning loads the current sources. This low impedance limits the ability of the current source to pull the inputs to positive full-scale for open-channel detection.

# **OPEN-SENSOR DETECTION**

For open-sensor detection, set the biasing to either  $1.5\mu$ A or  $24\mu$ A. Then select the channel and read the output code. When a sensor opens, the positive input is pulled to AVDD and the negative input is pulled to AVSS. Because of this configuration, the output code trends toward positive full-scale. Note that the interaction of the multiplexer resistance with the current source may lead to degradation in converter linearity. It is recommended to enable the current source only periodically to check for open inputs and discard the associated data.

# **EXTERNAL DIODE BIASING**

The current source can be used to bias external diodes for temperature sensing. Scan the appropriate channels with the current source set to  $24\mu$ A. Re-scan the same channels with the current source set to  $1.5\mu$ A. The difference in diode voltage readings resulting from the two bias currents is directly proportional to temperature.

Note that errors in current ratio, diode and cable resistance, or the non-ideality factor of the diode can lead to errors in temperature readings. These effects can be compensated by characterization or by calibrating the diode at known temperatures.

#### **EXTERNAL CHOPPING**

The modulator of the ADS1158 incorporates a chopping front-end that removes offset errors to provide excellent offset and offset drift performance. However, offset and offset drift that originate from external signal conditioning are not removed by the modulator. The ADS1158 has an additional chopping feature that removes external offset errors (CHOP = 1).

With external chopping enabled, the converter takes two readings in succession on the same channel. The first reading is taken with one polarity and the second reading is taken with the opposite polarity. The converter averages the two readings and cancels the offset, as shown in Figure 35. With chopping enabled, the effective reading reduces to half of the nominal reading rate.

Figure 35. External Chopping

Note that because the inputs are reversed under control of the ADS1158, a delay time may be necessary to provide time for external signal conditioning to fully settle before the second phase of the reading sequence starts (see the *Switch Time Delay* section).

External chopping can be used to reduce total offset errors and offset drift over temperature. Note that chopping must be disabled (CHOP = 0) in order to take the internal monitor readings.

SBAS429A-JUNE 2008-REVISED JUNE 2008

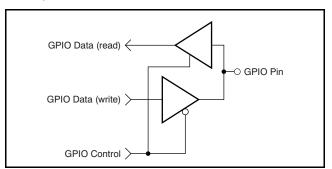

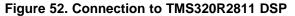

## **GPIO DIGITAL PORT (GPIOx)**

The ADS1158 has eight dedicated general-purpose digital input/output (GPIO) pins. The digital I/O pins are individually configurable as either inputs or as outputs through the GPIOC (GPIO-Configure) register. The GPIOD (GPIO-Data) register controls the level of the pins. When reading the GPIOD register, the data returned are the level of the pins, whether they are programmed as inputs or outputs. As inputs, a write to the GPIOD has no effect. As outputs, a write to the GPIOD sets the output value.

During Standby and Power-Down modes, the GPIO remains active. If configured as inputs, these pins must be driven (do not float). If configured as outputs, the pins are driven. The GPIO pins are set as inputs after power-on or after a reset. Figure 36 shows the GPIO port structure.

Figure 36. GPIO Port Pin

## POWER-DOWN INPUT (PWDN)

The PWDN pin controls the power-down mode of the converter. In power-down mode, all internal circuitry is deactivated including the oscillator and the clock output. Hold PWDN low for at least two f<sub>CLK</sub> cycles to engage power-down. The register settings are retained during power-down. When the pin is returned high, the converter requires a wake-up time before readings can be taken, as shown in the *Power-Up Timing* section. Note that in power-down mode, the inputs of the ADS1158 must continue to be driven and the device continues to drive the outputs.

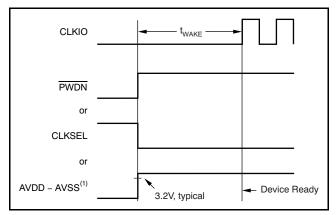

#### **POWER-UP TIMING**

When powering up the device or taking the  $\overline{PWDN}$  pin high to wake the device, a wake-up time is required before readings can be taken. When using the internal oscillator, the wake-up time is composed of the oscillator start-up time and the PLL lock time, and if the supplies are also being powered, there is a reset interval time of  $2^{18}$  f<sub>CLK</sub> cycles. Note that CLKIO is not valid during the wake-up period, as shown in Figure 37.

(1) Shown with DVDD stable.

#### Figure 37. Device Wake Time with Internal Oscillator

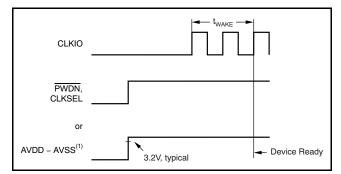

When using the device with an external clock, the wake-up time is  $2/f_{CLK}$  periods when waking up with the PWDN pin and  $2^{18}/f_{CLK}$  periods when powering the supplies, all after a valid CLKIO is applied, as shown in Figure 38.

(1) Shown with DVDD stable.

#### Figure 38. Device Wake Time with External Clock

Table 6summarizes the wake-up times using theinternal oscillator and the external clock operations.

www.ti.com

### Table 6. Wake-Up Times

| CONDITION      | t <sub>WAKE</sub><br>INTERNAL<br>OSCILLATOR <sup>(1)</sup> | t <sub>WAKE</sub><br>EXTERNAL CLOCK |  |  |

|----------------|------------------------------------------------------------|-------------------------------------|--|--|

| PWDN or CLKSEL | t <sub>OSC</sub>                                           | 2/f <sub>CLK</sub>                  |  |  |

| AVDD – AVSS    | t <sub>OSC</sub> + 2 <sup>18</sup> /f <sub>CLK</sub>       | 2 <sup>18</sup> /f <sub>CLK</sub>   |  |  |

(1) Wake-up times for the internal oscillator operation are typical and may vary depending on crystal characteristics and layout capacitance. The user should verify the oscillator start-up times (t<sub>OSC</sub> = oscillator start-up time).

### **POWER-UP SEQUENCE**

The analog and digital supplies should be applied before any analog or digital input is driven. The power supplies may be sequenced in any order. The internal master reset signal is generated from the analog power supply (AVDD – AVSS), when the level reaches approximately 3.2V. The power-up master reset signal is functionally the same as the Reset Command and the RESET input pin.

### Reset Input (RESET)

When  $\overrightarrow{\text{RESET}}$  is held low for at least two  $f_{\text{CLK}}$  cycles, all registers are reset to their default values and the digital filter is cleared. When  $\overrightarrow{\text{RESET}}$  is released high, the device is ready to convert data.

#### Clock Select Input (CLKSEL)

This pin selects the source of the system clock: the crystal oscillator or an external clock. Tie CLKSEL low to select the crystal oscillator. When using an external clock (applied to the CLKIO pin), tie CLKSEL high.

#### **Clock Input/Output (CLKIO)**

This pin serves either as a clock output or clock input, depending on the state of the CLKSEL pin. When using an external clock, apply the clock to this pin and set the CLKSEL pin high. When using the internal oscillator, this pin has the option of providing a clock output. The CLKENB bit of register CONFIGO enables the clock output (default is enabled).

#### Start Input (START)

The START pin is an input that controls the ADC process. When the START pin is taken high, the converter starts converting the selected input channels. When the START pin is taken low, the conversion in progress runs to completion and the converter is stopped. The device then enters one of the two idle modes (see the *Idle Modes* section for more details). See the *Conversion Control* section for details of using the START pin.

#### Data Ready Output (DRDY)

The DRDY pin is an output that asserts low to indicate when new channel data are available to read (the previous conversion data are lost). DRDY returns high after the first falling edge of SCLK during a data read operation. If the data are not read (no SCLK pulses), DRDY remains low until new channel data are available once again. DRDY then pulses high, then low to indicate new data are available; see Figure 39.

### Figure 39. DRDY Timing (See Figure 2 for the DRDY Pulse)

#### SBAS429A-JUNE 2008-REVISED JUNE 2008

DRDY is usually connected to an interrupt of a controller, DSP, or connected to a controller port pin for polling in a software loop. Channel data can be read without the use of DRDY. Read the data using the register format read and check the Status Byte when the NEW bit = 1, which indicates new channel data.

#### **Output Data Scaling and Over-Range**

The ADS1158 is scaled such that the output data code resulting from an input voltage equal to  $\pm V_{REF}$  has a margin of 6.6% before clipping. This architecture allows operation of applied input signals at or near full-scale without overloading the converter.

Specifically, the device is calibrated so that:

$1LSB = V_{REF}/7800h$ ,

and the output clips when:

$|V_{IN}| \ge 1.0\overline{6} \times V_{REF}$ .

Table 7 summarizes the ideal output codes versusinput signals.

| INPUT SIGNAL V <sub>IN</sub><br>(ADCINP – ADCINN)                 | IDEAL OUTPUT CODE <sup>(1)</sup> | DESCRIPTION                                        |

|-------------------------------------------------------------------|----------------------------------|----------------------------------------------------|

| ≥ +1.06 V <sub>REF</sub>                                          | 7FFFh                            | Maximum positive full-scale before output clipping |

| +V <sub>REF</sub>                                                 | 7800h                            | $V_{IN} = +V_{REF}$                                |

| +1.06 V <sub>REF</sub> /(2 <sup>15</sup> -1)                      | 0001h                            | +1LSB                                              |

| 0                                                                 | 0000h                            | Bipolar Zero                                       |

| -1.06 V <sub>REF</sub> /(2 <sup>15</sup> - 1)                     | FFFFh                            | -1LSB                                              |

| -V <sub>REF</sub>                                                 | 87FFh                            | $V_{IN} = -V_{REF}$                                |

| $\leq -1.0\overline{6} V_{\text{REF}} \times (2^{15}/2^{15} - 1)$ | 8000h                            | Maximum negative full-scale before output clipping |

#### Table 7. Ideal Output Code versus Input Signal

(1) Ideal output code –0.5LSB excludes effects of noise, linearity, offset, and gain errors.

23

#### INTERNAL SYSTEM READINGS

#### Analog Power-Supply Reading (VCC)

The analog power-supply voltage of the ADS1158 can be monitored by reading the VCC register. The supply voltage is routed internal to the ADS1158 and is measured and scaled using an internal reference. The supply readback channel outputs the difference between AVDD and AVSS (AVDD – AVSS), for both single and dual configurations. Note that it is required to disable chopping (CHOP = 0) before taking this reading.

The scale factor of Equation 5 converts the code value to volts:

Total Analog Supply Voltage (V) =

$$\frac{\text{Code}}{12 \text{ (0Ch)}}$$

(5)

When the power supply falls below the minimum specified operating voltage, the full operation of the ADS1158 cannot be ensured. Note that when the total analog supply voltage falls to below approximately 4.3V, the returned data are set to zero. The SUPPLY bit in the status byte is then set. The bit clears when the total supply voltage rises approximately 50mV higher than the lower trip point.

The digital supply (DVDD) may be monitored by looping-back the supply voltage to an input channel. A resistor divider may be required for bipolar supply operation to reduce the DVDD level to within the range of the analog supply.

# Gain Reading (GAIN)

In this configuration, the external reference is connected both to the analog input and to the reference input of the ADC. The data from this register indicate the gain of the device.

The following scale factor (Equation 6) converts the code value to device gain:

Device Gain (V/V) =

$$\frac{\text{Code}}{120 (78h)}$$

(6)

To correct the device gain error, the user software can divide each converter data value by the device gain. Note that this corrects only for gain errors originating within the ADC; system gain errors that occur because of an external gain stage error or because of reference errors are not compensated. Note that it is also required to disable chopping (CHOP = 0) before taking this reading.

# Reference Reading (REF)

In this configuration, the external reference is connected to the analog input and an internal reference is connected to the reference of the ADC. The data from this register indicate the magnitude of the external reference voltage.

The scale factor of Equation 7 converts the code value to external reference voltage:

External Reference (V) =  $\frac{\text{Code}}{12 \text{ (0Ch)}}$  (7)

This readback function can be used to check for missing or an out-of-range reference. If the reference input pins are floating (not connected), internal biasing pulls them to the AVSS supply. This pull causes the output code to tend toward '0'. Bypass capacitors connected to the external reference pins may slow the response of the pins when open. When reading this register immediately after power-on, verify that the reference has settled to ensure an accurate reading. Note that it is required to disable chopping (CHOP = 0) before taking this reading.

### Temperature Reading (TEMP)

The ADS1158 contains an on-chip temperature sensor. This sensor uses two internal diodes with one diode having a current density of 16x of the other. The difference in current densities of the diodes yields a difference voltage that is proportional to absolute temperature.

As a result of the low thermal resistance of the package to the printed circuit board (PCB), the internal device temperature tracks the PCB temperature closely. Note also that self-heating of the ADS1158 causes a higher reading than the temperature of the surrounding PCB. Note that it is required to disable chopping (CHOP = 0) before taking this reading.

The scale factor of Equation 8 converts the temperature reading to °C. Before using the equation, the temperature reading code must first be scaled to microvolts.

Temperature (°C) =

$$\left(\frac{\text{Temp Reading}(\mu V) - 168,000\mu V}{394\mu V/^{\circ}C}\right)$$

(8)

# Offset Reading (OFFSET)

The differential output of the multiplexer is shorted together and set to a common-mode voltage of (AVDD – AVSS)/2. Ideally, the code from this register function is 0h, but varies because of the noise of the ADC and offsets stemming from the ADC and external signal conditioning. This register can be used to calibrate or track the offset of the ADS1158 and external signal conditioning. The chop feature of the ADC can automatically remove offset and offset drift from the external signal conditioning; see the *External Chopping* section.

### **CONVERSION CONTROL**

The conversions of the ADS1158 are controlled by the START pin. Conversions begin when the START pin is taken high and conversions are stopped when the START pin is taken low. For continuous conversions, tie the START pin high. The START pin can also be tied low and the conversions controlled by the PULSE convert command. The PULSE convert command converts one channel (only) for each command sent. In this way, channel conversions can be stepped without the need to toggle the START pin.

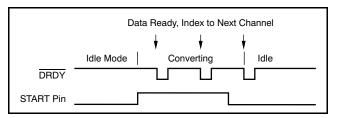

#### **START Pin**

As shown in Figure 40, when the START pin is taken high, conversions start beginning with the current channel. The device continues to convert all of the programmed channels, in a continuous loop, until the START pin is taken low. When this occurs, the conversion in process completes, and the device enters the standby or sleep mode and waits for a new start condition. When DRDY asserts low, the conversion data are ready. Figure 42 shows the START pin to DRDY timing. The order in which channel data are converted is described in Table 9. When the last selected channel in the program list the has been converted, device continues conversions starting with the highest priority channel. If there is only one channel selected in the Auto-Scan mode, the converter remains fixed on one channel. A write operation to any of the multiplexer channel select registers sets the channel pointer to the highest priority channel (see Table 10). In Fixed-Channel mode, the channel pointer remains fixed.

Figure 40. Conversion Control, Auto-Scan Mode

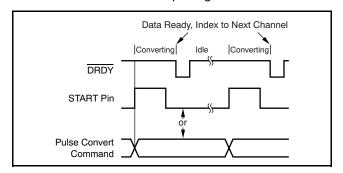

#### **Pulse Convert Command**

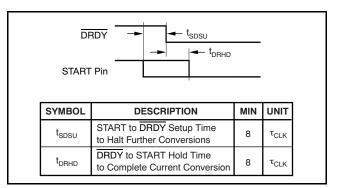

Figure 41 also shows the start of conversions with the rising edge of the START pin. If the START pin is taken high, and then low before completion of the conversion cycle (8  $\tau_{CLK}$  before DRDY asserts low), only the current channel is converted and the device enters the standby or sleep modes and waits for a new start condition. Figure 42 shows the START pin to DRDY timing. The same function of conversion control is possible using the Pulse Convert command (with the START pin low). In this operation, the data from one channel are converted with each Pulse Convert command. The Pulse convert command takes effect when the command byte is completely shifted in (eighth falling edge of SCLK). After conversion, if more than one channel is enabled (Auto-Scan mode), the converter indexes to the next selected channel after completing the conversion.

Figure 41. Pulse Conversion, Auto-Scan Mode

Figure 42. START Pin and DRDY Timing

25

#### **GPIO Linked START Pin Control**

The START pin can be controlled directly by software by connecting externally a GPIO port pin to the START pin. (Note that an external pull-down resistor is recommended to keep the GPIO from floating until the GPIO is configured as an output). For this mode of control, the START pin is effectively controlled by writing to the GPIO Data Register (GPIOD), with the write operation setting or resetting the appropriate bit. The data takes effect on the eighth falling edge of the data byte write. The START pin can then be controlled by the serial interface.

#### **Initial Delay**

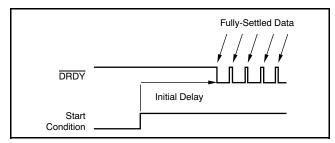

As seen in Figure 43, when a start convert condition occurs, the first reading from ADS1158 is delayed for a number of clock cycles. This delay allows fully settled data to occur at the first data read. Data reads thereafter are available at the full data rate. The number of clock cycles delayed before the first reading is valid depends on the data rate setting, and whether exiting the Standby or Sleep mode. Table 8 lists the delayed clock cycles versus data rate.

Figure 43. Start Condition to First Data

# **OPERATING MODES**

The operating modes of the ADS1158 are defined in three basic states: Converting mode, Idle mode, and

TEXAS INSTRUMENTS

Power-Down mode. In Converting mode, the device is actively converting channel data. The device power dissipation is the highest in this mode. This mode is divided into two sub-modes: Auto-Scan and Fixed-Channel.

The next mode is the Idle mode. In this mode, the device is not converting channel data. The device remains active, waiting for input to start conversions. The power consumption is reduced from that of the Converting mode. This mode also has two sub-modes: Standby and Sleep.

The last mode is Power-Down mode. In this mode, all functions of the converter are disabled to reduce power consumption to a minimum.

#### **CONVERTING MODES**