# 1 GSPS Quadrature Digital Upconverter w/18-Bit IQ Data Path and 14-Bit DAC

### PRELIMINARY TECHNICAL DATA

AD9957

#### **FEATURES**

1GSPS internal clock speed (up to 400MHz analog out) **Integrated 1GSPS 14-bit DAC** 250 MHz I/Q data throughput rate Phase noise ≤ -123 dBc/Hz (400 MHz carrier) Excellent dynamic performance >80 dB narrowband SFDR 8 Programmable Profiles for shift keying SIN(X)/(X) Correction (Inverse SINC filter) **Reference Clock Multiplier** Internal oscillator for a single crystal operation Software and hardware controlled power-down Integrated RAM Phase modulation capability **Multichip synchronization** Easy interface to Blackfin™ SPORT Interpolation factors from 4x to 252x **Test tone circuitry** Interpolation DAC Mode

#### **APPLICATIONS**

**Gain control DAC**

1.8V & 3.3V Power Supplies

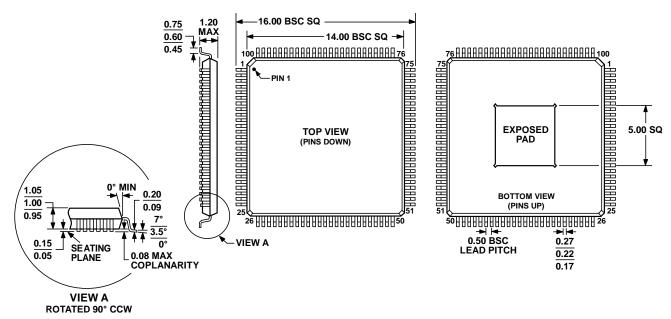

100 Lead TQFP package

HFC Data, Telephony & Video Modems

Wireless Base Station Transmission

Broadband Communications Transmissions

Internet Telephony

Internal divider allows references up to 2 GHz

#### **GENERAL DESCRIPTION**

The AD9957 functions as a universal I/Q modulator and agile upconverter for communications systems where cost, size, power consumption and dynamic performance are critical. The AD9957 integrates a high speed Direct Digital Synthesizer (DDS), a high performance, high speed 14-bit digital to analog converter (DAC), clock multiplier circuitry, digital filters and other DSP functions onto a single chip. It provides for base band up-conversion for data transmission in a wired or wireless communications system.

The AD9957 is the third offering in a family of a quadrature digital upconverters (QDUCs), which includes the AD9857 and AD9856. It offers performance gains in operating speed, power consumption and spectral performance. Unlike its predecessors, it also supports a 16-bit serial input mode for I/Q base band data. The device can alternatively be programmed to operate as a single-tone sinusoidal source or as an interpolating DAC.

The Reference Clock input circuitry includes a crystal oscillator, a high speed divide-by-two input, and a low noise PLL for multiplication of the reference clock frequency.

The user interface to the control functions includes a serial port easily configured to interface to the SPORT of the Blackfin DSP and profile pins which enable fast and easy shift keying of any signal parameter (phase, frequency, and amplitude).

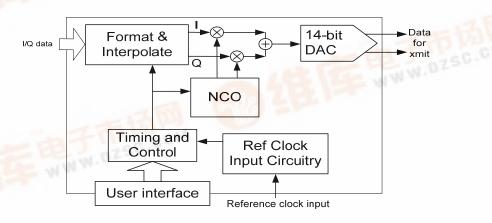

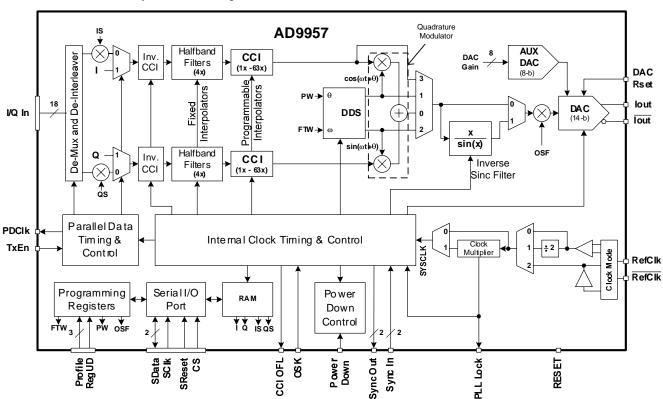

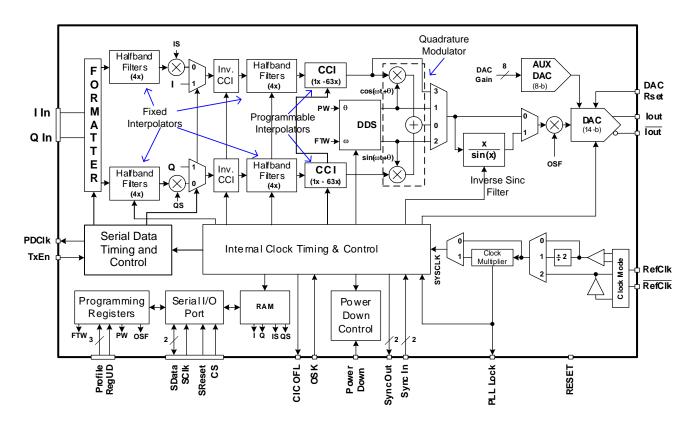

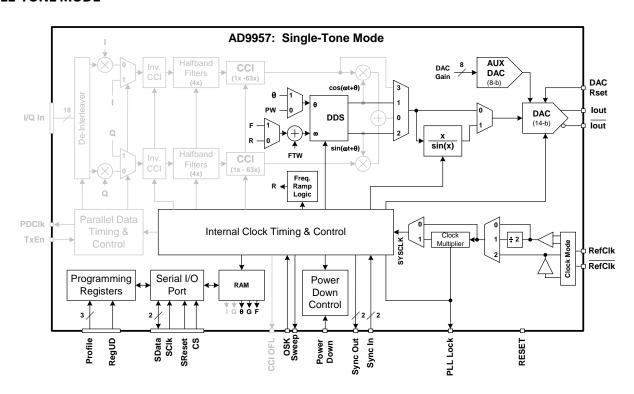

Figure 1: Basic Block Diagram

#### TABLE OF CONTENTS

| Electrical Specifications3                                                                                        | REFCLK: External Interface                                                     | 1               |

|-------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|-----------------|

| Absolute Maximum Ratings6                                                                                         | Serial Programming                                                             | 2               |

| Pin Configuration7                                                                                                | Control Interface—Serial I/O                                                   | 2               |

| Pin Description 8                                                                                                 | General Operation of the Serial Interface                                      | 2               |

| Modes of Operation10                                                                                              | Instruction Byte                                                               | 2               |

| Quadrature Modulation Mode10                                                                                      | Serial Interface Port Pin Description                                          | 2               |

| BlackFin Interface Mode 10                                                                                        | MSB/LSB Transfers                                                              | 2               |

| Signal Processing (QDUC & BFI modes)11                                                                            | RAM IO via Serial Port                                                         | 2               |

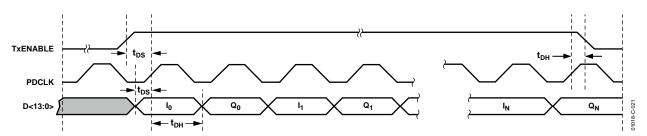

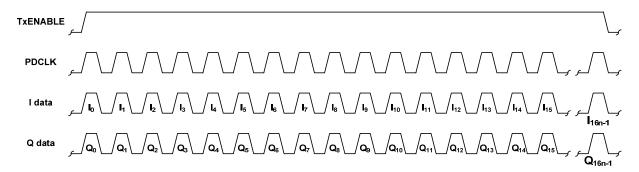

| PDCLK Pin11                                                                                                       | RAm control Modes                                                              | 2               |

| TxEnable Pin                                                                                                      | BAseband input scaling with RAM                                                | 2               |

| Inverse CCI Filter                                                                                                | I and q input data from ram                                                    |                 |

| Programmable Interpolating Filter14                                                                               | Register Map and Descriptions                                                  | 2               |

| Quadrature Modulator15DDS Core15                                                                                  | REGISTER MAP                                                                   | 2               |

| Inverse SINC Filter15Output Scale Factor (OSF)1514-Bit DAC15Auxiliary DAC16                                       | REGISTER DESCRIPTIONS                                                          | 3               |

| Interpolating DAC Mode16                                                                                          | Auxilliary DAC Control Register                                                | 3               |

| Single-Tone Mode         17           Amplitude Scale Factor (ASF)         17           I/O_UPDATE Pin         17 | IO Update Rate Register                                                        | R1)3<br>np Rate |

| REFCLK Input 19                                                                                                   | Frequency Tuning Word Register (FTW)Phase Offset Word Register (POW)           | 3               |

| REFCLK PLL 19                                                                                                     | Amplitude Scale Factor (ASF)                                                   | 3               |

| REFCLK PLL with Crystal19                                                                                         | QDUC Profile X Register (QDUC-PXR)/<br>Single Tone Profile X Register (ST-PXR) |                 |

#### **REVISION HISTORY**

Revision PrA (5/25/05): Initial Version of Preliminary Datasheet

Revision PrB (9/30/05): Register map, pinout, pin description added

Revision PrC (12/06/05): Register map completed, pinout updated.

Revision PrD (2/27/06) Further progress

Revision PrE (3/31/06) Incorporated Marketing review comments

### **ELECTRICAL SPECIFICATIONS**

Table 1. Unless otherwise noted, AVDD, DVDD = 1.8V  $\pm$  5%, DAC\_VDD, DVDD\_I/O = 3.3 V  $\pm$  5%, R<sub>SET</sub> = 10k $\Omega$ , External Reference Clock Frequency = 25 MHz. 40x REFLCK multiplier engaged.

| <u> </u>                                                      |       |      |        |             |

|---------------------------------------------------------------|-------|------|--------|-------------|

| Parameter                                                     | Min   | Тур  | Max    | Unit        |

| REF CLOCK INPUT CHARACTERISTICS                               |       |      |        |             |

| Frequency Range                                               |       |      |        |             |

| REFCLK Multiplier Disabled, Divider Disabled                  | 1     |      | 1000   | MHz         |

| REFCLK Multiplier Disabled, Divider Enabled                   |       |      | 2000   | MHz         |

| REFCLK Multiplier Enabled at 8×                               | 52.5  |      | 125    | MHz         |

| REFCLK Multiplier Enabled at 64×                              | 6.5   |      | 35     | MHz         |

| REFCLK Multiplier Enabled at 127×                             | 3.3   |      | 7.9    | MHz         |

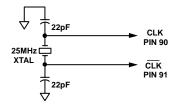

| XTAL frequency on REFCLK inputs                               | 20    |      | 30     | MHz         |

| Input Capacitance                                             |       | 3    |        | pF          |

| Input Impedance                                               |       | 1.5  |        | kΩ          |

| Duty Cycle                                                    |       | 50   |        | %           |

| Duty Cycle with REFCLK Multiplier Enabled                     | 35    |      | 65     | %           |

| REFCLK Input Voltage Swing                                    | 100   |      | 1000   | mV pk-pk    |

| REFCLK Input Power <sup>1</sup>                               | -15   | 0    | +3     | dBm         |

| DAC OUTPUT CHARACTERISTICS                                    | 1-2   |      | -      |             |

| Full Scale Output Current                                     | 10    | 20   | 30     | mA          |

| Gain Error                                                    | -10   | 20   | +10    | %FS         |

| Output Offset                                                 |       |      | 0.6    | μΑ          |

| Differential Nonlinearity                                     |       | 1    | 0.0    | LSB         |

| Integral Nonlinearity                                         |       | 2    |        | LSB         |

| Output Capacitance                                            |       | 5    |        | pF          |

| Residual Phase Noise @ 1 kHz Offset, 400 MHz A <sub>OUT</sub> |       | 3    |        | þr          |

|                                                               |       | 122  |        | -ID - /I I- |

| REFCLK Multiplier Disabled                                    |       | -123 |        | dBc/Hz      |

| REFCLK Multiplier Enabled @ 127×                              |       | TBD  |        | dBc/Hz      |

| REFCLK Multiplier Enabled @ 64×                               |       | -105 |        | dBc/Hz      |

| REFCLK Multiplier Enabled @ 8×                                |       | -115 | a = 1. | dBc/Hz      |

| AC Voltage Compliance Range                                   | -0.5V |      | 0.5V   | V           |

| SPURIOUS-FREE DYNAMIC RANGE (SFDR)                            |       |      |        |             |

| fout = 50 MHz                                                 |       | TBD  |        | dBc         |

| fout = 104 MHz                                                |       | TBD  |        | dBc         |

| fout = 209 MHz                                                |       | TBD  |        | dBc         |

| fout = 315 Mhz                                                |       | TBD  |        | dBc         |

| fout = 403 MHz                                                |       | TBD  |        | dBc         |

| TWO TONE INTERMODULATION DISTORTION (IMD)                     |       |      |        |             |

| fout = fout + 1.25 MHz                                        |       |      |        |             |

| fout = 50 MHz                                                 |       | TBD  |        | dBc         |

| fout = 104 MHz                                                |       | TBD  |        | dBc         |

| fout = 209 MHz                                                |       | TBD  |        | dBc         |

| fout = 315 Mhz                                                |       | TBD  | dBc    |             |

| fout = 403 MHz                                                |       | TBD  | dBc    |             |

| NOISE SPECTRAL DENSITY (NSD) Single Tone                      |       |      |        |             |

| fout = 50 MHz                                                 |       | TBD  |        | dBm / Hz    |

| fout = 104 MHz                                                |       | TBD  |        | dBm / Hz    |

| fout = 209 MHz                                                |       | TBD  |        | dBm / Hz    |

| fout = 315 Mhz                                                |       | TBD  |        | dBm / Hz    |

| fout = 403 MHz                                                |       | TBD  |        | dBm / Hz    |

| TOUL - TOU IVII IZ                                            | 1     | יטטי |        | UDITI/ TIZ  |

| Parameter                                                             | Min | Тур              | Max | Unit           |

|-----------------------------------------------------------------------|-----|------------------|-----|----------------|

| NOISE SPECTRAL DENSITY (NSD) Continued                                |     |                  |     |                |

| Eight Tone, 500KHz Tone Spacing                                       |     |                  |     |                |

| fout = 50 MHz                                                         |     | TBD              |     | dBm / Hz       |

| fout = 104 MHz                                                        |     | TBD              |     | dBm / Hz       |

| fout = 209 MHz                                                        |     | TBD              |     | dBm / Hz       |

| fout = 315 Mhz                                                        |     | TBD              |     | dBm / Hz       |

| fout = 403 MHz                                                        |     | TBD              |     | dBm / Hz       |

| MODULATOR CHARACTERISTICS (260MHz A <sub>OUT</sub>                    |     |                  |     |                |

| Input Data: 10MS/s, QPSK, 4x Oversampled                              |     |                  |     |                |

| I/Q Offset                                                            | 55  | 65               |     | dB             |

| Error Vector Magnitude                                                |     | 0.4              | 1   | %              |

| Input Data: 10MS/s GMSK 4x Oversampled                                |     |                  |     |                |

| I/Q Offset                                                            | TBD | TBD              |     | dB             |

| Error Vector Magnitude                                                |     | TBD              | TBD | %              |

| Input Data: 10MS/s 256-QAM 4x Oversampled                             |     |                  |     | ,-             |

| I/Q Offset                                                            | TBD | TBD              |     | dB             |

| Error Vector Magnitude                                                | 100 | TBD              | TBD | %              |

| Adjacent Channel Leakage Ratio (ACLR)                                 |     | 100              | 100 | 70             |

| WCDMA with 3.84MHz BW, 5MHz Channel Spacing                           |     |                  |     |                |

| fDAC=1GSPS, fOUT=200MHz                                               |     | 79               |     | dB             |

| fDAC=1GSPS, fOUT=400MHz                                               |     | 7 <i>9</i><br>74 |     | dB             |

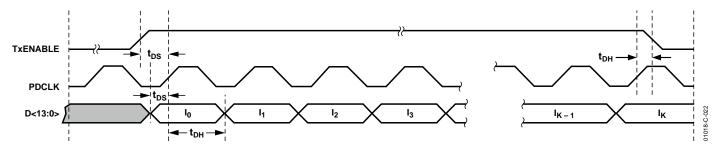

| TIMING CHARACTERISTICS                                                |     | /4               |     | ив             |

| Parallel Data Bus                                                     |     |                  |     |                |

|                                                                       |     | 250              |     | MS/s           |

| Maximum Frequency Minimum TxEnable Pulse Width Low                    |     | 250<br>2         |     |                |

|                                                                       |     | 2                |     | ns             |

| Minimum TxEnable Pulse Width High                                     |     | 2                |     | ns             |

| Minimum Data Setup Time (TxEnable to PDCIk)                           |     | 4                |     | ns             |

| Minium Data Hold Time (PDClk rising edge to data change)              |     | 0                |     | ns             |

| Serial Control Bus                                                    |     | 25               |     |                |

| Maximum Frequency                                                     |     | 25               |     | Mbps           |

| Minimum Clock Pulse Width Low                                         | 7   |                  |     | ns             |

| Minimum Clock Pulse Width High                                        | 7   | _                |     | ns             |

| Maximum Clock Rise/Fall Time                                          |     | 2                |     | ns             |

| Minimum Data Setup Time DVDD_I/O = 3.3 V                              | 3   |                  |     | ns             |

| Minimum Data Hold Time                                                | 0   |                  |     | ns             |

| Maximum Data Valid Time                                               |     | 25               |     | ns             |

| Wake-Up Time <sup>2</sup>                                             |     |                  |     |                |

| Minimum Reset Pulse Width High                                        | 5   |                  |     | SYSCLK Cycles3 |

| I/O UPDATE, PS0, PS1 to SYNCCLK Setup Time DVDD_I/O = $3.3 \text{ V}$ | 4   |                  |     | ns             |

| I/O UPDATE, PS0, PS1 to SYNCCLK Hold Time                             | 0   |                  |     | ns             |

| Latency                                                               |     |                  |     |                |

| I/O UPDATE to Frequency Change Propagation Delay                      | 24  |                  |     | SYSCLK Cycles  |

| I/O UPDATE to Phase Offset Change Propagation Delay                   | 24  |                  |     | SYSCLK Cycles  |

| I/O UPDATE to Amplitude Change Propagation Delay                      | 16  |                  |     | SYSCLK Cycles  |

| CMOS LOGIC INPUTS                                                     |     |                  |     |                |

| Logic 1 Voltage                                                       | 2.2 |                  |     | V              |

| Logic 0 Voltage                                                       |     |                  | 0.8 | V              |

| Logic 1 Current                                                       |     | 3                | 12  | μΑ             |

| Logic 0 Current                                                       |     |                  | 12  | μA             |

| Input Capacitance                                                     |     | 2                |     | pF             |

| _                                                                     |     | 2                | 14  | ·              |

Rev. PrF | Page 4 of 38

| CMOS LOGIC OUTPUTS (1 mA Load) Logic 1 Voltage Logic 0 Voltage  V XTAL OUTPUT BUFFER SPECS Logic 1 Voltage 1.6 V Logic 0 Voltage TBD V Output Current TBD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                |     |     |      |      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|-----|-----|------|------|

| Logic 1 Voltage Logic 0 Voltage  XTAL OUTPUT BUFFER SPECS Logic 1 Voltage Logic 0 Voltage  Logic 0 Voltage  Logic 0 Voltage  TBD V Output Current  TBD MA  POWER CONSUMPTION DVDD_I/O(3.3V) current consumption (QDUC mode) DVDD_I/O(3.3V) current consumption (QDUC mode) AVDD(1.8V) current consumption (QDUC mode)  MA  AVDD(1.8V) current consumption (QDUC mode)  Single Tone Mode Continuous Modulation 255x Interpolation TBD TBD TBD MW  Burst Modulation (25%) 255x Interpolation TBD TBD TBD TBD TBD MW  Full-Sleep Mode  V  V  V  V  V  V  V  V  V  V  V  V  V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Parameter                                      | Min | Тур | Max  | Unit |

| Logic 0 Voltage  XTAL OUTPUT BUFFER SPECS  Logic 1 Voltage  Logic 0 Voltage  1.6  V  Output Current  POWER CONSUMPTION  DVDD_I/O(3.3V) current consumption (QDUC mode)  AVDD(1.8V) current consumption (QDUC mode)  TABD  TABD | CMOS LOGIC OUTPUTS (1 mA Load)                 |     |     |      |      |

| XTAL OUTPUT BUFFER SPECS  Logic 1 Voltage  Logic 0 Voltage  Output Current  POWER CONSUMPTION  DVDD_I/O(3.3V) current consumption (QDUC mode)  DVDD(1.8V) current consumption (QDUC mode)  AVDD(3.3V) current consumption (QDUC mode)  AVDD(1.8V) current consumption (QDUC mode)  AVDD(1.8V) current consumption (QDUC mode)  Single Tone Mode  Continuous Modulation 255x Interpolation  Continuous Modulation 4x Interpolation  Burst Modulation (25%) 255x Interpolation  TBD  TBD  TBD  TBD  TBD  TBD  TBD  TB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Logic 1 Voltage                                | 2.8 |     |      | V    |

| Logic 1 Voltage Logic 0 Voltage TBD V Output Current TBD MA  POWER CONSUMPTION DVDD_I/O(3.3V) current consumption (QDUC mode) DVDD(1.8V) current consumption (QDUC mode) AVDD(3.3V) current consumption (QDUC mode) AVDD(1.8V) current consumption (QDUC mode)  AVDD(1.8V) current consumption (QDUC mode)  Single Tone Mode Continuous Modulation 255x Interpolation TBD TBD TBD TBD MW  Burst Modulation (25%) 255x Interpolation TBD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Logic 0 Voltage                                |     |     | 0.4  | V    |

| Logic 0 Voltage Output Current TBD V Output Current  POWER CONSUMPTION DVDD_I/O(3.3V) current consumption (QDUC mode) DVDD(1.8V) current consumption (QDUC mode) AVDD(3.3V) current consumption (QDUC mode) AVDD(1.8V) current consumption (QDUC mode) AVDD(1.8V) current consumption (QDUC mode) Single Tone Mode Continuous Modulation 255x Interpolation TBD TBD TBD mW Burst Modulation (25%) 255x Interpolation TBD TBD TBD TBD TBD mW Full-Sleep Mode TBD TBD mW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | XTAL OUTPUT BUFFER SPECS                       |     |     |      |      |

| Output Current TBD mA  POWER CONSUMPTION  DVDD_I/O(3.3V) current consumption (QDUC mode)  DVDD(1.8V) current consumption (QDUC mode)  AVDD(3.3V) current consumption (QDUC mode)  AVDD(1.8V) current consumption (QDUC mode)  AVDD(1.8V) current consumption (QDUC mode)  Single Tone Mode  Continuous Modulation 255x Interpolation  TBD 1000  TBD TBD mW  Burst Modulation (25%) 255x Interpolation  TBD TBD mW  Burst Modulation (25%) 4x Interpolation  TBD TBD mW  Full-Sleep Mode  TBD TBD mW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Logic 1 Voltage                                | 1.6 |     |      | V    |

| POWER CONSUMPTION  DVDD_I/O(3.3V) current consumption (QDUC mode)  AVDD(1.8V) current consumption (QDUC mode)  AVDD(1.8V) current consumption (QDUC mode)  AVDD(1.8V) current consumption (QDUC mode)  Single Tone Mode  Continuous Modulation 255x Interpolation  Continuous Modulation 4x Interpolation  Burst Modulation (25%) 255x Interpolation  Burst Modulation (25%) 4x Interpolation  TBD TBD mW  Burst Modulation (25%) 4x Interpolation  TBD TBD mW  TBD TBD mW  TBD TBD mW  TBD TBD mW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Logic 0 Voltage                                |     |     | TBD  | V    |

| DVDD_I/O(3.3V) current consumption (QDUC mode)  DVDD(1.8V) current consumption (QDUC mode)  AVDD(3.3V) current consumption (QDUC mode)  AVDD(1.8V) current consumption (QDUC mode)  Single Tone Mode  Continuous Modulation 255x Interpolation  Continuous Modulation 4x Interpolation  Burst Modulation (25%) 255x Interpolation  Burst Modulation (25%) 4x Interpolation  TBD TBD mW  Burst Modulation (25%) 4x Interpolation  TBD TBD mW  Full-Sleep Mode  mA  mA  mA  mA  mA  mA  mA  mA  mA  m                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Output Current                                 |     |     | TBD  | mA   |

| DVDD(1.8V) current consumption (QDUC mode)  AVDD(3.3V) current consumption (QDUC mode)  AVDD(1.8V) current consumption (QDUC mode)  Single Tone Mode  Continuous Modulation 255x Interpolation  Continuous Modulation 4x Interpolation  Burst Modulation (25%) 255x Interpolation  Burst Modulation (25%) 4x Interpolation  TBD  TBD  TBD  TBD  TBD  TBD  TBD  TB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | POWER CONSUMPTION                              |     |     |      |      |

| AVDD(3.3V) current consumption (QDUC mode)  AVDD(1.8V) current consumption (QDUC mode)  Single Tone Mode  Continuous Modulation 255x Interpolation  Continuous Modulation 4x Interpolation  Burst Modulation (25%) 255x Interpolation  Burst Modulation (25%) 4x Interpolation  TBD  TBD  TBD  TBD  TBD  TBD  TBD  TB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | DVDD_I/O(3.3V) current consumption (QDUC mode) |     |     |      | mA   |

| AVDD(1.8V) current consumption (QDUC mode)  Single Tone Mode  Continuous Modulation 255x Interpolation  Continuous Modulation 4x Interpolation  Burst Modulation (25%) 255x Interpolation  Burst Modulation (25%) 4x Interpolation  TBD  TBD  TBD  mW  TBD  TBD  mW  Full-Sleep Mode  TBD  TBD  mW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | DVDD(1.8V) current consumption (QDUC mode)     |     |     |      | mA   |

| Single Tone Mode500mWContinuous Modulation 255x InterpolationTBD1000mWContinuous Modulation 4x InterpolationTBDTBDmWBurst Modulation (25%) 255x InterpolationTBDTBDmWBurst Modulation (25%) 4x InterpolationTBDTBDmWFull-Sleep ModeTBDTBDmW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | AVDD(3.3V) current consumption (QDUC mode)     |     |     |      | mA   |

| Continuous Modulation 255x InterpolationTBD1000mWContinuous Modulation 4x InterpolationTBDTBDmWBurst Modulation (25%) 255x InterpolationTBDTBDmWBurst Modulation (25%) 4x InterpolationTBDTBDmWFull-Sleep ModeTBDTBDmW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | AVDD(1.8V) current consumption (QDUC mode)     |     |     |      | mA   |

| Continuous Modulation 4x Interpolation TBD TBD mW  Burst Modulation (25%) 255x Interpolation TBD TBD mW  Burst Modulation (25%) 4x Interpolation TBD TBD mW  Full-Sleep Mode TBD TBD mW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Single Tone Mode                               |     | 500 |      | mW   |

| Burst Modulation (25%) 255x Interpolation  Burst Modulation (25%) 4x Interpolation  TBD TBD mW  TBD TBD mW  Full-Sleep Mode  TBD TBD mW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Continuous Modulation 255x Interpolation       |     | TBD | 1000 | mW   |

| Burst Modulation (25%) 4x Interpolation TBD TBD mW Full-Sleep Mode TBD TBD mW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Continuous Modulation 4x Interpolation         |     | TBD | TBD  | mW   |

| Full-Sleep Mode TBD TBD mW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Burst Modulation (25%) 255x Interpolation      |     | TBD | TBD  | mW   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Burst Modulation (25%) 4x Interpolation        |     | TBD | TBD  | mW   |

| Inverse Sinc Filter Power Consumption 150 TBD mW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Full-Sleep Mode                                |     | TBD | TBD  | mW   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Inverse Sinc Filter Power Consumption          |     | 150 | TBD  | mW   |

<sup>1</sup> To achieve the best possible phase noise, the largest amplitude clock possible should be used. Reducing the clock input amplitude will reduce the phase noise performance of the device.

<sup>3</sup> SYSCLK cycle refers to the actual clock frequency used on-chip by the DDS. If the reference clock multiplier is used to multiply the external reference clock frequency, the SYSCLK frequency is the external frequency multiplied by the reference clock multiplication factor. If the reference clock multiplier and divider are not used, the SYSCLK frequency is the same as the external reference clock frequency.

Figure 2 Equivalent Input/Output (I/O) Circuits

<sup>2</sup> Wake-up time refers to the recovery from analog power-down modes.

### **ABSOLUTE MAXIMUM RATINGS**

Table 2.

| Parameter                           | Rating          |

|-------------------------------------|-----------------|

| Maximum Junction Temperature        | 150°C           |

| AVDD(1.8V), DVDD(1.8V) supplies     | 2 V             |

| AVDD(3.3V), DVDD_I/O(3.3V) supplies | 4V              |

| Digital Input Voltage)              | -0.7 V to +4V   |

| Digital Output Current              | 5 mA            |

| Storage Temperature                 | -65°C to +150°C |

| Operating Temperature               | -40°C to +85°C  |

| Lead Temperature (10 sec Soldering) | 300°C           |

| $	heta_{JA}$                        | 38°C/W          |

| $\theta_{ m JC}$                    | 15°C/W          |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ESD Caution**

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although this product features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

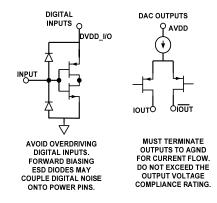

### PIN CONFIGURATION

# AD9957

### PIN DESCRIPTION

| Pin #                                    | Mnemonic        | I/O | Description                                                                                                                                                                                                                                                                                                                                 |

|------------------------------------------|-----------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 24, 61, 72,<br>86, 87, 93, 97-<br>100 | NC              |     | Not Connected. Allow device pin to float.                                                                                                                                                                                                                                                                                                   |

| 2                                        | PLL_LOOP_FILTER | I   | PLL loop filter compensation pin.                                                                                                                                                                                                                                                                                                           |

| 3, 6, 89, 92                             | AVDD (1.8V)     | I   | Analog Core VDD: 1.8V Analog Supply.                                                                                                                                                                                                                                                                                                        |

| 74-77, 83                                | AVDD (3.3V)     | I   | Analog DAC VDD: 3.3V Analog Supply.                                                                                                                                                                                                                                                                                                         |

| 17, 23, 30, 47,<br>57, 64                | DVDD (1.8V)     | I   | Digital Core VDD: 1.8V Digital Supply.                                                                                                                                                                                                                                                                                                      |

| 11, 15, 21, 28,<br>45, 56, 66            | DVDD_I/O (3.3V) | I   | Digital Input/Output VDD: 3.3V Digital Supply.                                                                                                                                                                                                                                                                                              |

| 4, 5, 73, 78,<br>79, 82, 85, 88,<br>96   | AGND            | I   | Analog Ground.                                                                                                                                                                                                                                                                                                                              |

| 13, 16,22,<br>29,46,58,62,63<br>65       | DGND            | I   | Digital Ground.                                                                                                                                                                                                                                                                                                                             |

| 7                                        | SYNC_IN+        | I   | Digital input (rising edge active). Synchronization signal from external master to synchronize internal sub-clocks.                                                                                                                                                                                                                         |

| 8                                        | SYNC_IN-        | I   | Digital input (rising edge active). Synchronization signal from external master to synchronize internal sub-clocks.                                                                                                                                                                                                                         |

| 9                                        | SYNC_OUT+       | 0   | Digitaloutput (rising edge active). Synchronization signal from internal device sub-<br>clocks to synchronize external slave devices.                                                                                                                                                                                                       |

| 10                                       | SYNC_OUT-       | 0   | Digitaloutput (rising edge active). Synchronization signal from internal device sub-<br>clocks to synchronize external slave devices.                                                                                                                                                                                                       |

| 12                                       | SYNC_SMP_ERR    | 0   | Digital output (active high). Sync sample error: A high on this pin indicates that the AD9957 did not receive a valid sync signal on SYNC_I+/SYNC_I                                                                                                                                                                                         |

| 14                                       | MASTER_RESET    | I   | Digital Input (active high). Master reset: clears all memory elements and sets registers to default values.                                                                                                                                                                                                                                 |

| 18                                       | EXT_PWR_DWN     | I   | Digital input (active high). External Power Down: A high level on this pin initates the currently programmed power down mode. Please see the Power Down Modes section of this document for further details. If unused, tie to ground.                                                                                                       |

| 19                                       | PLL_LOCK        | 0   | Digital output (active high). PLL_Lock: A high indicates the clock multiplier PLL has acquired lock to the reference clock input.                                                                                                                                                                                                           |

| 20                                       | CCI_OVFL        | 0   | Digital output (active high). CCI Overflow: A high indicates a CCI filter overflow. This pin will remain high until the CCI overflow condition is cleared.                                                                                                                                                                                  |

| 25-27, 31-39,<br>42-44, 48-50            | D<17:0>         | I   | Parallel data input bus (active high). These pins provide the interleaved 18 bit digital I & Q vectors for the modulator to upconvert.                                                                                                                                                                                                      |

| 42                                       | SPORT I-DATA    | I   | In Blackfin interface mode, this pin serves as the I-data serial input.                                                                                                                                                                                                                                                                     |

| 43                                       | SPORT Q-DATA    | I   | In Blackfin interface mode, this pin serves as the Q-data serial input.                                                                                                                                                                                                                                                                     |

| 40                                       | PDCLK/TSCLK     | 0   | Digital output (clock) Parallel Data Clock see Signal Processing section for details                                                                                                                                                                                                                                                        |

| 41                                       | TxENABLE        | I   | Digital input (active high). Transmit enable: see Signal Processing section for details                                                                                                                                                                                                                                                     |

| 41                                       | FS              | I   | In Blackfin interface mode, this pin serves as the FS Input, to receive the RFS OUTPUT signal from the ADSP BF533                                                                                                                                                                                                                           |

| 51                                       | ISFC            | I   | Digital input (active high). Input Scaling Function Control: Control for the RAM amplitude scaling function. When this function is engaged, a high sweeps the amplitude from the beginning RAM address to the end. A low sweeps the amplitude from the end RAM address to the beginning.                                                    |

| 52-54                                    | PROFILE <2:0>   | I   | Digital inputs (active high). Profile select pins: used to select one of eight phase/frequency profiles for the DDS core (single-tone or carrier tone). Changing the state of one of these pins will transfer the current contents of all I/O buffers to the corresponding registers. State changes should be setup to the IO_SYNC_CLK pin. |

| 55                                       | SYNC_CLK        | 0   | Digital output (clock). Outputs System clock/4. The I/O_UPDATE and PROFILE<2:0> pins should be setup to the rising edge of this signal.                                                                                                                                                                                                     |

| 59 | I/O_UPDATE | I   | Digital input (active high). Input/Output update: A high on this pin transfers the contents of the I/O buffers to the corresponding internal registers.                                                                                                                                                                                                                      |

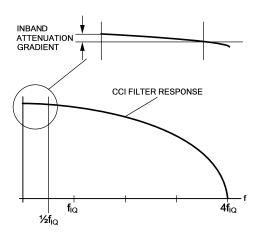

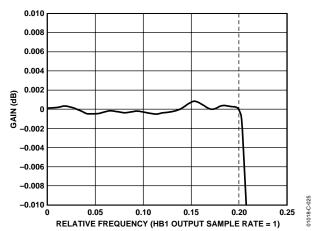

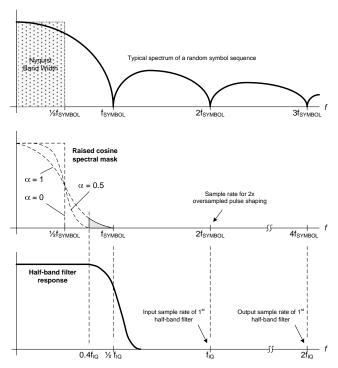

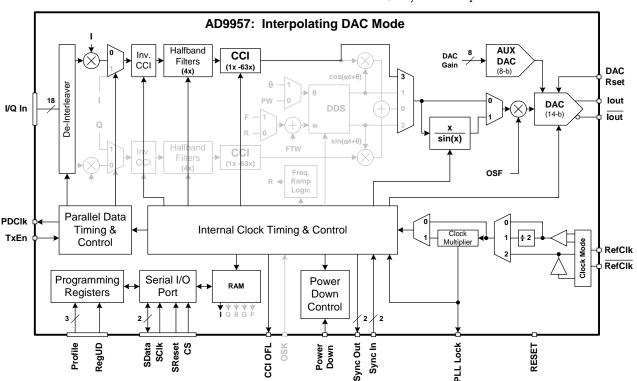

|----|------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|