## **Features**

- Integrated PLL Loop Filter

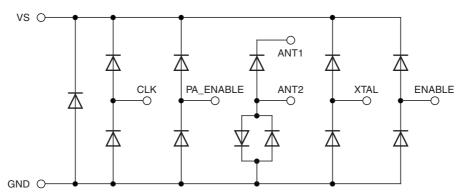

- ESD Protection also at ANT1/ANT2

(4 kV HBM/200V MM; Except Pin 2: 4 kV HBM/100V MM)

- High Output Power (5.5 dBm) with Low Supply Current (8.5 mA)

- Modulation Scheme ASK/FSK

- FSK Modulation is Achieved by Connecting an Additional Capacitor Between the XTAL Load Capacitor and the Open Drain Output of the Modulating Microcontroller

- Easy to Design-in Due to Excellent Isolation of the PLL from the PA and Power Supply

- Single Li-cell for Power Supply

- Supply Voltage 2.0V to 4.0V in the Temperature Range of -40°C to +85°C

- Package TSSOP8L

- Single-ended Antenna Output with High Efficient Power Amplifier

- CLK Output for Clocking the Microcontroller

- One-chip Solution with Minimum External Circuitry

# **Applications**

- Industrial/Aftermarket Remote Keyless Entry Systems

- Alarm, Telemetering, and Energy Metering Systems

- Remote Control Systems for Consumer and Industrial Markets

- Access Control Systems

- Home Automation

- Home Entertainment

- Toys

# 1. Description

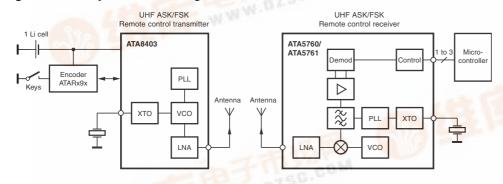

The ATA8403 is a PLL transmitter IC, which has been developed for the demands of RF low-cost transmission systems for industrial applications at data rates up to 50 kBaud ASK and 32 kBaud FSK modulation scheme. The transmitting frequency range is 868 MHz to 928 MHz. It can be used in both FSK and ASK systems.

Figure 1-1. System Block Diagram

# UHF ASK/FSK Industrial Transmitter

ATA8403

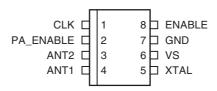

# 2. Pin Configuration

Figure 2-1. Pinning TSSOP8L

Table 2-1.Pin Description

| Pin | Symbol       | Function                                                                                                              | Configuration                           |

|-----|--------------|-----------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| 1   | CLK          | Clock output signal for microconroller<br>The clock output frequency is set by the<br>crystal to f <sub>XTAL</sub> /4 | 100Ω CLK                                |

| 2   | PA_ENABLE    | Switches on power amplifier, which is used for ASK modulation                                                         | PA_ENABLE 50 kΩ U <sub>REF</sub> = 1.1V |

| 3   | ANT2<br>ANT1 | Emitter of antenna output stage  Open collector antenna output                                                        | ANT1<br>O<br>ANT2                       |

Table 2-1.

Pin Description (Continued)

| Pin | Symbol | Function               | Configuration                                           |

|-----|--------|------------------------|---------------------------------------------------------|

| 5   | XTAL   | Connection for crystal | VS VS VS 1.5 kΩ 1.2 kΩ 182 μΑ                           |

| 6   | VS     | Supply voltage         | See ESD protection circuitry (see Figure 4-5 on page 9) |

| 7   | GND    | Ground                 | See ESD protection circuitry (see Figure 4-5 on page 9) |

| 8   | ENABLE | Enable input           | ENABLE 200 kΩ                                           |

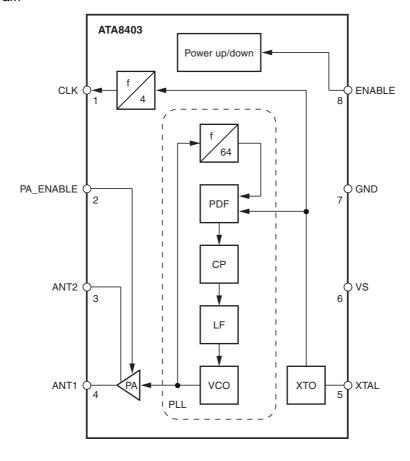

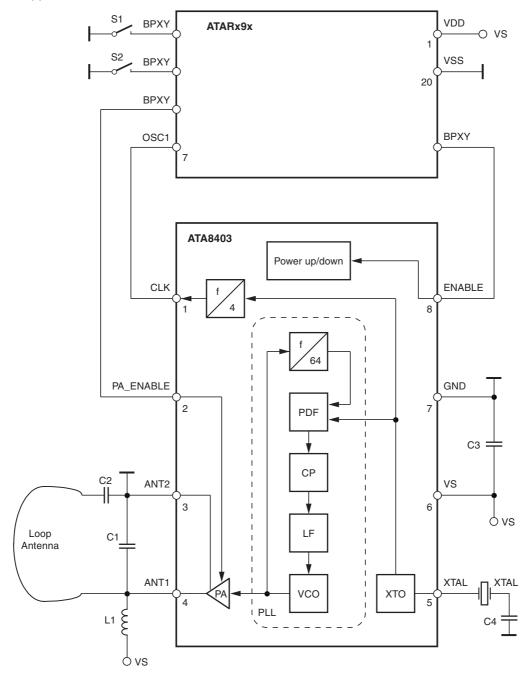

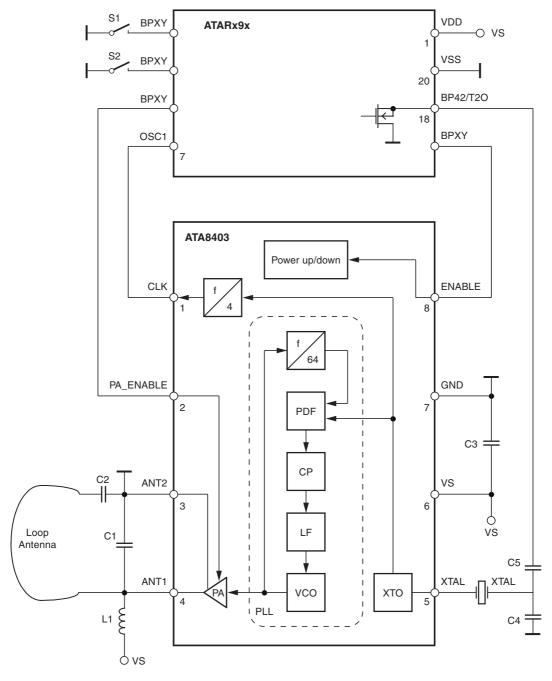

Figure 2-2. Block Diagram

# 3. General Description

This fully integrated PLL transmitter allows particularly simple, low-cost RF miniature transmitters to be assembled. The VCO is locked to  $64 \times f_{XTAL}$ , and therefore a 13.5672 MHz crystal is needed for a 868.3 MHz transmitter and a 14.2969 MHz crystal for a 915 MHz transmitter. All other PLL and VCO peripheral elements are integrated.

The XTO is a series resonance oscillator so that only one capacitor together with a crystal connected in series to GND are needed as external elements.

The crystal oscillator together with the PLL typically needs < 1 ms until the PLL is locked and the CLK output is stable. There is a wait time of  $\ge 4$  ms must be used until the CLK is used for the microcontroller and the PA is switched on.

The power amplifier is an open-collector output delivering a current pulse, which is nearly independent from the load impedance. The delivered output power is therefore controllable via the connected load impedance.

This output configuration enables a simple matching to any kind of antenna or to  $50\Omega$ . A high power efficiency of  $\eta = P_{out}/(I_{S,PA} \times V_S)$  of 24% for the power amplifier at 868.3 MHz results when an optimized load impedance of  $Z_{Load} = (166 + j226)\Omega$  is used at 3V supply voltage.

# 4. Functional Description

If ENABLE = L and the PA\_ENABLE = L, the circuit is in standby mode, consuming only a very small amount of current, so that a lithium cell used as power supply can work for several years.

With ENABLE = H the XTO, PLL, and the CLK driver are switched on. If PA\_ENABLE remains L, only the PLL and the XTO are running and the CLK signal is delivered to the microcontroller. The VCO locks to 64 times the XTO frequency.

With ENABLE = H and PA\_ENABLE = H the PLL, XTO, CLK driver, and the power amplifier are on. The power amplifier can be switched on and off with PA\_ENABLE. This is used to perform the ASK modulation.

#### 4.1 ASK Transmission

The ATA8403 is activated by ENABLE = H. PA\_ENABLE must remain L for  $t \ge 4$  ms, then the CLK signal can be taken to clock the microcontroller, and the output power can be modulated by means of the PA\_ENABLE pin. After transmission, PA\_ENABLE is switched to L, and the microcontroller switches back to internal clocking. The ATA8403 is switched back to standby mode with ENABLE = L.

#### 4.2 FSK Transmission

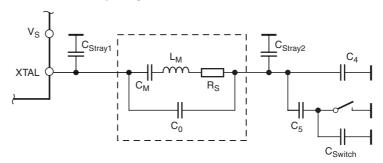

The ATA8403 is activated by ENABLE = H. PA\_ENABLE must remain L for  $t \ge 4$  ms, then the CLK signal can be taken to clock the microcontroller and the power amplifier is switched on with PA\_ENABLE = H. The chip is then ready for FSK modulation. The microcontroller starts to switch on and off the capacitor between the XTAL load capacitor and GND with an open-drain output port, thus changing the reference frequency of the PLL. If the switch is closed, the output frequency is lower than if the switch is open. After transmission PA\_ENABLE is switched to L and the microcontroller switches back to internal clocking. The ATA8403 is switched back to standby mode with ENABLE = L.

The accuracy of the frequency deviation with XTAL pulling method is about ±25% when the following tolerances are considered.

Figure 4-1. Tolerances of Frequency Modulation

Using  $C_4 = 9.2$  pF  $\pm 2\%$ ,  $C_5 = 6.8$  pF  $\pm 5\%$ , a switch port with  $C_{Switch} = 3$  pF  $\pm 10\%$ , stray capacitances on each side of the crystal of  $C_{Stray1} = C_{Stray2} = 1$  pF  $\pm 10\%$ , a parallel capacitance of the crystal of  $C_0 = 3.2$  pF  $\pm 10\%$  and a crystal with  $C_M = 13$  fF  $\pm 10\%$ , typically results in an FSK deviation of  $\pm 21.5$  kHz with worst case tolerances of  $\pm 16.8$  kHz to  $\pm 28.0$  kHz.

## 4.3 CLK Output

An output CLK signal is provided for a connected microcontroller. The delivered signal is CMOS compatible if the load capacitance is lower than 10 pF.

#### 4.3.1 Clock Pulse Take-over

The clock of the crystal oscillator can be used for clocking the microcontroller. A special feature of Atmel<sup>®</sup>'s ATARx9x is that it starts with an integrated RC-oscillator to switch on the ATA8403 with ENABLE = H, and after 4 ms assumes the clock signal of the transmission IC, so that the message can be sent with crystal accuracy.

### 4.3.2 Output Matching and Power Setting

The output power is set by the load impedance of the antenna. The maximum output power is achieved with a load impedance of  $Z_{Load,opt} = (166 + j226)\Omega$  at 868.3 MHz. There must be a low resistive path to  $V_S$  to deliver the DC current.

The delivered current pulse of the power amplifier is 7.7 mA. The maximum output power is delivered to a resistive load of  $475\Omega$  if the 0.53 pF output capacitance of the power amplifier is compensated by the load impedance.

An optimum load impedance of:

$Z_{Load}$  = 475 $\Omega$  || j/(2 × p × f × 0.53 pF) = (166 + j226) $\Omega$  thus results in the maximum output power of 5.5 dBm.

The load impedance is defined as the impedance seen from the ATA8403's ANT1, ANT2 into the matching network. Do not confuse this large signal load impedance with a small signal input impedance delivered as input characteristic of RF amplifiers and measured from the application into the IC instead of from the IC into the application for a power amplifier.

Less output power is achieved by lowering the real parallel part of  $475\Omega$  where the parallel imaginary part should be kept constant.

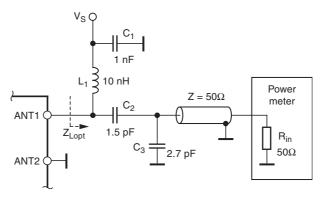

Output power measurement can be done with the circuit shown in Figure 4-2 on page 6. Note that the component values must be changed to compensate for the individual board parasitics until the ATA8403 has the right load impedance  $Z_{Load,opt} = (166 + j226)\Omega$  at 868.3 MHz. Also the damping of the cable used to measure the output power must be calibrated out.

Figure 4-2. Output Power Measurement

# 4.4 Application Circuit

A value of 68 nF/X7R is recommended for the supply-voltage blocking capacitor  $C_3$  (see Figure 4-3 on page 7 and Figure 4-4 on page 8).  $C_1$  and  $C_2$  are used to match the loop antenna to the power amplifier where  $C_1$  typically is 3.9 pF/NP0 and  $C_2$  is 1 pF/NP0. For  $C_2$ , two capacitors in series should be used to achieve a better tolerance value and to have the possibility of realizing the  $Z_{Load,opt}$  using standard valued capacitors.

$C_1$ , together with the pins of ATA8403 and the PCB board wires, forms a series resonance loop that suppresses the 1<sup>st</sup> harmonic. Therefore, the position of  $C_1$  on the PCB is important. Normally the best suppression is achieved when  $C_1$  is placed as close as possible to the pins ANT1 and ANT2.

The loop antenna should not exceed a width of 1.5 mm, otherwise the Q-factor of the loop antenna is too high.

$L_1$  ( $\approx 50$  nH to 100 nH) can be printed on PCB.  $C_4$  should be selected so that the XTO runs on the load resonance frequency of the crystal. Normally, a 15 pF load-capacitance crystal results in a value of 12 pF.

Figure 4-3. ASK Application Circuit

Figure 4-4. FSK Application Circuit

Figure 4-5. **ESD Protection Circuit**

#### **Absolute Maximum Ratings** 5.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

| Parameters           | Symbol                    | Minimum     | Maximum             | Unit |

|----------------------|---------------------------|-------------|---------------------|------|

| Supply voltage       | V <sub>S</sub>            |             | 5                   | V    |

| Power dissipation    | P <sub>tot</sub>          |             | 100                 | mW   |

| Junction temperature | T <sub>j</sub>            |             | 150                 | °C   |

| Storage temperature  | T <sub>stg</sub>          | <b>–</b> 55 | +85                 | °C   |

| Ambient temperature  | T <sub>amb</sub>          | <b>–</b> 55 | +85                 | °C   |

| Input voltage        | V <sub>maxPA ENABLE</sub> | -0.3        | $(V_S + 0.3)^{(1)}$ | V    |

Note: 1. If  $V_S$  + 0.3 is higher than 3.7V, the maximum voltage will be reduced to 3.7V.

# **Thermal Resistance**

| Parameters       | Symbol            | Value | Unit |  |

|------------------|-------------------|-------|------|--|

| Junction ambient | R <sub>thJA</sub> | 170   | K/W  |  |

# 7. Electrical Characteristics

$V_S$  = 2.0V to 4.0V,  $T_{amb}$  = 25°C unless otherwise specified. Typical values are given at  $V_S$  = 3.0V and  $T_{amb}$  = 25°C. All parameters are referred to GND (pin 7).

| Parameters     | Test Conditions                                                                                                                | Symbol                  | Min. | Тур. | Max. | Unit     |

|----------------|--------------------------------------------------------------------------------------------------------------------------------|-------------------------|------|------|------|----------|

| Supply current | Power down,<br>V <sub>ENABLE</sub> < 0.25V, -40°C to 85°C<br>V <sub>PA_ENABLE</sub> < 0.25V, 25°C<br>(100% correlation tested) | I <sub>S_Off</sub>      |      | < 10 | 350  | nA<br>nA |

| Supply ourrant | Power up, PA off, $V_S = 3V$ , $V_{ENABLE} > 1.7V$ , $V_{PA\_ENABLE} < 0.25V$                                                  | I <sub>S</sub>          |      | 3.6  | 4.6  | mA       |

| Supply current | Power up, $V_S = 3.0$ ,<br>$V_{ENABLE} > 1.7V$ , $V_{PA\_ENABLE} > 1.7V$                                                       | I <sub>S_Transmit</sub> |      | 8.5  | 11   | mA       |

| Output power   | $V_S = 3.0V$ , $T_{amb} = 25^{\circ}C$ ,<br>f = 868.3 MHz, $Z_{Load} = (166 + j226)\Omega$                                     | P <sub>Ref</sub>        | 3.5  | 5.5  | 8    | dBm      |

1. If  $V_S$  is higher than 3.6V, the maximum voltage will be reduced to 3.6V. Note:

# 7. Electrical Characteristics (Continued)

$V_S = 2.0V$  to 4.0V,  $T_{amb} = 25^{\circ}C$  unless otherwise specified. Typical values are given at  $V_S = 3.0V$  and  $T_{amb} = 25^{\circ}C$ . All parameters are referred to GND (pin 7).

| Parameters                                               | Test Conditions                                                                                                                                                                                                                                 |                                                       | Min.                 | Тур.                | Max.                                       | Unit             |

|----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|----------------------|---------------------|--------------------------------------------|------------------|

| Output power variation for the full temperature range    | $T_{amb} = 25^{\circ}C,$ $V_{S} = 3.0V$ $V_{S} = 2.0V$                                                                                                                                                                                          | $\DeltaP_{Ref} \ \DeltaP_{Ref}$                       |                      |                     | -1.5<br>-4.0                               | dB<br>dB         |

| Output power variation for the full temperature range    | ·                                                                                                                                                                                                                                               |                                                       |                      |                     | -2.0<br>-4.5                               | dB<br>dB         |

| Achievable output-power range                            | Selectable by load impedance                                                                                                                                                                                                                    | $P_{Out\_typ}$                                        | <del>ا</del>         |                     | +5.5                                       | dBm              |

| Spurious emission                                        | $f_{CLK} = f_0/128$ Load capacitance at pin CLK = 10 pF $f_0 \pm 1 \times f_{CLK}$ $f_0 \pm 4 \times f_{CLK}$ Other spurious are lower                                                                                                          |                                                       |                      | –52<br>–52          |                                            | dBc<br>dBc       |

| Oscillator frequency XTO (= phase comparator frequency)  | $\begin{split} &f_{\text{XTO}} = f_0/32 \\ &f_{\text{XTAL}} = \text{resonant frequency of the XTAL,} \\ &C_{\text{M}} \leq 10 \text{ fF, load capacitance selected} \\ &\text{accordingly} \\ &T_{\text{amb}} = 25^{\circ}\text{C} \end{split}$ | f <sub>XTO</sub>                                      |                      | f <sub>XTAL</sub>   |                                            | ppm              |

| PLL loop bandwidth                                       |                                                                                                                                                                                                                                                 |                                                       |                      | 250                 |                                            | kHz              |

| Phase noise of phase comparator                          | Referred to $f_{PC} = f_{XT0,}$<br>25 kHz distance to carrier                                                                                                                                                                                   |                                                       |                      | -116                | -110                                       | dBc/Hz           |

| In-loop phase noise PLL                                  | 25 kHz distance to carrier                                                                                                                                                                                                                      |                                                       |                      | -80                 | -74                                        | dBc/Hz           |

| Phase noise VCO                                          | At 1 MHz<br>At 36 MHz                                                                                                                                                                                                                           |                                                       |                      | -89<br>-120         | -86<br>-117                                | dBc/Hz<br>dBc/Hz |

| Frequency range of VCO                                   |                                                                                                                                                                                                                                                 | f <sub>VCO</sub>                                      | 868                  |                     | 928                                        | MHz              |

| Clock output frequency (CMOS microcontroller compatible) |                                                                                                                                                                                                                                                 |                                                       |                      | f <sub>0</sub> /256 |                                            | MHz              |

| Voltage swing at pin CLK                                 | C <sub>Load</sub> ≤ 10 pF                                                                                                                                                                                                                       | $V_{0h} V_{0l}$                                       | V <sub>S</sub> × 0.8 |                     | V <sub>S</sub> × 0.2                       | V<br>V           |

| Series resonance R of the crystal                        |                                                                                                                                                                                                                                                 | Rs                                                    |                      |                     | 110                                        | Ω                |

| Capacitive load at pin XT0                               |                                                                                                                                                                                                                                                 |                                                       |                      |                     | 7                                          | pF               |

| FSK modulation frequency rate                            | Duty cycle of the modulation signal = 50%                                                                                                                                                                                                       |                                                       | 0                    |                     | 32                                         | kHz              |

| ASK modulation frequency rate                            | Duty cycle of the modulation signal = 50%                                                                                                                                                                                                       |                                                       | 0                    |                     | 50                                         | kHz              |

| ENABLE input                                             | Low level input voltage<br>High level input voltage<br>Input current high                                                                                                                                                                       | V <sub>II</sub><br>V <sub>Ih</sub><br>I <sub>In</sub> | 1.7                  |                     | 0.25<br>20                                 | V<br>V<br>μΑ     |

| PA_ENABLE input                                          | Low level input voltage<br>High level input voltage<br>Input current high                                                                                                                                                                       | V <sub>II</sub><br>V <sub>Ih</sub><br>I <sub>In</sub> | 1.7                  |                     | 0.25<br>V <sub>S</sub> <sup>(1)</sup><br>5 | V<br>V<br>μΑ     |

1. If  $V_{\rm S}$  is higher than 3.6V, the maximum voltage will be reduced to 3.6V. Note:

# 8. Ordering Information

| Extended Type Number | Package | MOQ      | Remarks                   |

|----------------------|---------|----------|---------------------------|

| ATA8403-6AQY         | TSSOP8L | 5000 pcs | Taped and reeled, Pb-free |

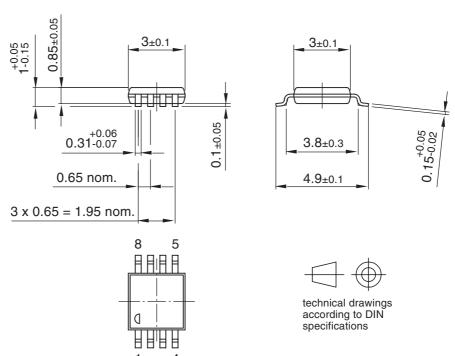

# 9. Package Information

Package: TSSOP 8L Dimensions in mm

Drawing-No.: 6.543-5083.01-4

Issue: 2; 15.03.04

## **Atmel Corporation**

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311

Fax: 1(408) 487-2600

## **Regional Headquarters**

#### Europe

Atmel Sarl Route des Arsenaux 41 Case Postale 80 CH-1705 Fribourg Switzerland

Tel: (41) 26-426-5555 Fax: (41) 26-426-5500

#### Asia

Room 1219 Chinachem Golden Plaza 77 Mody Road Tsimshatsui East Kowloon Hong Kong

Tel: (852) 2721-9778 Fax: (852) 2722-1369

#### Japan

9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan

Tel: (81) 3-3523-3551 Fax: (81) 3-3523-7581

## **Atmel Operations**

#### Memory

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 436-4314

#### Microcontrollers

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 436-4314

La Chantrerie BP 70602 44306 Nantes Cedex 3, France Tel: (33) 2-40-18-18-18

Fax: (33) 2-40-18-19-60 *ASIC/ASSP/Smart Cards*

Zone Industrielle 13106 Rousset Cedex, France Tel: (33) 4-42-53-60-00 Fax: (33) 4-42-53-60-01

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906, USA

Tel: 1(719) 576-3300 Fax: 1(719) 540-1759

Scottish Enterprise Technology Park Maxwell Building East Kilbride G75 0QR, Scotland

Tel: (44) 1355-803-000 Fax: (44) 1355-242-743

#### RF/Automotive

Theresienstrasse 2 Postfach 3535 74025 Heilbronn, Germany Tel: (49) 71-31-67-0 Fax: (49) 71-31-67-2340

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906, USA

Tel: 1(719) 576-3300 Fax: 1(719) 540-1759

#### **Biometrics**

Avenue de Rochepleine BP 123

38521 Saint-Egreve Cedex, France

Tel: (33) 4-76-58-47-50 Fax: (33) 4-76-58-47-60

Literature Requests www.atmel.com/literature

Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN ATMEL'S TERMS AND CONDITIONS OF SALE LOCATED ON ATMEL'S WEB SITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel's products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.

© 2007 Atmel Corporation. All rights reserved. Atmel<sup>®</sup>, logo and combinations thereof, Everywhere You Are<sup>®</sup> and others are registered trademarks or trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be trademarks of others.