# C2471 Datasheet

# RDFC Controllers for Offline Applications up to 6 W

### **ADVANTAGES**

- Low system component count

- High average efficiency

- Low no load power consumption

- EMI compliance without extra components

- High isolation & surge voltage withstand

- High power density in very small size

### **FEATURES**

- Highly integrated CMOS controller IC

- Low cost package options

- Drive suitable for low cost bipolar power transistors

- Resonant switching for high efficiency and low EMI

- Frequency optimised for power circuit parasitics

- Protection against overload, over-temperature and under-voltage

External AC/DC charger/adapter (single voltage input) e.g. cordless phones, low power adapters.

Embedded PSU (single voltage input), audio products, domestic appliances.

#### **OVERVIEW**

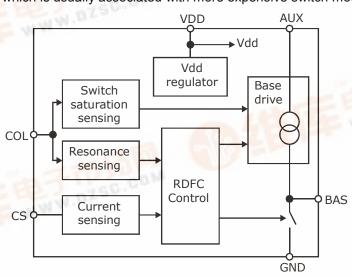

The C2471 controllers use CamSemi's low power Resonant Discontinuous Forward Converter (RDFC) topology to create a high efficiency, low cost alternative to line-frequency transformer PSUs, for applications up to 6 W. By operating in resonant mode, EMI is greatly reduced, enabling the replacement of linear PSUs in demanding applications such as audio products and cordless phone chargers. The C2471 controllers also offer overload protection which is usually associated with more expensive switch mode solutions.

Figure 1: Block Diagram of the C2471 Controller ICs

### PIN DEFINITIONS

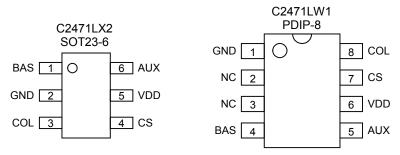

Figure 2: C2471 Pin Assignment (drawings are not to scale)

### **VDD Pin**

The VDD pin supplies power to the controller and is maintained at the correct voltage (nominally 3.3 V) by an internal shunt regulator.

#### **COL Pin**

The COL pin is used to sense the collector voltage of the primary switching transistor, via a coupling capacitor, to control the timing and current levels of the signals produced on the BAS pin.

### **CS Pin**

The CS pin senses the primary switch current via the current sensing resistor. The voltage sensed on this pin is used to control the operating modes to manage standby and overload protection. Operating characteristics are programmed via two external resistors.

#### **AUX Pin**

The AUX pin provides the supply current for the internal base driver block. The AUX pin is connected to the external supply rail via a current-limiting resistor to set the maximum base current.

#### **BAS Pin**

The BAS pin switches the external bipolar primary switch transistor on and off. The current supplied to the switch transistor is controlled to minimize the switching losses and thereby help optimize overall system efficiency.

#### **GND Pin**

GND pins provide the ground reference. Where the device has multiple GND pins, all must be connected to a common, low impedance path.

# TYPICAL APPLICATION CIRCUIT

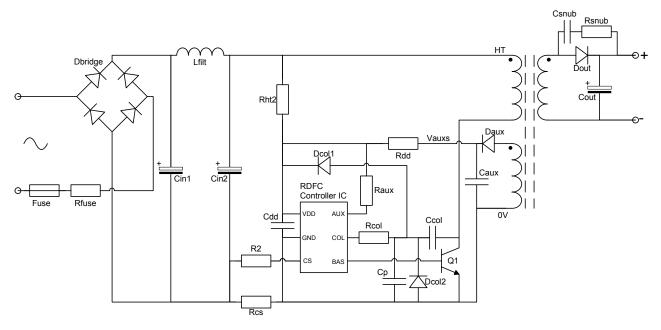

The C2471 controllers are intended primarily for single input voltage AC/DC applications, such as replacement of line frequency linear transformer power supplies. These versatile controllers support a wide range of applications at low cost. A typical circuit configuration is shown in Figure 3.

Figure 3: Typical Low Power RDFC Application Schematic

### **Typical Cordless Phone Adapters Using C2471**

The RDFC topology and CamSemi's C2471 controller deliver class-leading performance in cordless phone charger applications up to 6 W. Here are two examples of what can be typically achieved.

| Input               | 110 Vac                              | 230 Vac       |  |

|---------------------|--------------------------------------|---------------|--|

| Rated power         | 6 W                                  | 3 W           |  |

| Output              | 9 Vdc, 660 mA                        | 9 Vdc, 330 mA |  |

| Transformer core    | E <sup>.</sup>                       | 13            |  |

| Average efficiency  | 80                                   | %             |  |

| No-load power input | 150 mW                               |               |  |

| EMI compliance      | EN 55022 and FCC part 68 (TIA-968-A) |               |  |

Note: The C2471 controller is rated for applications up to 6 W.

### PRINCIPLE OF OPERATION

### Power-Up/Power-Down Sequences

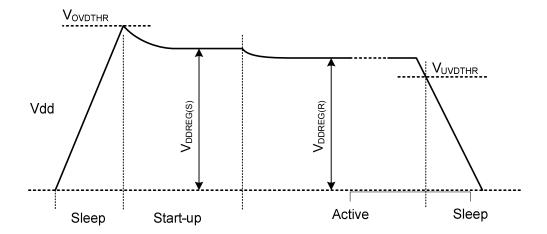

The C2471 controllers are powered via their VDD pins. When mains voltage is first applied, a small amount of current ( $I_{DDSLEEP}$ ) is drawn from the rectified mains input via high value start up resistors (Rht1 and Rht2 in Figure 3). When the voltage on the VDD pin ( $V_{DD}$ ) reaches a level  $V_{OVDTHR}$  the controller wakes up, demands more supply current ( $I_{DDWAKE}$ ) and enters the Start-up state (see Figure 4). The controller stays in Start-up for a short time during which internal circuit blocks are enabled and then changes to Active operation. In both Start-up and Active states, the controller uses an internal shunt regulator to regulate the  $V_{DD}$  rail voltage; the regulator is disabled in Sleep. A higher regulation voltage is applied during Start-up ( $V_{DDREG(S)}$ ) than during Active operation ( $V_{DDREG(R)}$ ) to help provide sufficient  $V_{DD}$  before the Auxiliary supply from the transformer rises to maintain  $V_{DD}$ .

If the VDD pin voltage drops below  $V_{\text{UVDTHR}}$  the controller goes back to Sleep, reducing the supply current demand. The system will restart when input power is restored. To achieve a smooth power up sequence the  $V_{\text{DD}}$  reservoir capacitor needs to be large enough to sustain the supply above  $V_{\text{UVDTHR}}$  over the Start-up period.

Figure 4: VDD Pin Waveform (VDD) During Initial Power-up and Power-down

| State    | Description                                                                                                                                                                                                                                                                                                                                                         |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Sleep    | From initial application of power or from Active state if $V_{DD}$ falls below $V_{UVDTHR}$ , the controller changes to Sleep state. Non-essential controller circuits are powered down and the external switching transistor (Q1) is held off. Exit from Sleep state occurs when $V_{DD}$ rises above $V_{OVDTHR}$ and the controller moves to the Start-up state. |

| Start-up | When the Start-up state is entered, internal controller circuits are activated and power conversion begins (Standby mode – see Table 2). In Start-up the on-chip shunt regulator stabilises $V_{DD}$ to an intermediate value, $V_{DDREG(S)}$ . After a preset time, the controller changes from Start-up to Active operation.                                      |

| Active   | Converter operation continues, the shunt regulator controls $V_{DD}$ to the lower $V_{DDREG(R)}$ . If $V_{DD}$ falls below $V_{UVDTHR}$ the controller ceases converter operation and reverts to Sleep state.                                                                                                                                                       |

Table 1: Summary of Low Power RDFC Controller States

## Start-up and Active State Power Conversion Modes

In the Start-up and Active states the C2471 ICs have several modes for controlling power conversion that are designed to achieve maximum efficiency and to limit power (current) across a wide range of loads. Refer to Table 2 for a summary of each mode.

| Mode           | Typical Load<br>Range                                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------|--------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Standby        | I <sub>OUT</sub> ≥ 0% to<br>~20% of rated<br>current   | Standby mode reduces power consumption at low loads. It achieves this by progressively reducing the on-time then by increasing the off-time as the load decreases. As load increases, the converter duty is increased until the controller returns to Normal mode. Typically, mains ripple causes change of operating mode during each mains half-cycle, with the converter moving to lower-power modes between peaks of the mains voltage.                      |

| Normal         | I <sub>OUT</sub> > ~20% to<br>100% of rated<br>current | Normal mode is used for steady state power delivery. During Normal mode the power device switches in a fully resonant minimum-voltage-switching waveform, with the off-time determined by the transformer resonance ( $T_{RES}$ ) and the on-time being equal to 75% of the off time. A low level of primary switch current, sensed via the CS pin voltage, causes the controller to change to Standby mode and a high level to Overload mode.                   |

| Overload       | I <sub>OUT</sub> >~100%<br>rated current               | Overload mode is activated at high output loads. In this mode the on-time of the primary switch is terminated early (before 75% of T <sub>RES</sub> ) when the primary current exceeds a preset maximum, thereby protecting the primary switch and limiting the output current. This results in reduction of the output voltage. Heavy overload (sensed by the on-period of the primary switch reducing below a preset time) causes Foldback mode to be entered. |

| Foldback       | V <sub>OUT</sub> < ~70% rated output                   | Foldback mode is entered from the Overload mode. In this mode the controller reduces the on/off duty cycle to protect the power supply and any connected load by both shortening the on-period and increasing the off-period of the primary switch. Converter cycles continue to maintain auxiliary power to the controller. The controller exits the Foldback mode and enters the Power Burst mode after a fixed number of power conversion cycles.             |

| Power<br>Burst | V <sub>OUT</sub> < ~70% rated output                   | Power Burst mode is entered periodically from Foldback mode in order to restart the power supply output. In Power Burst mode, the controller operates at maximum delivered power for a set number of power converter cycles. At the end of the burst, if the load is not excessive, the converter goes to Normal mode; otherwise it reverts to Foldback mode.                                                                                                    |

Table 2: Summary of Active Operating Modes

When the controller goes from Sleep to Start-up state, its power conversion mode is set to Standby. Typically the converter output voltage is low at this time so the primary switch current is high during the first few converter cycles. This causes the operating mode to change quickly to Normal or Overload mode.

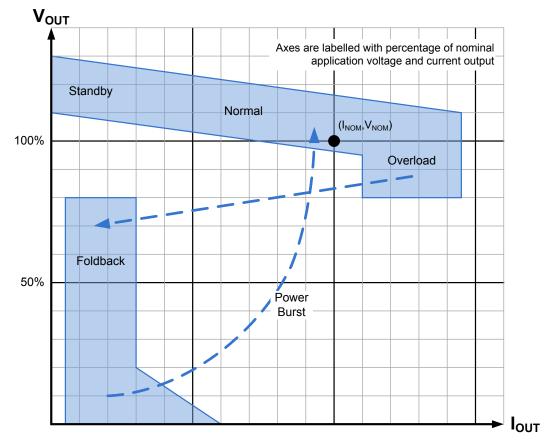

## Low Power RDFC Power Supply I-V Characteristic

Figure 5 illustrates a typical low power RDFC power supply characteristic with the various Active state modes of operation identified.  $I_{NOM}$  and  $V_{NOM}$  are the nominal output voltage and current drawn by the load at the rated power of the application circuit.

Figure 5: Typical Low Power RDFC Power Supply Characteristic Indicating Different Active Modes of Operation

The exact thresholds for transition between modes depend on specific application characteristics, controller internal clock frequency ( $F_{CLK}$ ) and CS pin thresholds ( $V_{OCPH}$  and  $V_{OCPL}$ ). These parameters and their effects are explained later.

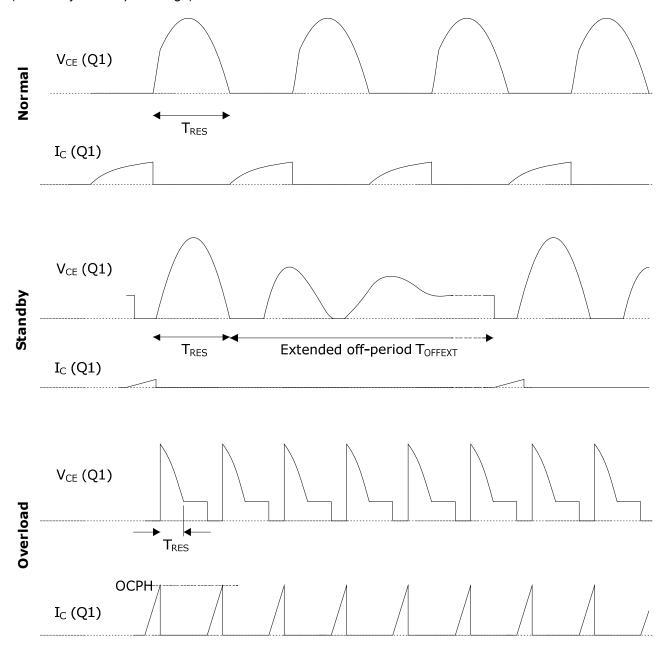

# **Switching Waveforms**

The collector voltage ( $V_{CE}$ ) and current ( $I_C$ ) waveforms of the primary switching transistor (Q1 in Figure 3) are shown in Figure 6.  $T_{RES}$  is the duration of the transformer resonance during the off period. Note that in Overload mode, the primary switch Q1 is turned off when the current exceeds the protection level OCPH (sensed by the CS pin voltage).

Figure 6: Typical Switch (Q1) Collector Voltage (V<sub>CE</sub>) and Current (I<sub>C</sub>) Waveforms

#### **Resonance Control**

The natural resonance of the transformer and associated components is deduced from the current flowing into and out of the COL pin via the collector coupling capacitor.

The voltage sensed on the COL pin is used to control saturation of the primary switch transistor (Q1 in Figure 3) during the on-period (see "Optimised Base Drive"). During the off-period, timing of the resonance is detected via the current in and out of the pin, which has a low impedance path to GND during this time. Rate of change of voltage at the transformer primary causes current into or out of the COL pin, which is processed to measure the resonance period  $T_{RES}$  and to find the optimum turn-on time for the following conversion cycle. The resonant period is also used to determine the maximum on-time of the primary switch transistor, so that

$$T_{ON} = 0.75 \times T_{RES}$$

The maximum duty cycle ( $D_{NORMAL}$ ) is therefore nominally 43%. On-time of the switch is controlled to manage power delivery and is reduced in both low-load and overload conditions. The minimum on-time in overload is determined by the internal CS blanking, specified as  $T_{CSBLANK}$ .

At turn-on of the primary switching transistor, its collector voltage can fall very rapidly, with correspondingly large current out of or in to the COL pin via the coupling capacitor (Ccol). An on-chip clamp transistor, controlled by an internal signal called ACTICLAMP, provides a low resistance path to GND. This transistor is turned on shortly before turn-on of the primary switch and remains on until time  $T_{ACT}$  after turn-on of the primary switch. It is then turned off during the remainder of the primary switch on-period. In some applications, the current through the coupling capacitor may develop sufficient voltage across the clamp transistor to cause conduction of the ESD protection diodes. This is permissible up to a limit  $I_{COL}$  which is specified in ABSOLUTE MAXIMUM RATINGS. If, due to application design, the capacitor current could exceed this level, external protection diodes and a resistor must be provided (Dcol1, Dcol2 and Rcol in Figure 3).

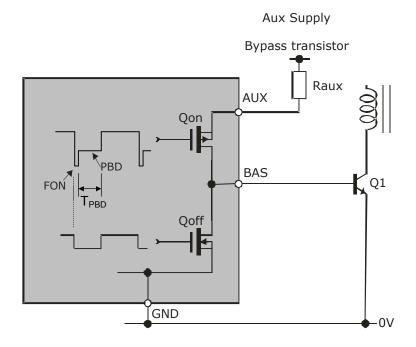

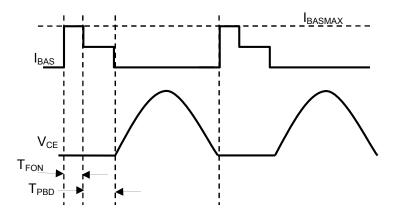

### **Optimised Base Drive**

To minimize losses in the primary switching transistor (Q1) its base current is carefully controlled. To minimize turn-on losses, the base current is initially forced to a maximum value  $I_{BASMAX}$  for a time  $T_{FON}$  (the force-on or "FON" pulse). For the remainder of the on-time the base current is reduced to a lower value such that the on-state collector voltage is maintained at a preset target voltage, thereby minimizing turn-off time and consequent losses. During this period,  $T_{PBD}$ , the so called "proportional base drive" (PBD) current is referred to as  $I_{BASPBD}$ .

Figure 7: Primary Switch (Q1) Base Drive

The BAS pin (see Figure 7) is driven by two transistors, Qon and Qoff. Qon provides  $I_{BASMAX}$  during  $T_{FON}$  and  $I_{BASPBD}$  during the remainder of the on-period. Transistor Qoff provides a low-resistance ( $R_{BASCLAMP}$ ) path to GND during the off-period to ensure rapid turn-off of the primary switch, Q1.  $I_{BASPBD}$  is set by the PBD system within the controller but  $I_{BASMAX}$  is determined by the external resistor Raux and the Aux Supply voltage.

Figure 8: Base Driver Current Waveforms

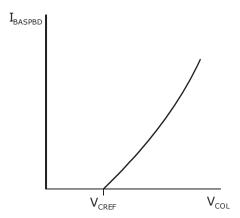

$I_{BASPBD}$  is controlled by monitoring the voltage at the COL pin during  $T_{PBD}$ ; base current is increased progressively as  $V_{COL}$  rises above threshold  $V_{CREF}$  (see Figure 9). The desired on-state  $V_{CE}$  of the switching transistor is set by capacitors Cp and Ccol (see Figure 3), the COL pin capacitance ( $C_{INCOL}$ ) and  $V_{CREF}$ .

Figure 9: I<sub>BASPBD</sub> characteristic

#### **Power Control**

Load conditions are sensed on a cycle-by-cycle basis via the CS pin. When low levels of output power demand are detected, the controller progressively reduces the switching duty cycle to reduce power consumption and to improve output voltage regulation. Power demand causes increase in duty up to the maximum, or until Overload is detected.

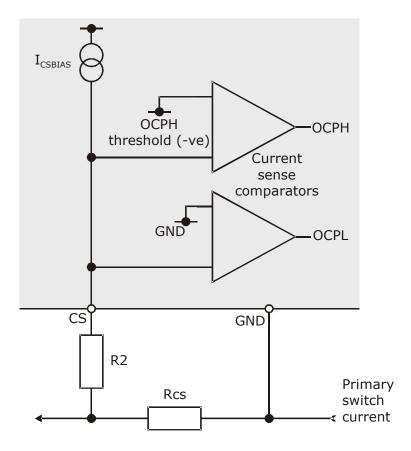

The voltage at the CS pin is compared to two thresholds, one nominally at GND voltage ( $V_{\text{OCPL}}$ ) to generate an internal signal OCPL and the other at a negative threshold ( $V_{\text{OCPH}}$ ) to generate an internal signal OCPH. The controller samples OCPL a short time ( $T_{\text{OCPL}}$ ) after turn-on of the primary switch. A negative voltage at the CS pin indicates power demand so the controller increases the switching duty up to the maximum; conversely a positive voltage causes a decrease in duty.

Excessive primary switch current, detected via OCPH, terminates the on-period of the primary switch to limit power delivery (Overload mode). High levels of overload (when the converter output voltage held is low by the load) causes OCPH to trigger soon after turn-on of the primary switch. This condition is detected by the controller sampling OCPH at time  $T_{FBTHR}$  after turn-on. If OCPH triggers within this time, the controller changes to Foldback mode. To prevent mis-triggering, OCPH is blanked for a short period  $T_{CSBLANK}$  after turn-on.

The effective thresholds for current through the primary switch for both power reduction (OCPL) and overload (OCPH) are programmed by the current-sense resistors connected to the CS pin as shown in Figure 10.

Figure 10: Current Sense Diagram

The internal current source (I<sub>CSBIAS</sub>) develops an offset voltage across the series resistor (R2 in Figure 10) so setting OCPL current threshold. Switch current in excess of overload (OCPH) is detected using a fixed threshold voltage but the contribution from the offset voltage across R2 has to be taken into account.

$I_{OCPL}$  threshold current =  $(V_{OCPL} + I_{CSBIAS}.R2)/Rcs$

$I_{\text{OCPH}}$  threshold current = ( $V_{\text{OCPH}} + I_{\text{CSBIAS}}.R2$ )/Rcs

$$R2 = \frac{V_{OCPH} \cdot I_{OCPL} - V_{OCPL} \cdot I_{OCPH}}{I_{OCPH} \cdot I_{CSBIAS} - I_{OCPL} \cdot I_{CSBIAS}}$$

$$Rcs = \frac{V_{OCPH} - V_{OCPL}}{I_{OCPH} - I_{OCPL}}$$

Note: I<sub>OCPL</sub>, I<sub>OCPH</sub>, V<sub>OCPH</sub> IC<sub>SBIAS</sub> are all positive magnitude in these formulae

#### **Protection Features**

CamSemi

#### Collector De-saturation (Over Voltage) Protection (COVP)

To protect the primary switch from excessive power dissipation, the on-state voltage of the primary switching transistor is limited by the controller. The controller will go to Foldback mode if the COL pin voltage is greater than V<sub>COVP</sub> at the end of the on-time for four consecutive cycles.

#### **Over-temperature Protection (OTP)**

Temperature sensing is integrated with the controller. If the temperature of the die rises above the shutdown temperature, T<sub>SH</sub>, the BAS output is inhibited. It restarts once the temperature has fallen more than T<sub>SH (HYST)</sub> below T<sub>SH</sub>. In typical applications "hiccup" operation will occur. While BAS is inhibited, the device is active and draws I<sub>DDWAKE</sub>. This causes V<sub>DD</sub> to fall since auxiliary power is not provided by the transformer. Once V<sub>DD</sub> reaches V<sub>UVDTHR</sub>, the controller enters the Sleep state and I<sub>DD</sub> falls to I<sub>DDSLEEP</sub> allowing V<sub>DD</sub> to rise again (via the resistors Vht1 and Vht2). When V<sub>DD</sub> reaches V<sub>OVDTHR</sub> reset occurs and the controller re-starts. If the die temperature is below T<sub>SH</sub>, BAS operation continues but if it is still above T<sub>SH</sub>, BAS operation ceases after a short period and the hiccup cycle repeats.

#### **Primary Switch Over-current Protection (OCP)**

To protect the primary switch, the base drive is turned off if the primary switch current rises too high, sensed via the CS input voltage falling below a preset negative threshold V<sub>OCPH</sub>. See also Power Control on page 10.

#### **Output Overload/Short-circuit Protection**

If the application circuit is overloaded beyond a certain limit the controller goes into Foldback mode with reduced duty cycle, protecting the primary switch by reducing its power dissipation. Transition to Foldback mode is triggered by the CS pin voltage crossing the V<sub>OCPH</sub> threshold within a time T<sub>FBTHR</sub> of the start of the FON pulse. This typically happens when the load holds the output voltage low. See also Power Control on page 10.

#### **Under Voltage Protection**

The controller is prevented from operating if the  $V_{DD}$  supply is inadequate ( $V_{DD} < V_{UVDTHR}$ ). Once the controller has stopped operation it will not restart until the V<sub>DD</sub> supply voltage rises above V<sub>OVDTHR</sub>.

# **ABSOLUTE MAXIMUM RATINGS**

CAUTION: Permanent damage may result if a device is subjected to operating conditions at or in excess of absolute maximum ratings. Current flowing into a pin is taken to be positive.

| Parameter                          | Symbol            | Condition                                                       |                                             | Min  | Max                   | Units |

|------------------------------------|-------------------|-----------------------------------------------------------------|---------------------------------------------|------|-----------------------|-------|

| Supply voltage                     | $V_{DD}$          |                                                                 |                                             |      | 4.6                   | V     |

| Input voltage AUX                  | V <sub>AUX</sub>  |                                                                 |                                             | -0.5 | V <sub>DD</sub> + 0.5 | V     |

| Input voltage BAS                  | $V_{BAS}$         |                                                                 |                                             | -0.5 | V <sub>DD</sub> + 0.5 | V     |

| Input voltage CS                   | V <sub>CS</sub>   |                                                                 |                                             | -0.5 | V <sub>DD</sub> + 0.5 | V     |

| Input voltage COL                  | V <sub>COL</sub>  |                                                                 |                                             | -0.5 | V <sub>DD</sub> + 0.5 | V     |

| Pin current VDD                    | $I_{DD}$          |                                                                 |                                             | -100 | 30                    | mA    |

| Pin current AUX                    | I <sub>AUX</sub>  | While Qon is on (Figure 7), duty < 30 %, V <sub>BAS</sub> > 0 V |                                             | -100 | 260                   | mA    |

|                                    |                   | All other conditions                                            |                                             | -100 | 100                   | mA    |

|                                    |                   | While Qoff is on (Figure 7), duty                               | T <sub>j</sub> < 125 °C                     | -100 | 220                   | mA    |

|                                    |                   | < 30%                                                           | T <sub>j</sub> < 100 °C                     | -100 | 400                   | mA    |

| Pin current BAS                    | I <sub>BAS</sub>  | While Qon is on (Figure 7), duty < 30 %, V <sub>BAS</sub> > 0 V |                                             | -260 | 100                   | mA    |

|                                    |                   | While Qon is on (Figure 7), duty < 30 % V <sub>BAS</sub> < 0 V  | In FON                                      | -190 | 100                   | mA    |

|                                    |                   |                                                                 | In PBD                                      | -122 | 100                   | mA    |

|                                    |                   | All other conditions                                            |                                             | -100 | 100                   | mA    |

| Pin current CS                     | Ics               |                                                                 |                                             | -100 | 100                   | mA    |

|                                    |                   | During PBD: ESD diode limit, input is high impedance            |                                             | -100 | 100                   | mA    |

| Pin current COL                    | I <sub>COL</sub>  | During turn-on transient (ACTICLA                               | During turn-on transient (ACTICLAMP active) |      | 250                   | mA    |

|                                    |                   | During resonance off period                                     |                                             | -125 | 250                   | mA    |

| Junction temperature               | TJ                |                                                                 |                                             | -25  | 125                   | °C    |

| Storage temperature                | T <sub>STOR</sub> |                                                                 |                                             | -40  | 150                   | °C    |

| Lead temperature (soldering, 10 s) | T∟                |                                                                 |                                             |      | 260                   | °C    |

| ESD withstand                      |                   | Human body model, JESD22-A11                                    | 4                                           |      | 2                     | kV    |

| LOD WILLISTATIO                    |                   | Charged device model, ANSI-ESI                                  | D-STM5.3.1                                  |      | 500                   | V     |

# NORMAL OPERATING CONDITIONS

| Parameter              | Symbol              | Condition                                                   | Min | Тур                    | Max  | Units               |

|------------------------|---------------------|-------------------------------------------------------------|-----|------------------------|------|---------------------|

| Supply voltage         | $V_{DD}$            | VDD pin, limited by internal regulator                      | 3.1 | 3.3                    | 3.5  | V                   |

| Junction temperature   | $T_J$               | Over temperature protection operates at higher temperatures | -25 | 25                     | 100  | °C                  |

| Internal digital clock | F <sub>CLK</sub>    | $V_{DD}=V_{DDREG(R)}$                                       | 6.7 |                        | 11.7 | MHz                 |

| frequency              | F <sub>CLKTC</sub>  | Temperature coefficient                                     |     | +13                    |      | kHz°C <sup>-1</sup> |

| Switching frequency,   | F <sub>MAX</sub>    | Determined by T <sub>RES</sub> (F <sub>CLK</sub> in MHz)    |     | F <sub>CLK</sub> / 61  |      | MHz                 |

| Normal mode            | $F_{MIN}$           |                                                             |     | F <sub>CLK</sub> / 490 |      | MHz                 |

| Transformer            | T <sub>RESMIN</sub> | Natural resonance of transformer and                        |     | 35 / F <sub>CLK</sub>  |      | μs                  |

| resonance time         | T <sub>RESMAX</sub> | associated capacitances. F <sub>CLK</sub> in MHz.           |     | 280 / F <sub>CLK</sub> |      | μs                  |

| Supply current         | I <sub>DD</sub>     | Limit externally                                            |     |                        | 30   | mA                  |

# **ELECTRICAL CHARACTERISTICS**

Unless otherwise stated:

- 1. Min and Max electrical characteristics apply over normal operating conditions.

- 2. Typical electrical characteristics apply at  $T_J = T_{JTYP}$  and  $V_{DD} = V_{DDTYP}$

- 3. Functionality and performance is not defined when a device is subjected to conditions outside the range of normal operating conditions and device reliability may be compromised.

- 4. For parameters dependent on F<sub>CLK</sub>, the value of F<sub>CLK</sub> in MHz should be used in calculations.

### **VDD Pin**

| Parameter                                   | Symbol                | Condition                                                                                                                                   | Min | Тур | Max | Units |

|---------------------------------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| Regulation voltage                          | $V_{\text{DDREG(R)}}$ | Active state, 2.5 mA < I <sub>DD</sub> < 30 mA                                                                                              | 3.1 | 3.3 | 3.5 | V     |

| Regulation voltage                          | $V_{\text{DDREG(S)}}$ | Start-up state, 2.5 mA < I <sub>DD</sub> < 30 mA                                                                                            |     | 4   |     | V     |

| Quiescent current                           | I <sub>DDSLEEP</sub>  | Sleep state, V <sub>DD</sub> < V <sub>UVDTHR</sub>                                                                                          |     |     | 8   | μΑ    |

| Residual supply current                     | I <sub>DDWAKE</sub>   | Start-up & Active states, Normal mode $(V_{DDREG(R)} - 300 \text{ mV}) < V_{DD}$ and $V_{DD} < (V_{DDREG(R)} - 100 \text{ mV})$ , Tj<100 °C | 0.7 |     | 1.8 | mA    |

| OVD threshold, Sleep                        | Vovdthr               | Sleep state                                                                                                                                 | 3.5 |     | 4.5 | V     |

| UVD threshold                               | V <sub>UVDTHR</sub>   | Start-up and Active states                                                                                                                  | 2.7 |     | 3.2 | V     |

| V <sub>DDREG(R)</sub> - V <sub>UVDTHR</sub> |                       | I <sub>DD</sub> < 30 mA                                                                                                                     | 150 |     |     | mV    |

#### **AUX Pin**

| Parameter        | Symbol  | Condition      |                           | Min  | Тур  | Max  | Units |

|------------------|---------|----------------|---------------------------|------|------|------|-------|

| ALIV nin voltage | V       | BAS = 800 mV   | $I_{AUX} = 10 \text{ mA}$ |      | 1.05 |      | V     |

| AUX pin voltage  | VAUXFON | BAS - 600 IIIV | I <sub>AUX</sub> = 80 mA  | 1.21 | 1.48 | 1.75 | V     |

### **CS Pin**

| Parameter                     | Symbol               | Condition                                                                   | Min  | Тур                            | Max  | Units |

|-------------------------------|----------------------|-----------------------------------------------------------------------------|------|--------------------------------|------|-------|

| OCPH comparator threshold     | V <sub>OCPH</sub>    | 0 °C < T <sub>J</sub> < 100 °C                                              | -260 |                                | -235 | mV    |

| OCPL comparator threshold     | $V_{\text{OCPL}}$    | T <sub>J</sub> = 25 °C                                                      | -6   |                                | 6    | mV    |

| OCPH comparator response time | T <sub>OCP</sub>     | Step CS input from $V_{CS} > -200 \text{ mV}$ to $V_{CS} < -300 \text{ mV}$ |      |                                | 0.1  | μs    |

| Bias current                  | I <sub>CSBIAS</sub>  | -25 °C < T <sub>J</sub> < 100 °C                                            | 35.0 |                                | 70.0 | μΑ    |

| Dias current                  |                      | T <sub>j</sub> = 25°C                                                       | 38.0 |                                | 63.0 | μA    |

| OCPL sampling time            | T <sub>OCPL</sub>    | F <sub>CLK</sub> in MHz                                                     |      | 19 / F <sub>CLK</sub><br>- 0.1 |      | μs    |

| Blanking period               | T <sub>CSBLANK</sub> | F <sub>CLK</sub> in MHz                                                     |      | 4 / F <sub>CLK</sub><br>- 0.1  |      | μs    |

| Foldback threshold time       | $T_{FBTHR}$          | F <sub>CLK</sub> in MHz                                                     |      | 26 / F <sub>CLK</sub><br>- 0.1 |      | μs    |

# **BAS Pin**

| Parameter                      | Symbol                   | Condition                                                                                 | Min | Тур                                           | Max | Units  |

|--------------------------------|--------------------------|-------------------------------------------------------------------------------------------|-----|-----------------------------------------------|-----|--------|

| Base drive current (FON)       | I <sub>BASMAX</sub>      |                                                                                           | 90  |                                               |     | mA     |

| Base drive current (PBD)       | I <sub>BASPBD</sub>      | V <sub>COL</sub> = V <sub>DD</sub> , V <sub>AUX</sub> = 2.1 V                             | 22  |                                               |     | mA     |

| Base clamp turn-off resistance | R <sub>BASCLAMP</sub>    | V <sub>BAS</sub> = 400 mV, -25 °C < T <sub>J</sub> < 100 °C                               |     |                                               | 8.5 | Ω      |

| Duty cycle                     | D <sub>NORMAL</sub>      | Normal mode                                                                               |     | 43                                            |     | %      |

| Force-on period                |                          | Standby mode                                                                              |     | 150                                           |     | ns     |

| (depends on F <sub>CLK</sub> ) | T <sub>FON</sub>         | Normal, Foldback & Power Burst modes                                                      |     | 650                                           |     | ns     |

| Minimum on-period              | T <sub>ONMIN</sub>       | Standby (F <sub>CLK</sub> in MHz)                                                         |     | 20 / F <sub>CLK</sub>                         |     | μs     |

| Maximum off-period             | T <sub>OFFMAX</sub>      | Standby (F <sub>CLK</sub> in MHz)                                                         |     | 1920 / F <sub>CLK</sub><br>+ T <sub>RES</sub> |     | μs     |

| Power Burst mode               | N <sub>BURST</sub>       | Burst length, number of converter cycles                                                  |     | 22144                                         |     | cycles |

| 1 ower Burst mode              | T <sub>BURSTCYCMIN</sub> | Minimum converter cycle period in Power Burst mode <sup>1</sup> (F <sub>CLK</sub> in MHz) |     | 39 / F <sub>CLK</sub>                         |     | μs     |

|                                | N <sub>FOLD</sub>        | Foldback duration between bursts, number of converter cycles                              |     | 18326                                         |     | cycles |

| Foldback mode                  | T <sub>FOLDCYCMIN</sub>  | Converter period in Foldback mode <sup>2</sup> (F <sub>CLK</sub> in MHz)                  |     | 900 / F <sub>CLK</sub> + T <sub>RES</sub>     |     | μs     |

|                                | T <sub>OFFEXTMIN</sub>   | Extended off time (F <sub>CLK</sub> in MHz)                                               |     | 896 / F <sub>CLK</sub>                        |     | μs     |

$<sup>^{1}</sup>$  Minimum converter period =  $T_{RES}$  +  $T_{ONMIN}$   $^{2}$  Minimum converter period =  $T_{RES}$  +  $T_{OFFEXT}$  +  $T_{ONMIN}$

### **COL Pin**

| Parameter                                          | Symbol             | Condition                                                                       | Min                | Тур                           | Max                | Units             |

|----------------------------------------------------|--------------------|---------------------------------------------------------------------------------|--------------------|-------------------------------|--------------------|-------------------|

| Rising edge<br>comparator<br>threshold             | I <sub>CRISE</sub> | -25 °C < T <sub>J</sub> < 100 °C                                                | 0.25               |                               | 1.00               | mA                |

| Falling edge<br>comparator<br>threshold            | I <sub>CFALL</sub> | -25 °C < T <sub>J</sub> < 100 °C                                                | -1.00              |                               | -0.25              | mA                |

| Collector over-<br>voltage comparator<br>threshold | $V_{COVP}$         |                                                                                 | 0.7V <sub>DD</sub> |                               | 0.9V <sub>DD</sub> | V                 |

| PBD threshold voltage                              | $V_{CREF}$         | Intercept of characteristic<br>5 mA < I <sub>BAS</sub> < 20mA<br>(see Figure 9) | 0.76               | 0.92                          | 1.10               | V                 |

| PBD transconductance                               |                    |                                                                                 |                    | 95                            |                    | mAV <sup>-1</sup> |

| Input leakage current                              |                    | T <sub>J</sub> < 100 ° C                                                        | -650               |                               | 650                | nA                |

| Input capacitance                                  | CINCOL             | V <sub>COL</sub> = 1 V                                                          | 25                 | 28                            | 31                 | pF                |

| ACTICLAMP                                          | T <sub>ACT</sub>   | Standby mode (F <sub>CLK</sub> in MHz)                                          |                    | 3 / F <sub>CLK</sub> – 0.1    |                    | μs                |

| duration after FON                                 | I ACT              | Normal, Foldback and Power Burst modes (F <sub>CLK</sub> in MHz)                |                    | 4 / F <sub>CLK</sub> –<br>0.1 |                    | μs                |

# THERMAL CIRCUIT PROTECTION

| Parameter                    | Symbol                 | Condition   | Min | Тур | Max | Units |

|------------------------------|------------------------|-------------|-----|-----|-----|-------|

| Thermal shutdown temperature | T <sub>SH</sub>        | At junction |     | 115 |     | °C    |

| Thermal shutdown hysteresis  | T <sub>SH (HYST)</sub> | At junction |     | 35  |     | °C    |

# PACKAGE THERMAL RESISTANCE CHARACTERISTICS

#### Conditions:

- 1. Controller IC mounted on typical PCB (1.6 mm thick, 35  $\mu$ m copper, CEM1);

- 2.  $\theta_{JP}$  measured to pin terminal of device at the surface of the PCB.

| Package | Junction-to-pin<br>θ <sub>JP</sub> (Typical) | Junction-to-ambient<br>θ <sub>JA</sub> (Typical) | Units  |

|---------|----------------------------------------------|--------------------------------------------------|--------|

| SOT23-6 | 60                                           | 170                                              | °C / W |

| PDIP-8  | 35                                           | 105                                              | °C / W |

# PACKAGE AND ORDERING INFORMATION

# **Package Marking**

The PDIP-8 (C2471LW1) package is marked with the full product type number. The SOT23-6 package (C2471LX2) is marked with a short code **FB** as illustrated in Figure 11.

Figure 11: C2471LX2 SOT23-6 Package Marking

# **Ordering**

| Туре     | Package | Packing Form    | Order         |

|----------|---------|-----------------|---------------|

| C2471LX2 | SOT23-6 | 7" Tape & Reel  | C2471LX2-TR7  |

|          |         | 13" Tape & Reel | C2471LX2-TR13 |

| C2471LW1 | PDIP-8  | Tube            | C2471LW1-T1   |

For further package and ordering information please contact CamSemi.

# C2471 Datasheet

### RDFC Controllers for Offline Applications up to 6 W

### **DATASHEET STATUS**

The status of this Datasheet is shown in the footer. Always refer to the most current version.

| Datasheet Status | Product<br>Status | Definition                                                                                                                                                                                                                |  |

|------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Product preview  | In development    | The Datasheet contains target specifications relating to design and development of the described IC product. Application circuits are illustrative only. Specifications are subject to change without notice.             |  |

| Preliminary      | In qualification  | The Datasheet contains preliminary specifications relating to functionality and performance of the described IC product. Application circuits are illustrative only. Specifications are subject to change without notice. |  |

| Product data     | In production     | The Datasheet contains specifications relating to functionality and performance of the described IC product. Application circuits are illustrative only. Specifications are subject to change without notice.             |  |

### **CONTACT DETAILS**

Cambridge Semiconductor Ltd St Andrew's House St Andrew's Road Cambridge CB4 1DL United Kingdom

Phone: +44 (0)1223 446450 Fax: +44 (0)1223 446451

Email: sales.enquiries@camsemi.com

Web: www.camsemi.com

### **DISCLAIMER**

The product information provided herein is believed to be accurate and is provided on an "as is" basis. Cambridge Semiconductor Ltd (CamSemi) assumes no responsibility or liability for the direct or indirect consequences of use of the information in respect of any infringement of patents or other rights of third parties. Cambridge Semiconductor Ltd does not grant any licence under its patent or intellectual property rights or the rights of other parties.

Any application circuits described herein are for illustrative purposes only. In respect of any application of the product described herein Cambridge Semiconductor Ltd expressly disclaims all warranties of any kind, whether express or implied, including, but not limited to, the implied warranties of merchantability, fitness for a particular purpose and non-infringement of third party rights. No advice or information, whether oral or written, obtained from Cambridge Semiconductor Ltd shall create any warranty of any kind. Cambridge Semiconductor Ltd shall not be liable for any direct, indirect, incidental, special, consequential or exemplary damages, howsoever caused including but not limited to, damages for loss of profits, goodwill, use, data or other intangible losses.

The products and circuits described herein are subject to the usage conditions and end application exclusions as outlined in Cambridge Semiconductor Ltd Terms and Conditions of Sale which can be found at <a href="https://www.camsemi.com/legal">www.camsemi.com/legal</a>.

Cambridge Semiconductor Ltd reserves the right to change specifications without notice. To obtain the most current product information available visit <a href="https://www.camsemi.com">www.camsemi.com</a> or contact us at the address shown above.