**CAST****C32025**

# Digital Signal Processor Megafunction

## General Description

The C32025 is a 16-bit fixed-point digital signal processor core. It combines the flexibility of a high-speed controller with the numerical capability of an array processor. The C32025 has the same instruction set as the TMS320C25 and also provides the same interrupts, serial interface and timer.

Developed for easy reuse with ASICs or FPGAs, the core requires under 18000 ASIC gates.

## Applications

- Digital sound processing (adaptive filtering, FFT, other special sound effects)

- Voice recognition

- Telecommunications (modems, codecs)

- Medical equipment (diagnostics tools)

- Computers peripherals

- Various embedded data-intensive systems

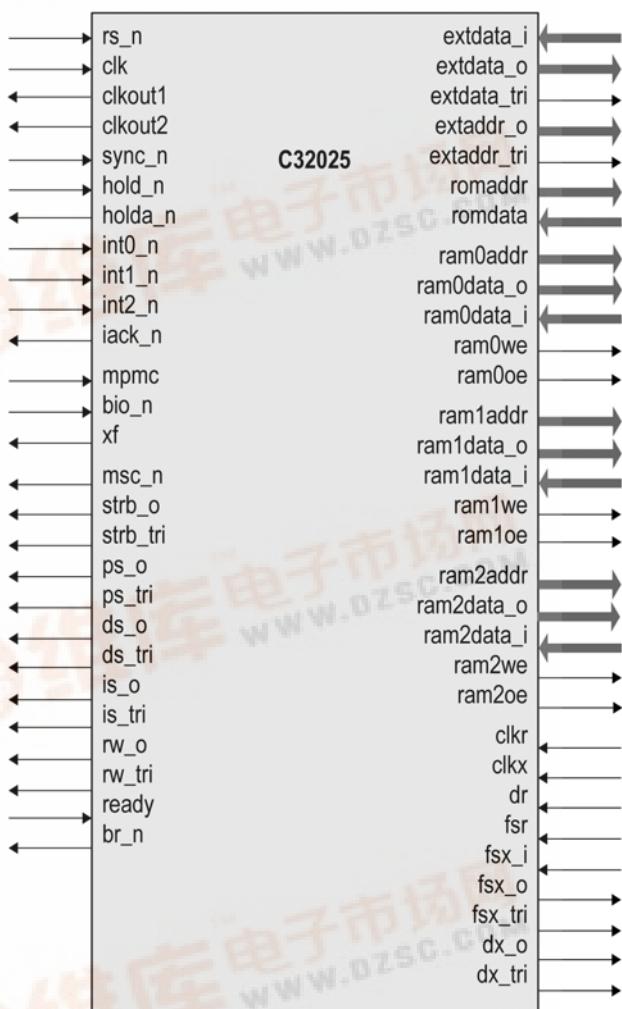

## Symbol

## Features

- Control Unit

- 16-bit instruction decoding

- Repeat instructions for efficient use of program space and enhanced execution

- Central Arithmetic-Logic Unit

- 16-bit parallel shifter; 32-bit arithmetic and logical operations

- 16 x 16 bit parallel multiplier with a 32-bit product

- 32-bit accumulator with output shifter

- Single-cycle Multiply-and-Accumulate instructions

- Auxiliary Registers

- 8 16-bit registers for indirect addressing or temporary data storage

- 16-bit Auxiliary Register Arithmetic Unit including operations with reversed-carry propagation

- Memory addressing modes

- Direct - using a 9-bit Page Pointer and instruction word's lowest 7-bits

- Indirect – using the Auxiliary Register File

- Immediate – less than 16-bit via instruction word or full 16-bit long immediate following the instruction word

- Block moves for data/program management

- 8-level Hardware Stack

- Interrupt Controller: 6 interrupt sources, excluding reset and a software interrupt

- Synchronous serial port for direct codec interface

- 16-bit reload timer

- Program Memory organization

- 4K-words of internal ROM

- Internal 256-word RAM block configurable either as program or data space

- 64K-word external program space

- Data Memory organization

- 2 Internal 256-word and one 32-word RAM blocks

- 64K-words of external data space

- 6 memory mapped registers

- 16 Input and 16 Output channels

- Wait states for interfacing slower off-chip devices

- Multiprocessing support

- Global data memory interface

- Synchronization input for synchronous multiprocessor configurations

- Concurrent DMA using an extended Hold operation

- Design is strictly synchronous with positive-edge clocking and synchronous reset, no internal tri-states.

## Pin Description

| Name     | Type | Polarity/<br>Bus size | Description                                                                                                   |

|----------|------|-----------------------|---------------------------------------------------------------------------------------------------------------|

| clk      | I    | Rise                  | <b>Master clock input</b><br>All internal synchronous circuits clock                                          |

| clkout1  | O    | -                     | <b>Master clock output</b> (fclk/4)<br>When High it indicates internal quarter-phases Q3 and Q4               |

| clkout2  | O    | -                     | <b>Second clock output</b> (fclk/4)<br>When High it indicates internal quarter-phases Q2 and Q3               |

| rs_n     | I    | Low                   | <b>Hardware reset input</b><br>Active for 2 cycles resets the device                                          |

| mpmc     | I    | -                     | <b>Microprocessor/microcomputer mode</b><br>When Low the internal ROM is mapped into program space            |

| sync_n   | I    | Fall                  | <b>Synchronization input</b><br>Forces the internal quarter-phase to Q1                                       |

| hold_n   | I    | Low                   | <b>Hold input</b><br>Forces processor to place the data & address buses and control lines in the hi-Z state   |

| holda_n  | O    | Low                   | <b>Hold acknowledge output</b><br>Indicates that processor is in the hold mode                                |

| int0_n   | I    | Low/Fall              | <b>External interrupt inputs</b>                                                                              |

| int1_n   | I    | Low/Fall              | External interrupt 0                                                                                          |

| int2_n   | I    | Low/Fall              | External interrupt 1                                                                                          |

|          |      |                       | External interrupt 2                                                                                          |

| iack_n   | I    | Low                   | <b>Interrupt acknowledge</b><br>Indicates branching to the interrupt vector                                   |

| ps_o     | O    | Low                   | <b>Program, data and I/O space select signals</b>                                                             |

| ds_o     | O    | Low                   |                                                                                                               |

| is_o     | O    | Low                   |                                                                                                               |

| ps_tri   | O    | High                  | <b>Select signals tri-state control</b>                                                                       |

| ds_tri   | O    | High                  | Enables external tri-state buffers                                                                            |

| is_tri   | O    | High                  |                                                                                                               |

| rw_o     | O    | -                     | <b>Read/write output signal</b><br>Indicates external transfer direction. High means reading                  |

| rw_tri   | O    | H                     | <b>Read/write tri-state control</b><br>Enables external tri-state buffer                                      |

| strb_o   | O    | Low                   | <b>Strobe signal</b><br>Low indicates an external bus cycle                                                   |

| strb_tri | O    | High                  | <b>Strobe tri-state control signal</b><br>Enables external tri-state buffer                                   |

| ready    | I    | High                  | <b>Data ready input</b><br>Indicates that external device is prepared for transfer to be completed            |

| bio_n    | I    | Low                   | <b>Branch control input</b><br>When active the BIOZ branch occurs                                             |

| br_n     | O    | Low                   | <b>Bus request output</b><br>Asserted when the processor requires access to external global data memory space |

| Name        | Type | Polarity/<br>Bus size | Description                                                                       |

|-------------|------|-----------------------|-----------------------------------------------------------------------------------|

| msc_n       | O    | Low                   | <b>Microstate complete output</b><br>Indicates a completion of a memory operation |

| xf          | O    | -                     | <b>External flag output</b><br>General purpose output pin                         |

| clkr        | I    | Fall                  | <b>Receive clock input</b>                                                        |

| clkx        | I    | Rise                  | <b>Transmit clock input</b>                                                       |

| dr          | I    | -                     | <b>Serial data receive input</b><br>Data clocked by clkr                          |

| dx_o        | O    | -                     | <b>Serial data transmit output</b>                                                |

| dx_tri      | O    | High                  | <b>Serial transmit tri-state control</b><br>Active only while transmitting        |

| fsr         | I    | Fall                  | <b>Frame synchronization pulse for receive input</b>                              |

| fsx_i       | I    | Fall                  | <b>Frame synchronization pulse for transmit input</b>                             |

| fsx_o       | O    | Fall                  | <b>Frame synchronization pulse for transmit output</b>                            |

| fsx_tri     | O    | High                  | <b>Frame synchronization pulse for transmit tri-state control</b>                 |

| extaddr_o   | O    | 16                    | <b>External Program/ Data/ IO interface</b>                                       |

| extaddr_tri | O    | High                  | Address bus output                                                                |

| extdata_i   | I    | 16                    | Address tri-state control                                                         |

| extdata_o   | O    | 16                    | Data bus input                                                                    |

| extdata_tri | O    | High                  | Data bus output                                                                   |

| romdata     | I    | 16                    | <b>Internal Program Memory interface</b>                                          |

| romaddr     | O    | 12                    | Data input                                                                        |

| romaddr     |      |                       | Address output                                                                    |

| ram0data_i  | I    | 16                    | <b>Internal RAM 0 interface</b>                                                   |

| ram0data_o  | O    | 16                    | Data bus input                                                                    |

| ram0addr    | O    | 8                     | Data bus output                                                                   |

| ram0we      | O    | High                  | Data file address                                                                 |

| ram0oe      | O    | High                  | Data file write enable                                                            |

| ram0oe      |      |                       | Data file output enable                                                           |

| ram1data_i  | I    | 16                    | <b>Internal RAM 1 interface</b>                                                   |

| ram1data_o  | O    | 16                    | Data bus input                                                                    |

| ram1addr    | O    | 8                     | Data bus output                                                                   |

| ram1we      | O    | High                  | Data file address                                                                 |

| ram1oe      | O    | High                  | Data file write enable                                                            |

| ram1oe      |      |                       | Data file output enable                                                           |

| ram2data_i  | I    | 16                    | <b>Internal RAM 2 interface</b>                                                   |

| ram2data_o  | O    | 16                    | Data bus input                                                                    |

| ram2addr    | O    | 5                     | Data bus output                                                                   |

| ram2we      | O    | High                  | Data file address                                                                 |

| ram2oe      | O    | High                  | Data file write enable                                                            |

| ram2oe      |      |                       | Data file output enable                                                           |

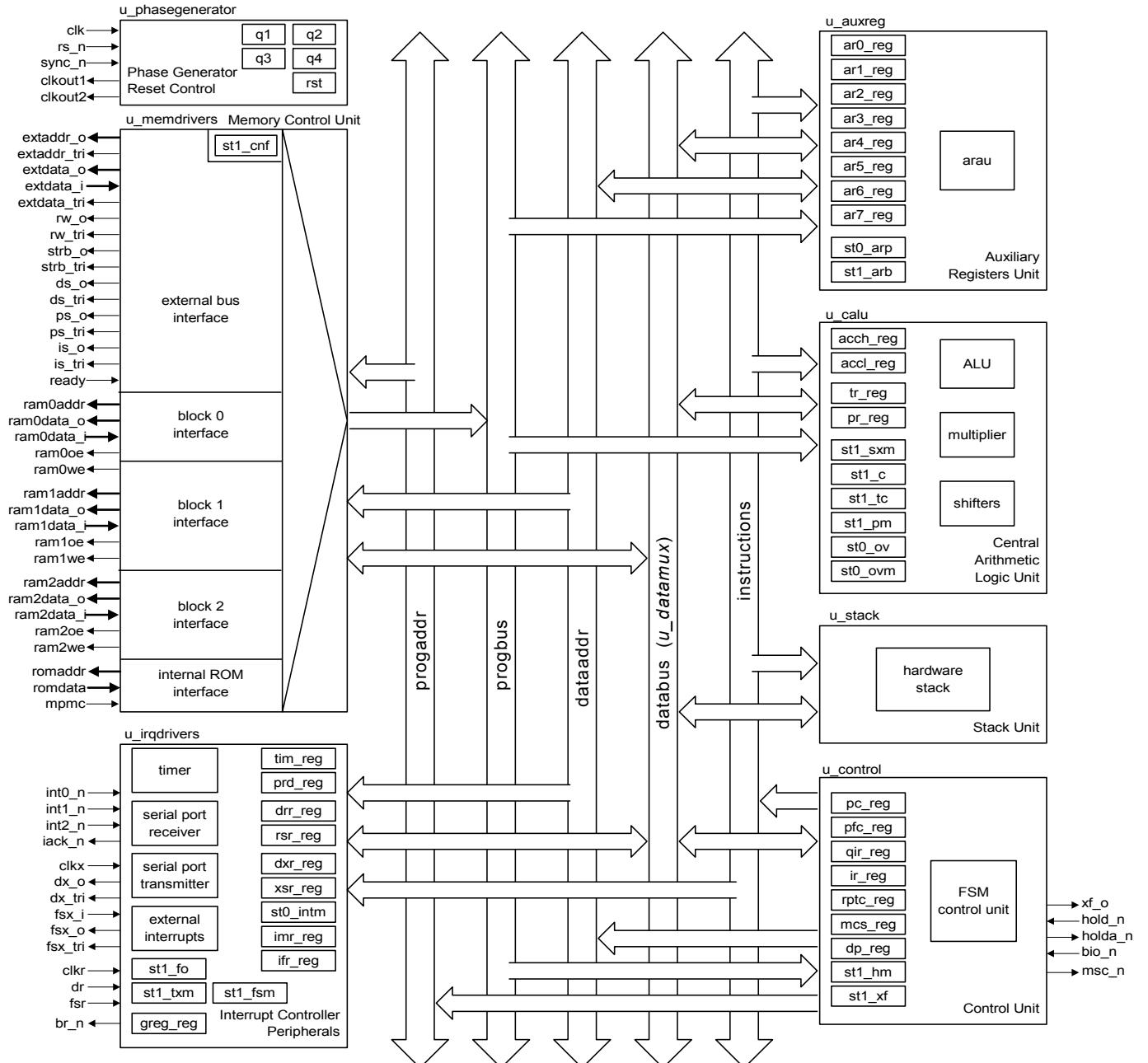

## Block Diagram

C32025 Block Diagram

## Functional Description

The C32025 core is partitioned into modules as described below.

### Control Unit

Control unit consists of Program Counter (PC) and Prefetch Counter (PFC) used for program addressing and pipelining. Sequencer is responsible for data flow organization. Repeat Counter (RPTC) is used to repeat the execution of several instructions, especially data-intensive ones.

### Memory Control Unit

It is an interface between the processor and all on-chip or off-chip memories. There are three internal RAM blocks interfaces, internal ROM interface and external address and data buses. External wait states are possible.

### Central Arithmetic Logic Unit

Central Arithmetic-Logic Unit. (CALU) performs:

- Sign-extended shifting

- 32-bit arithmetic operations

- 32-bit logic operations

- 16-bit signed or unsigned multiplication

### Auxiliary Registers Unit

Eight auxiliary registers are used for indirect data addressing or temporary data storage. Auxiliary Registers Arithmetic Unit performs operations on current auxiliary register after each indirect data memory read/write.

### Stack Unit

Eight level hardware stack for PC storage during subroutine calls and interrupt service.

### Peripherals

There is one 16-bit continuously operating timer with programmable period. Synchronous full-duplex serial interface can be used for interfacing serial AD/DA converters and codecs.

### Interrupt Controller

There are three external interrupts, both edge and level triggered. Internal interrupt is generated at timer underflow or serial port transmit/receive completion. Those six interrupts are maskable using Interrupt Mask Register (IMR). There is also one non-maskable software interrupt.

## Phase Generator

Internal clock cycle divider. Machine cycle consists of four main clock cycles.

## Reset Control

Reset input is sampled once a machine cycle and distributed all over the core.

## Device Utilization & Performance

| Supported Family      | Device Tested | Utilization |              |     | Performance $F_{max}$ |

|-----------------------|---------------|-------------|--------------|-----|-----------------------|

|                       |               | LEs         | Memory       | DSP |                       |

| Flex <sup>2</sup>     | EPF10K100E-1  | 4532        | M4Ks; 1 M512 | 1   | 24 MHz                |

| Acex <sup>2</sup>     | EP1K100E-1    | 4532        | M4Ks; 1 M512 | 1   | 26 MHz                |

| Apex <sup>1</sup>     | EP20K200E-1   | 4420        | 19 ESBs      | -   | 37 MHz                |

| Apex2 <sup>1</sup>    | EP2A15-7      | 4528        | 19 ESBs      | -   | 65 MHz                |

| Cyclone <sup>1</sup>  | EP1C6-6       | 4066        | 37 ESBs      | -   | 95 MHz                |

| Stratix <sup>1</sup>  | EP1S10-5      | 4370        | 7 EABs       | -   | 101 MHz               |

| Startix2 <sup>1</sup> | EP2S15-3      | 3835        | 7 EABs       | -   | 130 MHz               |

Notes:

1. Implemented with 544x16 bit RAM and 4096 x 16 bit ROM

2. Implemented with 544x16 bit RAM and 1048 x 16 bit ROM

## Core Assumptions

The IACK\_N and MSC\_N lines are valid only during the quarter-phases Q1 and Q2 (when CLKOUT1 = 0). In other cases their behaviour is unpredictable in the original Texas Instruments TMS320C25 device. The C32025 sets them to 1s in Q3 and Q4, except in the hold mode when MSC\_N remains 0.

The original Texas Instruments TMS320C25 serial port doesn't re-start properly when a frame sync pulse occurs in the middle of a transmission. The new transfer following a re-start is interrupted in a moment when previous transmission should be completed as if and there were no frame sync pulses, but the transferred data is re-loaded. The C32025 serial interface works properly as it is described in the specification document.

The CLKR and CLKX inputs are clock inputs in the original Texas Instruments TMS320C25 serial port registers. In C32025 they are not clock signals but are synchronously sampled at every positive edge of the main clock signal. The same applies to the external interrupts inputs INT0\_N, INT1\_N and INT2\_N. They are connected to a negative edge flip-flop in the original device, but in C32025 they are sampled synchronously with

main clock signal. These changes cause delays in the serial port operation and forces the minimum length of an external interrupt pulse to at least one oscillator cycle.

Some registers are not reset by RS\_N in the original Texas Instruments TMS320C25 device, but are reset in the C32025. They are:

ACC 00000000h

PR 00000000h

TR 0000h

ARP 000

ARB 000

DP 000000000

IMR 00000

DRR 0000h

DXR 0000h

Stack all levels are reset to 0000h

OVM 0

TC 0

AR0-AR7 all registers are reset to 0000h

## Verification Methods

The C32025 core's functionality was verified by means of a proprietary hardware modeler. The same stimulus was applied to a hardware model that contained the original Texas Instruments TMS320C25 chip, and the results compared with the core's simulation outputs.

## Development Environment

- VHDL source code for the C32025

- Synthesis support - Complete set of synthesis scripts for Synopsys

- Simulation support – A set of scripts and macros for Synopsys, MTI, and Aldec

- Example CHIP\_C32025 – TMS320C25 compatible design

This design uses the C32025 and illustrates how to build and connect memories and tri-state buffers

- Extensive HDL Test Bench that instantiates:

- Example design CHIP\_C32025

- External RAM

- External ROM

- External I/O

- Clock generator

- Process that compares your simulation results with the expected results

- A collection of test assembler programs which are executed directly by the Test Bench

- A set of expected results

- Additional documentation

- Architectural overview

- Hardware description

- User Guide

- Design support including consulting

## Deliverables

### Netlist Licenses

- Post-synthesis EDIF netlist

- Testbench (self-checking)

- Vectors for testbenches

- Expected results

- Place & Route script

- Simulation script

- Constraint file

- Instantiation templates

- User Documentation

### HDL Source Licenses

- Synthesizable VHDL or Verilog RTL source code

- Testbench (self-checking)

- Vectors for testbenches

- Expected results

- Simulation script

- Synthesis script

- User Documentation

## Related Information

Texas Instruments

URL: <http://www.ti.com>

## Contact Information

CAST, Inc.

11 Stonewall Court

Woodcliff Lake, New Jersey 07677 USA

Phone: +1 201-391-8300

Fax: +1 201-391-8694

E-Mail: [info@cast-inc.com](mailto:info@cast-inc.com)

URL: [www.cast-inc.com](http://www.cast-inc.com)

This megafunction developed by the

processor experts at

Evatronix SA