# 捷多邦,专业PCB打样工厂,24小时加急出货

### DG2303

Vishay Siliconix

# High-Speed, Low r<sub>ON</sub>, 1.8-V/2.5-V/3.3-V/5-V, SPST Analog Switch (1-Bit Bus Switch) WWW.DZSG.COM

#### DESCRIPTION

VISHAY

The DG2303 is a high-speed, 1-bit, low power, TTLcompatible bus switch. Using sub-micron CMOS technology, DG2303 achieves low on-resistance and negligible propagation delay.

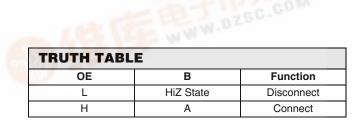

The DG2303 consist of a bi-directional input/output pins A and B. When the output enable (OE) is low, the input/output pins are connected. When the OE is high, the switch is open and a high-impedance state exists between input/output pins A and B.

#### **FEATURES**

- SC-70 5-Lead Package

- 5 Ω Switch Connection Between Two Ports

- Minimal Propagation Delay Through The Switch

- Low I<sub>CC</sub>

- Zero Bounce In Flow-Through Mode

- Control Inputs Compatible with TTL Level

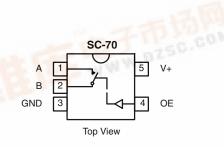

### FUNCTIONAL BLOCK DIAGRAM AND PIN CONFIGURATION

Device Marking: E6

| ORDERING INFORMATION |         |                               |  |  |

|----------------------|---------|-------------------------------|--|--|

| Temp Range           | Package | Part Number                   |  |  |

| - 40 to 85 °C        | SC70-5  | DG2303DL-T1<br>DG2303DL-T1-E3 |  |  |

Vishay Siliconix

| ABSOLUTE MAXIMUM RA                       | TINGS                   |                       |      |  |  |

|-------------------------------------------|-------------------------|-----------------------|------|--|--|

| Parameter                                 |                         | Limit                 | Unit |  |  |

| Reference V+ to GND                       |                         | - 0.3 to + 6 V        | N/   |  |  |

| OE, A, B <sup>a</sup>                     |                         | - 0.3 to (V+ + 0.3 V) | V    |  |  |

| Continuous Current (Any Terminal)         |                         | ± 50                  | mA   |  |  |

| Peak Current (Pulsed at 1 ms, 10 % du     | ty cycle)               | ± 200                 | IIIA |  |  |

| Storage Temperature (D Suffix)            |                         | - 65 to 150           | °C   |  |  |

| Power Dissipation (Packages) <sup>b</sup> | 5-Pin SC70 <sup>c</sup> | 250                   | mW   |  |  |

Notes:

a. Signals on A, or B or OE exceeding V+ will be clamped by internal diodes. Limit forward diode current to maximum current ratings. b. All leads welded or soldered to PC Board.

c. Derate 3.1 mW/°C above 70 °C.

|                                       |                                    | Test Conditions<br>Otherwise Unless Specified<br>$V+ = 1.65 V$ to 5.5 V, $V_{IN} = V_{IH}$ or $V_{IL}^e$ |                   | Limits<br>- 40 to 85 °C |                  |                  |      |

|---------------------------------------|------------------------------------|----------------------------------------------------------------------------------------------------------|-------------------|-------------------------|------------------|------------------|------|

| Parameter                             | Symbol                             |                                                                                                          | Temp <sup>a</sup> | Min <sup>b</sup>        | Тур <sup>с</sup> | Max <sup>b</sup> | Unit |

| DC Characteristics                    |                                    |                                                                                                          | ·                 |                         |                  | •                |      |

|                                       |                                    | $V+ = 1.8 V, V_A = 0 V, I_B = 4 mA$                                                                      | Full              |                         |                  | 28.0             | Ω    |

|                                       |                                    | V+ = 1.8 V, V <sub>A</sub> = 1.8 V, I <sub>B</sub> = 4 mA                                                | Full              |                         |                  | 60.0             |      |

|                                       |                                    | $V+ = 2.3 V, V_A = 0 V, I_B = 8 mA$                                                                      | Full              |                         |                  | 12.0             |      |

|                                       |                                    | $V$ + = 2.3 V, $V_A$ = 2.3 V, $I_B$ = 8 mA                                                               | Full              |                         |                  | 30.0             |      |

| On-Resistance                         | r <sub>ON</sub>                    | $V$ + = 3.0 V, $V_A$ = 0 V, $I_B$ = 24 mA                                                                | Full              |                         |                  | 9.0              |      |

|                                       |                                    | V+ = 3.0 V, V <sub>A</sub> = 3.0 V, I <sub>B</sub> = 24 mA                                               | Full              |                         |                  | 20.0             |      |

|                                       |                                    | $V+ = 4.5 V$ , $V_A = 0 V$ , $I_B = 30 mA$                                                               | Full              |                         |                  | 7.0              |      |

|                                       | -                                  | V+ = 4.5 V, $V_A$ = 2.4 V, $I_B$ = 15 mA                                                                 | Full              |                         |                  | 12.0             |      |

|                                       |                                    | V+ = 4.5 V, $V_A$ = 4.5 V, $I_B$ = 30 mA                                                                 | Full              |                         |                  | 15.0             |      |

|                                       |                                    | $V + = 1.8 V$ , $V_A = 0 V$ to $V +$ , $I_B = 4 mA$                                                      | Full              |                         | 125              |                  |      |

| - d                                   | r <sub>ON</sub>                    | $V$ + = 2.5 V, $V_A$ = 0 V to V+, $I_B$ = 8 mA                                                           | Full              |                         | 28               |                  |      |

| r <sub>ON</sub> Flatness <sup>d</sup> | Flatness                           | V+ = 3.3 V, $V_A$ = 0 V to V+, $I_B$ = 24 mA                                                             | Full              |                         | 12               |                  |      |

|                                       |                                    | $V$ + = 5.0 V, $V_A$ = 0 V to V+, $I_B$ = 30 mA                                                          | Full              |                         | 6                |                  |      |

| Switch Off Leakage Current            | I <sub>(off)</sub>                 | V+ = 5.5 V, V <sub>A</sub> = 1 V/4.5 V, V <sub>B</sub> = 4.5 V/1 V                                       | Full              | - 10                    |                  | 10               |      |

| Switch-On Leakage Current             | I <sub>(on)</sub>                  | V+ = 5.5 V, V <sub>A</sub> = V <sub>B</sub> = 1 V/4.5 V                                                  | Full              | - 10                    |                  | 10               | μA   |

| _                                     | (* )                               | V+ = 1.65 V to 1.95 V                                                                                    | Full              | 1.35                    |                  |                  | - V  |

| Innut Lligh Voltage                   | V                                  | V+ = 2.3 V to 2.7 V                                                                                      | Full              | 1.6                     |                  |                  |      |

| Input High Voltage                    | V <sub>IH</sub>                    | V+ = 3.0 V to 3.6 V                                                                                      | Full              | 2.0                     |                  |                  |      |

|                                       |                                    | V+ = 4.5 V to 5.5 V                                                                                      | Full              | 2.4                     |                  |                  |      |

|                                       |                                    | V+ = 1.65 V to 1.95 V                                                                                    | Full              |                         |                  | 0.4              |      |

| Input Low Voltage                     | V <sub>IL</sub>                    | V+ = 2.3 V to 2.7 V                                                                                      | Full              |                         |                  | 0.4              |      |

| input Low Voltage                     |                                    | V+ = 3.0 V to 3.6 V                                                                                      | Full              |                         |                  | 0.6              |      |

|                                       |                                    | V+ = 4.5 V to 5.5 V                                                                                      | Full              |                         |                  | 0.8              |      |

| Input Current                         | I <sub>IL</sub> or I <sub>IH</sub> | V <sub>OE</sub> = 0 or V+                                                                                | Full              | - 1                     |                  | 1                | μA   |

# DG2303

Vishay Siliconix

| SPECIFICATIONS                       |                                     |                                                                                       |                   |                      |                  |                  |      |

|--------------------------------------|-------------------------------------|---------------------------------------------------------------------------------------|-------------------|----------------------|------------------|------------------|------|

|                                      |                                     | Test Conditions<br>Otherwise Unless Specified                                         |                   | Limits<br>- 40 to 85 |                  | с                |      |

| Parameter                            | Symbol                              | V+ = 1.65 V to 5.5 V, $V_{IN} = V_{IH} \text{ or } V_{IL}^{e}$                        | Temp <sup>a</sup> | Min <sup>b</sup>     | Тур <sup>с</sup> | Max <sup>b</sup> | Unit |

| Dynamic Characteristics              | •                                   | •                                                                                     | •                 |                      | •                |                  | •    |

|                                      | t <sub>PHL</sub> , t <sub>PLH</sub> | $V_{LD}$ = Open, V = 1.65 V to 1.95 V, (Figure 1 and 2)                               | Full              |                      |                  | 5                | -    |

| Prop Delay Bus-to-Bus <sup>f</sup>   |                                     | $V_{LD}$ = Open, V = 2.3 V to 2.7 V, (Figure 1 and 2)                                 | Full              |                      |                  | 2                |      |

| Prop Delay Bus-lo-Bus                | PHL, PLH                            | $V_{LD}$ = Open, V = 3.0 V to 3.6 V, (Figure 1 and 2)                                 | Full              |                      |                  | 1                |      |

|                                      |                                     | $V_{LD}$ = Open, V = 4.5 V to 5.5 V, (Figure 1 and 2)                                 | Full              |                      |                  | 1                |      |

|                                      |                                     | $V_{LD} = 2 \times V_{+}, V_{+} = 1.65 V \text{ to } 1.95 V \text{ (Figure 1 and 2)}$ | Full              |                      | 4.2              |                  | ns   |

|                                      | +                                   | $V_{LD} = 2 \times V_{+}, V_{+} = 2.3 \vee to 2.7 \vee (Figure 1 and 2)$              | Full              |                      | 3.3              |                  |      |

|                                      | t <sub>PZL</sub>                    | V <sub>LD</sub> = 2 x V+, V+ = 3.0 V to 3.6 V (Figure 1 and 2)                        | Full              |                      | 2.6              |                  |      |

| O data de Estado                     |                                     | V <sub>LD</sub> = 2 x V+, V+ = 4.5 V to 5.5 V (Figure 1 and 2)                        | Full              |                      | 1.8              |                  |      |

| Output Enable Time <sup>d</sup>      |                                     | V <sub>LD</sub> = 0 V, V+ = 1.65 V to 1.95 V (Figure 1 and 2)                         | Full              |                      | 4.4              |                  |      |

|                                      | t                                   | V <sub>LD</sub> = 0 V, V+ = 2.3 V to 2.7 V (Figure 1 and 2)                           | Full              |                      | 3.3              |                  |      |

|                                      | t <sub>PZH</sub>                    | V <sub>LD</sub> = 0 V, V+ = 3.0 V to 3.6 V (Figure 1 and 2)                           | Full              |                      | 2.7              |                  |      |

|                                      |                                     | V <sub>LD</sub> = 0 V, V+ = 4.5 V to 5.5 V (Figure 1 and 2)                           | Full              |                      | 2.0              |                  |      |

|                                      | t <sub>PLZ</sub>                    | $V_{LD} = 2 \text{ x V}$ +, V+ = 1.65 V to 1.95 V (Figure 1 and 2)                    | Full              |                      | 14.3             |                  |      |

|                                      |                                     | V <sub>LD</sub> = 2 x V+, V+ = 2.3 V to 2.7 V (Figure 1 and 2)                        | Full              |                      | 10.5             |                  |      |

|                                      |                                     | V <sub>LD</sub> = 2 x V+, V+ = 3.0 V to 3.6 V (Figure 1 and 2)                        | Full              |                      | 8.6              |                  |      |

| o                                    |                                     | $V_{LD} = 2 \times V_{+}, V_{+} = 4.5 V \text{ to } 5.5 V \text{ (Figure 1 and 2)}$   | Full              |                      | 7.4              |                  |      |

| Output Disable Time <sup>d</sup>     |                                     | $V_{LD} = 0 V$ , V+ = 1.65 V to 1.95 V (Figure 1 and 2)                               | Full              |                      | 10.7             |                  |      |

|                                      |                                     | V <sub>LD</sub> = 0 V, V+ = 2.3 V to 2.7 V (Figure 1 and 2)                           | Full              |                      | 9.6              |                  |      |

|                                      |                                     | V <sub>LD</sub> = 0 V, V+ = 3.0 V to 3.6 V (Figure 1 and 2)                           | Full              |                      | 8.7              |                  |      |

|                                      |                                     | V <sub>LD</sub> = 0 V, V+ = 4.5 V to 5.5 V (Figure 1 and 2)                           | Full              |                      | 7.5              |                  |      |

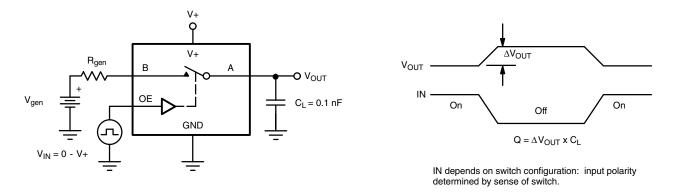

| Charge Injection <sup>d</sup>        | Q <sub>INJ</sub>                    | $C_L$ = 1 nF, $V_{GEN}$ = 0 V, $R_{GEN}$ = 0 Ω, (Figure 3)                            | Room              |                      | 0.5              |                  | рС   |

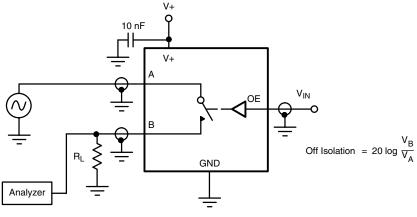

| Off Isolation <sup>d</sup>           | OIRR                                | $R_{L} = 50 \Omega$ , $C_{L} = 5 pF$ , f = 10 MHz                                     | Room              |                      | - 50             |                  | dB   |

| Insertion Loss <sup>d</sup>          | Loss                                | R <sub>L</sub> = 50 Ω                                                                 | Room              |                      | > 200            |                  | MHz  |

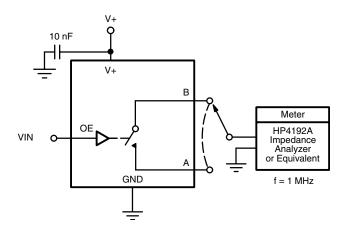

| Input Capacitance <sup>d</sup>       | C <sub>in</sub>                     |                                                                                       | Room              |                      | 4                |                  |      |

| Channel-Off Capacitance <sup>d</sup> | C <sub>(off)</sub>                  | - V <sub>OE</sub> = 0 or V+, f = 1 MHz                                                | Room              |                      | 9                |                  | pF   |

| Channel-On Capacitance <sup>d</sup>  | C <sub>ON</sub>                     |                                                                                       | Room              |                      | 20               |                  | 1    |

| Power Supply                         |                                     |                                                                                       |                   |                      |                  |                  |      |

| Power Supply Range                   | V+                                  |                                                                                       |                   | 1.65                 |                  | 5.5              | V    |

| Power Supply Current                 | l+                                  | V <sub>OE</sub> = 0 or V+                                                             |                   |                      |                  | 1.0              | μA   |

Notes:

a. Room = 25 °C, Full = as determined by the operating suffix.

b. The algebraic convention whereby the most negative value is a minimum and the most positive a maximum, is used in this data sheet.

c. Typical values are for design aid only, not guaranteed nor subject to production testing.

d. Guarantee by design, nor subjected to production test.

e.  $V_{IN}$  = input voltage to perform proper function.

f. Guaranteed by design and not production tested. The bus switch propagation delay is a function of the RC time constant contributed by the on-resistance and the specified load capacitance with an ideal voltage source (zero output impedance) driving the switch.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### DG2303

Vishay Siliconix

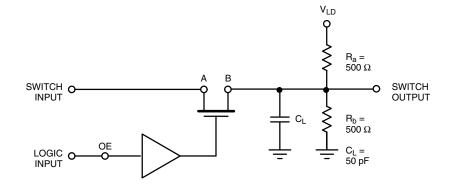

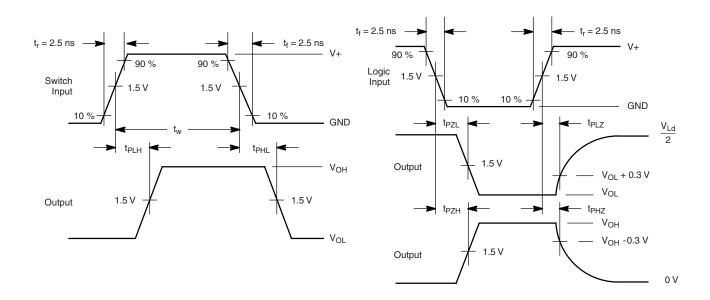

### AC LOADING AND WAVEFORMS

Input driven by 50  $\Omega$  source terminated in 50  $\Omega$  C<sub>L</sub> includes load and stray capacitance Input PRR = 1.0 MHz, t<sub>W</sub> = 50 ns

Figure 1. AC Test Circuit

Figure 2. AC Waveforms

DG2303 Vishay Siliconix

#### **TEST CIRCUITS**

Figure 4. Off-Isolation

Figure 5. Channel Off/On Capacitance

Vishay Siliconix maintains worldwide manufacturing capability. Products may be manufactured at one of several qualified locations. Reliability data for Silicon Technology and Package Reliability represent a composite of all qualified locations. For related documents such as package/tape drawings, part marking, and reliability data, see http://www.vishay.com/ppg?72073.

Vishay

## Disclaimer

All product specifications and data are subject to change without notice.

Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively, "Vishay"), disclaim any and all liability for any errors, inaccuracies or incompleteness contained herein or in any other disclosure relating to any product.

Vishay disclaims any and all liability arising out of the use or application of any product described herein or of any information provided herein to the maximum extent permitted by law. The product specifications do not expand or otherwise modify Vishay's terms and conditions of purchase, including but not limited to the warranty expressed therein, which apply to these products.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay.

The products shown herein are not designed for use in medical, life-saving, or life-sustaining applications unless otherwise expressly indicated. Customers using or selling Vishay products not expressly indicated for use in such applications do so entirely at their own risk and agree to fully indemnify Vishay for any damages arising or resulting from such use or sale. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications.

Product names and markings noted herein may be trademarks of their respective owners.