# Sensor Signal Conditioning IC for Closed-Loop Magnetic Current Sensor

# **FEATURES**

- DESIGNED FOR SENSORS FROM VACUUMSCHMELZE (VAC)

- SINGLE SUPPLY: 5V

- POWER OUTPUT: H-Bridge

- DESIGNED FOR DRIVING INDUCTIVE LOADS

- EXCELLENT DC PRECISION

- WIDE SYSTEM BANDWIDTH

- HIGH-RESOLUTION, LOW-TEMPERATURE DRIFT

- BUILT-IN DEGAUSS SYSTEM

- EXTENSIVE FAULT DETECTION

- EXTERNAL HIGH-POWER DRIVER OPTION

# **APPLICATIONS**

- GENERATOR/ALTERNATOR MONITORING AND CONTROL

- FREQUENCY AND VOLTAGE INVERTERS

- MOTOR DRIVE CONTROLLERS

- SYSTEM POWER CONSUMPTION

- PHOTOVOLTAIC SYSTEMS

#### Patents Pending.

# DESCRIPTION

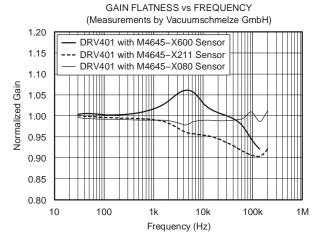

The DRV401 is designed to control and process signals from specific magnetic current sensors made by Vacuumschmelze GmbH & Co. KG (VAC). A variety of current ranges and mechanical configurations are available. Combined with a VAC sensor, the DRV401 monitors both ac and dc currents to high accuracy.

Provided functions include: probe excitation, signal conditioning of the probe signal, signal loop amplifier, an H-bridge driver for the compensation coil, and an analog signal output stage that provides an output voltage proportional to the primary current. It offers overload and fault detection, as well as transient noise suppression.

The DRV401 can directly drive the compensation coil, or connect to external power drivers. Therefore, the DRV401 combines with sensors to measure small to very large currents.

To maintain the highest accuracy, the DRV401 can demagnetize (degauss) the sensor at power-up and on demand.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments

PowerPAD is a trademark of Texas Instruments. All other trademarks are the property of their respective owners.

SBVS070A - JUNE 2006 - REVISED OCTOBER 2006

#### ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

| Supply Voltage+7V                                          |

|------------------------------------------------------------|

| Signal Input Terminals:                                    |

| Voltage <sup>(2)</sup>                                     |

| Differential Amplifier <sup>(3)</sup> –10V to +10V         |

| Current at IS1 and IS2 ±75mA                               |

| Current (pins other than IS1 and IS2) <sup>(2)</sup> ±25mA |

| I <sub>COMP</sub> Short Circuit <sup>(4)</sup> +250mA      |

| Operating Junction Temperature50°C to +150°C               |

| Storage Temperature55°C to +150°C                          |

| ESD Rating:                                                |

| Human Body Model (HBM)                                     |

| Pins IA <sub>IN1</sub> and IA <sub>IN2</sub> Only 1kV      |

| All Other Pins 4kV                                         |

(1) Stresses above these ratings may cause permanent damage. Exposure to absolute maximum conditions for extended periods may degrade device reliability. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those specified is not supported.

- (2) Input terminals are diode-clamped to the power-supply rails. Input signals that can swing more than 0.5V beyond the supply rails must be current limited, except for the differential amplifier input pins.

- (3) These inputs are not internally protected against over voltage. The differential amplifier input pins must be limited to 5mA, max or ±10V, max.

- (4) Power-limited; observe maximum junction temperature.

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### **ORDERING INFORMATION**<sup>(1)</sup>

| PRODUCT | PACKAGE-LEAD          | PACKAGE<br>DESIGNATOR | PACKAGE<br>MARKING |

|---------|-----------------------|-----------------------|--------------------|

| DRV401  | QFN-20<br>(5mm x 5mm) | RGW                   | HAAQ               |

| DRV401  | SO-20                 | DWP                   | DRV401A            |

(1) For the most current package and ordering information see the Package Option Addendum at the end of this document, or see the TI web site at www.ti.com.

## **ELECTRICAL CHARACTERISTICS**

Boldface limits apply over the specified temperature range:  $T_J = -40^{\circ}C$  to  $+125^{\circ}C$ .

At  $T_A = +25^{\circ}C$  and  $V_{DD1} = V_{DD2} = +5V$  with external 100kHz filter BW, and zero output current I<sub>COMP</sub>, unless otherwise noted.

|                                                                                   |                                                  |                      | DRV401               |                        |               |  |

|-----------------------------------------------------------------------------------|--------------------------------------------------|----------------------|----------------------|------------------------|---------------|--|

| PARAMETER                                                                         | CONDITIONS                                       | MIN                  | TYP                  | MAX                    | UNITS         |  |

| DIFFERENTIAL AMPLIFIER                                                            | $R_L$ = 10k $\Omega$ to 2.5V, $V_{REFIN}$ = 2.5V |                      |                      |                        |               |  |

| OFFSET VOLTAGE                                                                    |                                                  |                      |                      |                        |               |  |

| Offset Voltage, RTO <sup>(1)(2)</sup> Vos                                         | Gain 4V/V                                        |                      | ±0.01                | ±0.1                   | mV            |  |

| Drift, RTO <sup>(2)</sup> dV <sub>OS</sub> /dT                                    |                                                  |                      | ±0.1                 | ±1(3)                  | μ <b>ν/∘C</b> |  |

| vs Common-Mode, RTO CMRR                                                          | $-1V$ to +6V, $V_{REF} = 2.5V$                   |                      | ±50                  | ±250                   | μV/V          |  |

| vs Power-Supply, RTO PSRR                                                         | V <sub>REF</sub> not included                    |                      | ±4                   | ±50                    | μV/V          |  |

| SIGNAL INPUT                                                                      |                                                  |                      |                      |                        |               |  |

| Common-Mode Voltage Range                                                         |                                                  | -1                   |                      | (V <sub>DD</sub> ) + 1 | V             |  |

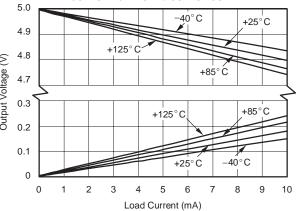

| SIGNAL OUTPUT                                                                     |                                                  |                      |                      |                        |               |  |

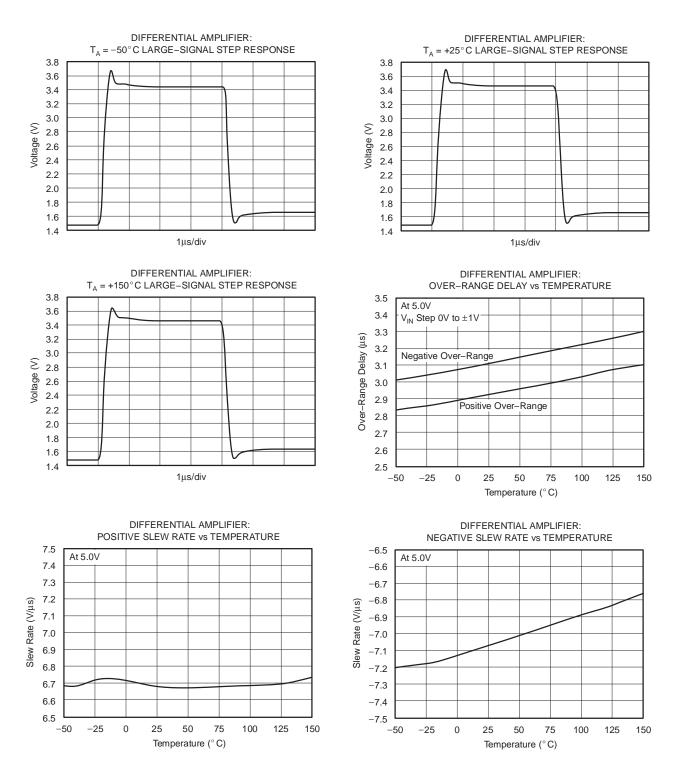

| Signal Over-Range Indication (OVER-RANGE), Delay <sup>(2)</sup>                   | $V_{IN}$ = 1V Step, See Notes 2 and 3            |                      | 2.5 to 3.5           |                        | μ <b>s</b>    |  |

| Voltage Output Swing From Negative Rail <sup>(2)</sup> ,<br>OVER-RANGE Trip Level | l = +2.5mA, CMP Trip Level                       |                      | +48                  | +85                    | mV            |  |

| Voltage Output Swing From Positive Rail <sup>(2)</sup> ,<br>OVER-RANGE Trip Level | I = -2.5mA, CMP Trip Level                       | V <sub>DD</sub> – 85 | V <sub>DD</sub> – 48 |                        | mV            |  |

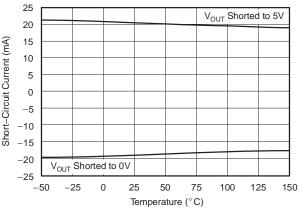

| Short-Circuit Current <sup>(2)</sup> I <sub>SC</sub>                              | V <sub>OUT</sub> Connected To GND                |                      | -18                  |                        | mA            |  |

|                                                                                   | V <sub>OUT</sub> Connected To V <sub>DD</sub>    |                      | +20                  |                        | mA            |  |

| Gain, V <sub>OUT</sub> /V <sub>IN_DIFF</sub>                                      |                                                  |                      | 4                    |                        | V/V           |  |

| Gain Error                                                                        |                                                  |                      | ±0.02                | ±0.3                   | %             |  |

| Gain Error Drift                                                                  |                                                  |                      | ±0.1                 |                        | ppm/°C        |  |

| Linearity Error                                                                   | $R_L = 1k\Omega$                                 |                      | 10                   |                        | ppm           |  |

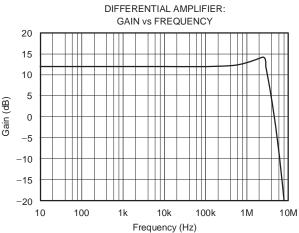

| FREQUENCY RESPONSE                                                                |                                                  |                      |                      |                        |               |  |

| Bandwidth <sup>(2)</sup> BW <sub>-3dB</sub>                                       |                                                  |                      | 2                    |                        | MHz           |  |

| Slew Rate <sup>(2)</sup> SR                                                       | CMVR = -1V to = +4V                              |                      | 6.5                  |                        | V/µs          |  |

| Settling Time, Large-Signal <sup>(2)</sup>                                        | dV $\pm$ 2V to 1%, No External Filter            | i i                  | 0.9                  |                        | μs            |  |

| Settling Time <sup>(2)</sup>                                                      | dV $\pm$ 0.4V to 0.01%                           |                      | 14                   |                        | μs            |  |

| INPUT RESISTANCE                                                                  |                                                  |                      |                      |                        |               |  |

| Differential                                                                      |                                                  | 16.5                 | 20                   | 23.5                   | kΩ            |  |

| Common-Mode                                                                       |                                                  | 41                   | 50                   | 59                     | kΩ            |  |

| External Reference Input                                                          |                                                  | 41                   | 50                   | 59                     | kΩ            |  |

| NOISE                                                                             |                                                  |                      |                      |                        |               |  |

| Output Voltage Noise Density, $f = 1 \text{ kHz}$ , RTO <sup>(2)</sup> $e_n$      | Compensation Loop Disabled                       |                      | 170                  |                        | nV/√Hz        |  |

| COMPENSATION LOOP                                                |                   |                                                  |      |                               |      |                 |

|------------------------------------------------------------------|-------------------|--------------------------------------------------|------|-------------------------------|------|-----------------|

| DC STABILITY                                                     |                   | Probe f = 250kHz, $R_{LOAD}$ = 20 $\Omega$       |      |                               |      |                 |

| Offset Error <sup>(4)</sup>                                      |                   | Deviation from 50% PWM, Pin Gain = L             |      | 0.03                          |      | %               |

| Offset Error Drift <sup>(2)</sup>                                |                   | Deviation from 50% PWM, Pin Gain = L             |      | 7.5                           |      | ppm/°C          |

| Gain, Pin Gain = L <sup>(2)</sup>                                |                   | VICOMP1 - VICOMP2                                | -200 | 25                            | 200  | ppm/V           |

| Power-Supply Rejection Ratio                                     | PSRR              | Probe Loop f = 250kHz                            |      | 500                           |      | ppm/V           |

| FREQUENCY RESPONSE                                               |                   |                                                  |      |                               |      |                 |

| Open-Loop Gain, Two Modes, 7.8kHz                                |                   | Pin Gain H/L                                     |      | 24/32                         |      | dB              |

| PROBE COIL LOOP                                                  |                   |                                                  |      |                               |      |                 |

| Input Voltage Clamp Range                                        |                   | Field Probe Current < 50mA                       |      | –0.7 to V <sub>DD</sub> + 0.7 | ,    | V               |

| Internal Resistor, IS1 or IS2 to V <sub>DD1</sub> <sup>(2)</sup> | R <sub>HIGH</sub> |                                                  | 47   | 59                            | 71   | Ω               |

| Internal Resistor, IS1 or IS2 to GND1 <sup>(2)</sup>             | R <sub>LOW</sub>  |                                                  | 60   | 75                            | 90   | Ω               |

| Resistance Mismatch Between IS1 and IS2 <sup>(2)</sup>           |                   | ppm of R <sub>HIGH</sub> + R <sub>LOW</sub>      |      | 300                           | 1500 | ppm             |

| Total Input Resistance <sup>(3)</sup>                            |                   |                                                  |      | 134                           | 200  | Ω               |

| Comparator Threshold Current <sup>(3)</sup>                      |                   |                                                  | 22   | 28                            | 34   | mA              |

| Minimum Probe Loop Half-Cycle <sup>(2)</sup>                     |                   |                                                  | 250  | 280                           | 310  | ns              |

| Probe Loop Minimum Frequency                                     |                   |                                                  | 250  |                               |      | kHz             |

| No Oscillation Detect (Error) Suppression                        |                   |                                                  |      | 35                            |      | μs              |

| COMPENSATION COIL DRIVER, H-BRIDGE                               |                   |                                                  |      |                               |      |                 |

| Peak Current(2)                                                  |                   | $V_{ICOMP1} - V_{ICOMP2} = 4.0V_{PP}$            |      | 250                           |      | mA              |

| Voltage Swing                                                    |                   | 20Ω Load                                         | 4.2  |                               |      | V <sub>PP</sub> |

| Output Common-Mode Voltage                                       |                   |                                                  |      | V <sub>DD2</sub> /2           |      | V               |

| Wire Break Detect, Threshold Current <sup>(5)</sup>              |                   | I <sub>COMP1</sub> and I <sub>COMP2</sub> Railed |      | 33                            | 57   | mA              |

ELECTRICAL CHARACTERISTICS (continued) Boldface limits apply over the specified temperature range,  $T_J = -40^{\circ}$ C to +125°C, with zero output current I<sub>COMP</sub>.

At  $T_A = +25^{\circ}C$  and  $V_{DD1} = V_{DD2} = +5V$  with external 100kHz filter BW, unless otherwise noted.

|                                |                                               |       | DRV401 |        |        |

|--------------------------------|-----------------------------------------------|-------|--------|--------|--------|

| PARAMETER                      | CONDITIONS                                    | MIN   | TYP    | MAX    | UNITS  |

| VOLTAGE REFERENCE              |                                               |       |        |        |        |

| Voltage <sup>(2)</sup>         | No Load                                       | 2.495 | 2.5    | 2.505  | V      |

| Drift <sup>(2)</sup>           | No Load                                       |       | ±5     | ±50    | ppm/°C |

| PSRR <sup>(2)</sup>            |                                               |       | ±15    | ±200   | μV/V   |

| Load Regulation <sup>(2)</sup> | Load to GND/V <sub>DD</sub> , dI = 0mA to 5mA |       | 0.15   |        | mV/mA  |

| Short-Circuit Current ISC      | REFOUT Connected to VDD                       |       | +20    |        | mA     |

|                                | REFOUT Connected to GND                       |       | -18    |        | mA     |

| DEMAGNETIZATION                |                                               |       |        |        |        |

| Duration                       | See Timing Diagram                            |       | 106    | 130(3) | ms     |

| DIGITAL I/O                                 |                           |                          |    |

|---------------------------------------------|---------------------------|--------------------------|----|

| LOGIC INPUTS (DEMAG, GAIN, and CCdiag Pins) | CMOS Type Levels          |                          |    |

| Pull-Up High Current (CCdiag)               | $3.5 < V_{IN} < V_{DD}$   | 160                      | μΑ |

| Pull-Up Low Current (CCdiag)                | 0 < V <sub>IN</sub> < 1.5 | 5                        | μΑ |

| Logic Input Leakage Current                 | $0 < V_{IN} < V_{DD}$     | 0.01 5                   | μΑ |

| Logic Level, Input: L/H                     |                           | 2.1/2.8                  | V  |

| Hysteresis                                  |                           | 0.7                      | V  |

| OUTPUTS (ERROR AND OVER-RANGE Pins)         |                           |                          |    |

| Logic Level, Output: L                      | 4mA Sink                  | 0.3                      | V  |

| Logic Level, Output: H                      |                           | No Internal Pull-Up      |    |

| OUTPUTS (PWM and PWM Pins)                  | Push-Pull Type            |                          |    |

| Logic Level L                               | 4mA Sink                  | 0.2                      | V  |

| Logic Level H                               | 4mA Source                | (V <sub>DD</sub> ) – 0.4 | V  |

| POWER SUPPLY                                                    |                 |                                               |     | İ   |      |      |

|-----------------------------------------------------------------|-----------------|-----------------------------------------------|-----|-----|------|------|

| Specified Voltage Range                                         | V <sub>DD</sub> |                                               | 4.5 | 5   | 5.5  | v    |

| Power-On Reset Threshold                                        | Vrst            |                                               |     | 1.8 |      | V    |

| Quiescent Current [I(V <sub>DD1</sub> ) + I(V <sub>DD2</sub> )] | lQ              | I <sub>COMP</sub> = 0mA, Sensor Not Connected |     |     | 6.8  | mA   |

| Brownout Voltage Level <sup>(2)</sup>                           |                 |                                               |     | 4   |      | V    |

| Brownout Indication Delay                                       |                 |                                               |     | 135 |      | μs   |

| TEMPERATURE RANGE                                               |                 |                                               |     |     |      |      |

| Specified Range                                                 | TJ              |                                               | -40 |     | +125 | °C   |

| Operating Range                                                 | TJ              |                                               | -50 |     | +150 | °C   |

| Package Thermal Resistance                                      |                 |                                               |     |     |      |      |

| QFN Surface-Mount                                               | $	heta_{JA}$    | See Note 6                                    |     | 40  |      | °C/W |

| SO PowerPAD Surface-Mount                                       | $\theta_{JA}$   | See Note 6                                    |     | 27  |      | °C/W |

Parameter value referred to output (RTO).

See Typical Characteristic curves.

(3) Total input resistance and comparator threshold current are inversely related. See Figure 2a.

(4) For VAC sensors, 0.2% of PWM offset approximately corresponds to 10mA primary current offset per winding.

(5) See *Compensation Driver* section in Applications Information.

(6) See Applications Information section for information on power dissipation, layout considerations, and proper PCB soldering and heat-sinking technique.

#### TEXAS INSTRUMENTS www.ti.com

SBVS070A - JUNE 2006 - REVISED OCTOBER 2006

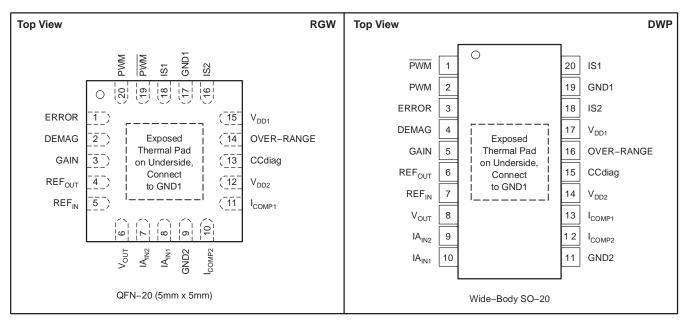

#### **PIN CONFIGURATIONS**

#### **PIN ASSIGNMENTS**

| NAME                | NO. | DESCRIPTION                                                      |

|---------------------|-----|------------------------------------------------------------------|

| ERROR               | 1   | Error flag: open-drain output, see the Error Conditions section. |

| DEMAG               | 2   | Control input, see the Demagnetization section.                  |

| GAIN                | 3   | Control input for open-loop gain: low = normal, high = $-8$ dB.  |

| REFOUT              | 4   | Output for internal 2.5V reference voltage.                      |

| REF <sub>IN</sub>   | 5   | Input for zero reference to differential amplifier.              |

| V <sub>OUT</sub>    | 6   | Output for differential amplifier.                               |

| IA <sub>IN2</sub>   | 7   | Noninverting input of differential amplifier.                    |

| IA <sub>IN1</sub>   | 8   | Inverting input of differential amplifier.                       |

| GND2                | 9   | Ground connection. Connect to GND1.                              |

| I <sub>COMP2</sub>  | 10  | Output 2 of compensation coil driver.                            |

| I <sub>COMP1</sub>  | 11  | Output 1 of compensation coil driver.                            |

| V <sub>DD2</sub>    | 12  | Supply voltage. Connect to V <sub>DD1</sub> .                    |

| CCdiag              | 13  | Control input for wire-break detection: high = enable.           |

| OVER-RANGE          | 14  | Open-drain output for over-range indication: low = over-range.   |

| V <sub>DD1</sub>    | 15  | Supply voltage.                                                  |

| IS2                 | 16  | Probe connection 2.                                              |

| GND1                | 17  | Ground connection.                                               |

| IS1                 | 18  | Probe connection 1.                                              |

| PWM                 | 19  | PWM output from probe circuit (inverted).                        |

| PWM                 | 20  | PWM output from probe circuit.                                   |

| Exposed Thermal Pad |     | Connect to GND1.                                                 |

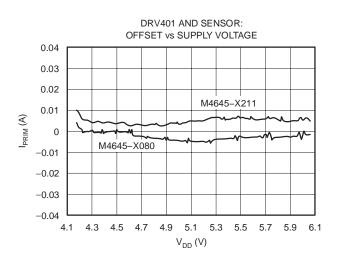

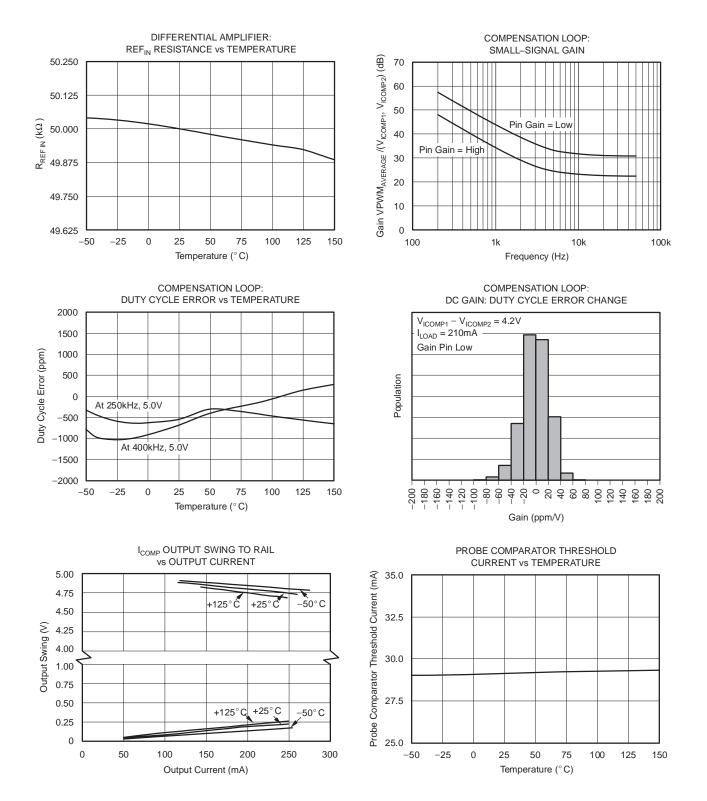

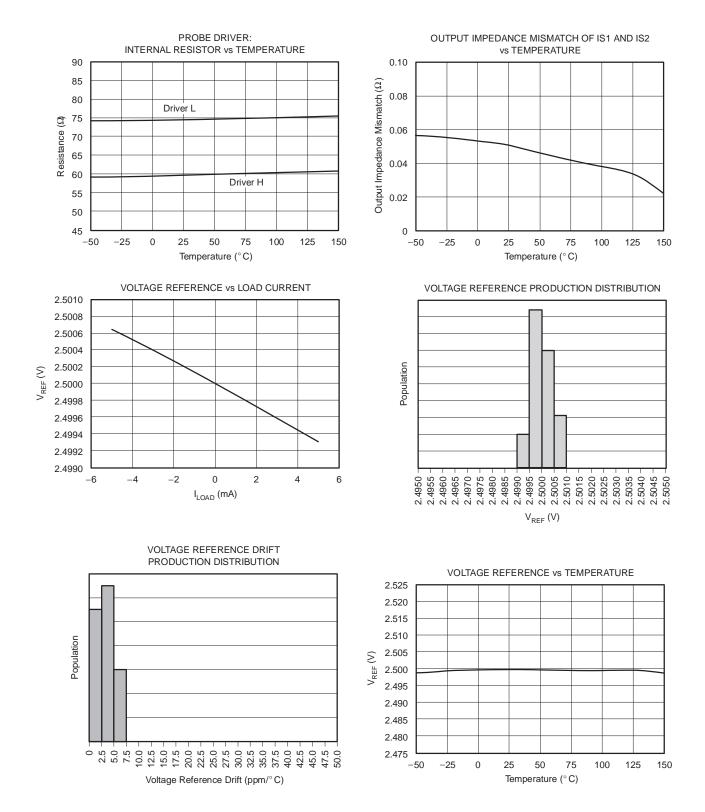

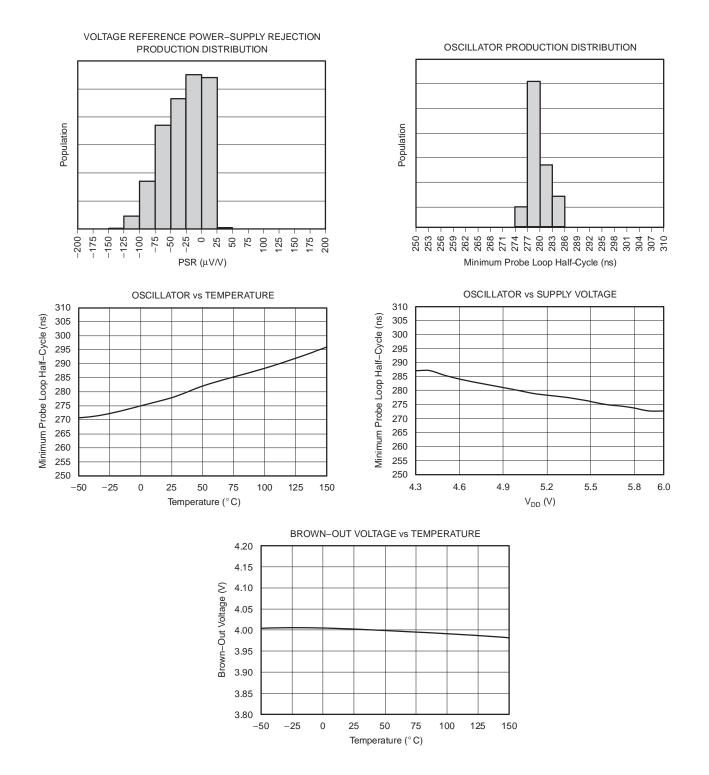

#### **TYPICAL CHARACTERISTICS**

At  $T_A = +25^{\circ}C$  and  $V_{DD1} = V_{DD2} = +5V$  with external 100kHz filter BW, unless otherwise noted.

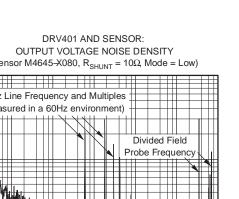

OUTPUT VOLTAGE NOISE DENSITY (Sensor M4645–X080,  $R_{SHUNT} = 10\Omega$ , Mode = Low) 100 60Hz Line Frequency and Multiples (measured in a 60Hz environment) V<sub>N</sub> (μV/VHz) Divided Field Probe Frequency 10 0.1 0.1 100 10 1k 10k 100k 1 Frequency (Hz)

Texas **STRUMENTS** www.ti.com

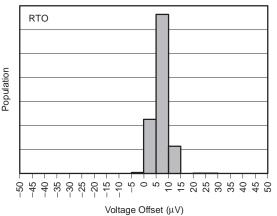

DIFFERENTIAL AMPLIFIER: VOLTAGE OFFSET PRODUCTION DISTRIBUTION

#### **TYPICAL CHARACTERISTICS (Continued)**

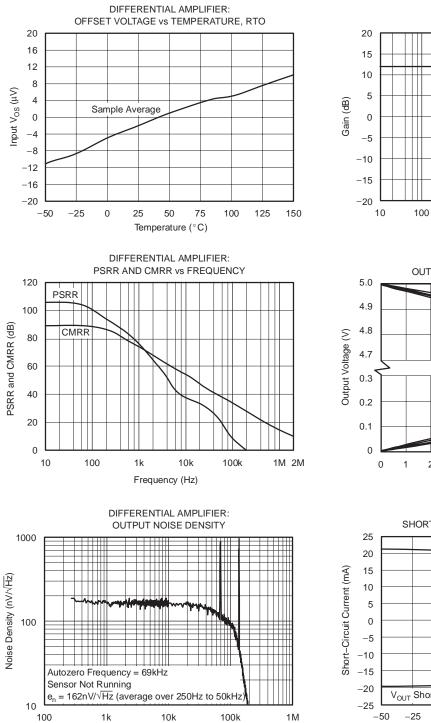

At  $T_A = +25^{\circ}C$  and  $V_{DD1} = V_{DD2} = +5V$  with external 100kHz filter BW, unless otherwise noted.

Frequency (Hz)

DIFFERENTIAL AMPLIFIER: OUTPUT VOLTAGE vs OUTPUT CURRENT

DIFFERENTIAL AMPLIFIER: SHORT-CIRCUIT CURRENT vs TEMPERATURE

### **TYPICAL CHARACTERISTICS (Continued)**

### **TYPICAL CHARACTERISTICS (Continued)**

SBVS070A - JUNE 2006 - REVISED OCTOBER 2006

## **TYPICAL CHARACTERISTICS (Continued)**

#### **TYPICAL CHARACTERISTICS (Continued)**

# **APPLICATIONS INFORMATION**

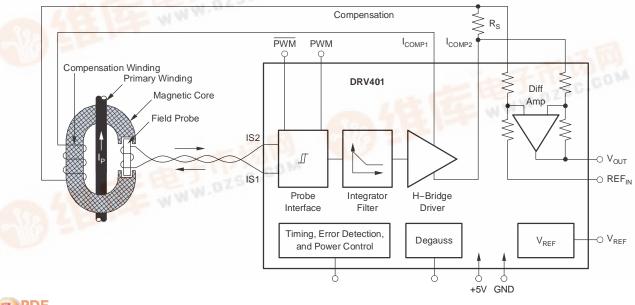

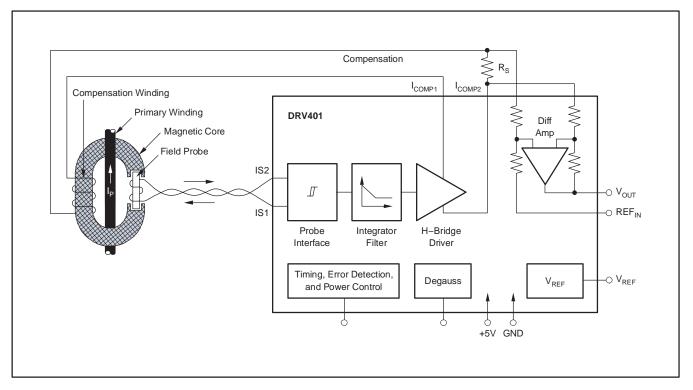

#### FUNCTIONAL PRINCIPLE OF CLOSED-LOOP CURRENT SENSORS WITH MAGNETIC PROBE USING THE DRV401

Closed-loop current sensors measure current over wide frequency ranges, including dc. These types of devices offer a contact-free method as well as excellent galvanic isolation performance combined with high resolution, accuracy, and reliability.

At dc and in low-frequency ranges, the magnetic field induced from the current in the primary winding is compensated by a current flowing through a compensation winding. A magnetic field probe, located in the magnetic core loop, detects the magnetic flux. This probe delivers the signal to the amplifier that drives the current through the compensation coil, bringing the magnetic flux back to zero. This compensation current is proportional to the primary current, relative to the winding ratio.

In higher frequency ranges, the compensation winding acts as the secondary winding in the current transformer, while the H-bridge compensation driver is rolled off and provides low output impedance.

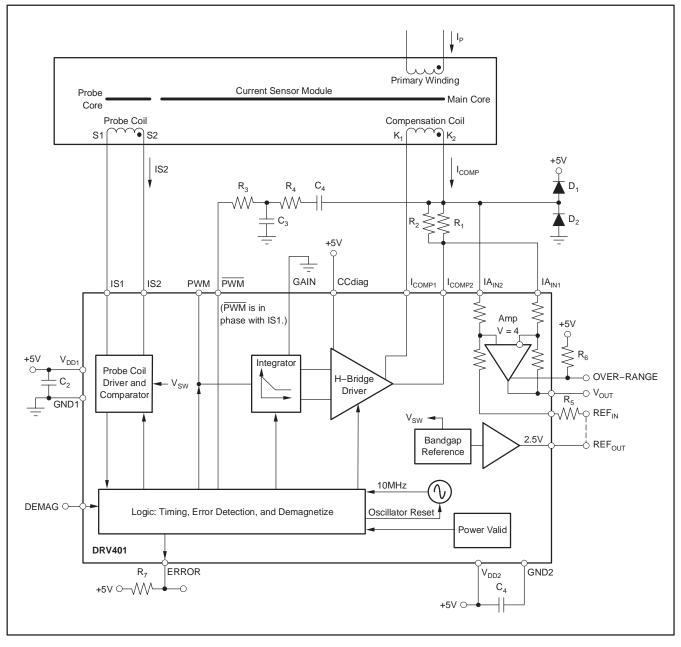

A difference amplifier senses the voltage across a small shunt resistor that is connected to the compensation loop. This difference amplifier generates the output voltage that is referenced to  $\text{REF}_{\text{IN}}$  and is proportional to the primary current. Figure 1 shows the DRV401 used as a compensation current sensor.

Figure 1. Principle of Compensation Current Sensor with the DRV401

#### FUNCTIONAL DESCRIPTION

The DRV401 operates from a single +5V supply. It is a complete sensor signal conditioning circuit that directly connects to the current sensor, providing all necessary functions for the sensor operation. The DRV401 provides magnetic field probe excitation, signal conditioning, and compensation coil driver amplification. In addition, it detects error conditions and handles overload situations. A precise differential amplifier allows translation of the compensation current into an output voltage using a small shunt resistor. A buffered voltage reference can be used for comparator, analog-to-digital converter (ADC), or bipolar zero reference voltages.

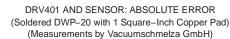

Dynamic error correction ensures high dc precision over temperature and long-term accuracy. The DRV401 uses analog signal conditioning; the internal loop filter and integrator are switched capacitor-based circuits. Therefore, the DRV401 allows combination with high-precision sensors for exceptional accuracy and resolution. The typical characteristic curve, *DRV401 and Sensor Linearity*, shows an example of the linearity and temperature stability achieved by the device.

A demagnetization cycle can be initiated on demand or on power-up. This cycle reduces offset and restores high performance after a strong overload condition. An internal clock and counter logic generate the degauss function. The same clock controls power-up, overload detection and recovery, error, and time-out conditions.

The DRV401 is built on a highly reliable CMOS process. Unique protection cells at critical connections enable the design to handle inductive energy.

#### MAGNETIC PROBE (SENSOR) INTERFACE

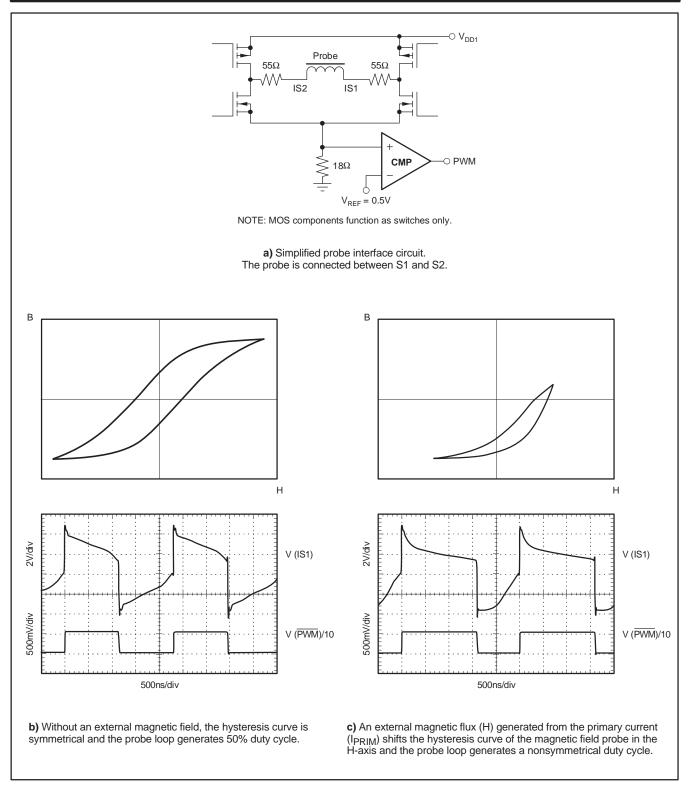

The magnetic field probe consists of an inductor wound on a soft magnetic core. The probe is connected between pins IS1 and IS2 of the probe driver that applies approximately +5V (the supply voltage) through resistors across the probe coil (see Figure 2a).

#### SBVS070A - JUNE 2006 - REVISED OCTOBER 2006

The probe core reaches saturation at a current of typically 28mA (see Figure 2a). The comparator is connected to  $V_{REF}$  by approximately 0.5V. A current comparator detects the saturation and inverts the excitation voltage polarity, causing the probe circuit to oscillate in a frequency range of 250kHz to 550kHz. The oscillating frequency is a function of the magnetic properties of the probe core and its coil.

The current rise rate is a function of the coil inductance:  $dI = L \times V \times dT$ . However, the inductance of the field probe is low while its core material is in saturation (the horizontal part of the hysteresis curve) and is high at the vertical part of the hysteresis curve. The resulting inductance and the series resistance determine the output voltage and current versus time performance characteristic.

Without external magnetic influence, the duty cycle is exactly 50% because of the inherent symmetry of the magnetic hysteresis; the probe inductor is driven from –B saturation through the high inductance range to +B saturation and back again in a time-symmetric manner (see Figure 2b).

If the core material is magnetized in one direction, a long and a short charge time result because the probe current through the inductors generates a field that either subtracts or adds to the flux in the probe core, either driving the probe core out of saturation or further into saturation (see Figure 2c). The current into the probe is limited by the voltage drops across the probe driver resistors.

The DRV401 continuously monitors the logic magnetic flux polarity state. In the case of distortion noise and excessive overload that could fully saturate the probe, the overload control circuit recovers the probe loop. During an overload condition, the probe oscillation frequency increases to approximately 1.6MHz until limited by the internal timing control.

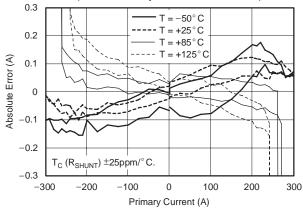

In an overload condition, the compensation current ( $I_{COMP}$ ) driver cannot deliver enough current into the sensor secondary winding, and the magnetic flux in the sensor main core becomes uncompensated.

SBVS070A - JUNE 2006 - REVISED OCTOBER 2006

Figure 2. Magnetic Probe, Hysteresis, and Duty Cycle

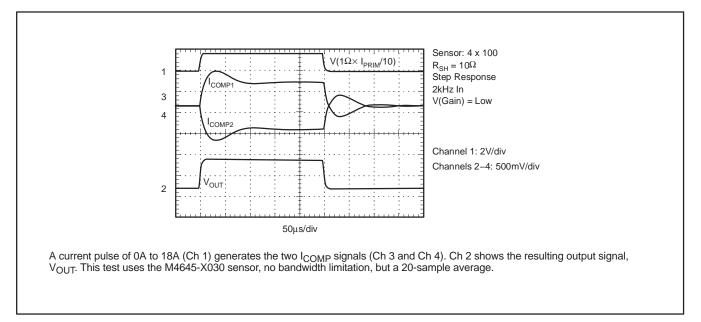

The transition from normal operation to overload happens relatively slowly, because the inherent sensor transformer characteristics induce the initial primary current step, as shown in Figure 3. As the transformer-induced secondary current starts to decay, the compensation feedback driver increases its output voltage to maintain the sensor core flux compensation at zero.

When the system compensation loop reaches its driving limit, the rising magnetic flux causes one of the probe PWM half-periods to become shorter. The minimum half-period of the probe oscillation is limited by the internal timing to 280ns, based on the properties of the VAC magnetic sensors. After three consecutive cycles of the same half-period being shorter than 280ns, the DRV401 goes into overload-latch mode. The device stores the  $I_{COMP}$  driver output signal polarity and continues producing the skewed-duty cycle PWM signal. This action prevents the loss of compensation signal polarity information during very strong overloads. In this case, both PWM half-periods are short and approximately equal, because the field probe stays completely in one of the saturated regions.

The overload-latch condition is removed after the primary current goes low enough for the  $I_{COMP}$  driver to compensate, and both half-periods of the probe driver oscillation become longer than 280ns (the field probe comes out of the saturated region).

Peak voltages and currents can be generated during normal operations as well as overload conditions. Therefore, both probe connection pins are internally protected against coupled energy from the magnetic core. Wiring between probe and IC inputs should be short and guarded against interference; see *Layout Considerations*. For reliable operation, error detection circuits monitor the probe operation:

- 1. If the probe driver comparator (CMP) output stays low longer than  $32\mu$ s, the ERROR flag asserts active, and the compensation current (I<sub>COMP</sub>) is set to zero.

- 2. If the probe driver period is less than 275ns on three consecutive pulses, the ERROR flag asserts active.

See the Error Conditions section for more details.

#### **PWM PROCESSING**

The outputs PWM and PWM represent the probe output signal as a differential PWM signal. It can drive external circuitry or be used for synchronous ripple reduction. The PWM signal from the probe excitation and sense stage is internally connected to а high-performance, switched-capacitor integrator followed by an integrating-differentiating filter. This filter converts the PWM signal into a filtered delta signal and prepares it for driving the analog compensation coil driver. The gain roll-off frequency of the filter stage is set to provide high dc gain and loop stability. If additional gain is added from external circuitry, the internal gain can be reduced by 8dB, asserting the GAIN pin high (see the External Compensation Coil Driver section).

Figure 3. Primary Current Step Response

#### **COMPENSATION DRIVER**

The compensation coil driver provides the driving current for the compensation coil. A fully differential driver stage offers high signal voltages to overcome the wire resistance of the coil with only +5V supply. The compensation coil is connected between  $I_{COMP1}$  and  $I_{COMP2}$ , both generating an analog voltage across the coil (see Figure 3) that turns into current from the wire resistance (and eventually from the inductance). The compensation current represents the primary current transformed by the turns ratio. A shunt resistor is connected in this loop and the high-precision difference amplifier translates the voltage from this shunt to an output voltage.

Both compensation driver outputs provide low impedance over a wide frequency range to insure smooth transitions between the closed-loop compensation frequency range and the high-frequency range, where the primary winding directly couples the primary current into the compensation coil at a rate set by the winding ratio.

The two compensation driver outputs are designed with protection circuitry to handle inductive energy. However, additional external protection diodes might be necessary for high current sensors.

For reliable operation, a wire break in the compensation circuit can be detected. If the feedback loop is broken, the integrating filter drives the outputs  $I_{COMP1}$  and  $I_{COMP2}$  to the opposite rails. With one of these pins coming within 300mV to ground, a comparator tests for a minimum current flowing between  $I_{COMP1}$  and  $I_{COMP2}$ . If this current stays below the threshold current level for at least 100µs, the ERROR pin is asserted active (low). The threshold current level for this test is less than 57mA at 25°C and 65mA at -40°C, if the  $I_{COMP}$  pins are fully railed (see the Typical Characteristics).

$$R_{MAX} = \frac{V_{OUT}}{65mA}$$

(1)

NSTRUMENTS www.ti.com

Where:

$V_{\text{OUT}}$  equals the peak voltage between  $I_{\text{COMP1}}$  and  $I_{\text{COMP2}}$  at a 65mA drive current.

R<sub>MAX</sub> equals the sum of the coil and the shunt resistance.

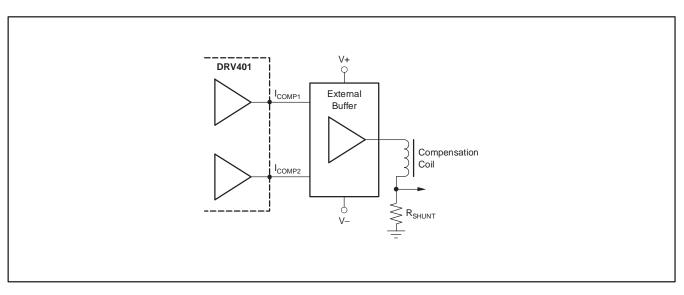

#### EXTERNAL COMPENSATION COIL DRIVER

An external driver for the compensation coil can be connected to the  $I_{COMP1}$  and  $I_{COMP2}$  outputs. To prevent a wire break indication, CCdiag has to be asserted low.

An external driver can provide both a higher drive voltage and more drive current. It also moves the power dissipation to the external transistors, thereby allowing a higher winding resistance in the compensation coil and more current. Figure 4 shows a block diagram of an external compensation coil driver. To drive the buffer, either one or both I<sub>COMP</sub> outputs can be used. Note, however, that the additional voltage gain could cause instability of the loop. Therefore, the internal gain can be reduced by approximately 8dB by asserting the GAIN pin high. R<sub>SHUNT</sub> is connected to GND to allow for a single-ended external compensation driver. The differential amplifier can continue to sense the voltage, and used for the gain and over-range comparator or ERROR flag.

Figure 4. DRV401 with External Compensation Coil Driver and R<sub>SHUNT</sub> Connected to GND

TEXAS INSTRUMENTS www.ti.com

#### SHUNT SENSE AMPLIFIER

The differential (H-bridge) driver arrangement for the compensation coil requires a differential sense amplifier for the shunt voltage. This differential amplifier offers wide bandwidth and a high slew rate for fast current sensors. Excellent dc stability and accuracy result from an auto-zero technique. The voltage gain is 4V/V, set by precisely matched and stable internal SiCr resistors.

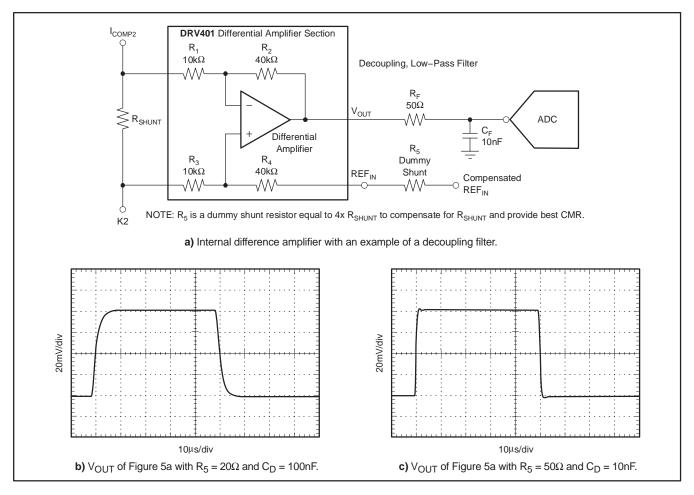

Both inputs of the differential amplifier are normally connected to the current shunt resistor. This resistor adds to the internal ( $10k\Omega$ ) resistor, slightly reducing the gain in this leg. For best common-mode rejection (CMR), a dummy shunt resistor ( $R_5$ ) is placed in series with the REF<sub>IN</sub> pin to restore matching of both resistor dividers, as shown in Figure 5a.

For gains of 4V/V:

$$4 = \frac{R_2}{R_1} = \frac{R_4 + R_5}{R_{SHUNT} + R_3}$$

(2)

With  $R_2/R_1 = R_4/R_3 = 4$ ;  $R_5 = R_{SHUNT} \times 4$

## **DRV401**

#### SBVS070A - JUNE 2006 - REVISED OCTOBER 2006

Typically, the gain error resulting from the resistance of  $R_{SHUNT}$  is negligible; for 70dB of common-mode rejection, however, the match of both divider ratios needs to be better than 1/3000.

The amplifier output can drive close to the supply rails, and is designed to drive the input of a SAR-type ADC; adding an RC low-pass filter stage between the DRV401 and the ADC is recommended. This filter not only limits the signal bandwidth but also decouples the high-frequency component of the converter input sampling noise from the amplifier output. For  $R_F$  and  $C_F$  values, refer to the specific converter recommendations in the specific product data sheet. Empirical evaluation may be necessary to obtain optimum results.

The output can drive 100pF directly and shows 50% overshoot with approximately 1nF capacitance. Adding R<sub>F</sub> allows much larger capacitive loads, as shown in Figure 5b and Figure 5c. Note that with R<sub>F</sub> of only 20 $\Omega$ , the load capacitor should be either smaller than 1nF or larger than 33nF to avoid overshoot; with R<sub>F</sub> of 50 $\Omega$  this transient area is avoided.

Figure 5. Internal Difference Amplifier with Example of a Decoupling Filter

#### SBVS070A - JUNE 2006 - REVISED OCTOBER 2006

The reference input (REF<sub>IN</sub>) is the reference node for the exact output signal (V<sub>OUT</sub>). Connecting REF<sub>IN</sub> to the reference output (REF<sub>OUT</sub>) results in a live zero reference voltage of 2.5V. Using the same reference for REF<sub>IN</sub> and the ADC avoids mismatch errors that exist between two reference sources.

#### **OVER-RANGE COMPARATOR**

High peak current can overload the differential amplifier connected to the shunt. The OVER-RANGE pin, an open-drain output, indicates an over-voltage condition for the differential amplifier by pulling low. The output of this flag is suppressed for  $3\mu$ s, preventing unwanted triggering from transients and noise. This pin returns to high as soon as the overload condition is removed (external pull-up required to return the pin high).

This ERROR flag not only provides a warning about a signal clipping condition, but is also a window comparator output for actively shutting off circuits in the system. The value of the shunt resistor defines the operating window for the current. It sets the ratio between the nominal signal and the trip level of the Over-Range flag. The trip current of this window comparator is calculated using the following example:

With a 5V supply, the output voltage swing is approximately  $\pm 2.45V$  (load and supply voltage-dependent).

The gain of 4V/V allows an input swing of  $\pm 0.6125V$ .

Thus, the clipping current is  $I_{MAX} = 0.6125 V/R_{SHUNT}$ .

See the differential amplifier curve of the Typical Characteristics, *Output Voltage vs Output Current*.

The over-range condition is internally detected as soon as the amplifier exceeds its linear operating range, not just a set voltage level. Therefore, the error or the over-range comparator level is reliably indicated in fault conditions such as output shorts, low load or low supply conditions. As soon as the output cannot drive the voltage higher, the flag is activated. This configuration is a safety improvement over a voltage level comparator.

**NOTE:** The internal resistance of the compensation coil may prevent high compensation current from flowing because of  $I_{COMP}$  driver overload. Therefore, the differential amplifier may not overload with this current. However, a fast rate of change of the primary current would be transmitted through transformer action and safely trigger the overload flag.

#### **VOLTAGE REFERENCE**

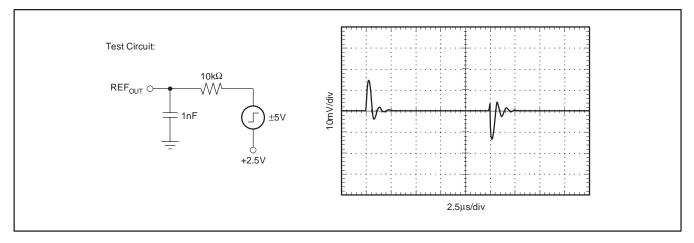

The precision 2.5V reference circuit offers low drift (typically 10ppm/K) and is used for internal biasing; it is also connected to the REF<sub>OUT</sub> pin. The circuit is intended as the reference point of the output signal to allow a bipolar signal around it. This output is buffered for low impedance and tolerates sink and source currents of  $\pm$ 5mA. Capacitive loads can be directly connected, but generate ringing on fast load transients. A small series resistor of a few ohms improves the response, especially for a capacitive load in the range of 1µF. Figure 6 shows the transient load regulation with 1nF direct load.

The reference source is part of the integrated circuit and referenced to GND2. Large current pulses driving the compensation coil can generate a voltage drop in the GND connection that would add on to the reference voltage. Therefore, a low impedance GND layout is critical to handle the currents and the high bandwidth of this IC.

#### DEMAGNETIZATION

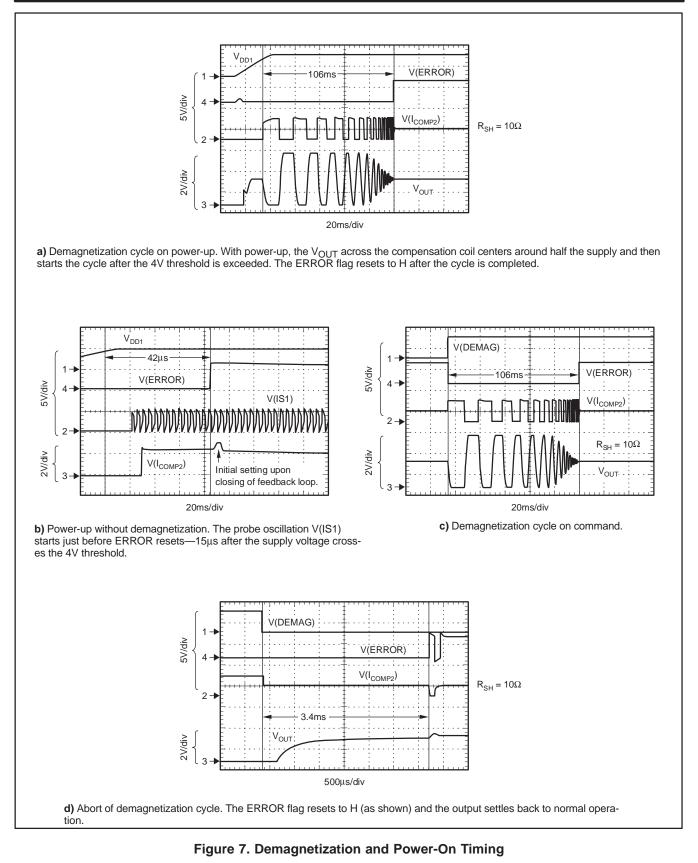

Iron cores are not immune to residual (remanence) magnetism. The residual remanence can produce a signal offset error, especially after strong current overload, which goes along with high magnetic field density. Therefore, the DRV401 includes a signal generator for a demagnetization cycle. The digital control pin, DEMAG, starts this cycle on demand after this pin is held high for at least 25.6 $\mu$ s. Shorter pulses are ignored. The cycle lasts for approximately 110ms. During this time, the Error flag is asserted low to indicate that the output is not valid. When DEMAG is high during power-on, a demagnetization cycle immediately initiates (12 $\mu$ s) after power-on (V<sub>DD</sub> > 4V). Holding DEMAG low avoids this cycle at power-up (see the *Power-On and Brownout* section).

The probe circuit is in normal operation and oscillates during the demagnetization cycle. The outputs  $\overline{\text{PWM}}$  and PWM are active accordingly.

A demagnetization cycle can be aborted by pulling DEMAG low, filtered by  $25\mu s$  to ignore glitches (see Figure 7). In a typical circuit, the DEMAG pin may be connected to the positive supply, which enables a degauss cycle every time the unit is powered on.

The degauss cycle is based on an internal clock and counter logic. The maximum current is limited by the resistance of the connected coil in series with the shunt resistor. The DEMAG logic input requires a +5V CMOS-compatible signal.

#### **POWER-ON AND BROWNOUT**

Power-on is detected with the supply voltage going higher than 4V at  $V_{DD1}$ . When DEMAG is high, a degauss cycle is started (see Figure 7a). During this time the ERROR flag remains low, indicating the not ready condition. Maintaining DEMAG low prevents this cycle, and the DRV401 starts operation approximately  $32\mu s$  after

#### SBVS070A - JUNE 2006 - REVISED OCTOBER 2006

power-up. If no probe error conditions are detected within four full cycles (that is, the probe half-periods are shorter than  $32\mu s$  and longer than 280ns), the compensation driver starts and the ERROR pin indicates the ready condition by going high, typically about  $42\mu s$  after power-up.

**NOTE:** an external pull-up resistor is required to pull the ERROR pin high.

Both supply pins ( $V_{DD1}$  and  $V_{DD2}$ ) should not differ by more than 100mV for proper device operation. They are normally connected together or separately filtered (see *Layout Considerations*).

The DRV401 tests for low supply voltage with a brown-out voltage level of +4V; proper power conditions must be supplied. Good power-supply and low ESR bypass capacitors are required to maintain the supply voltage during the large current pulses that the DRV401 can drive.

A critical voltage level is derived from the proper operation of the probe driver. The probe interface relies on a peak current flowing through the probe to trip the comparator. The probe resistance plus the internal resistance of the driver (see Electrical Characteristics specification, *Probe Coil Loop, Internal Resistor*) sets the lower limit for the acceptable supply voltage. Voltage drops lasting less than 31µs are ignored. The probe error detection activates the ERROR pin as soon as proper oscillation fails for more than 32µs.

A low supply voltage condition, or brown-out, is detected at +4V. Short and light voltage drops of less than 100µs are ignored, provided the probe circuit continues to operate. If the probe no longer operates, the ERROR pin goes active. Signal overload recovery is only provided if the probe loop was not discontinued.

A supply drop lasting longer than 100 $\mu$ s generates power-on reset. A voltage dip down to +1.8V (for V<sub>DD1</sub>) also initiates a power-on reset.

#### SBVS070A - JUNE 2006 - REVISED OCTOBER 2006

#### **ERROR CONDITIONS**

In addition to the Over-Range flag that indicates signal clipping in the output amplifier (differential amplifier), a system error flag is provided. The ERROR flag indicates conditions when the output voltage does not represent the primary current. It is active during a demagnetization cycle, during a power-fail or brown-out. It also goes active with an open or short-circuit in the probe loop. As soon as the error condition is no longer present and the circuit has returned to normal operation, the flag resets.

Both the ERROR and Over-Range flags are open-drain logic outputs. They can be connected together for a wired-OR and require an external pull-up resistor for proper operation.

The following conditions result in ERROR flag activation (ERROR asserts low):

- 1. The probe comparator stays low for more than  $32\mu$ s. This condition occurs either if the probe coil connection is open or if the supply voltage dips to the level where the required saturation current cannot be reached. During the  $32\mu$ s timeout, the I<sub>COMP</sub> driver remains active but goes inactive thereafter. In case of recovery, ERROR is low and the I<sub>COMP</sub> driver remains in reset for another 3.3ms.

- 2. The probe driver pulse-width is less than 280ns for three consecutive periods. This condition indicates either a shorted field probe coil or a fully-saturated sensor at start-up. If this condition persists longer than  $25\mu$ s and then recovers, the ERROR flag remains low and I<sub>COMP</sub> is in reset for another 3.3ms. If the condition lasts less than  $25\mu$ s, the ERROR flag recovers immediately and the I<sub>COMP</sub> driver is not interrupted.

- During demagnetization, if the cycle is aborted early by pulling DEMAG low, the ERROR flag stays low for another 3.3ms (I<sub>COMP</sub> is disabled during this time).

#### SBVS070A - JUNE 2006 - REVISED OCTOBER 2006

- 4. An open compensation coil is detected (longer than  $100\mu$ s). Note: the probe driver, the PWM signal filter and the I<sub>COMP</sub> driver continue to function in normal mode—only the ERROR flag is asserted in this case. This condition indicates that not enough current is flowing in the I<sub>COMP</sub> driver output; this condition might be the result of a high-resistance compensation coil or the connection of an external driver. Detection of this condition can be disabled by setting the CCdiag pin low.

- 5. At power-on after  $V_{DD1}$  crosses the +4V threshold, the ERROR flag is low for approximately 42 $\mu$ s.

- 6. A supply voltage low (brown-out) condition lasts longer than  $100\mu$ s. Recovery is the same as power-up, either with or without a demag cycle.

#### PROTECTION RECOMMENDATIONS

The inputs  $IA_{IN1}$  and  $IA_{IN2}$  require external protection to limit the voltage swing beyond 10V of the supply voltage. The driver outputs  $I_{COMP1}$  and  $I_{COMP2}$  can handle high current pulses protected by internal clamp circuits to the supply voltage. If repeated over-currents of large magnitudes are expected, connect external Schottky diodes to the supply rails. This external protection prevents current flowing into the die.

The probe connections IS1 and IS2 are protected with diode clamps to the supply rails. In normal applications, no external protection is required. The maximum current must be limited to  $\pm$ 75mA.

All other pins offer standard protection—see the Absolute Maximum Ratings table.

### BASIC CONNECTION EXAMPLE

The circuit shown in Figure 8 offers an axample of a fully-connected current sensor system.

Figure 8. Basic Connection Circuit

The connection example in Figure 8 illustrates the few external components required for optimal performance. Each component is described in the following list:

$\mathbf{I}_{P}$  is the primary current to be measured;  $K_{1}$  and  $K_{2}$  connect to the compensation coil. **S1** and **S2** connect to the magnetic field probe. The dots indicate the winding direction on the sensor main core.

$R_1$  and  $R_2$  form the shunt resistor  $R_{SHUNT}$ . This resistance is split into two to allow for adjustments to the required  $R_{SHUNT}$  value. The accuracy and temperature stability of these resistors are part of the final system performance.

$R_3$  and  $R_4$ , together with  $C_3$  and  $C_4$ , form a network that reduces the remaining probe oscillator ripple in the output signal. The component values depend on the sensor type and are tailored for best results. This network is not required for normal operation.

$\textbf{R_5}$  is the dummy shunt (R<sub>D</sub>) resistor used to restore the symmetry of both differential amplifier inputs.  $\textbf{R_5} = 4 \times \textbf{R}_{\text{SHUNT}}$ , but the accuracy is less important.

$R_6$  and  $R_7$  are pull-up resistors connected to the logic outputs.

$C_1$  and  $C_2$  are decoupling capacitors. Use low ESR-type capacitors connected close to the pins. Use low impedance printed circuit board (PCB) traces, either avoiding vias (plated-through holes) or using multiple vias. A combination of a large (> 1µF) and a small (< 4.7nF) capacitor are suggested. When selecting capacitors, make sure to consider the large pulse currents handled from the DRV401.

$\mathbf{D_1}$  and  $\mathbf{D_2}$  are protection diodes for the differential amplifier input. They are only needed if the voltage drop at  $R_{SHUNT}$  exceeds 10V at the maximum possible peak current.

SBVS070A - JUNE 2006 - REVISED OCTOBER 2006

#### LAYOUT CONSIDERATIONS

The DRV401 operates with relatively large currents and fast current pulses, and offers wide-bandwidth performance. It is often exposed to large distortion energy from both the primary signal and the operating environment. Therefore, the wiring layout must provide shielding and low-impedance connections between critical points.

Use low ESR capacitors for power-supply decoupling. Use a combination of a small capacitor and a large capacitor of  $1\mu$ F or larger. Use low-impedance tracks to connect the capacitors to the pins.

Both grounds should be connected to a local ground plane. Both supplies can be connected together; however, best results are achieved with separate decoupling (to the local GND plane) and ferrite beads in series with the main supply. The ferrite beads decouple the DRV401, reducing interaction with other circuits powered from the same supply voltage source.

The reference output is referred to GND2. A low-impedance, star-type connection is required to avoid the driver current and the probe current modulating the voltage drop on the ground track.

The connection wires of the difference amplifier to the shunt must be low resistance and of equal length. For best accuracy, avoid current in this connection. Consider using a *Kelvin Contact*-type connection. The required resistance value can be set using two resistors.

Wires and PCB traces for S1 and S2 should be very close or twisted.  $I_{COMP1}$  and  $I_{COMP2}$  should also be wired close together. To avoid capacitive coupling, run a ground shield between the S1/S2 and  $I_{COMP}$  wire pair or keep them distant from each other.

The compensation driver outputs  $(I_{COMP})$  are low frequency only; however, the primary signal (with high-frequency content present) is coupled into the compensation winding, the shunt, and the difference amplifier. Therefore, careful layout is recommended.

The output of  $\text{REF}_{\text{OUT}}$  and  $V_{\text{OUT}}$  can drive some capacitive loads, but avoid large direct capacitive loads; these loads increase internal pulse currents. Given the wide bandwidth of the differential amplifier, isolate any large capacitive load with a small series resistor. A small capacitor in the pF range can improve the transient response on a high resistive load.

The exposed thermal pad on the bottom of the package must be soldered to GND because it is internally connected to the substrate, which must be connected to the most negative potential. It is also necessary to solder the exposed pad to the PCB to provide structural integrity and long-term reliability.

#### POWER DISSIPATION

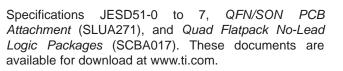

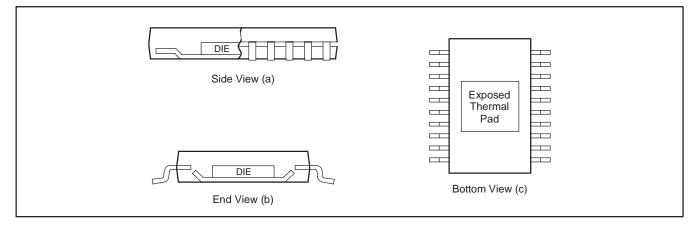

Using the thermally-enhanced PowerPAD<sup>™</sup> SO and QFN packages dramatically reduces the thermal impedance from junction to case. These packages are constructed using a down-set lead frame upon which the die is mounted, as shown in Figure 9a and Figure 9b. This arrangement results in the lead frame being exposed as a thermal pad on the underside of the package. Figure 9 shows the SO-20 package as an example. Because this thermal pad has direct thermal contact with the die, excellent thermal path away from the thermal pad.

The two outputs  $I_{COMP1}$  and  $I_{COMP2}$  are linear outputs. Therefore, the power dissipation on each output is proportional to the current multiplied by the internal voltage drop on the active transistor. For  $I_{COMP1}$  and  $I_{COMP2}$ , this internal voltage drop is the voltage drop to  $V_{DD2}$  or GND, according to the current-conducting side of the output.

Output short-circuits are particularly critical for the driver because the full supply voltage can be seen across the conducting transistor, and the current is not limited by anything other than the current density limitation of the FET. Permanent damage to the device can occur.

The DRV401 does not include temperature protection or thermal shut-down.

#### THERMAL PAD

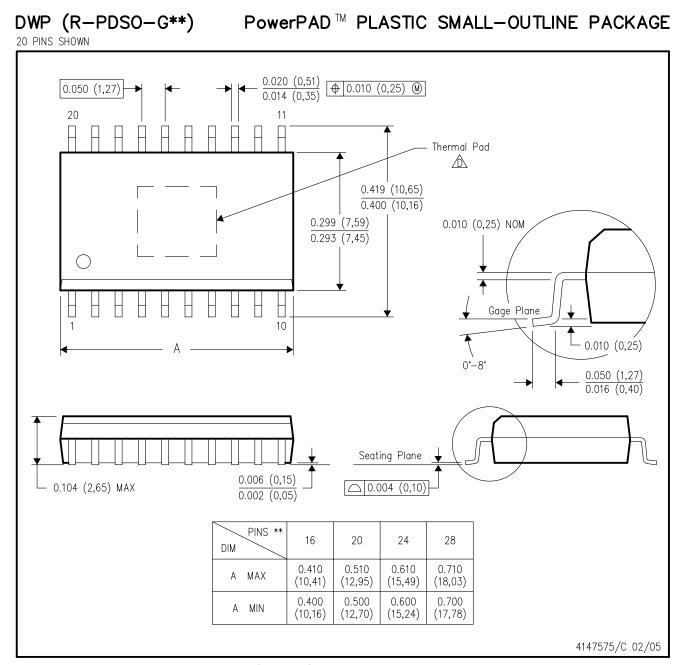

Packages with an exposed thermal pad are specifically designed to provide excellent power dissipation, but board layout greatly influences overall heat dissipation. Table 1 shows the thermal resistance  $(T_{JA})$  for the two packages with the exposed thermal pad soldered to a normal PCB, as described in Technical Brief SLMA002, *PowerPAD Thermally-Enhanced Package*. See also EIA/JEDEC

# Table 1. $\theta_{JA/JP}$ Estimations According To EIA/JED51-7

|                                            | QFN-20 | SO-20 |

|--------------------------------------------|--------|-------|

| θJP                                        | 9      | 9     |

| $\theta_{JA}$ Still Air                    | 40     | 35    |

| $\theta_{JA}$ with Forced Airflow (150lfm) | 38     | 32    |

$\theta_{1A}$  = junction-to-ambient thermal resistance,

$\theta_{\rm JP}$  = junction-to-pad thermal resistance,

Ifm = linear foot per minute.

**NOTE**: All thermal models have an accuracy  $\approx 20\%$ .

Measuring the temperature as close as possible to the exposed thermal pad is recommended. The relatively low thermal impedance,  $\theta_{JP}$  of less than 10°C/W (with some additional °C/W to the temperature test point on the PCB) allows good estimation of the junction temperature in the application.

The thermal pad on the PCB should contain nine or more vias for the QFN package. The same applies for the SO package, where the solder pad on the PCB can be larger than the exposed pad (for example, 6.6mm  $\times$  18mm) as recommended in the application literature noted previously.

Component population, layout of traces, layers, and air flow strongly influence heat dissipation. Worst-case load conditions should be tested in the real environment to ensure proper thermal conditions. Minimize thermal stress for proper long-term operation with a junction temperature well below  $+125^{\circ}C$ .

Figure 9. SO-20 Package Example of Thermally-Enhanced PowerPAD

# PACKAGE OPTION ADDENDUM

6-Dec-2006

#### **PACKAGING INFORMATION**

| Orderable Device | Status <sup>(1)</sup> | Package<br>Type    | Package<br>Drawing | Pins | Package<br>Qty | e Eco Plan <sup>(2)</sup>  | Lead/Ball Finish | MSL Peak Temp <sup>(3)</sup> |

|------------------|-----------------------|--------------------|--------------------|------|----------------|----------------------------|------------------|------------------------------|

| DRV401AIDWP      | ACTIVE                | SO<br>Power<br>PAD | DWP                | 20   | 25             | Green (RoHS & no Sb/Br)    | CU NIPDAU        | Level-2-260C-1 YEAR          |

| DRV401AIDWPG4    | ACTIVE                | SO<br>Power<br>PAD | DWP                | 20   | 25             | Green (RoHS &<br>no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR          |

| DRV401AIDWPR     | ACTIVE                | SO<br>Power<br>PAD | DWP                | 20   | 1000           | Green (RoHS &<br>no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR          |

| DRV401AIDWPRG4   | ACTIVE                | SO<br>Power<br>PAD | DWP                | 20   | 1000           | Green (RoHS &<br>no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR          |

| DRV401AIRGWR     | ACTIVE                | QFN                | RGW                | 20   | 2500           | Green (RoHS & no Sb/Br)    | CU NIPDAU        | Level-2-260C-1 YEAR          |

| DRV401AIRGWRG4   | ACTIVE                | QFN                | RGW                | 20   | 2500           | Green (RoHS & no Sb/Br)    | CU NIPDAU        | Level-2-260C-1 YEAR          |

| DRV401AIRGWT     | ACTIVE                | QFN                | RGW                | 20   | 250            | Green (RoHS & no Sb/Br)    | CU NIPDAU        | Level-2-260C-1 YEAR          |

| DRV401AIRGWTG4   | ACTIVE                | QFN                | RGW                | 20   | 250            | Green (RoHS & no Sb/Br)    | CU NIPDAU        | Level-2-260C-1 YEAR          |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

**TBD:** The Pb-Free/Green conversion plan has not been defined.

**Pb-Free (RoHS):** TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

<sup>(3)</sup> MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

**Important Information and Disclaimer:**The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

NOTES: A. All linear dimensions are in inches (millimeters).

B. This drawing is subject to change without notice.

C. Body dimensions do not include mold flash or protrusion not to exceed 0.006 (0,15).

This package is designed to be soldered to a thermal pad on the board. Refer to Technical Brief, PowerPad Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 for information regarding recommended board layout. This document is available at www.ti.com <a href="http://www.ti.com">http://www.ti.com</a>. See the product data sheet for details regarding the exposed thermal pad dimensions.

# **MECHANICAL DATA**

- The package thermal pad must be soldered to the board for thermal and mechanical performance.. See the Product Data Sheet for details regarding the exposed thermal pad dimensions.

- E. Falls within JEDEC MO-220.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products           |                        | Applications       |                           |

|--------------------|------------------------|--------------------|---------------------------|

| Amplifiers         | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters    | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP                | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Interface          | interface.ti.com       | Digital Control    | www.ti.com/digitalcontrol |

| Logic              | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt         | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers   | microcontroller.ti.com | Security           | www.ti.com/security       |

| Low Power Wireless | www.ti.com/lpw         | Telephony          | www.ti.com/telephony      |

|                    |                        | Video & Imaging    | www.ti.com/video          |

|                    |                        | Wireless           | www.ti.com/wireless       |

#### Mailing Address:

Post Office Box 655303 Dallas, Texas 75265

**Texas Instruments**

Copyright © 2006, Texas Instruments Incorporated