DS1201

## **DALLAS** SEMICONDUCTOR

# DS1201 Electronic Tag

#### **FEATURES**

- User-insertable, nonvolatile 1024 bits of read/write memory

- Low-power CMOS circuitry allows for 10 years of data retention

- Miniature and transportable

- Durable and rugged

- Impervious to handling

- Four million bits/second data rate

- Single-byte or multiple-byte data transfer capability

- No restrictions on the number of write cycles

- Applications include computer identification, system access control, secure personnel areas, calibration, automatic system setup, and traveling work record.

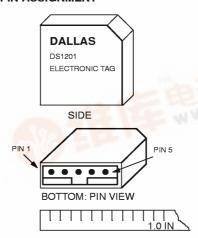

#### **PIN ASSIGNMENT**

See Mech. Drawings

## PIN DESCRIPTION

Pin 1 Vcc +5 Volts

Pin 2 RST RESET

Pin 3 DQ Data Input/Output

Pin 4 CLK Clock

Pin 5 GND Ground

## DESCRIPTION

The DS1201 Electronic Tag is a miniature nonvolatile, read/write memory system which can randomly access individual 8-bit strings (bytes) or sequentially access the entire 1024-bit contents (burst). Interface cost to a microprocessor is minimized by on-chip circuitry which permits data transfers with only three signals: CLOCK,

RESET, and DATA INPUT/OUTPUT. Low pin count and a guided entry for a mating receptacle overcome mechanical problems normally encountered when a conventional integrated circuit package is inserted by the end user.

030598 1/7

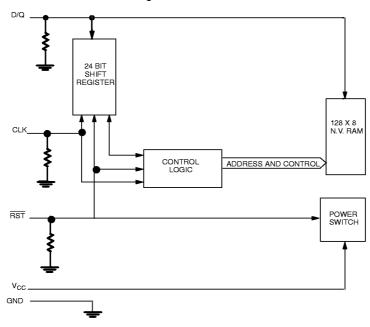

#### **ELECTRONIC TAG BLOCK DIAGRAM** Figure 1

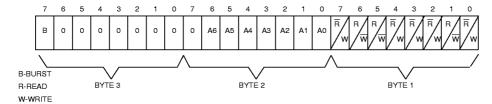

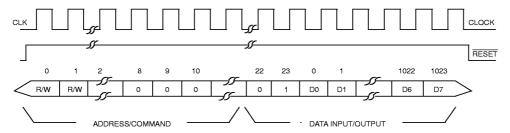

## ADDRESS/COMMAND Figure 2

#### **OPERATION**

The block diagram (Figure 1) of the Electronic Tag illustrates the main elements of the device: shift register, control logic, nonvolatile RAM, and power switch. To initiate a memory cycle RESET is taken high and 24 bits are loaded into the shift register, providing both address and command information. Each bit is input serially on the rising edge of the CLOCK input. Seven address bits specify one of the 128 RAM locations. The remaining command bits specify read/write and byte/burst mode. After the first 24 CLOCKs which load the shift register, additional CLOCKs will output data for a read or input

data for a write. The number of CLOCK pulses equals 24 plus 8 for byte mode or 24 plus 1024 for burst mode.

The tag can be used as a four-pin or five-pin device, depending on the application. For hardwired applications, active power is supplied by the Vcc pin. Alternatively, for user-insertable applications, power can be supplied by the  $\overline{\mbox{RESET}}$  pin.

#### ADDRESS/COMMAND

Each memory transfer consists of a three-byte input called the address/command. The address/command is shown in Figure 2. As defined, the first byte of the address/command specifies whether the memory will be written into or read. If any one of the bits of the first byte of the address/command fails to meet the exact pattern of read or write, the cycle is aborted and all future inputs to the tag are ignored until RESET is brought low and then high again to begin a new cycle. The 8-bit pattern for read is 01100010. The pattern for write is 10011101. The second byte of the address/command describes address inputs A0 in bit 0 through A6 in bit 6. Bit 7 of the second byte of the address/command word must be set to logic 0. This bit is reserved for future higher density versions of the tag. If bit 7 does not equal logic 0, the cycle is aborted and all future inputs to the tag are ignored until RESET is brought low and then high again to begin a new cycle. The third byte of the address/command is also set aside for future expansion. Bits 0 through 6 must be set to logic 0 or the cycle is aborted and all future inputs are ignored until RESET is brought low and then high again to begin a new cycle. Bit 7 of byte 3 of the address/command is used along with address bits A0 through A6 to define burst mode. When A0 through A6 equals logic 0 and bit 7 of byte 3 of the address command equals logic 1, the tag will enter the burst mode after the address/command sequence is complete.

#### **BURST MODE**

Burst mode is specified for the Electronic Tag when all address bits (A0-A6) of the address/command are set to logic 0 and bit 7 of byte 3 to logic 1. The burst mode causes 128 consecutive bytes to be read or written. Burst mode terminates when the RESET input is driven low.

#### **RESET AND CLOCK CONTROL**

All data transfers are initiated by driving the RESET input high. The RESET input serves three functions. First, RESET turns on the control logic which allows access to the shift register for the address/command sequence. Second, the RESET signal provides a power source for the cycle to follow. To meet this requirement, a drive

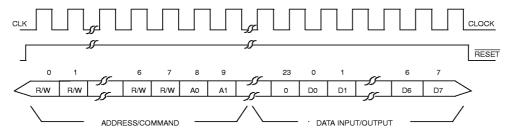

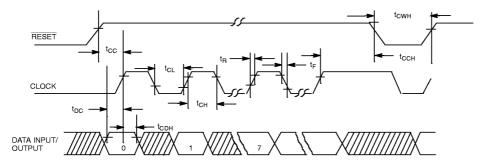

source for RESET of 2 mA @ 3.8 volts is required. However if the Vcc pin is connected to a 5-volt source within nominal limits, then the RESET pin is not used as a source of power and input levels revert to normal VIH and  $V_{II}$  inputs with a drive current requirement of 500 μA. Finally, the RESET signal provides a method of terminating either single byte or multiple byte data transfers. A CLOCK cycle is a sequence of falling edge followed by a rising edge. For data inputs, the data must be valid during the rising edge of the CLOCK cycle. Address/command bits and data bits are input on the rising edge of the CLOCK and data bits are output on the falling edge of the CLOCK. All data transfer terminates if the RESET input is low and D/Q pin goes to a high impedance state. When data transfer to the tag is terminated using RESET, the transition of RESET must occur while the clock is at high level to avoid disturbing the last bit of data. Data transfer is illustrated in Figure 3.

#### **DATA INPUT**

Following the 24 CLOCK cycles that input an address/command, a data byte is input on the rising edge of the next eight CLOCK cycles, assuming that the read/write and write/read bits are properly set (for data input byte 1, bit 0 = 1; bit 1 = 0; bit 2 = 1; bit 3 = 1; bit 4 = 1; bit 5 = 0; bit 6 = 0; bit 7 = 1).

#### **DATA OUTPUT**

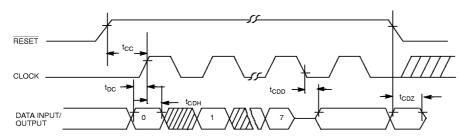

Following the 24 CLOCK cycles that input the read mode, a data byte is output on the falling edge of the next 8 CLOCK cycles (for data output byte 1, bit 0 = 0; bit 1 = 1; bit 2 = 0; bit 3 = 0; bit 4 = 0; bit 5 = 1; bit 6 = 1; bit 7 = 0).

#### **TAG CONNECTIONS**

The tag is designed to be plugged into a standard 5-pin, 0.1-inch center SIP receptacle. A key is provided to prevent the tag from being plugged in backwards and to aid in alignment of the receptacle. For portable applications, contact to the tag pins can be determined to ensure connection integrity before data transfer begins. CLOCK, RESET, and DATA INPUT/OUTPUT all have internal 40K ohm pulldown resistors to ground which can be sensed by a reading device.

## **DATA TRANSFER** Figure 3

## SINGLE BYTE TRANSFER

## **BURST MODE TRANSFER**

#### NOTES:

- 1. Data input sampled on rising edge of clock cycle.

- 2. Data output changes on falling edge of clock.

## **READ/WRITE DATA TRANSFER** Figure 4

## **WRITE DATA TRANSFER**

#### **READ DATA TRANSFER**

#### NOTES:

- 1. All voltages and resistances are referenced to ground.

- Input levels apply to CLK, D/Q, and RST while V<sub>CC</sub> is within nominal limits. When V<sub>CC</sub> is not connected to the tag, then RST input reverts to V<sub>IHE</sub>.

- 3. Measured at  $V_{IH} = 2.0$  or  $V_{IL} = 0.8V$  and 10 ns maximum rise and fall time.

- 4. Measured at  $V_{OH} = 2.4$  volts and  $V_{OL} = 0.4$  volts.

- 5. For CLK, D/Q,  $\overline{RST}$  and  $V_{CC}$  at 5 volts.

- 6. Load capacitance = 50 pF.

- 7. Applies to  $\overline{RST}$  when  $V_{CC} < 3.8$  volts.

- 8. Measured with outputs open.

- 9. Measured at  $V_{IH}$  of  $\overline{RST}$  greater than or equal to 3.8V when  $\overline{RST}$  supplies power.

- 10. Logic 1 maximum is  $V_{CC}$  + 0.3V if the  $V_{CC}$  pin supplies power and  $\overline{RST}$  +0.3V if the  $\overline{RST}$  pin supplies power.

- 11.  $\overline{\text{RST}}$  logic 1 maximum is  $V_{\text{CC}}$  + 0.3V if the  $V_{\text{CC}}$  pin supplies power and 5.5V maximum if  $\overline{\text{RST}}$  supplies power.

- 12. Each DS1201 is marked with a 4-digit date code AABB. AA designates the year of manufacture. BB designates the week of manufacture. The expected t<sub>DB</sub> is defined as starting at the date of manufacture.

- 13. Average AC  $\overline{\text{RST}}$  current can be determined using the following formula:

- $I_{TOTAL} = 2 + I_{LOAD DC} + (4 \times 10^{-3})(CL + 140)f$

- $I_{\mbox{\scriptsize TOTAL}}$  and  $I_{\mbox{\scriptsize LOAD}}$  are in mA; CL is in pF; f is in MHz.

- Applying the above formula, a load capacitance of 50 pF running at a frequency of 4.0 MHz gives an I<sub>TOTAL</sub> current of 5 mA.

- 14. When  $\overline{\text{RST}}$  is supplying power  $t_{\text{CWH}}$  must be increased to 100 ms.

#### **ABSOLUTE MAXIMUM RATINGS\***

Voltage on Any Pin Relative to Ground Operating Temperature Storage Temperature -1.0 to +7.0V 0°C to 70°C -40°C to +70°C

## **RECOMMENDED DC OPERATING CONDITIONS**

(0°C to 70°C)

| PARAMETER     | SYMBOL           | MIN  | TYP | MAX | UNITS | NOTES  |

|---------------|------------------|------|-----|-----|-------|--------|

| Logic 1       | V <sub>IH</sub>  | 2.0  |     |     | ٧     | 1,2,10 |

| Logic 0       | V <sub>IL</sub>  | -0.3 |     | 0.8 | ٧     | 1      |

| RESET Logic 1 | V <sub>IHE</sub> | 3.8  |     |     | ٧     | 1,7,11 |

| Supply        | V <sub>CC</sub>  | 4.5  | 5.0 | 5.5 | V     | 1      |

#### DC ELECTRICAL CHARACTERISTICS

$(0^{\circ}\text{C to }70^{\circ}\text{C}; V_{CC} = 5\text{V} \pm 10\%)$

|                       |                  |     |     | (5 5 15 75 5, 100 51 2 15 75 |        |        |  |

|-----------------------|------------------|-----|-----|------------------------------|--------|--------|--|

| PARAMETER             | SYMBOL           | MIN | TYP | MAX                          | UNITS  | NOTES  |  |

| Input Leakage         | ΙL               |     |     | +500                         | μΑ     | 5      |  |

| Output Leakage        | l <sub>LO</sub>  |     |     | +500                         | μΑ     | 5      |  |

| Output Current @ 2.4V | Іон              | -1  |     |                              | mA     |        |  |

| Output Current @ 0.4V | l <sub>OL</sub>  |     |     | +2                           | mA     |        |  |

| RST Input Resistance  | Z <sub>RST</sub> | 10  |     | 40                           | K ohms | 1      |  |

| D/Q Input Resistance  | $Z_{DQ}$         | 10  |     | 40                           | K ohms | 1      |  |

| CLK Input Resistance  | Z <sub>CLK</sub> | 10  |     | 40                           | K ohms | 1      |  |

| Active Current        | I <sub>CC1</sub> |     |     | 6                            | mA     | 8      |  |

| Standby Current       | I <sub>CC2</sub> |     |     | 2.5                          | mA     | 8      |  |

| RST Current           | I <sub>RST</sub> |     |     |                              | mA     | 7,8,13 |  |

**CAPACITANCE**  $(t_A = 25^{\circ}C)$

| PARAMETER          | SYMBOL           | MIN | TYP | MAX | UNITS | NOTES |

|--------------------|------------------|-----|-----|-----|-------|-------|

| Input Capacitance  | C <sub>IN</sub>  |     |     | 5   | pF    |       |

| Output Capacitance | C <sub>OUT</sub> |     |     | 7   | pF    |       |

<sup>\*</sup> This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability.

## **AC ELECTRICAL CHARACTERISTICS**

(0°C to 70°C;  $V_{CC}$  = 5V  $\pm$  10%)

| PARAMETER                       | SYMBOL           | MIN | TYP | MAX | UNITS | NOTES   |

|---------------------------------|------------------|-----|-----|-----|-------|---------|

| Data to CLK Setup               | t <sub>DC</sub>  | 35  |     |     | ns    | 3,9     |

| Data to CLK Hold                | t <sub>CDH</sub> | 40  |     |     | ns    | 3,9     |

| Data to CLK Delay               | t <sub>CDD</sub> |     |     | 125 | ns    | 3,4,6,9 |

| CLK Low Time                    | t <sub>CL</sub>  | 125 |     |     | ns    | 3,9     |

| CLK High Time                   | t <sub>CH</sub>  | 125 |     |     | ns    | 3,9     |

| CLK Frequency                   | fCLK             | DC  |     | 4.0 | MHz   | 3,9     |

| CLK Rise & Fall                 | $t_{R},t_{F}$    |     |     | 500 | ns    | 9       |

| RST to CLK Setup                | t <sub>CC</sub>  | 1   |     |     | με    | 3,9     |

| CLK to RST Hold                 | tссн             | 40  |     |     | ns    | 3,9     |

| RST Inactive Time               | <sup>†</sup> CWH | 125 |     |     | ns    | 3,9,14  |

| RST to I/O High Z               | t <sub>CDZ</sub> |     |     | 50  | ns    | 3,9     |

| Expected Data<br>Retention Time | t <sub>DR</sub>  | 10  |     |     | Years | 12      |