## 捷多邦,专业PCB打样工厂,24小时加急出货

May 2007

DS15BR400/DS15BR401 4-Channel LVDS Buffer/Repeater with Pre-Emphasis

## DS15BR400/DS15BR401 4-Channel LVDS Buffer/Repeater with Pre-Emphasis

## **General Description**

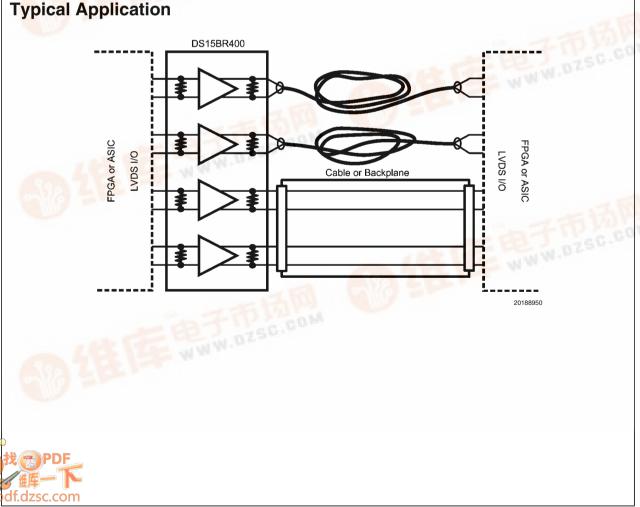

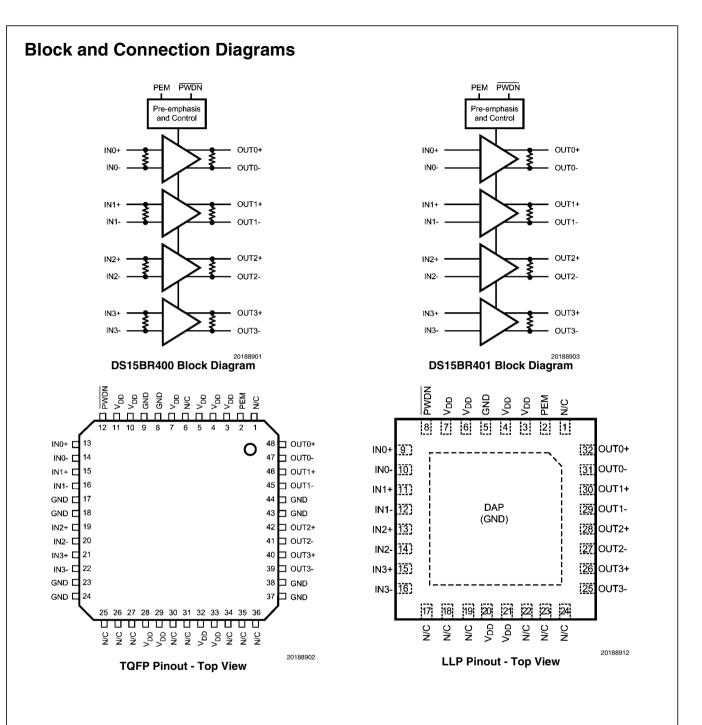

The DS15BR400/DS15BR401 are four channel LVDS buffer/ repeaters capable of datarates of up to 2 Gbps. High speed data paths and flow-through pinout minimize internal device jitter and simplify board layout, while pre-emphasis overcomes ISI jitter effects from Iossy backplanes and cables. The differential inputs interface to LVDS, and Bus LVDS signals such as those on National's 10-, 16-, and 18- bit Bus LVDS SerDes, as well as CML and LVPECL. The differential inputs and outputs of the DS15BR400 are internally terminated with  $100\Omega$  resistors to improve performance and minimize board space. The DS15BR401 does not have input termination resistors. The repeater function is especially useful for boosting signals for longer distance transmission over lossy cables and backplanes.

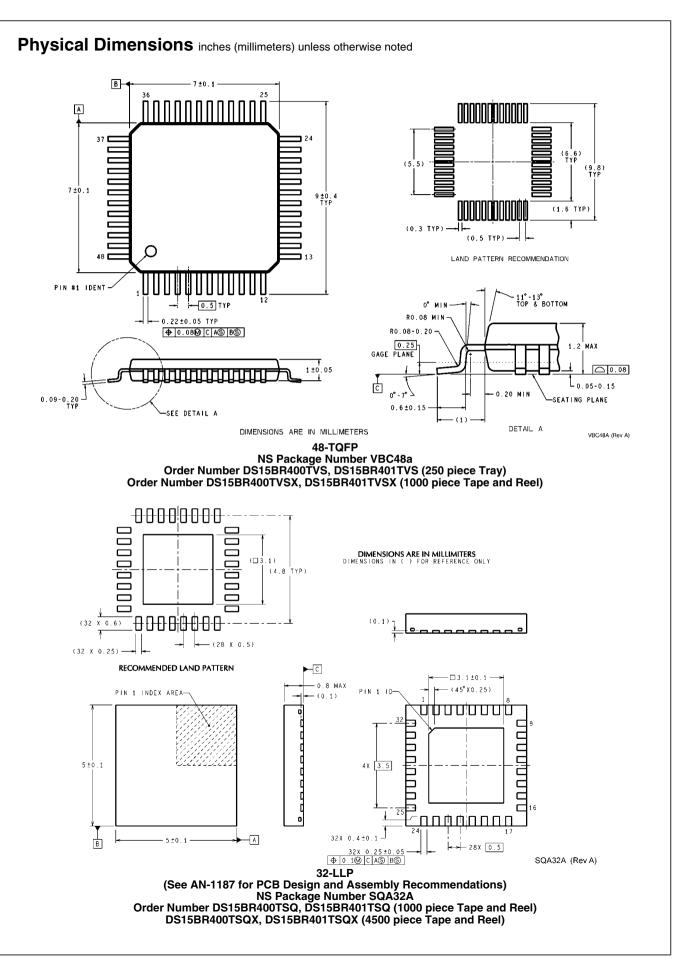

The DS15BR400/DS15BR401 are powered from a single 3.3V supply and consume 578 mW (typ). They operate over the full -40°C to +85°C industrial temperature range and are available in space saving LLP-32 and TQFP-48 packages.

## **Features**

- DC to 2 Gbps low jitter, high noise immunity, low power operation

- 6 dB of pre-emphasis drives lossy backplanes and cables

- LVDS/CML/LVPECL compatible input, LVDS output

- On-chip 100 Ω output termination, optional 100 Ω input termination

- 15 kV ESD protection on LVDS inputs and outputs

- Single 3.3V supply

- Industrial -40 to +85°C temperature range

- Space saving LLP-32 or TQFP-48 packages

- Evaluation Kit Available

## **Applications**

- Cable extention applications

- Signal repeating and buffering

- Digital routers

#### © 2007 National Semiconductor Corporation 201889

www.national.com

| Pin<br>Name     | TQFP Pin<br>Number                         | LLP Pin<br>Number             | I/O, Type | Description                                                                                                                                                                                                                                                                                                                                             |

|-----------------|--------------------------------------------|-------------------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DIFFERE         | ENTIAL INPUTS                              |                               |           |                                                                                                                                                                                                                                                                                                                                                         |

| IN0+            | 13                                         | 9                             | I, LVDS   | Channel 0 inverting and non-inverting differential inputs.                                                                                                                                                                                                                                                                                              |

| IN0-            | 14                                         | 10                            |           |                                                                                                                                                                                                                                                                                                                                                         |

| IN1+            | 15                                         | 11                            | I, LVDS   | Channel 1 inverting and non-inverting differential inputs.                                                                                                                                                                                                                                                                                              |

| IN1–            | 16                                         | 12                            |           |                                                                                                                                                                                                                                                                                                                                                         |

| IN2+            | 19                                         | 13                            | I, LVDS   | Channel 2 inverting and non-inverting differential inputs.                                                                                                                                                                                                                                                                                              |

| IN2-            | 20                                         | 14                            |           |                                                                                                                                                                                                                                                                                                                                                         |

| IN3+            | 21                                         | 15                            | I, LVDS   | Channel 3 inverting and non-inverting differential inputs.                                                                                                                                                                                                                                                                                              |

| IN3–            | 22                                         | 16                            |           |                                                                                                                                                                                                                                                                                                                                                         |

| DIFFERE         | ENTIAL OUTPUTS                             | 6                             |           |                                                                                                                                                                                                                                                                                                                                                         |

| OUT0+           | 48                                         | 32                            | O, LVDS   | Channel 0 inverting and non-inverting differential outputs. (Note 2)                                                                                                                                                                                                                                                                                    |

| OUT0-           | 47                                         | 31                            |           |                                                                                                                                                                                                                                                                                                                                                         |

| OUT1+           | 46                                         | 30                            | O, LVDS   | Channel 1 inverting and non-inverting differential outputs. (Note 2)                                                                                                                                                                                                                                                                                    |

| OUT1-           | 45                                         | 29                            |           |                                                                                                                                                                                                                                                                                                                                                         |

| OUT2+           | 42                                         | 28                            | O, LVDS   | Channel 2 inverting and non-inverting differential outputs. (Note 2)                                                                                                                                                                                                                                                                                    |

| OUT2-           | 41                                         | 27                            |           |                                                                                                                                                                                                                                                                                                                                                         |

| OUT3+           | 40                                         | 26                            | O, LVDS   | Channel 3 inverting and non-inverting differential outputs. (Note 2)                                                                                                                                                                                                                                                                                    |

| OUT3-           | 39                                         | 25                            |           |                                                                                                                                                                                                                                                                                                                                                         |

| DIGITAL         | CONTROL INTE                               | RFACE                         |           |                                                                                                                                                                                                                                                                                                                                                         |

| PWDN            | 12                                         | 8                             | I, LVTTL  | A logic low at PWDN activates the hardware power down mode (all channels).                                                                                                                                                                                                                                                                              |

| PEM             | 2                                          | 2                             | I, LVTTL  | Pre-emphasis Control Input (affects all Channels)                                                                                                                                                                                                                                                                                                       |

| POWER           |                                            |                               |           |                                                                                                                                                                                                                                                                                                                                                         |

| V <sub>DD</sub> | 3, 4, 5, 7, 10, 11,<br>28, 29, 32, 33      | 3, 4, 6, 7, 20,<br>21         | I, Power  | V <sub>DD</sub> = 3.3V, ±10%                                                                                                                                                                                                                                                                                                                            |

| GND             | 8, 9, 17, 18, 23,<br>24, 37, 38, 43,<br>44 | 5 (Note 1)                    | I, Ground | Ground reference for LVDS and CMOS circuitry. For the LLP package, the DAP is used as the primary GND connection to the device in addition to the pin numbers listed. The DAP is the exposed metal contact at the bottom of the LLP-32 package. It should be connected to the ground plane with at least 4 vias for optimal AC and thermal performance. |

| N/C             | 1,6, 25, 26, 27,<br>30, 31, 34, 35,<br>36  | 1, 17,<br>18,19,22, 23,<br>24 |           | No Connect                                                                                                                                                                                                                                                                                                                                              |

Note 1: Note that for the LLP package the GND is connected thru the DAP on the back side of the LLP package in addition to the actual pin numbers listed. Note 2: The LVDS outputs do not support a multidrop (BLVDS) environment. The LVDS output characteristics of the DS15BR400 and DS15BR401 are optimized for point-to-point backplane and cable applications.

## Absolute Maximum Ratings (Note 3)

|                                        | •                                |

|----------------------------------------|----------------------------------|

| Supply Voltage (V <sub>DD</sub> )      | -0.3V to +4.0V                   |

| CMOS Input Voltage                     | –0.3V to (V <sub>DD</sub> +0.3V) |

| LVDS Receiver Input Voltage            | –0.3V to (V <sub>DD</sub> +0.3V) |

| LVDS Driver Output Voltage             | –0.3V to (V <sub>DD</sub> +0.3V) |

| LVDS Output Short Circuit Current      | +40 mA                           |

| Junction Temperature                   | +150°C                           |

| Storage Temperature                    | –65°C to +150°C                  |

| Lead Temperature (Solder, 4sec)        | 260°C                            |

| Max Pkg Power Capacity @ 25°C          |                                  |

| TQFP                                   | 1.64W                            |

| LLP                                    | 4.16W                            |

| Thermal Resistance (θ <sub>.ιΑ</sub> ) |                                  |

| TQFP                                   | 76°C/W                           |

| LLP                                    | 30°C/W                           |

| Package Derating above +25°C           |                                  |

| TQFP                                   | 13.2mW/°C                        |

| LLP                                    | 33.3mW/°C                        |

| ESD Last Passing Voltage               |                                  |

| HBM, 1.5kΩ, 100pF                      | 8 kV                             |

|                                        |                                  |

| LVDS pins to GND only | 15 kV |

|-----------------------|-------|

| EIAJ, 0Ω, 200pF       | 250V  |

| Charged Device Model  | 1000V |

# Recommended Operating Conditions

| Supply Voltage (V <sub>CC</sub> )        | 3.0V to 3.6V   |

|------------------------------------------|----------------|

| Input Voltage (V <sub>I</sub> ) (Note 4) | 0V to $V_{CC}$ |

| Output Voltage (V <sub>O</sub> )         | 0V to $V_{CC}$ |

| Operating Temperature (T <sub>A</sub> )  |                |

| Industrial                               | –40°C to +85°C |

**Note 3:** Absolute maximum ratings are those values beyond which damage to the device may occur. The databook specifications should be met, without exception, to ensure that the system design is reliable over its power supply, temperature, and output/input loading variables. National does not recommend operation of products outside of recommended operation conditions.

Note 4: V<sub>ID</sub> max < 2.4V

## **Electrical Characteristics**

Over recommended operating supply and temperature ranges unless other specified.

| Symbol           | Parameter                                     | Conditions                                                 | Min  | Typ<br>(Note<br>5) | Max      | Units |

|------------------|-----------------------------------------------|------------------------------------------------------------|------|--------------------|----------|-------|

| LVCMOS           | S DC SPECIFICATIONS (PWD                      | N, PEM)                                                    |      | •                  |          |       |

| V <sub>IH</sub>  | High Level Input Voltage                      |                                                            | 2.0  |                    | $V_{DD}$ | V     |

| V <sub>IL</sub>  | Low Level Input Voltage                       |                                                            | GND  |                    | 0.8      | V     |

| I <sub>IH</sub>  | High Level Input Current                      | $V_{IN} = V_{DD} = 3.6V (\overline{PWDN} \text{ pin})$     | -10  |                    | +10      | μA    |

| I <sub>IHR</sub> | High Level Input Current                      | $V_{IN} = V_{DD} = 3.6V (PEM pin)$                         | 40   |                    | 200      | μA    |

| I                | Low Level Input Current                       | $V_{IN} = V_{SS}, V_{DD} = 3.6V$                           | -10  |                    | +10      | μA    |

| C <sub>IN1</sub> | LVCMOS Input Capacitance                      | Any Digital Input Pin to V <sub>SS</sub>                   |      | 5.5                |          | pF    |

| V <sub>CL</sub>  | Input Clamp Voltage                           | $I_{CL} = -18 \text{ mA}, V_{DD} = 0 \text{ V}$            | -1.5 | -0.8               |          | V     |

| LVDS IN          | PUT DC SPECIFICATIONS (II                     | Nn±)                                                       |      | •                  |          |       |

| V <sub>TH</sub>  | Differential Input High<br>Threshold (Note 6) | V <sub>CM</sub> = 0.8V to 3.55V,<br>V <sub>DD</sub> = 3.6V |      | 0                  | 100      | mV    |

| V <sub>TL</sub>  | Differential Input Low<br>Threshold (Note 6)  | $V_{CM} = 0.8V$ to 3.55V,<br>$V_{DD} = 3.6V$               | -100 | 0                  |          | mV    |

| V <sub>ID</sub>  | Differential Input Voltage                    | $V_{CM} = 0.8V$ to 3.55V, $V_{DD} = 3.6V$                  | 100  |                    | 2400     | mV    |

| V <sub>CMR</sub> | Common Mode Voltage<br>Range                  | V <sub>ID</sub> = 150 mV, V <sub>DD</sub> = 3.6V           | 0.05 |                    | 3.55     | v     |

| C <sub>IN2</sub> | LVDS Input Capacitance                        | IN+ or IN– to V <sub>SS</sub>                              |      | 3.0                |          | pF    |

| I <sub>IN</sub>  | Input Current                                 | V <sub>IN</sub> = 3.6V, V <sub>DD</sub> = 3.6V             | -10  |                    | +10      | μA    |

|                  |                                               | $V_{IN} = 0V, V_{DD} = 3.6V$                               | -10  |                    | +10      | μA    |

| Symbol            | Parameter                                                 | Conditions                                                                                                               | Min  | Typ<br>(Note<br>5) | Мах   | Units |

|-------------------|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|------|--------------------|-------|-------|

| LVDS O            | UTPUT DC SPECIFICATIONS                                   | (OUTn±)                                                                                                                  |      |                    |       |       |

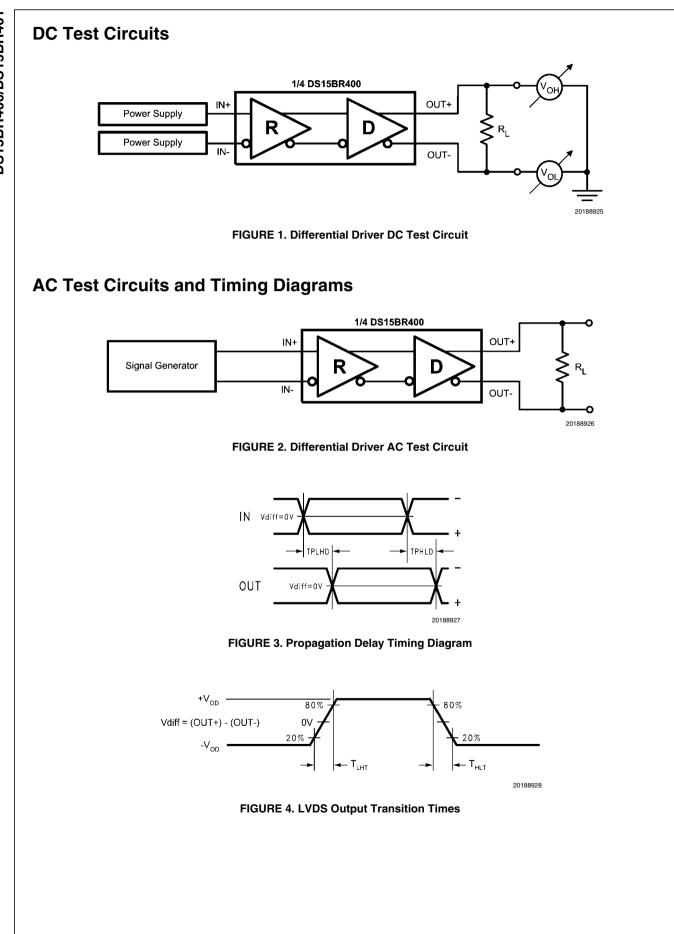

| V <sub>OD</sub>   | Differential Output Voltage,<br>0% Pre-emphasis (Note 6)  | $R_L = 100\Omega$ external resistor between OUT+ and OUT-<br>Figure 1                                                    | 250  | 360                | 500   | mV    |

| ΔV <sub>OD</sub>  | Change in V <sub>OD</sub> between<br>Complementary States |                                                                                                                          | -35  |                    | 35    | mV    |

| V <sub>os</sub>   | Offset Voltage (Note 7)                                   |                                                                                                                          | 1.05 | 1.18               | 1.475 | V     |

| ΔV <sub>OS</sub>  | Change in V <sub>OS</sub> between<br>Complementary States |                                                                                                                          | -35  |                    | 35    | mV    |

| C <sub>OUT</sub>  | LVDS Output Capacitance                                   | OUT+ or OUT- to V <sub>SS</sub>                                                                                          |      | 2.5                |       | pF    |

| I <sub>OS</sub>   | Output Short Circuit Current                              | OUT+ or OUT– Short to GND                                                                                                |      | -21                | -40   | mA    |

|                   |                                                           | OUT+ or OUT- Short to VDD                                                                                                |      | 6                  | 40    | mA    |

| SUPPLY            | CURRENT (Static)                                          |                                                                                                                          |      | •                  |       |       |

| I <sub>CC</sub>   | Supply Current                                            | All inputs and outputs enabled and active, terminated with differential load of $100\Omega$ between OUT+ and OUT PEM = L |      | 175                | 215   | mA    |

| l <sub>ccz</sub>  | Supply Current - Power Down<br>Mode                       | PWDN = L, PEM = L                                                                                                        |      | 20                 | 200   | μA    |

| SWITCH            | ING CHARACTERISTICS-LV                                    | /DS OUTPUTS                                                                                                              |      |                    |       | -     |

| t <sub>LHT</sub>  | Differential Low to High<br>Transition Time (Note 12)     | Use an alternating 1 and 0 pattern at 200 Mbps, measure between 20% and 80% of V <sub>OD</sub> .                         |      | 170                | 250   | ps    |

| t <sub>HLT</sub>  | Differential High to Low<br>Transition Time (Note 12)     | Figures 2, 4                                                                                                             |      | 170                | 250   | ps    |

| t <sub>PLHD</sub> | Differential Low to High<br>Propagation Delay             | Use an alternating 1 and 0 pattern at 200 Mbps, measure at 50% $V_{OD}$ between input to output.                         |      | 1.0                | 2.0   | ns    |

| t <sub>PHLD</sub> | Differential High to Low<br>Propagation Delay             | Figures 2, 3                                                                                                             |      | 1.0                | 2.0   | ns    |

| t <sub>SKD1</sub> | Pulse Skew (Note 12)                                      | It <sub>PLHD</sub> -t <sub>PHLD</sub> I                                                                                  |      | 10                 | 60    | ps    |

| t <sub>skcc</sub> | Output Channel to Channel<br>Skew (Note 12)               | Difference in propagation delay (t <sub>PLHD</sub> or t <sub>PHLD</sub> ) among all output channels.                     |      | 25                 | 75    | ps    |

| t <sub>SKP</sub>  | Part to Part Skew (Note 12)                               | Common edge, parts at same temp and $V_{CC}$                                                                             |      |                    | 550   | ps    |

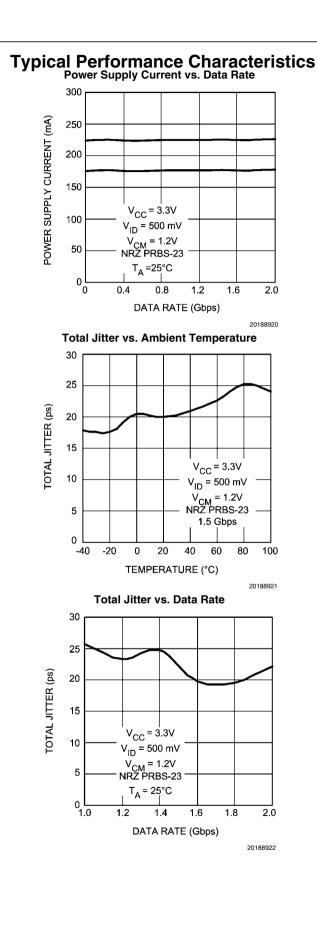

| t <sub>JIT</sub>  | Jitter (0% Pre-emphasis)                                  | RJ - Alternating 1 and 0 at 750 MHz (Note 9)                                                                             |      | 0.5                | 1.5   | ps    |

|                   | (Note 8)                                                  | DJ - K28.5 Pattern, 1.5 Gbps (Note 10)                                                                                   |      | 14                 | 30    | ps    |

|                   |                                                           | TJ - PRBS 223-1 Pattern, 1.5 Gbps (Note 11)                                                                              |      | 14                 | 31    | ps    |

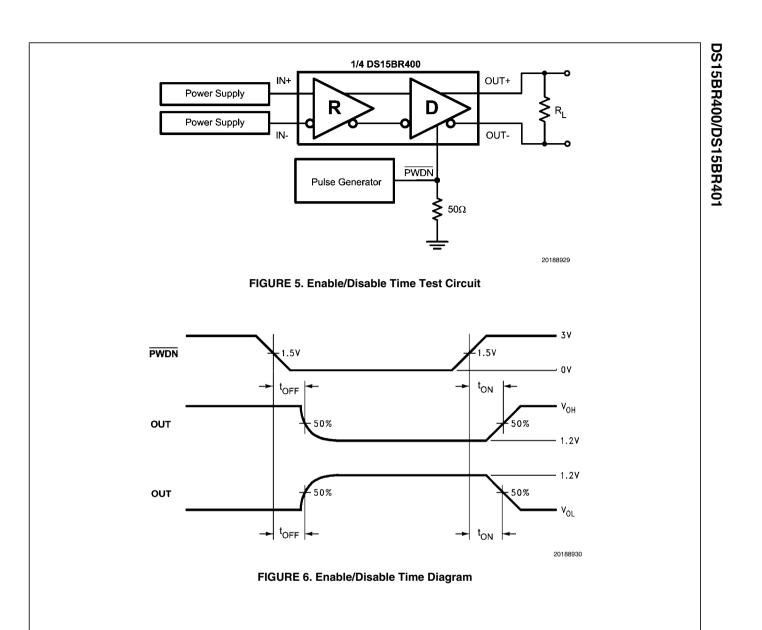

| t <sub>on</sub>   | LVDS Output Enable Time                                   | Time from PWDN to OUT± change from TRI-STATE to active.<br>Figures 5, 6                                                  |      |                    | 20    | μs    |

| t <sub>OFF</sub>  | LVDS Output Disable Time                                  | Time from PWDN to OUT± change from active to TRI-<br>STATE.<br>Figures 5, 6                                              |      |                    | 12    | ns    |

Note 5: Typical parameters are measured at  $V_{DD}$  = 3.3V,  $T_A$  = 25°C. They are for reference purposes, and are not production-tested.

Note 6: Differential output voltage V<sub>OD</sub> is defined as ABS(OUT+-OUT-). Differential input voltage V<sub>ID</sub> is defined as ABS(IN+-IN-).

Note 7: Output offset voltage V<sub>OS</sub> is defined as the average of the LVDS single-ended output voltages at logic high and logic low states.

Note 8: Jitter is not production tested, but guaranteed through characterization on a sample basis.

**Note 9:** Random Jitter, or RJ, is measured RMS with a histogram including 1500 histogram window hits. Stimulus and fixture Jitter has been subtracted. The input voltage =  $V_{ID}$  = 500 mV, input common mode voltage =  $V_{ICM}$  = 1.2V, 50% duty cycle at 750 MHz,  $t_r = t_f$  = 50 ps (20% to 80%).

Note 10: Deterministic Jitter, or DJ, is a peak to peak value. Stimulus and fixture jitter has been subtracted. The input voltage =  $V_{ID}$  = 500 mV, input common mode voltage =  $V_{ICM}$  = 1.2V, K28.5 pattern at 1.5 Gbps,  $t_r = t_f = 50$  ps (20% to 80%). The K28.5 pattern is repeating bit streams of (0011111010 1100000101). Note 11: Total Jitter, or TJ, is measured peak to peak with a histogram including 3500 window hits. Stimulus and fixture Jitter has been subtracted. The input voltage =  $V_{ID}$  = 500 mV, input common mode voltage =  $V_{ICM}$  = 1.2V, 2<sup>23</sup>-1 PRBS pattern at 1.5 Gbps,  $t_r$  =  $t_f$  = 50 ps (20% to 80%).

Note 12: Not production tested. Guaranteed by a statistical analysis on a sample basis at the time of characterization.

DS15BR400/DS15BR401

6

DS15BR400/DS15BR401

## **Application Information**

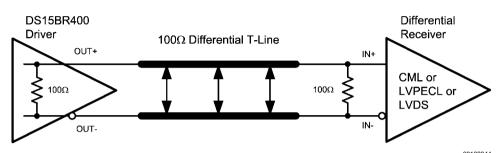

#### INTERNAL TERMINATIONS

The DS15BR400 has integrated termination resistors on both the input and outputs. The inputs have a 100 $\Omega$  resistor across the differential pair, placing the receiver termination as close as possible to the input stage of the device. The LVDS outputs also contain an integrated 100 $\Omega$  ohm termination resistor, this resistor is used to minimize the output return loss and does not take the place of the 100 ohm termination at the inputs to the receiving device. The integrated terminations improve signal integrity and decrease the external component count resulting in space savings. The DS15BR401 has 100 $\Omega$  output terminations only.

#### **OUTPUT CHARACTERISTICS**

The output characteristics of the DS15BRB400/DS15BR401 have been optimized for point-to-point backplane and cable applications, and are not intended for multipoint or multidrop signaling.

#### **POWERDOWN MODE**

The PWDN input activates a hardware powerdown mode. When the powerdown mode is active (PWDN=L), all input and output buffers and internal bias circuitry are powered off. When exiting powerdown mode, there is a delay associated with turning on bandgap references and input/output buffer circuits as indicated in the LVDS Output Switching Characteristics

#### **PRE-EMPHASIS**

Pre-emphasis dramatically reduces ISI jitter from long or lossy transmission media. One pin is used to select the preemphasis level for all outputs, off or on. The pre-emphasis boost is approximately 6 dB at 750 MHz.

| Pre-emphasis Co | ntrol Selection Table |

|-----------------|-----------------------|

|-----------------|-----------------------|

| PEM | Pre-Emphasis |

|-----|--------------|

| 0   | Off          |

| 1   | On           |

#### INPUT FAILSAFE BIASING

External pull up and pull down resistors may be used to provide enough of an offset to enable an input failsafe under open-circuit conditions. This configuration ties the positive LVDS input pin to  $V_{DD}$  thru a pull up resistor and the negative LVDS input pin is tied to GND by a pull down resistor. The pull up and pull down resistors should be in the  $5k\Omega$  to  $15k\Omega$  range to minimize loading and waveform distortion to the driver. The common-mode bias point ideally should be set to approximately 1.2V. Please refer to application note AN-1194 "Failsafe Biasing of LVDS Interfaces" for more information.

#### DECOUPLING

Each power or ground lead of the DS15BR400 should be connected to the PCB through a low inductance path. For best results, one or more vias are used to connect a power or ground pin to the nearby plane. Ideally, via placement is immediately adjacent to the pin to avoid adding trace inductance. Placing power plane closer to the top of the board reduces effective via length and its associated inductance.

Bypass capacitors should be placed close to VDD pins. Small physical size capacitors, such as 0402, X7R, surface mount capacitors should be used to minimize body inductance of capacitors. Each bypass capacitor is connected to the power and ground plane through vias tangent to the pads of the capacitor. An X7R surface mount capacitor of size 0402 has about 0.5 nH of body inductance. At frequencies above 30 MHz or so, X7R capacitors behave as low impedance inductors. To extend the operating frequency range to a few hundred MHz, an array of different capacitor values like 100 pF, 1 nF, 0.03  $\mu$ F, and 0.1  $\mu$ F are commonly used in parallel. The most effective bypass capacitor can be built using sandwiched layers of power and ground at a separation of 2–3 mils. With a 2 mil FR4 dielectric, there is approximately 500 pF per square inch of PCB.

The center dap of the LLP package housing the DS15BR400 should be connected to a ground plane through an array of vias. The via array reduces the effective inductance to ground and enhances the thermal performance of the LLP package.

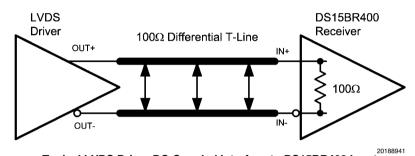

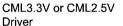

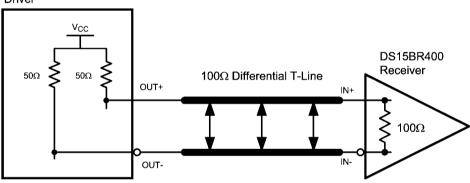

#### INPUT INTERFACING

The DS15BR400 and DS15BR401 accept differential signals and allow simple AC or DC coupling. With a wide common mode range, the DS15BR400 and DS15BR401 can be DC-coupled with all common differential drivers (i.e. LVPECL, LVDS, CML). The following three figures illustrate typical DC-coupled interface to common differential drivers. Note that the DS15BR400 inputs are internally terminated with a 100 $\Omega$  resistor while the DS15BR401 inputs are not, therefore the latter requires external input termination.

Typical LVDS Driver DC-Coupled Interface to DS15BR400 Input

Typical CML Driver DC-Coupled Interface to DS15BR400 Input

Typical LVPECL Driver DC-Coupled Interface to DS15BR400 Input

20188942

#### **OUTPUT INTERFACING**

The DS15BR400 and DS15BR401 output signals that are compliant to the LVDS standard. Their outputs can be DC-coupled to most common differential receivers. The following figure illustrates typical DC-coupled interface to common differential receivers and assumes that the receivers have high impedance inputs. While most differential receivers have a common mode input range that can accomodate LVDS compliant signals, it is recommended to check respective receiver's data sheet prior to implementing the suggested interface implementation.

Typical DS15BR400 Output DC-Coupled Interface to an LVDS, CML or LVPECL Receiver

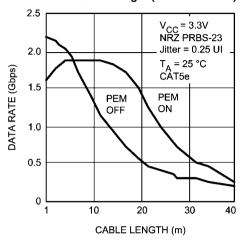

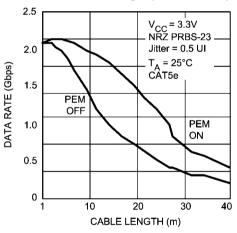

Data Rate vs. Cable Length (0.25 UI Criteria)

20188923

Data presented in this graph was collected using the DS15BR400EVK, a pair of RJ-45 to SMA adapter boards and various length Belden 1700a cables. The maximum data rate was determined based on total jitter (0.25 UI criteria) measured after the cable. The total jitter was a peak to peak value measured with a histogram including 3000 window hits.

20188924

Data presented in this graph was collected using the DS15BR400EVK, a pair of RJ-45 to SMA adapter boards and various length Belden 1700a cables. The maximum data rate was determined based on total jitter (0.5 UI criteria) measured after the cable. The total jitter was a peak to peak value measured with a histogram including 3000 window hits.

www.national.com

DS15BR400/DS15BR401

4-Channel LVDS Buffer/Repeater with Pre-Emphasis

DS15BR400/DS15BR401

THE CONTENTS OF THIS DOCUMENT ARE PROVIDED IN CONNECTION WITH NATIONAL SEMICONDUCTOR CORPORATION ("NATIONAL") PRODUCTS. NATIONAL MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE ACCURACY OR COMPLETENESS OF THE CONTENTS OF THIS PUBLICATION AND RESERVES THE RIGHT TO MAKE CHANGES TO SPECIFICATIONS AND PRODUCT DESCRIPTIONS AT ANY TIME WITHOUT NOTICE. NO LICENSE, WHETHER EXPRESS. IMPLIED, ARISING BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS

TESTING AND OTHER QUALITY CONTROLS ARE USED TO THE EXTENT NATIONAL DEEMS NECESSARY TO SUPPORT NATIONAL'S PRODUCT WARRANTY. EXCEPT WHERE MANDATED BY GOVERNMENT REQUIREMENTS, TESTING OF ALL PARAMETERS OF EACH PRODUCT IS NOT NECESSARILY PERFORMED. NATIONAL ASSUMES NO LIABILITY FOR APPLICATIONS ASSISTANCE OR BUYER PRODUCT DESIGN. BUYERS ARE RESPONSIBLE FOR THEIR PRODUCTS AND APPLICATIONS USING NATIONAL COMPONENTS. PRIOR TO USING OR DISTRIBUTING ANY PRODUCTS THAT INCLUDE NATIONAL COMPONENTS, BUYERS SHOULD PROVIDE ADEQUATE DESIGN, TESTING AND OPERATING SAFEGUARDS.

EXCEPT AS PROVIDED IN NATIONAL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, NATIONAL ASSUMES NO LIABILITY WHATSOEVER. AND NATIONAL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO THE SALE AND/OR USE OF NATIONAL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE CHIEF EXECUTIVE OFFICER AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

National Semiconductor and the National Semiconductor logo are registered trademarks of National Semiconductor Corporation. All other brand or product names may be trademarks or registered trademarks of their respective holders.

Copyright© 2007 National Semiconductor Corporation

For the most current product information visit us at www.national.com

| N |

|---|

|   |

National Semiconductor Americas Customer Support Center Email: new.feedback@nsc.com Tel: 1-800-272-9959

National Semiconductor Europe **Customer Support Center** Fax: +49 (0) 180-530-85-86 Email: europe.support@nsc.com Deutsch Tel: +49 (0) 69 9508 6208 English Tel: +49 (0) 870 24 0 2171 Français Tel: +33 (0) 1 41 91 8790 National Semiconductor Asia Pacific Customer Support Center Email: ap.support@nsc.com

National Semiconductor Japan **Customer Support Center** Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560