### **General Description**

The DS4402 and DS4404 contain two and four I2C\* adjustable current DACs, respectively, that are each capable of sinking or sourcing current. Each output has 31 sink and 31 source settings that are programmed by the I2C interface. External resistors set the full-scale range and step size of each output.

## **Applications**

Power-Supply Adjustment Power-Supply Margining Adjustable Current Sink or Source

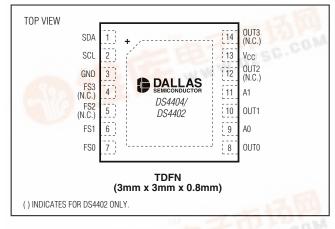

## **Pin Configuration**

#### Features

- ◆ Two (DS4402) or Four (DS4404) Current DACs

- ♦ Full-Scale Range for Each DAC Determined by **External Resistors**

- 31 Settings Each for Sink and Source Modes

- ♦ I<sup>2</sup>C-Compatible Serial Interface

- Two Three-Level Address Pins Allow Nine Devices on Same I<sup>2</sup>C Bus

- ♦ Low Cost

- Small Package (14-Pin TDFN)

- ♦ -40°C to +85°C Temperature Range

- ♦ 1.7V to 5.5V Operation

## **Ordering Information**

| PART                                     | TEMP RANGE     | PIN-PACKAGE         |

|------------------------------------------|----------------|---------------------|

| <b>DS4402</b> N+                         | -40°C to +85°C | 14 TDFN (3mm x 3mm) |

| DS4402N+T&R                              | -40°C to +85°C | 14 TDFN (3mm x 3mm) |

| <b>DS4404</b> N+                         | -40°C to +85°C | 14 TDFN (3mm x 3mm) |

| DS4404N+T&R                              | -40°C to +85°C | 14 TDFN (3mm x 3mm) |

| +Denotes lead-free<br>T&R denotes tape-a |                | N.DZSC.COM          |

<sup>+</sup>Denotes lead-free package.

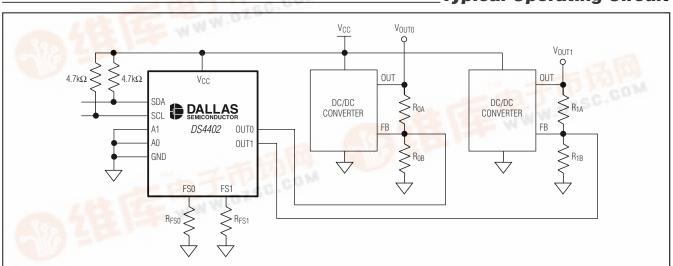

## **Typical Operating Circuit**

\*Purchase of I<sup>2</sup>C components from Maxim Integrated Products, Inc., or one of its sublicensed Associated Companies, conveys a license under the Philips I<sup>2</sup>C Patent Rights to use these components in an I<sup>2</sup>C system, provided that the system conforms to the I<sup>2</sup>C Standard Specification as defined by Philips.

PALLAS /VI /IX I /VI

#### **ABSOLUTE MAXIMUM RATINGS**

Voltage Range on V<sub>CC</sub>, SDA, and SCL

Relative to Ground......-0.5V to +6.0V

Voltage Range on A0, A1, FS0, FS1, FS2, FS3,

OUT0, OUT1, OUT2, and OUT3 Relative to

Ground ......-0.5V to (V<sub>CC</sub> + 0.5V) (Not to exceed 6.0V.)

Operating Temperature Range ....-40°C to +85°C

Storage Temperature Range ....-55°C to +125°C

Soldering Temperature Range ....-55°C to +125°C

Soldering Temperature Range ....-40°C to +85°C

Storage Temperature Range ....-55°C to +125°C

Soldering Temperature Range ....-55°C to +125°C

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### RECOMMENDED OPERATING CONDITIONS

$(T_A = -40^{\circ}C \text{ to } +85^{\circ}C.)$

| PARAMETER                        | SYMBOL | CONDITIONS | MIN                      | TYP | MAX                       | UNITS |

|----------------------------------|--------|------------|--------------------------|-----|---------------------------|-------|

| Supply Voltage                   | Vcc    | (Note 1)   | 2.7                      |     | 5.5                       | V     |

| Input Logic 1 (SDA, SCL, A0, A1) | VIH    |            | 0.7 x<br>V <sub>CC</sub> |     | V <sub>CC</sub> +         | V     |

| Input Logic 0 (SDA, SCL, A0, A1) | VIL    |            | -0.3                     |     | 0.3 x<br>V <sub>C</sub> C | V     |

### DC ELECTRICAL CHARACTERISTICS

$(V_{CC} = +2.7V \text{ to } +5.5V, T_A = -40^{\circ}C \text{ to } +85^{\circ}C.)$

| PARAMETER                  | SYMBOL           |                        | CONDITIONS | MIN | TYP  | MAX | UNITS |

|----------------------------|------------------|------------------------|------------|-----|------|-----|-------|

| Cura al Currant            | 1                | $V_{CC} = 5.5V$        | DS4402     |     |      | 500 |       |

| Supply Current             | Icc              | (Note 2)               | DS4404     |     |      | 500 | μΑ    |

| Input Leakage (SDA, SCL)   | Ι <sub>Ι</sub> L | $V_{CC} = 5.5V$        |            |     |      | 1   | μΑ    |

| Output Leakage (SDA)       | ΙL               |                        |            |     |      | 1   | μΑ    |

| Contract Comment Law (CDA) | 1.               | $V_{OL} = 0.4V$        |            | 3   |      |     | A     |

| Output Current Low (SDA)   | loL              | V <sub>OL</sub> = 0.6V |            | 6   |      |     | mA    |

| Address Input Resistors    | RIN              |                        |            |     | 240  |     | kΩ    |

| Reference Voltage          | VREF             |                        |            |     | 1.23 |     | V     |

### **OUTPUT CURRENT CHARACTERISTICS**

$(V_{CC} = +2.7V \text{ to } +5.5V, T_A = -40^{\circ}C \text{ to } +85^{\circ}C.)$

| PARAMETER                              | SYMBOL               | CONDITIONS                                                          | MIN  | TYP | MAX                   | UNITS  |

|----------------------------------------|----------------------|---------------------------------------------------------------------|------|-----|-----------------------|--------|

| Output Voltage for Sinking Current     | Vout:sink            | (Note 3)                                                            | 0.5  |     | Vcc                   | V      |

| Output Voltage for Sourcing<br>Current | Vout:source          | (Note 3)                                                            | 0    |     | V <sub>CC</sub> - 0.5 | V      |

| Full-Scale Sink Output Current         | IOUT:SINK            | (Note 3)                                                            | 0.5  |     | 2.0                   | mA     |

| Full-Scale Source Output Current       | IOUT:SOURCE          | (Note 3)                                                            | -2.0 |     | -0.5                  | mΑ     |

| Output-Current Full-Scale<br>Accuracy  | I <sub>OUT:</sub> FS | +25°C, V <sub>CC</sub> = 4.0V; using ideal R <sub>FS</sub> resistor |      | 2.5 | 5.0                   | %      |

| Output-Current Temperature Drift       | IOUT:TC              | (Note 4)                                                            |      | 70  |                       | ppm/°C |

### **OUTPUT CURRENT CHARACTERISTICS (continued)**

$(V_{CC} = +2.7V \text{ to } +5.5V, T_A = -40^{\circ}C \text{ to } +85^{\circ}C.)$

| PARAMETER                                      | SYMBOL | CONDITIONS | MIN | TYP  | MAX | UNITS |

|------------------------------------------------|--------|------------|-----|------|-----|-------|

| Output-Current Power-Supply<br>Rejection Ratio |        | DC         |     | 0.33 |     | %/V   |

| Output Leakage Current at Zero Current Setting | IZERO  |            | -1  |      | +1  | μΑ    |

| Output-Current Differential Linearity          | DNL    | (Note 5)   |     |      | 0.5 | LSB   |

| Output-Current Integral Linearity              | INL    | (Note 6)   |     |      | 1   | LSB   |

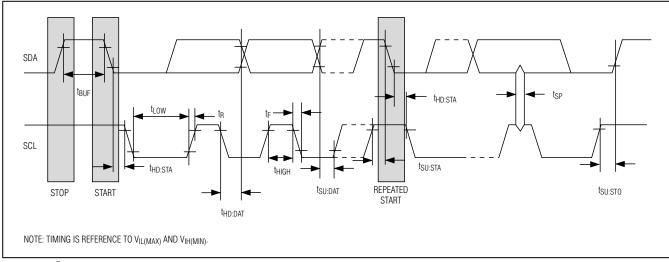

#### I<sup>2</sup>C AC ELECTRICAL CHARACTERISTICS

$(V_{CC} = +2.7V \text{ to } +5.5V, T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C.})$

| PARAMETER                                       | SYMBOL              | CONDITIONS | MIN                       | TYP | MAX | UNITS |

|-------------------------------------------------|---------------------|------------|---------------------------|-----|-----|-------|

| SCL Clock Frequency                             | fscl                | (Note 7)   | 0                         |     | 400 | kHz   |

| Bus Free Time Between STOP and START Conditions | tBUF                |            | 1.3                       |     |     | μs    |

| Hold Time (Repeated) START<br>Condition         | tHD:STA             |            | 0.6                       |     |     | μs    |

| Low Period of SCL                               | tLOW                |            | 1.3                       |     |     | μs    |

| High Period of SCL                              | tHIGH               |            | 0.6                       |     |     | μs    |

| Data Hold Time                                  | t <sub>DH:DAT</sub> |            | 0                         |     | 0.9 | μs    |

| Data Setup Time                                 | tsu:dat             |            | 100                       |     |     | ns    |

| START Setup Time                                | tsu:sta             |            | 0.6                       |     |     | μs    |

| SDA and SCL Rise Time                           | t <sub>R</sub>      | (Note 8)   | 20 +<br>0.1C <sub>B</sub> |     | 300 | ns    |

| SDA and SCL Fall Time                           | tF                  | (Note 8)   | 20 +<br>0.1C <sub>B</sub> |     | 300 | ns    |

| STOP Setup Time                                 | tsu:sto             |            | 0.6                       |     |     | μs    |

| SDA and SCL Capacitive Loading                  | СВ                  | (Note 8)   |                           |     | 400 | рF    |

- Note 1: All voltages with respect to ground. Currents entering the IC are specified positive, and currents exiting the IC are negative.

- Note 2: Supply current specified with all outputs set to zero current setting with all inputs (except A1 and A0, which can be open) driven to well-defined logic levels. SDA and SCL are connected to V<sub>CC</sub>. Excludes current through R<sub>FS</sub> resistors (I<sub>RFS</sub>). Total current including I<sub>RFS</sub> is I<sub>CC</sub> + (2 x I<sub>RFS</sub>).

- Note 3: The output-voltage full-scale current ranges must be satisfied to ensure the device meets its accuracy and linearity specifications.

- Note 4: Temperature drift excludes drift caused by external resistor.

- **Note 5:** Differential linearity is defined as the difference between the expected incremental current increase with respect to position and the actual increase. The expected incremental increase is the full-scale range divided by 31.

- **Note 6:** Integral linearity is defined as the difference between the expected value as a function of the setting and the actual value. The expected value is a straight line between the zero and the full-scale values proportional to the setting.

- Note 7: Timing shown is for fast-mode (400kHz) operation. This device is also backward compatible with I<sup>2</sup>C standard-mode timing.

- Note 8: C<sub>B</sub>—total capacitance of one bus line in pF.

## **Pin Description**

| P      | IN           | NAME   | FUNCTION                                                                                                                                                                                                 |  |  |  |

|--------|--------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| DS4404 | DS4402       | NAME   | FUNCTION                                                                                                                                                                                                 |  |  |  |

| 1      | 1            | SDA    | I <sup>2</sup> C Serial Data. Input/output for I <sup>2</sup> C data.                                                                                                                                    |  |  |  |

| 2      | 2            | SCL    | I <sup>2</sup> C Serial Clock. Input for I <sup>2</sup> C clock.                                                                                                                                         |  |  |  |

| 3      | 3            | GND    | Ground                                                                                                                                                                                                   |  |  |  |

| 4      | _            | FS3    |                                                                                                                                                                                                          |  |  |  |

| 5      | _            | FS2    | Full-Scale Calibration Input. A resistor to ground on these pins determines the full-scale                                                                                                               |  |  |  |

| 6      | 6            | FS1    | current for each output. FS0 controls OUT0, FS1 controls OUT1, etc. (DS4402 has only two inputs: FS0 and FS1.)                                                                                           |  |  |  |

| 7      | 7            | FS0    | two inputs. 1 30 and 1 o 1.)                                                                                                                                                                             |  |  |  |

| 8      | 8            | OUT0   |                                                                                                                                                                                                          |  |  |  |

| 10     | 10           | OUT1   | Current Output. Sinks or sources the current determined by the I <sup>2</sup> C interface and the                                                                                                        |  |  |  |

| 12     | _            | OUT2   | resistance connected to FSx. (DS4402 has only two outputs: OUT0 and OUT1.)                                                                                                                               |  |  |  |

| 14     | _            | OUT3   |                                                                                                                                                                                                          |  |  |  |

| 9, 11  | 9, 11        | A0, A1 | Address Select Inputs. Tri-level inputs (V <sub>CC</sub> , GND, N.C.) determine the I <sup>2</sup> C slave address. See the <i>Detailed Description</i> section for the nine available device addresses. |  |  |  |

| 13     | 13           | Vcc    | Power Supply                                                                                                                                                                                             |  |  |  |

| _      | 4, 5, 12, 14 | N.C.   | No Connection                                                                                                                                                                                            |  |  |  |

| _      | _            | EP     | Exposed Pad. Leave floating or connect to GND.                                                                                                                                                           |  |  |  |

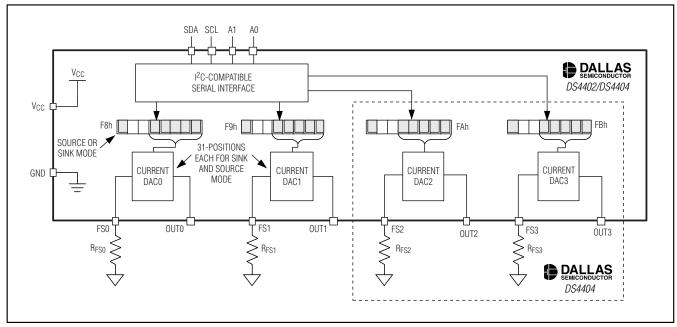

Figure 1. Functional Diagram

## **Detailed Description**

The DS4402/DS4404 contain two/four I<sup>2</sup>C adjustable current sources (Figure 1) that are each capable of sinking and sourcing current. Each output has 31 sink and 31 source settings that are programmed through the I<sup>2</sup>C interface. The full-scale ranges (and corresponding step sizes) of the outputs are determined by external resistors that adjust the output currents over a 4:1 range. The formula to determine the external resistor values (RFS) for each of the outputs is given by:

#### Equation 1:

$R_{FS} = (V_{REF} / I_{FS}) \times (31 / 4)$

where IFS = desired full-scale current

On power-up, the DS4402/DS4404 output zero current. This is done to prevent it from sinking or sourcing an incorrect current before the system host controller has had a chance to modify the device's setting.

As a source for biasing instrumentation or other circuits, the DS4402/DS4404 provide a simple and inexpensive current source with an I<sup>2</sup>C interface for control. The adjustable full-scale range allows the application to get the most out of its 5-bit sink or source resolution.

When used in adjustable power-supply applications (see the *Typical Operating Circuit*), the DS4402/DS4404 do not affect the initial power-up supply voltage because it defaults to providing zero output current on power-up. As it sources or sinks current into the feedback voltage node, it changes the amount of output voltage required by the regulator to reach its steady state operating point. By using the external resistor to set the output current range, the devices provide flexibility for adjusting the impedances of the feedback network or the range over which the power supply can be controlled or margined.

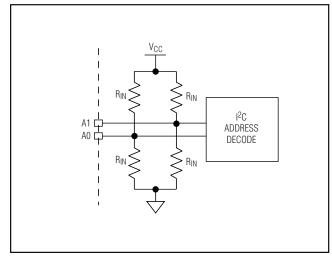

#### I<sup>2</sup>C Slave Address

The DS4402/DS4404 respond to one of nine I<sup>2</sup>C slave addresses determined by the two tri-level address inputs. The three input states are connected to V<sub>CC</sub>, connected to ground, or disconnected. To sense the disconnected state (Figure 2), the address inputs have weak internal resistors that pull the pins to mid-supply.

Figure 2. I<sup>2</sup>C Address Inputs

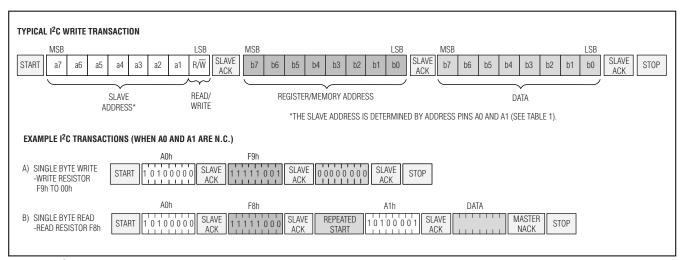

Table 1 lists the slave address determined by the address input combinations.

#### **Table 1. Slave Addresses**

| A1              | Α0              | SLAVE ADDRESS<br>(HEXADECIMAL) |

|-----------------|-----------------|--------------------------------|

| GND             | GND             | 90h                            |

| GND             | Vcc             | 92h                            |

| Vcc             | GND             | 94h                            |

| V <sub>CC</sub> | V <sub>CC</sub> | 96h                            |

| N.C.            | GND             | 98h                            |

| N.C.            | Vcc             | 9Ah                            |

| GND             | N.C.            | 9Ch                            |

| Vcc             | N.C.            | 9Eh                            |

| N.C.            | N.C.            | A0h                            |

#### **Memory Organization**

To control the DS4402/DS4404's current sources, write to the memory addresses listed in Table 2.

### Table 2. Memory Addresses

| MEMORY ADDRESS<br>(HEXADECIMAL) | CURRENT SOURCE |

|---------------------------------|----------------|

| F8h                             | OUT0           |

| F9h                             | OUT1           |

| FAh*                            | OUT2*          |

| FBh*                            | OUT3*          |

<sup>\*</sup>Only for DS4404.

The format of each output control register is given by:

| MSB |   |   |                |                |                |                | LSB            |

|-----|---|---|----------------|----------------|----------------|----------------|----------------|

| S   | Χ | Χ | D <sub>4</sub> | D <sub>3</sub> | D <sub>2</sub> | D <sub>1</sub> | D <sub>0</sub> |

#### Where:

| ВІТ | NAME     | FUNCTION                                                                                                             | POWER-ON<br>DEFAULT |

|-----|----------|----------------------------------------------------------------------------------------------------------------------|---------------------|

| S   | Sign Bit | Determines if DAC sources or sinks current. For sink S = 0, for source S = 1.                                        | 0b                  |

| Х   | Reserved | Reserved. Both bits read zero.                                                                                       | 00b                 |

| Dx  | Data     | 5-Bit Data Word Controlling DAC Output. Setting 00000b outputs zero current regardless of the state of the sign bit. | 00000b              |

Example: IFS0 =  $800\mu A$ , and register F8h is written to a value of 92h. Calculate the value of external resistance required, and the magnitude of the output current with this register setting.

$$R_{FS} = (V_{REF} / 800 \mu A) \times (31 / 4) = 11.9 k\Omega$$

The MSB of the output register is 1, so the output is sourcing the value corresponding to position 12h (18 decimal). The magnitude of the output current is equal to:

$$800\mu A \times (18 / 31) = 465\mu A$$

## \_I<sup>2</sup>C Serial Interface Description

I<sup>2</sup>C Definitions

The following terminology is commonly used to describe I<sup>2</sup>C data transfers:

**Master Device:** The master device controls the slave devices on the bus. The master device generates SCL clock pulses, START and STOP conditions.

**Slave Devices:** Slave devices send and receive data at the master's request.

**Bus Idle or Not Busy:** Time between STOP and START conditions when both SDA and SCL are inactive and in their logic-high states. When the bus is idle it often initiates a low-power mode for slave devices.

**START Condition:** A START condition is generated by the master to initiate a new data transfer with a slave. Transitioning SDA from high to low while SCL remains high generates a START condition. See Figure 3 for applicable timing.

**STOP Condition:** A STOP condition is generated by the master to end a data transfer with a slave. Transitioning SDA from low to high while SCL remains high generates a STOP condition. See Figure 3 for applicable timing.

Repeated START Condition: The master can use a repeated START condition at the end of one data transfer to indicate that it will immediately initiate a new data transfer following the current one. Repeated starts are commonly used during read operations to identify a specific memory address to begin a data transfer. A repeated START condition is issued identically to a normal START condition. See Figure 3 for applicable timing.

**Bit Write:** Transitions of SDA must occur during the low state of SCL. The data on SDA must remain valid and unchanged during the entire high pulse of SCL, plus the setup and hold time requirements (Figure 3). Data is shifted into the device during the rising edge of the SCL.

**Bit Read:** At the end of a write operation, the master must release the SDA bus line for the proper amount of setup time (Figure 3) before the next rising edge of SCL during a bit read. The device shifts out each bit of data on SDA at the falling edge of the previous SCL pulse and the data bit is valid at the rising edge of the current SCL pulse. Remember that the master generates all SCL clock pulses, including when it is reading bits from the slave.

Acknowledgement (ACK and NACK): An Acknowledgement (ACK) or Not Acknowledge (NACK) is always the ninth bit transmitted during a byte transfer. The device receiving data (the master during a read or the slave during a write operation) performs an ACK by transmitting a zero during the ninth bit. A device performs a NACK by transmitting a one during the ninth bit. Timing for the ACK and NACK is identical to all other bit writes (Figure 4). An ACK is the acknowledgment that the device is properly receiving data. A NACK is used to terminate a read sequence or as an indication that the device is not receiving data.

**Byte Write:** A byte write consists of 8 bits of information transferred from the master to the slave (most significant bit first) plus a 1-bit acknowledgement from the slave to the master. The 8 bits transmitted by the master are done according to the bit-write definition, and the acknowledgement is read using the bit-read definition.

**Byte Read:** A byte read is an 8-bit information transfer from the slave to the master plus a 1-bit ACK or NACK from the master to the slave. The 8 bits of information that are transferred (most significant bit first) from the slave to the master are read by the master using the bit read definition above, and the master transmits an ACK using the bit write definition to receive additional data bytes. The master must NACK the last byte read to terminated communication so the slave will return control of SDA to the master.

**Slave Address Byte:** Each slave on the I<sup>2</sup>C bus responds to a slave address byte sent immediately following a START condition. The slave address byte contains

the slave address in the most significant 7 bits and the R/W bit in the least significant bit. The DS4402/DS4404s' slave address is determined by the state of the A0 and A1 address pins. Table 1 describes the addresses corresponding to the state of A0 and A1.

When the  $R\overline{W}$  bit is 0 (such as in A0h), the master is indicating it will write data to the slave. If  $R/\overline{W}=1$  (A1h in this case), the master is indicating it wants to read from the slave. If an incorrect slave address is written, the DS4402/DS4404 assume the master is communicating with another I<sup>2</sup>C device and ignore the communication until the next START condition is sent.

**Memory Address:** During an I<sup>2</sup>C write operation, the master must transmit a memory address to identify the memory location where the slave is to store the data. The memory address is always the second byte transmitted during a write operation following the slave address byte.

### I<sup>2</sup>C Communication

**Writing to a Slave:** The master must generate a START condition, write the slave address byte  $(R/\overline{W}=0)$ , write the memory address, write the byte of data, and generate a STOP condition. Remember that the master must read the slave's acknowledgement during all byte-write operations.

**Reading from a Slave:** To read from the slave, the master generates a START condition, writes the slave address byte with  $R/\overline{W}=1$ , reads the data byte with a NACK to indicate the end of the transfer, and generates a STOP condition.

Figure 3. I<sup>2</sup>C Timing Diagram

## Application Information

# **Example Calculations for an Adjustable Power Supply**

Using the typical circuit, assuming a typical output voltage of 2.0V, a feedback voltage of 0.8V, R1 = 500 $\Omega$ , and R2 = 333 $\Omega$ , to adjust or margin the supply 20% requires a full-scale current equal to [(0.2 x 2.0V) / 500 $\Omega$  = 800 $\mu$ A]. Using Equation 1, RFS can be calculated [RFS = (VREF / 800 $\mu$ A) x (31 / 4) = 11.9k $\Omega$ ]. The current DAC in this configuration allows the output voltage to be stepped linearly from 1.6V to 2.4V using 63 settings. This corresponds to a resolution of 12.7mV/step.

#### **Power-Supply Feedback Voltage**

The feedback voltage for adjustable power supplies must be between 0.5V and VCC - 0.5V for the DS4402/DS4404 to properly sink/source currents for adjusting the voltage.

### I<sup>2</sup>C Reset on Address Change

In addition to defining the I<sup>2</sup>C slave address, the DS4402/DS4404 address select inputs have an alternate function.

Changing the address select inputs resets the I<sup>2</sup>C interface. This function aborts the current transaction and puts the SDA driver into a high-impedance state. This hardware reset function should never be required because it is achievable through software, but it does provide an alternative way of resetting the I<sup>2</sup>C interface, if needed.

### **Vcc Decoupling**

To achieve the best results when using the DS4402/DS4404, decouple the power supply with a 0.01µF or 0.1µF capacitor. Use a high-quality ceramic surfacemount capacitor if possible. Surface-mount components minimize lead inductance, which improves performance, and ceramic capacitors tend to have adequate high-frequency response for decoupling applications.

#### **Layout Considerations**

Care should be taken to ensure that traces underneath the DS4402/DS4404 do not short with the exposed pad. The exposed pad should be connected to the signal ground, or can be left floating.

Figure 4. I<sup>2</sup>C Communication Examples

## \_Chip Information

Package Information

TRANSISTOR COUNT: 10,992

For the latest package outline information, go to **www.maxim-ic.com/DallasPackInfo**.

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

© 2006 Maxim Integrated Products

Printed USA

is a registered trademark of Maxim Integrated Products, Inc.