December 2003

# DS90C387R 85MHz Dual 12-Bit Double Pumped Input LDI Transmitter - VGA/UXGA

### **General Description**

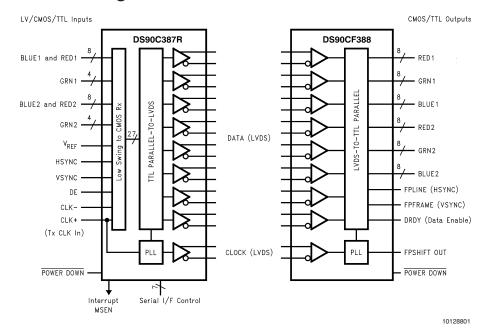

The DS90C387R transmitter is designed to support pixel data transmission from a Host to a Flat Panel Display up to UXGA resolution. It is designed to be compatible with Graphics Memory Controller Hub( GMCH) by implementing two data per clock and can be controlled by a two-wire serial communication interface. Two input modes are supported: one port of 12-bit( two data per clock) input for 24-bit RGB, and two ports of 12-bit( two data per clock) input for dual 24-bit RGB( 48-bit total). In both modes, input data will be clocked on both rising and falling edges in LVTTL level operation, or clocked on the cross over of differential clock signals in the low swing operation. Each input data width will be 1/2 of clock cycle. With an input clock at 85MHz and input data at 170Mbps, the maximum transmission rate of each LVDS line is 595Mbps, for a aggregate throughput rate of 2.38Gbps/4.76Gbps. It converts 24/48 bits (Single/Dual Pixel 24-bit color) of data into 4/8 LVDS (Low Voltage Differential Signaling) data streams. DS90C387R can be programmed via the two-wire serial communication interface. The LVDS output pin-out is identical to DS90C387. Thus, this transmitter can be paired up with DS90CF388, receiver of the 112MHz LDI chipset or FPD-Link Receivers in non-DC Balance mode operation which provides GUI/LCD panel/ mother board vendors a wide choice of inter-operation with LVDS based TFT panels.

DS90C387R also comes with features that can be found on DS90C387. Cable drive is enhanced with a user selectable pre-emphasis feature that provides additional output current during transitions to counteract cable loading effects. DC Balancing on a cycle-to-cycle basis is also provided to reduce ISI( Inter-Symbol Interference), control signals ( VSYNC, HSYNC, DE) are sent during blanking intervals. With pre-emphasis and DC Balancing, a low distortion eyepattern is provided at the receiver end of the cable. These enhancements allow cables 5 to 15+ meters in length to be driven depending on media characteristic and pixel clock speed. Pre-emphasis is available in both the DC Balanced

and Non-DC Balanced modes. In the Non-DC Balanced mode backward compatibility with FPD-Link Receivers is obtained.

This chip is an ideal solution to solve EMI and cable size problems for high-resolution flat panel display applications. It provides a reliable industry standard interface based on LVDS technology that delivers the bandwidth needed for high-resolution panels while maximizing bit times, and keeping clock rates low to reduce EMI and shielding requirements. For more details, please refer to the "Applications Information" section of this datasheet.

#### **Features**

- Complies with Open LDI specification for digital display interfaces

- 25 to 85MHz clock support

- Supports VGA through UXGA panel resolution

- Up to 4.76Gbps bandwidth in dual 24-bit RGB in-to-dual pixel out application.

- Dual 12-bit Double Pumped Input DVO port.

- Pre-emphasis reduces cable loading effects.

- Drives long, low cost cables

- DC Balance data transmission provided by transmitter reduces ISI distortion

- Transmitter rejects cycle-to-cycle jitter.(+/– 2ns of input bit period)

- Support both LVTTL and low voltage level input(capable of 1.0 to 1.8V)

- Two-wire serial communication interface up to 400 KHz

- Programmable input clock and control strobe select

- Backward compatible configuration with 112MHz LDI and FPD-Link.

- Optional second LVDS clock for backward compatibility w/ FPD-Link Receivers

- Compatible with TIA/EIA-644

| Mode Configuration / PerformanceTable |                            |           |  |  |  |  |  |  |

|---------------------------------------|----------------------------|-----------|--|--|--|--|--|--|

| Mode                                  | Mode one 12-bit two 12-bit |           |  |  |  |  |  |  |

| Mode (GUI Out/Cable)                  | single/single              | dual/dual |  |  |  |  |  |  |

| Input Clock Rate (MHz)                | 25-85                      | 25-85     |  |  |  |  |  |  |

| Input Data Rate (Mbps)                | 50-170                     | 50-170    |  |  |  |  |  |  |

| LVDS data Pairs Out                   | 4                          | 8         |  |  |  |  |  |  |

| Ouput Clock Rate (MHz)                | 25-85                      | 25-85     |  |  |  |  |  |  |

| Data Rate Out (Mbps) per LVDS channel | 175-595                    | 175-595   |  |  |  |  |  |  |

| Throughput Data Rate Out              | 2.38Gbps                   | 4.76Gbps  |  |  |  |  |  |  |

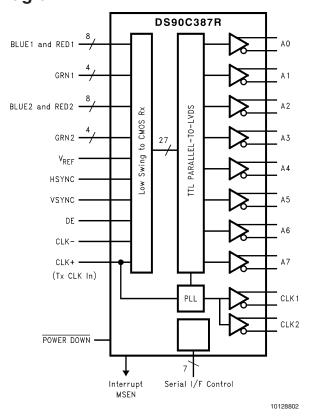

# **Generalized Block Diagrams**

# **Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

Supply Voltage ( $V_{CC}$ ) -0.3V to +4V

LVCMOS/LVTTL Output

Voltage -0.3V to  $(V_{CC} + 0.3V)$

LVDS Driver Output

Voltage -0.3V to  $(V_{CC} + 0.3V)$

LVDS Output Short

Circuit Duration Continuous

Junction Temperature +150°C

Storage Temperature -65°C to +150°C

Lead Temperature

(Soldering, 4 sec.) +260°C

Maximum Package Power Dissipation Capacity @

25°C

100 TQFP Package: 2.8W

Package Derating:

DS90C387R 18.2mW/°C above +25°C

ESD Rating:

(HBM, 1.5kΩ, 100pF) > 2 kV(EIAJ, 0Ω, 200pF) > 300 V

# Recommended Operating Conditions

Min Nom Max Units

All Supply Voltage 3.0 3.3 3.6 V

Operating Free Air

Temperature (T<sub>A)</sub> -10 +25 +70 °C

Supply Noise Voltage ( $V_{CC}$ )up 100 m $V_{p-p}$

to 33MHz

#### **Electrical Characteristics**

Over recommended operating supply and temperature ranges unless otherwise specified.(Note 2)

| Symbol            | Parameter                         | Conditions                                             | Min              | Тур                  | Max              | Units |

|-------------------|-----------------------------------|--------------------------------------------------------|------------------|----------------------|------------------|-------|

| LVCMOS/           | LVTTL DC SPECIFICATIONS ( A       | II pins, except output pins AnP, AnI                   | M, CLKnP and C   | LKnM, BAL,           | PD pins)         |       |

| V <sub>IH</sub>   | High Level Input Voltage          | V <sub>REF</sub> = V <sub>CC3V</sub> = V <sub>CC</sub> | 2.0              |                      | V <sub>CC</sub>  | V     |

| V <sub>IL</sub>   | Low Level Input Voltage           | $V_{REF} = V_{CC3V} = V_{CC}$                          | GND              |                      | 0.8              | V     |

| V <sub>CL</sub>   | Input Clamp Voltage               | I <sub>CL</sub> = 18 mA                                |                  | -0.8                 | -1.5             | V     |

| I <sub>IN</sub>   | Input Current                     | $V_{IN} = 0.4V$ , or $V_{CC}$                          |                  | +1.8                 | +15              | μA    |

|                   |                                   | V <sub>IN</sub> = GND                                  | -15              | 0                    |                  | μΑ    |

| V <sub>OL</sub>   | Low level Open Drain Output       | I <sub>OL</sub> = 2 mA                                 |                  | 0.1                  | 0.3              | V     |

|                   | Voltage                           |                                                        |                  |                      |                  |       |

| LVCMOS            | DC SPECIFICATIONS ( PD pin)       |                                                        |                  |                      |                  |       |

| V <sub>IH</sub>   | High Level Input Voltage          | $V_{REF} = V_{CC3V} = V_{CC}$                          | 2.9              |                      | V <sub>CC</sub>  | V     |

| V <sub>IL</sub>   | Low Level Input Voltage           | V <sub>REF</sub> = V <sub>CC3V</sub> = V <sub>CC</sub> | GND              |                      | 0.8              | V     |

| V <sub>CL</sub>   | Input Clamp Voltage               | I <sub>CL</sub> = 18 mA                                |                  | -0.8                 | -1.5             | V     |

| I <sub>IN</sub>   | Input Current                     | $V_{IN} = 0.4V$ , or $V_{CC}$                          |                  | +1.8                 | +15              | μΑ    |

|                   |                                   | V <sub>IN</sub> = GND                                  | -15              | 0                    |                  | μΑ    |

| LVDS DR           | IVER DC SPECIFICATIONS (outp      | out pins AnP, AnM, CLKnP and CLK                       | (nM)             |                      | •                |       |

| V <sub>OD</sub>   | Differential Output Voltage       | $R_L = 100\Omega$                                      | 247              | 345                  | 550              | mV    |

| $\Delta V_{OD}$   | Change in V <sub>OD</sub> between |                                                        |                  |                      | 35               | mV    |

|                   | Complimentary Output States       |                                                        |                  |                      |                  |       |

| V <sub>os</sub>   | Offset Voltage                    |                                                        | 1.125            | 1.25                 | 1.475            | V     |

| ΔV <sub>os</sub>  | Change in V <sub>OS</sub> between |                                                        |                  |                      | 35               | mV    |

|                   | Complimentary Output States       |                                                        |                  |                      |                  |       |

| Ios               | Output Short Circuit Current      | $V_{OUT} = 0V, R_L = 100\Omega$                        |                  | -3.5                 | -11              | mA    |

| l <sub>oz</sub>   | Output TRI-STATE® Current         | $\overline{PD}$ = 0V, $V_{OUT}$ = 0V or $V_{CC}$       |                  | ±1                   | ±10              | μΑ    |

| Low Volta         | age Mode DC SPECIFICATIONS(       | pins D0 to D23, CLKINP, CLKINM, I                      | DE, HSYNC,VSY    | NC)                  |                  |       |

| V <sub>IHLS</sub> | Low Swing High Level Input        |                                                        | V <sub>REF</sub> |                      | 1.8              | V     |

|                   | Voltage, V <sub>CC</sub> = 3V     |                                                        | +100mV           |                      |                  |       |

| V <sub>ILLS</sub> | Low Swing Low Level Input         |                                                        | GND              |                      | V <sub>REF</sub> | V     |

|                   | Voltage,V <sub>CC</sub> = 3V      |                                                        |                  |                      | -100mV           |       |

| V <sub>REF</sub>  | Differential Input Reference      | Low Swing,V <sub>REF</sub> = ½V <sub>DDQ</sub>         | 0.45             | 0.5*V <sub>DDQ</sub> | 1                | V     |

|                   | Voltage, V <sub>CC</sub> = 3V     |                                                        |                  |                      |                  |       |

#### **Electrical Characteristics** (Continued)

Over recommended operating supply and temperature ranges unless otherwise specified.(Note 2)

| Symbol  | Parameter                                    | Cond                                         | itions                                  | Min | Тур | Max | Units |

|---------|----------------------------------------------|----------------------------------------------|-----------------------------------------|-----|-----|-----|-------|

| TRANSMI | TTER SUPPLY CURRENT                          |                                              |                                         |     |     | •   | •     |

| ICCTW   | Transmitter Supply Current<br>Worst Case     | $R_L = 100\Omega$ , $C_L = 5$ pF,            | f = 32.5 MHz,<br>DUAL = V <sub>CC</sub> |     | 115 | 180 | mA    |

|         |                                              | Worst Case<br>Pattern                        | f = 32.5 MHz,<br>DUAL = Gnd             |     | 75  |     | mA    |

|         |                                              | ( <i>Figure 3</i> , BAL=High                 | f = 65 MHz,<br>DUAL = V <sub>CC</sub>   |     | 150 | 215 | mA    |

|         |                                              | (enabled), V <sub>CC</sub> = 3.6V            | f = 65 MHz,<br>DUAL = Gnd               |     | 95  |     | mA    |

|         |                                              |                                              | f = 85 MHz,<br>DUAL = V <sub>CC</sub>   |     | 175 | 235 | mA    |

|         |                                              |                                              | f = 85 MHz,<br>DUAL = Gnd               |     | 110 |     | mA    |

| ICCTG   | Transmitter Supply Current 16 Grayscale Case | $R_L = 100\Omega$ , $C_L = 5$ pF,            | f = 32.5  MHz,<br>$DUAL = V_{CC}$       |     | 110 | 170 | mA    |

|         |                                              | 16 Grayscale<br>Pattern                      | f = 32.5 MHz,<br>DUAL = Gnd             |     | 70  |     | mA    |

|         |                                              | Figure 2, BAL = High (enabled),              | f = 65 MHz,<br>DUAL = V <sub>CC</sub>   |     | 135 | 205 | mA    |

|         |                                              | $V_{CC} = 3.6V$                              | f = 65 MHz,<br>DUAL = Gnd               |     | 90  |     | mA    |

|         |                                              |                                              | f = 85 MHz,<br>DUAL = V <sub>CC</sub>   |     | 155 | 225 | mA    |

|         |                                              |                                              | f = 85 MHz,<br>DUAL = Gnd               |     | 100 |     | mA    |

| ICCTZ   | Transmitter Supply Current<br>Power Down     | PD = Low Driver Outputs in TF Powerdown Mode | RI-STATE under                          |     | 4.8 | 85  | μА    |

**Note 1:** "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. They are not meant to imply that the device should be operated at these limits. The tables of "Electrical Characteristics" specify conditions for device operation.

# DIGITAL DC CHARACTERISTICS for Two-Wire Serial Communication Interface

Over recommended operating supply and temperature ranges unless otherwise specified.(Note 2) Parameters list below only valid when I2CSEL pin = Vcc.

| Symbol              | Parameter                           | Conditions           | Min | Тур | Max | Units |

|---------------------|-------------------------------------|----------------------|-----|-----|-----|-------|

| V <sub>IN</sub> (1) | Logical " 1 " input voltage         |                      | 2.1 |     |     | V     |

| V <sub>IN</sub> (0) | Logical " 0 " input voltage         |                      |     |     | 0.8 | V     |

| V <sub>OL</sub>     | Serial Bus Low level output voltage | I <sub>OL</sub> =3mA |     |     | 0.4 | V     |

|                     |                                     | I <sub>OL</sub> =6mA |     |     | 0.6 | V     |

Note 2: Typical values are given for  $V_{CC}$  = 3.3V and T  $_{A}$  = +25 $^{\circ}C$ . Device tested in Non-Balanced mode only.

**Note 3:** Current into device pins is defined as positive. Current out of device pins is defined as negative. Voltages are referenced to ground unless otherwise specified (except  $V_{OD}$  and  $\Delta V_{OD}$ ).

Note 4: Low Swing DC threshold testing is preformed on data and control inputs only. Clock inputs tested by functional testing only.

# **Recommended Transmitter Input Characteristics**

Over recommended operating supply and temperature ranges unless otherwise specified. Device driving the transmitter inputs should comply to this table of recommendations.

| Symbol | Parameter                             |                               |       | Тур  | Max  | Units |

|--------|---------------------------------------|-------------------------------|-------|------|------|-------|

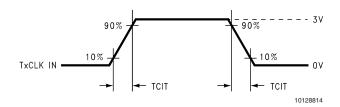

| TCIT   | TxCLK IN Transition Time (Figure 5)   | DUAL = Gnd or V <sub>CC</sub> | 0.8   | 1.2  | 2.4  | ns    |

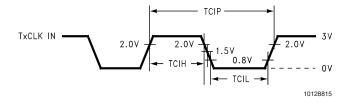

| TCIP   | TxCLK IN Period (Figure 6)            | DUAL = Gnd or V <sub>CC</sub> | 11.76 | Т    | 40   | ns    |

| TCIH   | TxCLK in High Time (Figure 6)         |                               |       | 0.5T | 0.6T | ns    |

| TCIL   | TxCLK in Low Time (Figure 6)          |                               | 0.4T  | 0.5T | 0.6T | ns    |

| VDDQ   | Low Swing Voltage Amplitude from GMCH |                               | 1.0   |      | 1.8  | V     |

# **Transmitter Switching Characteristics**

Over recommended operating supply and temperature ranges unless otherwise specified.(Note 2)

| Symbol | Parameter                                                             | Min                         | Тур  | Max     | Units |    |

|--------|-----------------------------------------------------------------------|-----------------------------|------|---------|-------|----|

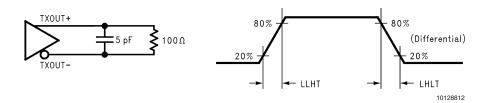

| LLHT   | LVDS Low-to-High Transition Time (Figure 4), PRE = no connect         |                             |      | 0.14    | 0.9   | ns |

|        | (minimum pre-empahsis).                                               |                             |      |         |       |    |

|        | LVDS Low-to-High Transition Time (Figure 4                            | $I)$ , PRE = $V_{CC}$ (max. |      | 0.11    | 0.7   | ns |

|        | pre-empahsis).                                                        |                             |      |         |       |    |

| LHLT   | LVDS High-to-Low Transition Time (Figure 4                            | t), PRE = no connect        |      | 0.16    | 0.9   | ns |

|        | (mini. pre-empahsis).                                                 | * DDE _ \/ _ /              |      | 0.44    |       |    |

|        | LVDS High-to-Low Transition Time (Figure 4 pre-empahsis).             | $V_{CC}$ (max.              |      | 0.11    | 0.7   | ns |

| TCCS   | TxOUT Channel to Channel Skew                                         |                             |      | 100     |       | ps |

| TPPOS0 | Transmitter Output Pulse Position for Bit0 from TxCLKout rising edge. | f = 85MHz (Note 8)          | -300 | 0       | +300  | ps |

| TPPOS1 | Transmitter Output Pulse Position for Bit1 from TxCLKout rising edge. |                             | 1.38 | 1.68    | 1.98  | ns |

| TPPOS2 | Transmitter Output Pulse Position for Bit2                            | -                           | 3.06 | 3.36    | 3.66  | ns |

|        | from TxCLKout rising edge.                                            |                             |      |         |       |    |

| TPPOS3 | Transmitter Output Pulse Position for Bit3                            |                             | 4.74 | 5.04    | 5.34  | ns |

|        | from TxCLKout rising edge.                                            |                             |      |         |       |    |

| TPPOS4 | Transmitter Output Pulse Position for Bit4                            |                             | 6.42 | 6.72    | 7.02  | ns |

|        | from TxCLKout rising edge.                                            |                             |      |         |       |    |

| TPPOS5 | Transmitter Output Pulse Position for Bit5                            |                             | 8.10 | 8.40    | 8.70  | ns |

| TDDOOG | from TxCLKout rising edge.                                            | _                           | 0.70 | 10.00   | 10.00 |    |

| TPPOS6 | Transmitter Output Pulse Position for Bit6 from TxCLKout rising edge. |                             | 9.78 | 10.08   | 10.38 | ns |

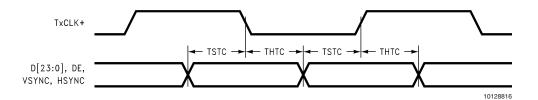

| TSTC   | TxIN Setup to TxCLK IN in low swing mode                              | at 85 MHz (Figure 7)        | 1.8  |         |       | ns |

| THTC   | TxIN Hold to TxCLK IN in low swing mode a                             | t 85 MHz (Figure 7)         | 2    |         |       | ns |

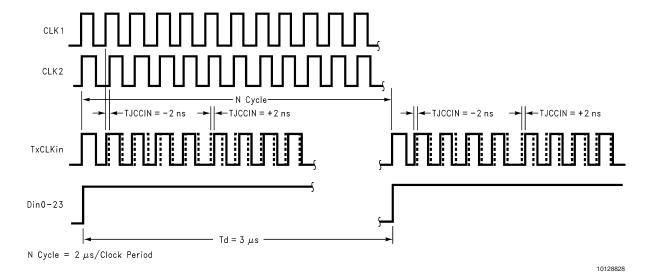

| TJCC   | Transmitter Jitter Cycle-to-cycle (Figures                            | f = 85 MHz                  |      | 110     | 150   | ps |

|        | 12, 13) (Note 5), DUAL = Gnd, V <sub>CC</sub> = 3V                    | f = 65 MHz                  |      | 80      | 120   | ps |

|        |                                                                       | f = 32.5 MHz                |      | 75      | 115   | ps |

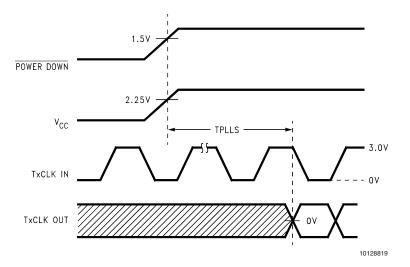

| TPLLS  | Transmitter Phase Lock Loop Set (Figure 8)                            | •                           |      |         | 10    | ms |

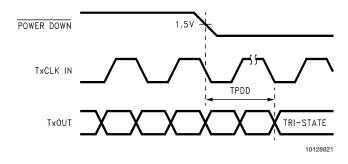

| TPDD   | Transmitter Powerdown Delay (Figure 9)                                |                             |      |         | 100   | ns |

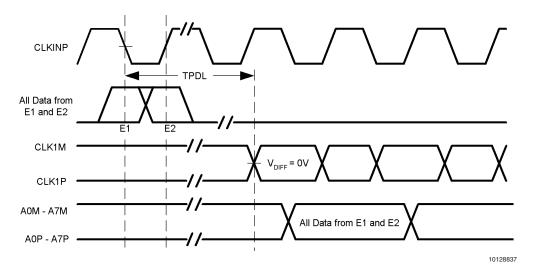

| TPDL   | Transmitter Input to Output Latency (Figure                           | f = 32.5/65/85 MHz          |      | 1.5TCIP |       | ns |

|        | 10)                                                                   | (Note 9)                    |      | +4.1    |       |    |

#### **Transmitter Switching Characteristics** (Continued)

Note 5: The limits are based on bench characterization of the device's jitter response over the power supply voltage range. Output clock jitter is measured with a cycle-to-cycle jitter of ±2ns applied to the input clock signal while data inputs are switching (see figures 10 and 11). A jitter event of 2ns, represents worse case jump in the clock edge from most graphics VGA chips currently available. This parameter is used when calculating system margin as described in AN-1059.

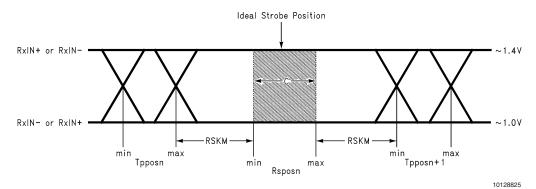

**Note 6:** Receiver Skew Margin is defined as the valid data sampling region at the receiver inputs. This margin takes into account transmitter output pulse positions (min and max) and the receiver input setup and hold time (internal data sampling window - RSPOS). This margin allows for LVDS interconnect skew, inter-symbol interference (both dependent on type/length of cable) and clock jitter.

RSKM ≥ cable skew (type, length) + source clock jitter (cycle to cycle).

Note 7: This limit is based on the capability of deskew circuitry. This margin allows for LVDS interconnect skew, inter-symbol interference (both dependent on type/length of cable) and clock jitter. RSKM with deskew is ± 1 LVDS bit time (1/7th clock period) data to clock skew.

Note 8: The parameters are guaranteed by design. The limits are based on statistical analysis of the device performance over PVT(process, voltage and temperature) range.

Note 9: From V = 1.5V of CLKINP to V<sub>DIFF</sub>= 0V of CLK1P when R\_FB = High, DUAL = Low or High, BAL = Low.

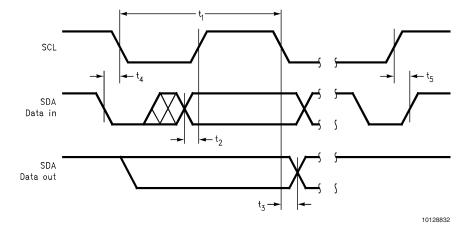

# DIGITAL SWITCHING CHARACTERISTICS for Two-Wire Serial Communication Interface

Unless otherwise noted, below specifications apply for  $V_{cc}$ =+3.3V, load capacitance on output lines = 80 pF. Load capacitance on output lines can be up to 400 pF provided that external pull-up switch is on board. The following parameters are the timing relationships between SCL and SDA signals related to the DS90C387R.

| Symbol         | Parameter                                          | Min | Тур | Max | Units |

|----------------|----------------------------------------------------|-----|-----|-----|-------|

| t <sub>1</sub> | SCL (Clock) Period                                 | 2.5 |     |     | μs    |

| t <sub>2</sub> | Data in Set-Up Time to SCL High                    | 100 |     |     | ns    |

| t <sub>3</sub> | Data Out Stable after SCL Low                      | 0   |     |     | ns    |

| t <sub>4</sub> | SDA Low Set-Up Time to SCL Low (Start Condition)   | 100 |     |     | ns    |

|                | SDA High Hold Time after SCL High (Stop Condition) | 100 |     |     | ns    |

### **AC Timing Diagrams**

FIGURE 1. Two-Wire Serial Communication Interface Timing Diagram when I2CSEL = Vcc

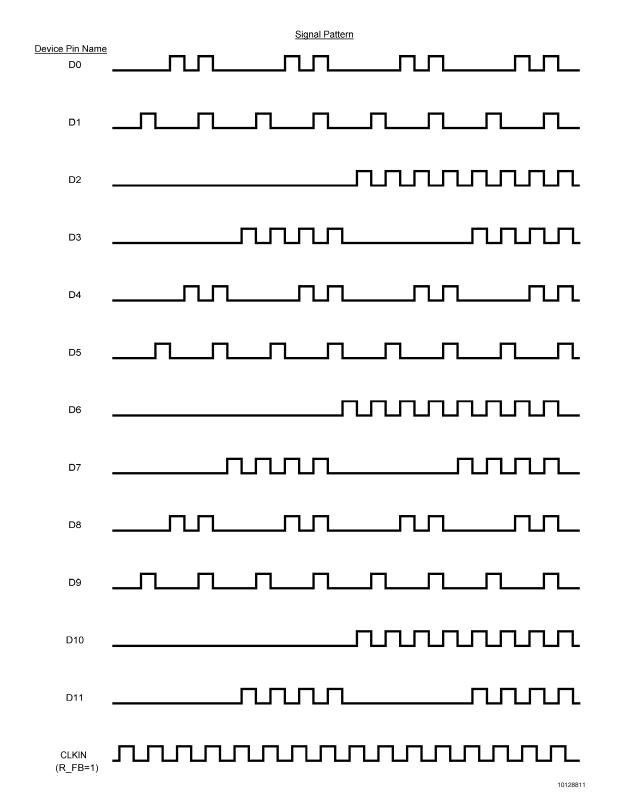

FIGURE 2. "16 Grayscale" Test Pattern (Note 11)

Note 10: The worst case test pattern produces a maximum toggling of digital circuits, LVDS I/O and CMOS/TTL I/O.

Note 11: The 16 grayscale test pattern tests device power consumption for a "typical" LCD display pattern. The test pattern approximates signal switching needed to produce groups of 16 vertical stripes across the display.

FIGURE 3. "Worst Case" Test Pattern (Note 10)

FIGURE 4. DS90C387R LVDS Output Load and Transition Times

FIGURE 5. DS90C387R Input Clock Transition Time

FIGURE 6. DS90C387R TxCLK IN Period, and High/Low Time (Falling Edge Strobe)

FIGURE 7. DS90C387R Setup/Hold (Falling Edge Strobe First)

FIGURE 8. DS90C387R Phase Lock Loop Set Time

FIGURE 9. DS90C387R Power Down Delay

FIGURE 10. DS90C387R Input to Output Latency(Note 9)

$C-Setup \ and \ Hold \ Time \ (Internal \ data \ sampling \ window) \ defined \ by \ Rspos \ (receiver \ input \ strobe \ position) \ min \ and \ max$

Tppos — Transmitter output pulse position (min and max)

RSKM = Cable Skew (type, length) + Source Clock Jitter (cycle to cycle) (Note 12) + ISI (Inter-symbol interference) (Note 13)

Cable Skew — typically 10 ps-40 ps per foot, media dependent

Note 12: Cycle-to-cycle jitter is less than 150 ps at 85 MHz

Note 13: ISI is dependent on interconnect length; may be zero

#### FIGURE 11. Receiver Skew Margin

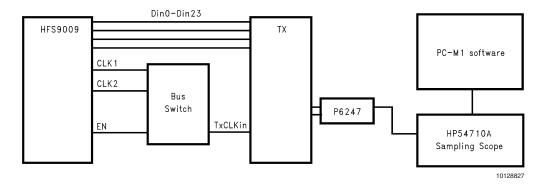

FIGURE 12. TJCC Test Setup - DS90C387R

FIGURE 13. Timing Diagram of the Input Cycle-to-Cycle Clock Jitter

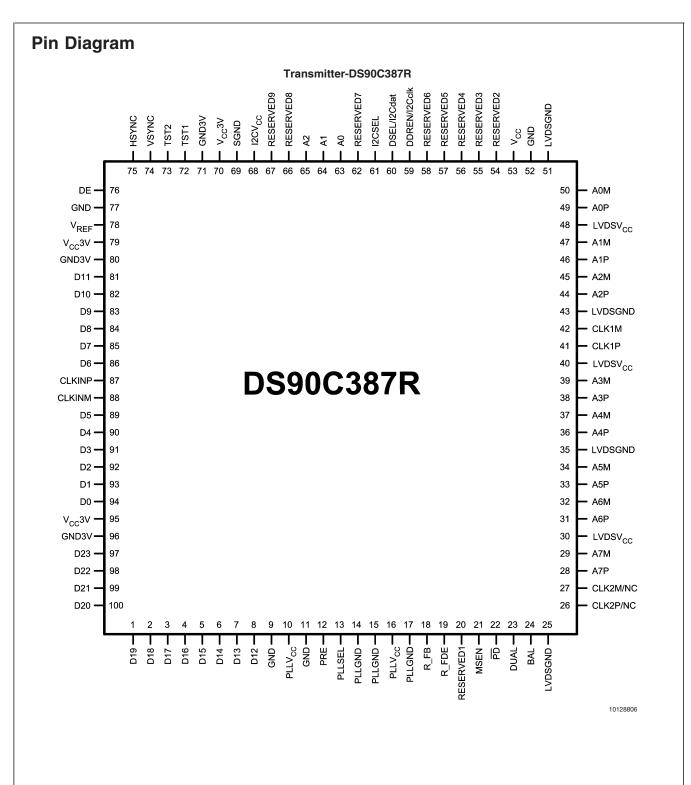

# DS90C387R Pin Description—LDI Transmitter

| Pin Name          | I/O | No. | Description                                                                             |

|-------------------|-----|-----|-----------------------------------------------------------------------------------------|

| D0-D23            | I   | 24  | LVTTL level single-ended inputs or low swing pseduo differential inputs.                |

|                   |     |     | Reference to V <sub>REF</sub> pin.                                                      |

|                   |     |     | D0-D11 are for 12-bit input mode (24 RGB data); D0-D11 (first 12-bit port)              |

|                   |     |     | and D12-D23 (second 12-bit port) are for two 12-bit input mode (48 RGB                  |

|                   |     |     | data).                                                                                  |

| DE                | I   | 1   | LVTTL level or low swing level inputs for data enable. This signal is HIGH              |

|                   |     |     | when input pixel data is valid to DS90C387R provided that R_FDE = HIGH.                 |

| HSYNC             | I   | 1   | Horizontal Sync input control signal. LVTTL level or low swing level.                   |

| VSYNC             | I   | 1   | Vertical Horizontal Sync input control signal. LVTTL level or low swing level.          |

| AnP               | 0   | 8   | Positive LVDS differential data output.                                                 |

| AnM               | 0   | 8   | Negative LVDS differential data output.                                                 |

| CLKINP            | ı   | 1   | In LVTTL level operation, this is a single-ended clock. In low swing                    |

|                   |     |     | operation, this is the positive differential clock input .                              |

| CLKINM            | ı   | 1   | In LVTTL level operation, no connect or connect to V <sub>REF</sub> pin. Do not connect |

|                   |     |     | to GND under any condition. In low swing operation, this is negative                    |

|                   |     |     | differential clock input .                                                              |

| R_FB              | ı   | 1   | LVTTL level input for selecting the Primary clock edge E1. Falling clock                |

|                   |     |     | edge selected when input is HIGH; Rising clock edge selected when input is              |

|                   |     |     | LOW.(Note 14)                                                                           |

| R_FDE             | I   | 1   | LVTTL level input. Programmable control (DE) strobe select. Tie HIGH for                |

|                   |     |     | data active when DE is HIGH. (Note 14)                                                  |

| CLK1P             | 0   | 1   | Positive LVDS differential clock output.                                                |

| CLK1M             | 0   | 1   | Negative LVDS differential clock output.                                                |

| PD                | ı   | 1   | LVCMOS level input. Input = LOW will place the entire device in power down              |

|                   |     | -   | mode. Outputs of the device will be in TRI-STATE mode to ensure low                     |

|                   |     |     | current at power down. (Note 14)                                                        |

|                   |     |     | Input = HIGH for normal operation.                                                      |

| PLLSEL            | ı   | 1   | LVTTL level in. Tie to Vcc for normal operation. (Note 14)                              |

| BAL               | i   | 1   | LVTTL level input. Mode select for dc balanced or non-dc balanced                       |

| <i>5</i> , (2     |     |     | interface. DC balance is active when input is high. (Note 14)                           |

| PRE               | ı   | 1   | Pre-emphasis level select. Pre-emphasis is active when input is tied to V <sub>CC</sub> |

|                   |     |     | through external pull-up resistor. Resistor value determines pre-emphasis               |

|                   |     |     | level (see table in application section). For normal LVDS drive level                   |

|                   |     |     | (minimum pre-emphasis) leave this pin open (do not tie to ground).(Note 14)             |

| DUAL              | ı   | 1   | LVTTL level input. Input = LOW for one 12-bit input mode, 24 RGB data in,               |

|                   |     |     | 24 RGB data out.(Note 14)                                                               |

|                   |     |     | LVTTL level input. Input = V <sub>CC</sub> for two 12-bit input mode, 48 RGB data in,   |

|                   |     |     | 48 RGB data out.(Note 14)                                                               |

| V <sub>CC</sub>   | ı   | 1   | Connect to power supply with voltage stated under " Recommended                         |

| 66                |     |     | Operating Conitions " on page 3. Power supply pin for LVTTL inputs and                  |

|                   |     |     | digital circuitry, pin53.                                                               |

| GND               | I   | 4   | Ground pins for LVTTL inputs and digital circuitry, pins 9, 11, 52, 77.                 |

| I2V <sub>CC</sub> | ı   | 1   | Connect to power supply with voltage stated under " Recommended                         |

| 00                |     |     | Operating Conitions " on page 3, pin 68.                                                |

| V <sub>CC3V</sub> | ı   | 3   | Connect to power supply with voltage stated under " Recommended                         |

| CC3V              |     |     | Operating Conitions " on page 3, pins 70, 79, 95.                                       |

| GND <sub>3V</sub> | I   | 3   | Ground pin(s) for powering the data inputs, pins 71, 80, 96.                            |

| - '- 3v           | i   | 1   | Connect to ground, pin 69.                                                              |

| Pin Name            | I/O | No. | Description                                                                                                                                                                             |

|---------------------|-----|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PLLV <sub>CC</sub>  | I   | 2   | Connect to power supply with voltage stated under "Recommended Operating Conitions" on page 3. Power supply pins for PLL circuitry, pin 10, 16.                                         |

| PLLGND              | I   | 3   | Ground pins for PLL circuitry, pins 14, 15, 17.                                                                                                                                         |

| LVDSV <sub>CC</sub> | I   | 3   | Connect to power supply with voltage stated under "Recommended Operating Conitions" on page 3. Power supply pins for LVDS outputs, pins 30, 40, 48.                                     |

| LVDSGND             | I   | 4   | Ground pins for LVDS outputs, pins 25, 35, 43, 51.                                                                                                                                      |

| CLK2P/NC            | 0   | 1   | Additional positive LVDS differential clock output identical to CLK1P. No connect if not used.                                                                                          |

| CLK2M/NC            | 0   | 1   | Additional negative LVDS differential clock output identical to CLK1M. No connect if not used.                                                                                          |

| $V_{REF}$           | I   | 1   | V <sub>REF</sub> = 1/2 V <sub>DDQ</sub> , a "Fixed " line of differential input.                                                                                                        |

|                     |     |     | If V <sub>REF</sub> ≥ 1.8V, indicates input data is in LVTTL mode.                                                                                                                      |

|                     |     |     | If V <sub>REF</sub> < 1.1V, indicates input data is in low voltage swing mode.                                                                                                          |

|                     |     |     | In low voltage swing mode, input data = logic HIGH = V <sub>REF</sub> + 100mV.                                                                                                          |

|                     |     |     | In low voltage swing mode, input data = logic LOW = V <sub>REF</sub> - 100mV.                                                                                                           |

|                     |     |     | This pin is not to be left floating. When not use in LVTTL mode, tie to $V_{\rm cc}$                                                                                                    |

| I2CSEL              | I   | 1   | HIGH to enable two-wire serial communication interface; LOW to disable the interface.                                                                                                   |

| DDREN/I2Cclk        | I   | 1   | Always HIGH for one 12-bit port and two 12-bit ports operation. When I2CSEL = HIGH, this is the clock line for the two-wire serial communication interface.                             |

| DSEL/I2Cdat         | I/O | 1   | Differential select pin for CLKIN (HIGH = single-ended, LOW = differentail) or when I2CSEL = HIGH, this is the Bidirectional Data line for the two-wire serial communication interface. |

| A0                  | I   | 1   | when I2CSEL = HIGH, this is one of the Slave Device Address Lower Bits.                                                                                                                 |

| A1                  | I   | 1   | when I2CSEL = HIGH, this is one of the Slave Device Address Lower Bits.                                                                                                                 |

| A2                  | I   | 1   | when I2CSEL = HIGH, this is one of the Slave Device Address Lower Bits.                                                                                                                 |

| MSEN                | 0   | 1   | Interrupt signal. This is an open drain output, pull-up resistor is required.                                                                                                           |

| TST1                |     | 1   | Test pin, tie to Vcc.                                                                                                                                                                   |

| TST2                |     | 1   | Test pin, no connect. Do not tie to ground.                                                                                                                                             |

| RESERVED1           |     | 1   | Reserved pin, tie to ground.                                                                                                                                                            |

| RESERVED2           |     | 1   | Reserved pin, tie to ground.                                                                                                                                                            |

| RESERVED3           |     | 1   | Reserved pin, no connect. Do not tie to ground.                                                                                                                                         |

| RESERVED4           |     | 1   | Reserved pin, tie to ground.                                                                                                                                                            |

| RESERVED5           |     | 1   | Reserved pin, tie to ground.                                                                                                                                                            |

| RESERVED6           |     | 1   | Reserved pin, tie to ground.                                                                                                                                                            |

| RESERVED7           |     | 1   | Reserved pin, tie to ground.                                                                                                                                                            |

| RESERVED8           |     | 1   | Reserved pin, tie to ground.                                                                                                                                                            |

| RESERVED9           |     | 1   | Reserved pin, tie to ground.                                                                                                                                                            |

Note 14: Inputs default to "low" when left open due to internal pull-down resistor.

TABLE 1. Control Settings for mode selection

| Mode           | 12bit | Two 12-bit |  |  |  |  |  |

|----------------|-------|------------|--|--|--|--|--|

| DUAL           | L     | Н          |  |  |  |  |  |

| BAL            | L/H   | L/H        |  |  |  |  |  |

| I2CSEL         | L     | L          |  |  |  |  |  |

| DDREN/I2Cclk   | Н     | Н          |  |  |  |  |  |

| CLKIN polarity | R_FB  | R_FB       |  |  |  |  |  |

# DS90C387R Pin Description—LDI Transmitter (Continued)

TABLE 1. Control Settings for mode selection (Continued)

| Mode                                | 12bit                                                             | Two 12-bit                                                                     |  |  |  |  |

|-------------------------------------|-------------------------------------------------------------------|--------------------------------------------------------------------------------|--|--|--|--|

| CLKIN,single-ended/<br>differentail | DSEL                                                              | DSEL                                                                           |  |  |  |  |

| Description                         | 12-bit in, 24-bit pixel out,<br>non-DC Balanced or<br>DC-Balanced | Two 12-bit in, two 24-bit<br>pixels out, non-DC<br>Balanced or<br>DC-Balanced. |  |  |  |  |

13

# DS90C387R Pin Description—LDI Transmitter (Continued)

TABLE 2. Relationship between R\_FB, DE, HSYNC and VSYNC pins

| R_FB | Primary Edge | Secondary Edge | DE latches on | HSYNC latches on | VSYNC latches on |

|------|--------------|----------------|---------------|------------------|------------------|

| VCC  | Falling      | Rising         | Rising        | Falling          | Falling          |

| GND  | Rising       | Falling        | Falling       | Rising           | Rising           |

# **Two-Wire Serial Communication Interface Description**

The DS90C387R operates as a slave on the Serial Bus, so the SCL line is an input (no clock is generated by the DS90C387R) and the SDA line is bi-directional. DS90C387R has a 7-bit slave address. The address bits are controlled by the state of the address select pins A2, A1 and A0, and are set by connecting these pins to ground for a LOW, (0) , to  $V_{\rm CC}$  for a HIGH, (1).

Therefore, the complete slave address is:

| A6  | A5 | A4 | А3 | A2 | A1 | A0  |

|-----|----|----|----|----|----|-----|

| MSB |    |    |    |    |    | LSB |

and is selected as follows:

| Ado | Iress Selec<br>State | DS90C387R Serial<br>Bus Slave Address |              |

|-----|----------------------|---------------------------------------|--------------|

| A2  | A1                   | A0                                    | A6:A0 binary |

| 0   | 0                    | 0                                     | 0111000      |

| 0   | 0                    | 1                                     | 0111001      |

| 0   | 1                    | 0                                     | 0111010      |

| 0   | 1                    | 1                                     | 0111011      |

| 1   | 0                    | 0                                     | 0111100      |

| 1   | 0                    | 1                                     | 0111101      |

| 1   | 1                    | 0                                     | 0111110      |

| 1   | 1                    | 1                                     | 0111111      |

The DS90C387R latches the state of the address select pins during the first read or write on the Serial Bus. Changing the state of the address select pins after the first read or write to any device on the Serial Bus will not change the slave address of the DS90C387R.

A zero in front of the register address is required as the most left column shown in the table below. For example, to access register F, "0F" is the correct way of accessing the register.

TABLE 3. Register Mapping(" \* ' = features not implemented on DS90C387R)

|      | TABLE 3. Register Mapping( = reatures not implemented on D590C387H) |             |               |           |                          |          |            |         |

|------|---------------------------------------------------------------------|-------------|---------------|-----------|--------------------------|----------|------------|---------|

| Addr | Bit7                                                                | Bit6        | Bit5          | Bit4      | Bit3                     | Bit2     | Bit1       | Bit0    |

| 000  |                                                                     |             |               | VND_I     | DL(RO)                   |          |            |         |

| 001  |                                                                     |             |               | VND_I     | )H(RO)                   |          |            |         |

| 002  |                                                                     |             |               | DEV_I     | DL(RO)                   |          |            |         |

| 003  |                                                                     |             |               | DEV_ID    | H(RO)                    |          |            |         |

| 004  |                                                                     |             |               | DEV_RI    | EV(RO)                   |          |            |         |

| 005  |                                                                     |             |               | RSVD[7    | :0](RO)                  |          |            |         |

| 006  |                                                                     |             |               | FRQ_LOV   | V[7:0](RO)               |          |            |         |

| 007  |                                                                     |             |               | FRQ_HIGH  | H[7:0](RO)               |          |            |         |

| 008  | RSV                                                                 | D[1:0]      | VEN(RW)       | HEN(RW)   | DSEL(RW)                 | BSEL(RW) | EDGE(RW)   | PD(RW)  |

| 009  | VLOW(RO)                                                            |             | MSEL[2:0](RW) |           | TSEL(RW)                 | RSEN(RO) | *HTPLG(RO) | MDI(RW) |

| 00A  |                                                                     | *DK[3:1](RW | )             | *DKEN(RW) | W) CTL[3:1](RW) RSVD(RW) |          |            |         |

| 00B  |                                                                     |             |               | *CFG[7    | :0](RO)                  |          |            |         |

| 00C  | *VDJK[7:0](RW)                                                      |             |               |           |                          |          |            |         |

| 00D  | RSVD[3:0](RW) RSVD[3:0](RO)                                         |             |               |           |                          |          |            |         |

| 00E  | RSVD[7:0](RW)                                                       |             |               |           |                          |          |            |         |

| 00F  |                                                                     |             |               | RSVD[7    | :0](RW)                  |          |            |         |

# Two-Wire Serial Communication Interface Description (Continued)

TABLE 4. Register Field Definitions(' \* " = features not implemented on DS90C387R)

| Field      | Access | Description                                                                                              |

|------------|--------|----------------------------------------------------------------------------------------------------------|

| VND_IDL    | RO     | Vendor ID low byte, value is 05h.                                                                        |

| VND_IDH    | RO     | Vendor ID high byte, value is 13h.                                                                       |

| DEV_IDL    | RO     | Device ID low byte, value is 24h.                                                                        |

| DEV_IDH    | RO     | Device ID high byte, value is 67h.                                                                       |

| DEV_REV    | RO     | Device revision, value is 00h.                                                                           |

| FRQ_LOW    | RO     | 25 MHz is Low frequency limit for the current mode, value is 19h.                                        |

| FRQ_HIGH   | RO     | 85 MHz is High frequency limit for the current mode, value is 55h.                                       |

| PD         | RW     | Power down mode, default = 1.                                                                            |

|            |        | 0 - power down only the LVDS drivers. Output of this device will be in TRI-STATE                         |

|            |        | mode. Other circuitry are still active.                                                                  |

|            |        | 1 - normal operation.                                                                                    |

| EDGE       | RW     | Edge select (same function as R_FB pin), default = 1.                                                    |

|            |        | 0 - input data is rising edge latched (rising edge latched first in 12-bit and two 12-bit mode).         |

|            |        | 1 - input data is falling edge latched (falling edge latched first in 12-bit and two 12-bit mode).       |

| BSEL       | RW     | Input bus select (same as DUAL pin), default = 0.                                                        |

|            |        | 0 - one 12-bit bus.                                                                                      |

|            |        | 1 - two 12-bit bus.                                                                                      |

| DSEL       | RW     | Dual level clock select (same function as DSEL pin), default = 1.                                        |

|            |        | 0 - input clock is differential.                                                                         |

|            |        | 1 - input clock is single-ended (up to 65MHz). CLKINM and V <sub>REF</sub> pin are internally connected. |

| HEN        | RW     | Horizontal sync enable, default = 1.                                                                     |

|            |        | 0 - HSYNC input is transmitted as fixed LOW.                                                             |

|            |        | 1 - HSYNC input is transmitted as it is.                                                                 |

| VEN        | RW     | Vertical sync enable, default = 1.                                                                       |

|            |        | 0 - VSYNC input is transmitted as fixed LOW.                                                             |

|            |        | 1 - VSYNC input is transmitted as it is.                                                                 |

| MDI        | RW     | Monitor Detect Interrupt, default = 1.                                                                   |

|            |        | 0 - Detection signal has changed logical level (write "1" to this bit to clear).                         |

|            |        | 1 - Detection signal has not changed state.                                                              |

| *HTPLG     | RO     | Feature not implemented.                                                                                 |

| RSEN       | RO     | This bit is a "1 " if a powered on receiver is connected to the transmitter outputs, " 0                 |

|            |        | otherwsie. This function is only available for use in DC-coupled systems. Default=0.                     |

| TSEL       | RW     | Interrupt generation method, default=0.                                                                  |

|            |        | 0 - Interrupt bit (MDI) is generated by monitoring RSEN.                                                 |

|            |        | 1 - Interrupt bit (MDI) is generated by monitoring HTPLG.                                                |

| MSEL [2:0] | RW     | Select source for the MSEN output pin. Default valus is 001.                                             |

| - [1       |        | 000 - Force MSEN output HIGH (disabled).                                                                 |

|            |        | 001 - Output the value of MDI bit (interrupt). This is default.                                          |

|            |        | 010 - Output the value of RSEN bit (receiver detect).                                                    |

|            |        | 011 - Output the value of HTPLG bit (hot plug detect).                                                   |

|            |        | 1xx - Reserved.                                                                                          |

| VLOW       | RO     | This bit is an 1 if the VREF signal indicates low swing inputs. Default=1.                               |

|            |        | It is a 0 if VREF indicates high swing inputs.                                                           |

|            |        | problem writer indicates riigir swirig inputs.                                                           |

| CTL [3:1]  | RW     | General purpose inputs.                                                                                  |

15

#### Two-Wire Serial Communication Interface Description (Continued)

TABLE 4. Register Field Definitions(' \* " = features not implemented on DS90C387R) (Continued)

| Field       | Access | Description              |  |  |

|-------------|--------|--------------------------|--|--|

| *VDJK [7:0] | RW     | Reserved.                |  |  |

| *DK [3:1]   | RW     | Feature not implemented. |  |  |

| *DKEN       | RW     | Feature not implemented. |  |  |

#### Communicating with the DS90C387R through Registers

There are 31 data registers in the DS90C387R, and can be accessed through sixteen register addresses. All registers are predefined as read only, or read and write. The device will always attempt to detect if a LCD panel/monitor is connected.

A **Write** to the DS90C387R will always include the slave address byte, data register address byte, a data byte.

Reading the DS90C387R can take place either of two ways:

- If the location latched in the data register addresses is correct, then the read can simply consist of a slave address byte, followed by retrieving the data byte.

- If the data register address needs to be set, then a slave address byte, data register address will be sent first, then the master will repeat start, send the slave address

byte and data byte to accomplish a read.

The data byte has the most significant bit first. At the end of a read, the DS90C387R can accept either Acknowledge or No Acknowledge from the Master (No Acknowledge is typically used as a signal for the slave that the Master has read its last byte).

# Two-Wire Serial Communication Interface for Slave

The DS90C387R slave state machine does not require an internal clock and it supports only byte read and write. Page mode is not supported. The 7-bit binary address is "0111A $_2$ A $_1$ A $_0$ ", where A $_2$ A $_1$ A $_0$  are pin programmable to "1" or "0" and the "0111" is hardwired internally.

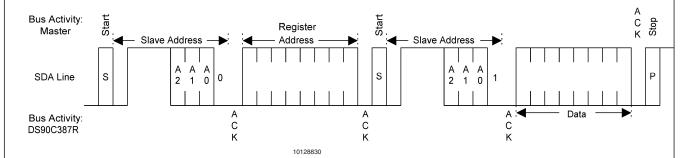

FIGURE 14. Byte Read

The master must generate a "Start" by sending the 7-bit slave address plus a 0 first, and wait for acknowledge from DS90C387R. When DS90C387R acknowledges (the 1st ACK) that the master is calling, the master then sends the data register address byte and waits for acknowledge from the slave. When the slave acknowledges (the 2nd ACK), the master repeats the "Start" by sending the 7-bit slave

address plus a 1 (indicating that READ operation is in progress) and waits for acknowledge from DS90C387R. After the slave responds (the 3rd ACK), the slave sends the data to the bus and waits for acknowledge from the master. When the master acknowledges (the 4th ACK), it generates a "Stop". This completes the "READ".

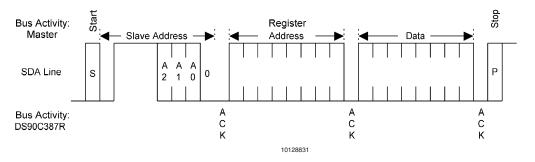

FIGURE 15. Byte Write

# Two-Wire Serial Communication Interface for Slave (Continued)

The master must generate a "Start", by sending the 7-bit slave address plus a 0 and wait for acknowledge from DS90C387R. When DS90C387R acknowledges (the 1st

ACK) that the master is calling, the master then sends the data register address byte and waits for acknowledge from the slave. When the slave acknowledges (the 2nd ACK), the master sends the data byte and wait for acknowledge from the slave. When the slave acknowledges (the 3rd ACK), the master generates a "Stop". This completes the "WRITE".

# **LVDS Interface**

TABLE 5. LVDS data bit naming convention

| Х   | Υ   | Z     | Description                                     |

|-----|-----|-------|-------------------------------------------------|

| X=R |     |       | Red                                             |

| X=G |     |       | Green                                           |

| X=B |     |       | Blue                                            |

|     | Y=1 |       | Odd (First) Pixel                               |

|     | Y=2 |       | Even (Second) Pixel                             |

|     |     | Z=0-7 | LVDS bit number (not VGA controller LSB to MSB) |

Note 15: For a 48-bit dual pixel application - LSB (Less Significant Bit) = R16,G16,B16,R26,G26,B26 and MSB (Most Significant Bit) = R15,G15,B15,R25,G25,B25.

TABLE 6. 12-bit (two data per clock) data mapping (DUAL=GND, BAL=Vcc/GND, only A0-A3 are used).

| VGA - 1            | FT Data | Transmitter input pin names | Receiver output pin names | TFT Panel Data |        |  |

|--------------------|---------|-----------------------------|---------------------------|----------------|--------|--|

| Signals Color Bits |         |                             |                           | Signals        |        |  |

|                    | 24-bit  | DS90C387R                   | DS90CF388                 | 18-bit         | 24-bit |  |

| LSB                | R0      | E2-D4                       | R16                       |                | R0     |  |

|                    | R1      | E2-D5                       | R17                       |                | R1     |  |

|                    | R2      | E2-D6                       | R10                       | R0             | R2     |  |

|                    | R3      | E2-D7                       | R11                       | R1             | R3     |  |

|                    | R4      | E2-D8                       | R12                       | R2             | R4     |  |

|                    | R5      | E2-D9                       | R13                       | R3             | R5     |  |

|                    | R6      | E2-D10                      | R14                       | R4             | R6     |  |

| MSB                | R7      | E2-D11                      | R15                       | R5             | R7     |  |

| LSB                | G0      | E1-D8                       | G16                       |                | G0     |  |

|                    | G1      | E1-D9                       | G17                       |                | G1     |  |

|                    | G2      | E1-D10                      | G10                       | G0             | G2     |  |

|                    | G3      | E1-D11                      | G11                       | G1             | G3     |  |

|                    | G4      | E2-D0                       | G12                       | G2             | G4     |  |

|                    | G5      | E2-D1                       | G13                       | G3             | G5     |  |

|                    | G6      | E2-D2                       | G14                       | G4             | G6     |  |

| MSB                | G7      | E2-D3                       | G15                       | G5             | G7     |  |

| LSB                | В0      | E1-D0                       | B16                       |                | B0     |  |

|                    | B1      | E1-D1                       | B17                       |                | B1     |  |

|                    | B2      | E1-D2                       | B10                       | B0             | B2     |  |

|                    | В3      | E1-D3                       | B11                       | B1             | B3     |  |

|                    | B4      | E1-D4                       | B12                       | B2             | B4     |  |

|                    | B5      | E1-D5                       | B13                       | В3             | B5     |  |

|                    | B6      | E1-D6                       | B14                       | B4             | B6     |  |

| MSB                | B7      | E1-D7                       | B15                       | B5             | B7     |  |

TABLE 7. Two 12-bit (two data per clock) data mapping (DUAL=Vcc, BAL=Vcc/GND, A0-A7 are used).

| VGA - TFT Data<br>Signals Color Bits |        | Transmitter input pin names | Receiver output pin names | TFT Panel Data<br>Signals |          |  |

|--------------------------------------|--------|-----------------------------|---------------------------|---------------------------|----------|--|

|                                      | 24-bit | DS90C387R                   | DS90CF388                 | 18-bit 24-                |          |  |

|                                      |        | Port 1-Primary (odd         | pixel/first RGB pixel)    | I.                        |          |  |

| LSB                                  | R0     | E2-D4                       | R16                       |                           | R0       |  |

|                                      | R1     | E2-D5                       | R17                       |                           | R1       |  |

|                                      | R2     | E2-D6                       | R10                       | R0                        | R2       |  |

|                                      | R3     | E2-D7                       | R11                       | R1                        | R3       |  |

|                                      | R4     | E2-D8                       | R12                       | R2                        | R4       |  |

|                                      | R5     | E2-D9                       | R13                       | R3                        | R5       |  |

|                                      | R6     | E2-D10                      | R14                       | R4                        | R6       |  |

| MSB                                  | R7     | E2-D11                      | R15                       | R5                        | R7       |  |

| LSB                                  | G0     | E1-D8                       | G16                       |                           | G0       |  |

|                                      | G1     | E1-D9                       | G17                       |                           | G1       |  |

|                                      | G2     | E1-D10                      | G10                       | G0                        | G2       |  |

|                                      | G3     | E1-D11                      | G11                       | G1                        | G3       |  |

|                                      | G4     | E2-D0                       | G12                       | G2                        | G4       |  |

|                                      | G5     | E2-D1                       | G13                       | G3                        | G5       |  |

|                                      | G6     | E2-D2                       | G14                       | G4                        | G6       |  |

| MSB                                  | G7     | E2-D3                       | G15                       | G5                        | G7       |  |

| LSB                                  | B0     | E1-D0                       | B16                       |                           | B0       |  |

| LOD                                  | B1     | E1-D1                       | B17                       |                           | B1       |  |

|                                      | B2     | E1-D2                       | B10                       | B0                        | B2       |  |

|                                      | B3     | E1-D2                       | B11                       | B1                        | B3       |  |

|                                      | B4     | E1-D3                       | B12                       | B2                        | B4       |  |

|                                      | B5     | E1-D4                       | B13                       | B3                        | B5       |  |

|                                      | B6     | E1-D5                       | B14                       | B4                        | B6       |  |

| MSB                                  | B7     | E1-D6                       | B15                       | B5                        | B7       |  |

| IVIOD                                | D/     |                             | pixel/second RGB pixel)   | <br>                      | D/       |  |

| LSB                                  | R0     | E2-D16                      | R26                       |                           | DO.      |  |

| LOD                                  | R1     | E2-D17                      | R27                       |                           | R0<br>R1 |  |

|                                      | R2     | E2-D17                      | R20                       | R0                        | R2       |  |

|                                      |        |                             |                           |                           |          |  |

|                                      | R3     | E2-D19                      | R21                       | R1                        | R3       |  |

|                                      | R4     | E2-D20                      | R22                       | R2                        | R4       |  |

|                                      | R5     | E2-D21                      | R23                       | R3                        | R5       |  |

| MCD                                  | R6     | E2-D22                      | R24                       | R4                        | R6       |  |

| MSB                                  | R7     | E2-D23                      | R25                       | R5                        | R7       |  |

| LSB                                  | G0     | E1-D20                      | G26                       |                           | G0       |  |

|                                      | G1     | E1-D21                      | G27                       |                           | G1       |  |

|                                      | G2     | E1-D22                      | G20                       | G0                        | G2       |  |

|                                      | G3     | E1-D23                      | G21                       | G1                        | G3       |  |

|                                      | G4     | E2-D12                      | G22                       | G2                        | G4       |  |

|                                      | G5     | E2-D13                      | G23                       | G3                        | G5       |  |

| MCD                                  | G6     | E2-D14                      | G24                       | G4                        | G6       |  |

| MSB                                  | G7     | E2-D15                      | G25                       | G5                        | G7       |  |

| LSB                                  | B0     | E1-D12                      | B26                       |                           | B0       |  |

|                                      | B1     | E1-D13                      | B27                       | 5.0                       | B1       |  |

|                                      | B2     | E1-D14                      | B20                       | B0                        | B2       |  |

|                                      | B3     | E1-D15                      | B21                       | B1                        | B3       |  |

TABLE 7. Two 12-bit (two data per clock) data mapping (DUAL=Vcc, BAL=Vcc/GND, A0-A7 are used). (Continued)

| VGA - TFT Data<br>Signals Color Bits |    | Transmitter input pin names | Receiver output pin names | TFT Par<br>Sigr | nel Data<br>nals |

|--------------------------------------|----|-----------------------------|---------------------------|-----------------|------------------|

| B4                                   |    | E1-D16                      | B22                       | B2              | B4               |

|                                      | B5 | E1-D17                      | B23                       | В3              | B5               |

|                                      | B6 | E1-D18                      | B24                       | B4              | B6               |

| MSB                                  | B7 | E1-D19                      | B25                       | B5              | B7               |

10128833

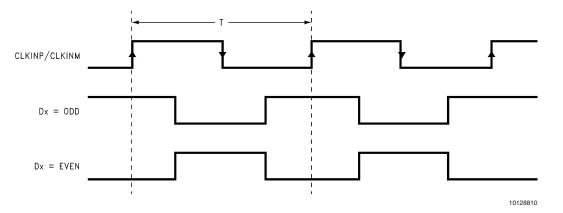

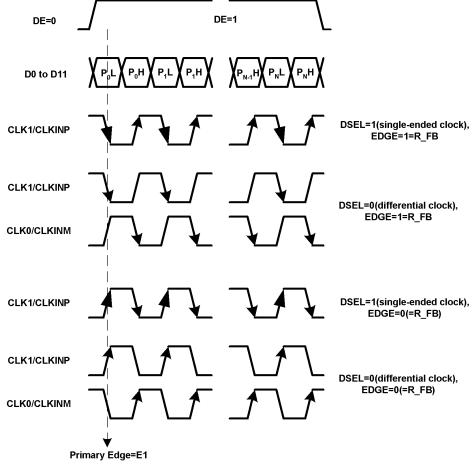

FIGURE 16. How ds90c387r latch data

Note 16: The lower half of the pixel is latched by the primary clock edge E1.

Note 17: Above figure only valids when R\_FDE = HIGH, DE signal from GUI is active HIGH.

Note 18: D0 to D11 are clocked at the crossing point of CLKOUT+ and CLKOUT- when differential clock input is applied, DSEL = 0.

Note 19: Single-ended clock is not recommended for operation above 65MHz.

TABLE 8. 12-bit (two data per clock) input application data mapping with GMCH.

|          | P0    |       | Р     | P1    |       | P2    |

|----------|-------|-------|-------|-------|-------|-------|

|          | P0L   | P0H   | P1L   | P1H   | P2L   | P2H   |

| Pin Name | Low   | High  | Low   | High  | Low   | High  |

| D11      | G0[3] | R0[7] | G1[3] | R1[7] | G2[3] | R2[7] |

| D10      | G0[2] | R0[6] | G1[2] | R1[6] | G2[2] | R2[6] |

| D9       | G0[1] | R0[5] | G1[1] | R1[5] | G2[1] | R2[5] |

| D8       | G0[0] | R0[4] | G1[0] | R1[4] | G2[0] | R2[4] |

| D7       | B0[7] | R0[3] | B1[7] | R1[3] | B2[7] | R2[3] |

| D6       | B0[6] | R0[2] | B1[6] | R1[2] | B2[6] | R2[2] |

| D5       | B0[5] | R0[1] | B1[5] | R1[1] | B2[5] | R2[1] |

| D4       | B0[4] | R0[0] | B1[4] | R1[0] | B2[4] | R2[0] |

| D3       | B0[3] | G0[7] | B1[3] | G1[7] | B2[3] | G2[7] |

| D2       | B0[2] | G0[6] | B1[2] | G1[6] | B2[2] | G2[6] |

| D1       | B0[1] | G0[5] | B1[1] | G1[5] | B2[1] | G2[5] |

| D0       | B0[0] | G0[4] | B1[0] | G1[4] | B2[0] | G2[4] |

Note 20: Color notation: R = RED, G = GREEN, B = BLUE. Note 21: Bit significance within a color: [7:0] = [MSB:LSB].

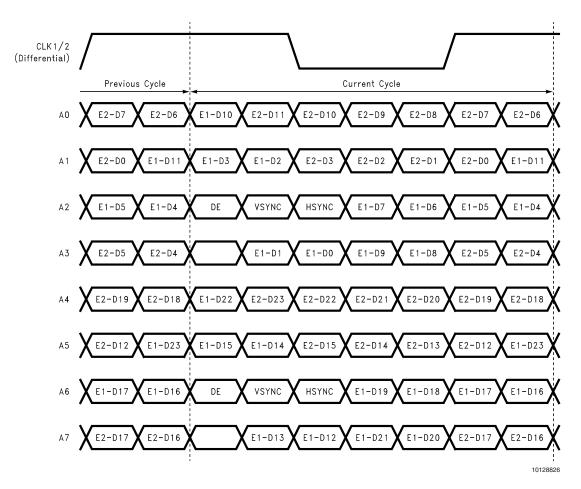

FIGURE 17. TTL Data Inputs Mapped to LVDS Outputs

Non-DC Balanced Mode (Backward Compatible, BAL=Low, A0 to A3 for Port1, A4 to A7 for Port2)

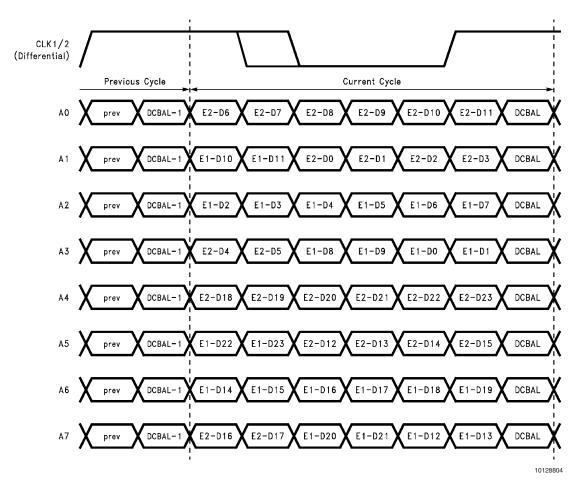

FIGURE 18. 48 Parallel TTL Data Inputs Mapped to LVDS Outputs DC Balanced Mode (Data Enabled, BAL=High, A0 to A3 for Port1, A4 to A7 for Port2)

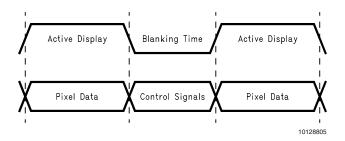

FIGURE 19. Control Signals Transmitted During Blanking in DC-Balance mode

TABLE 9. Control Signals Transmitted During Blanking in DC-Balance mode

| Control Signal | Signal Level | Channel | Pattern            |

|----------------|--------------|---------|--------------------|

| DE             | HIGH         | CLK1    | 1111000 or 1110000 |

|                | LOW          |         | 1111100 or 1100000 |

| HSYNC          | HIGH         | A0      | 1100000 or 1111100 |

|                | LOW          |         | 1110000 or 1111000 |

| VSYNC          | HIGH         | A1      | 1100000 or 1111100 |

|                | LOW          |         | 1110000 or 1111000 |

Note 22: The control signal during blanking shown above is for R\_FDE=High, when R\_FDE=Low, low/high patterns are reversed only for DE signal.

23

### **Applications Information**

How to configure the DS90C387R to work with DS90CF384/DS90CF384A/DS90CF386 or DS90CF388 for most common application:

1. To configure for single pixel application using the DS90C387R to interface with GMCH host, please see table below for reference pin connection and configuration. Due to the implementation differences among various GMCH vendors, the table is using the GMCH vendor located in Santa Clara, California, USA as an example. A two-wire serial communication interface based EEPROM containing EDID 128 bytes LCD timing information may be required depending on device driver implementation.

| From DS90C387R | To GMCH        |  |  |

|----------------|----------------|--|--|

| data signal    | connection     |  |  |

| D0             | D0             |  |  |

| D1             | D1             |  |  |

| D2             | D2             |  |  |

| D3             | D3             |  |  |

| D4             | D4             |  |  |

| D5             | D5             |  |  |

| D6             | D6             |  |  |

| D7             | D7             |  |  |

| D8             | D8             |  |  |

| D9             | D9             |  |  |

| D10            | D10            |  |  |

| D11            | D11            |  |  |

| CLKINP         | CLK1           |  |  |

| CLKINM         | CLK0           |  |  |

| DE             | BLANK          |  |  |

| HSYNC          | HSYNC          |  |  |

| VSYNC          | VSYHC          |  |  |

| configuration  | for other pins |  |  |

| DDRENI2Cclk    | I2CCLK         |  |  |

| DSELI2Cdat     | I2CDATA        |  |  |

| A0             | GND            |  |  |

| A1             | GND            |  |  |

| A2             | GND            |  |  |

| PLLSEL         | Vcc            |  |  |

| DUAL           | GND            |  |  |

| BAL            | GND            |  |  |

| D12 to D23     | No connect     |  |  |

| RESERVED1      | GND            |  |  |

| RESERVED2      | GND            |  |  |

| RESERVED3      | No connect     |  |  |

| RESERVED4      | GND            |  |  |

| RESERVED5      | GND            |  |  |

| RESERVED6      | GND            |  |  |

| RESERVED7      | GND            |  |  |

| RESERVED8      | GND            |  |  |

| RESERVED9      | GND            |  |  |

| TST1           | Vcc            |  |  |

| TST2           | No connect     |  |  |

| VREF | VREF |

|------|------|

| MSEN | INT# |

2. To configure for single pixel application using the DS90C387R with single DS90CF384 or DS90CF384A or DS90CF386 LVDS based LCD panel or monitor, the "DUAL" pin must be set to Gnd (single RGB), and "BAL" pin must be set to Gnd to disable the feature for DS90CF384/DS90CF386 doesn't support DC balance function. For cable length more than two meters, pre-emphasis feature is recommended. Please see table below for reference pin connection.

| From DS90C387R Output                 | To LVDS based LCD          |  |  |

|---------------------------------------|----------------------------|--|--|

| Pins                                  | monitor                    |  |  |

| data signal                           | data signal connection     |  |  |

| A0M                                   | RxIN0-                     |  |  |

| A0P                                   | RxIN0+                     |  |  |

| A1M                                   | RxIN1-                     |  |  |

| A1P                                   | RxIN1+                     |  |  |

| A2M                                   | RxIN2-                     |  |  |

| A2P                                   | RxIN2+                     |  |  |

| CLK1M                                 | RxCLKIN0-                  |  |  |

| CLK1P                                 | RxCLKIN0+                  |  |  |

| A3M(valid for 8-bit LCD               | RxIN3-(valid for 8-bit LCD |  |  |

| only; no connect for 6-bit            | only; no connect for 6-bit |  |  |

| LCD)                                  | LCD)                       |  |  |

| A3P(valid for 8-bit LCD               | RxIN3+(valid for 8-bit LCD |  |  |

| only; no connect for 6-bit            | only; no connect for 6-bit |  |  |

| LCD)                                  | LCD)                       |  |  |

| A4M                                   | No connect                 |  |  |

| A4P                                   | No connect                 |  |  |

| A5M                                   | No connect                 |  |  |

| A5P                                   | No connect                 |  |  |