April 2006

# DS91D176/DS91C176 Multipoint-LVDS (M-LVDS) Transceivers

#### **General Description**

The DS91C176 and DS91D176 are high-speed M-LVDS differential transceivers designed for multipoint applications with multiple drivers or receivers. Multipoint LVDS (M-LVDS) is a new bus interface standard (TIA/EIA-899) based on LVDS but including several enhancements to improve multipoint performance. M-LVDS devices have superior drive capability and can support up to 32 loads. Along with increased drive, M-LVDS devices are required to have a controlled edge rate to minimize reflections and EMI. The 1 nSec minimum edge rate is tolerant of stub lengths up to 2 inches in length. M-LVDS devices also have a very large common mode range for additional noise margin in heavily loaded and noisy backplane environments.

The DS91C176/DS91D176 are half-duplex transceivers that accept LVTTL/LVCMOS signals at the driver inputs and convert them to differential M-LVDS signal levels. The receiver inputs accept low voltage differential signals (LVDS,

B-LVDS, M-LVDS, LV-PECL) and convert them to 3V LVC-MOS signals. The DS91C176 receiver contains an M-LVDS type 2 failsafe circuit with an internal 100 mV offset that provides a LOW output for both short and open input conditions.

#### **Features**

- Meets TIA/EIA-899 M-LVDS Standard

- Capable of driving 32 LVDS loads

- Controlled Edge Rates Tolerant to Stubs

- Wide Common Mode for Increased Noise Immunity

- DS91C176 has type 2 Fail-safe support

- Up to 200 Mbps operation

- Industrial temperature range

- Single 3.3V supply

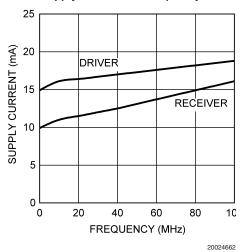

- 8-lead SOIC package

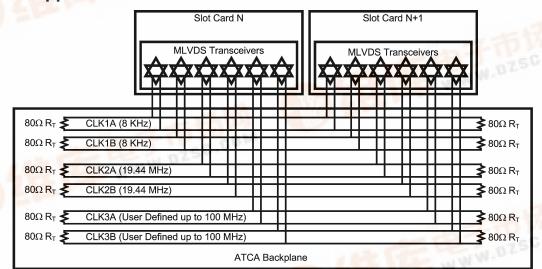

# Typical Application in AdvancedTCA Clock Distribution

20024630

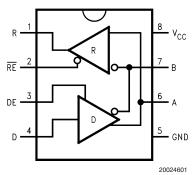

# **Connection and Logic Diagram**

Top View

Order Number DS91D176TMA, DS91C176TMA

See NS Package Number M08A

# **Ordering Information**

| Order Number Function |                                     | Package Type |

|-----------------------|-------------------------------------|--------------|

| DS91D176TMA           | Data (0V threshold receiver)        | SOIC/M08A    |

| DS91C176TMA           | Control (offset fail-safe receiver) | SOIC/M08A    |

#### **Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

Supply Voltage,  $V_{\rm CC}$ -0.3V to +4V Control Input Voltages -0.3V to  $(V_{CC} + 0.3V)$ Driver Input Voltage -0.3V to  $(V_{CC} + 0.3V)$ -1.8V to +4.1V**Driver Output Voltages** Receiver Input Voltages -1.8V to +4.1V Receiver Output Voltage -0.3V to  $(V_{CC} + 0.3V)$ Maximum Package Power Dissipation at +25°C SOIC Package 833 mW Derate SOIC Package 6.67 mW/°C above +25°C Thermal Resistance  $\theta_{\mathsf{JA}}$ 150°C/W 63°C/W  $\theta_{JC}$ Maximum Junction Temperature 150°C ESD Ratings:  $(HBM 1.5kΩ, 100pF) \qquad \qquad \geq 8 \text{ kV}$   $(EIAJ 0Ω, 200pF) \qquad \qquad \geq 1000 \text{ V}$   $(CDM 0Ω, 0pF) \qquad \qquad \geq 250 \text{ V}$

# Recommended Operating Conditions

|                                            | Min  | Тур | Max      | Units |

|--------------------------------------------|------|-----|----------|-------|

| Supply Voltage, V <sub>CC</sub>            | 3.0  | 3.3 | 3.6      | V     |

| Voltage at Any Bus Terminal                | -1.4 |     | +3.8     | V     |

| (Separate or Common-Mode)                  |      |     |          |       |

| Differential Input Voltage V <sub>ID</sub> |      |     | 2.4      | V     |

| LVTTL Input Voltage High $V_{\rm IH}$      | 2.0  |     | $V_{CC}$ | V     |

| LVTTL Input Voltage Low V <sub>IL</sub>    | 0    |     | 8.0      | V     |

| Operating Free Air                         |      |     |          |       |

| Temperature T <sub>A</sub>                 | -40  | +25 | +85      | °C    |

#### **Electrical Characteristics**

Storage Temperature Range

(Soldering, 4 seconds)

Lead Temperature

Over recommended operating supply and temperature ranges unless otherwise specified. (Notes 2, 3, 4, 8)

260°C

-65°C to +150°C

| Symbol                | Parameter Conditions                                 |                                                | Min    | Тур                 | Max  | Units              |      |

|-----------------------|------------------------------------------------------|------------------------------------------------|--------|---------------------|------|--------------------|------|

| M-LVDS D              | river                                                |                                                |        |                     |      |                    |      |

| V <sub>AB</sub>       | Differential output voltage magnitude                | $R_L = 50\Omega$ , $C_L = 5pF$                 |        | 480                 |      | 650                | mV   |

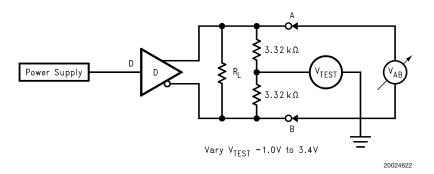

| $\Delta V_{AB}$       | Change in differential output voltage magnitude      | Figure 1 and Figure 3                          |        | -50                 | 0    | +50                | mV   |

|                       | between logic states                                 |                                                |        | -50                 | U    | +50                | IIIV |

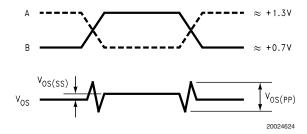

| $V_{OS(SS)}$          | Steady-state common-mode output voltage              | $R_L = 50\Omega$ , $C_L = 5pF$                 |        | 0.3                 | 1.8  | 2.1                | V    |

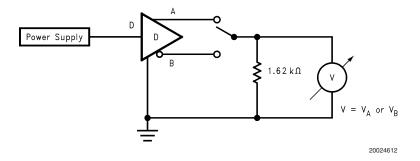

| $ \Delta V_{OS(SS)} $ | Change in steady-state common-mode output            | Figure 1 and Figure 2                          |        | 0                   |      | +50                | mV   |

|                       | voltage between logic states                         |                                                |        | 0                   |      | +30                | 1117 |

| $V_{OS(PP)}$          | Peak-to-peak common-mode output voltage              | (V <sub>OS(PP)</sub> @ 500KHz clock            | k)     |                     | 135  |                    | mV   |

| $V_{A(OC)}$           | Maximum steady-state open-circuit output voltage     | Figure 4                                       |        | 0                   |      | 2.4                | V    |

| $V_{B(OC)}$           | Maximum steady-state open-circuit output voltage     |                                                |        | 0                   |      | 2.4                | V    |

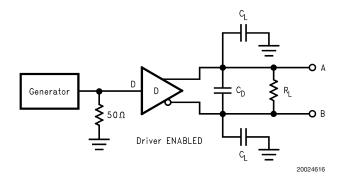

| $V_{P(H)}$            | Voltage overshoot, low-to-high level output          | $R_L = 50\Omega$ , $C_L = 5pF$ , $C_D = 0.5pF$ |        |                     |      | 1.2V <sub>SS</sub> | V    |

| $V_{P(L)}$            | Voltage overshoot, high-to-low level output          | Figure 6 and Figure 7 (Note 9)                 |        | -0.2V <sub>SS</sub> |      |                    | V    |

| I <sub>IH</sub>       | High-level input current (LVTTL inputs)              | V <sub>IH</sub> = 2.0V                         |        | -15                 |      | 15                 | μΑ   |

| I <sub>IL</sub>       | Low-level input current (LVTTL inputs)               | $V_{IL} = 0.8V$                                |        | -15                 |      | 15                 | μΑ   |

| $V_{IKL}$             | Input Clamp Voltage (LVTTL inputs)                   | I <sub>IN</sub> = -18mA                        |        | -1.5                |      |                    | V    |

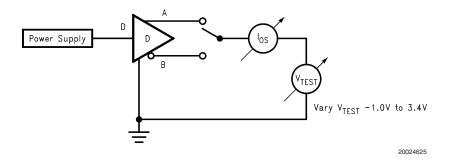

| Ios                   | Differential short-circuit output current            | Figure 5                                       |        | -43                 |      | 43                 | mA   |

| M-LVDS R              | eceiver                                              |                                                |        |                     |      |                    |      |

| V <sub>IT+</sub>      | Positive-going differential input voltage threshold  | See Function Tables                            | Type 1 |                     | 20   | 50                 | mV   |

|                       |                                                      |                                                | Type 2 |                     | 94   | 150                | mV   |

| V <sub>IT-</sub>      | Negative-going differential input voltage threshold  | See Function Tables                            | Type 1 | -50                 | 20   |                    | mV   |

|                       |                                                      |                                                | Type 2 | 50                  | 94   |                    | mV   |

| V <sub>OH</sub>       | High-level output voltage (LVTTL output)             | I <sub>OH</sub> = -8mA                         |        | 2.4                 | 2.7  |                    | V    |

| V <sub>OL</sub>       | Low-level output voltage (LVTTL output)              | I <sub>OL</sub> = 8mA                          |        |                     | 0.28 | 0.4                | V    |

| l <sub>OZ</sub>       | TRI-STATE output current                             | V <sub>O</sub> = 0V or 3.6V                    |        | -10                 |      | 10                 | μΑ   |

| I <sub>OSR</sub>      | Short-circuit receiver output current (LVTTL output) | V <sub>O</sub> = 0V                            |        |                     | -48  | -90                | mA   |

**Electrical Characteristics** (Continued)

Over recommended operating supply and temperature ranges unless otherwise specified. (Notes 2, 3, 4, 8)

| Symbol               | Parameter                                                                                            | Conditions                                                       | Min | Тур | Max  | Units |

|----------------------|------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|-----|-----|------|-------|

| M-LVDS E             | Bus (Input and Output) Pins                                                                          |                                                                  |     |     |      |       |

| I <sub>A</sub>       | Transceiver input/output current                                                                     | $V_A = 3.8V, V_B = 1.2V$                                         |     |     | 32   | μA    |

|                      |                                                                                                      | $V_A = 0V \text{ or } 2.4V, V_B = 1.2V$                          | -20 |     | +20  | μA    |

|                      |                                                                                                      | $V_A = -1.4V, V_B = 1.2V$                                        | -32 |     |      | μΑ    |

| I <sub>B</sub>       | Transceiver input/output current                                                                     | $V_B = 3.8V, V_A = 1.2V$                                         |     |     | 32   | μΑ    |

|                      |                                                                                                      | $V_B = 0V \text{ or } 2.4V, V_A = 1.2V$                          | -20 |     | +20  | μA    |

|                      |                                                                                                      | $V_B = -1.4V, V_A = 1.2V$                                        | -32 |     |      | μΑ    |

| I <sub>AB</sub>      | Transceiver input/output differential current $(I_A - I_B)$                                          | $V_A = V_B, -1.4V \le V \le 3.8V$                                | -4  |     | +4   | μA    |

| I <sub>A(OFF)</sub>  | Transceiver input/output power-off current                                                           | $V_A = 3.8V, V_B = 1.2V,$<br>DE = $V_{CC} = 1.5V$                |     |     | 32   | μA    |

|                      |                                                                                                      | $V_A = 0V \text{ or } 2.4V, V_B = 1.2V,$<br>DE = $V_{CC} = 1.5V$ | -20 |     | +20  | μΑ    |

|                      |                                                                                                      | $V_A = -1.4V, V_B = 1.2V,$<br>DE = $V_{CC} = 1.5V$               | -32 |     |      | μA    |

| I <sub>B(OFF)</sub>  | Transceiver input/output power-off current                                                           | $V_B = 3.8V, V_A = 1.2V,$<br>DE = $V_{CC} = 1.5V$                |     |     | 32   | μA    |

|                      |                                                                                                      | $V_B = 0V \text{ or } 2.4V, V_A = 1.2V,$<br>DE = $V_{CC} = 1.5V$ | -20 |     | +20  | μA    |

|                      |                                                                                                      | $V_B = -1.4V, V_A = 1.2V,$<br>DE = $V_{CC} = 1.5V$               | -32 |     |      | μA    |

| I <sub>AB(OFF)</sub> | Transceiver input/output power-off differential current (I <sub>A(OFF)</sub> - I <sub>B(OFF)</sub> ) | $V_A = V_B, -1.4V \le V \le 3.8V,$<br>$V_{CC} = 1.5V, DE = 1.5V$ | -4  |     | +4   | μA    |

| C <sub>A</sub>       | Transceiver input/output capacitance                                                                 | V <sub>CC</sub> = OPEN                                           |     | 9   |      | pF    |

| Св                   | Transceiver input/output capacitance                                                                 | 1                                                                |     | 9   |      | pF    |

| C <sub>AB</sub>      | Transceiver input/output differential capacitance                                                    | 1                                                                |     | 5.7 |      | pF    |

| C <sub>A/B</sub>     | Transceiver input/output capacitance balance $(C_A/C_B)$                                             |                                                                  |     | 1.0 |      |       |

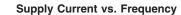

| SUPPLY (             | CURRENT (V <sub>CC</sub> )                                                                           |                                                                  |     |     |      | 1     |

| I <sub>CCD</sub>     | Driver Supply Current                                                                                | $R_L = 50\Omega$ , $DE = V_{CC}$ , $\overline{RE} = V_{CC}$      |     | 20  | 29.5 | mA    |

| I <sub>CCZ</sub>     | TRI-STATE Supply Current                                                                             | DE = GND, RE = V <sub>CC</sub>                                   |     | 6   | 9.0  | mA    |

| I <sub>CCR</sub>     | Receiver Supply Current                                                                              | DE = GND, RE = GND                                               |     | 14  | 18.5 | mA    |

#### **Switching Characteristics**

Over recommended operating supply and temperature ranges unless otherwise specified. (Notes 3, 8)

| Symbol                                  | Parameter                                                        | Conditions                       | Min | Тур | Max | Units |

|-----------------------------------------|------------------------------------------------------------------|----------------------------------|-----|-----|-----|-------|

| DRIVER AC S                             | PECIFICATION                                                     |                                  | •   |     | •   |       |

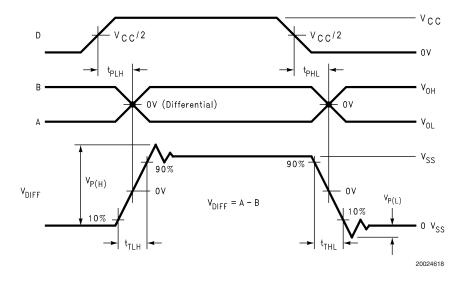

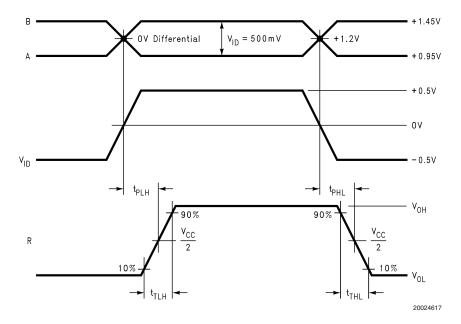

| t <sub>PLH</sub>                        | Differential Propagation Delay Low to High                       | $R_L = 50\Omega$ , $C_L = 5$ pF, | 1.3 | 3.4 | 5.5 | ns    |

| t <sub>PHL</sub>                        | Differential Propagation Delay High to Low                       | $C_{\rm D} = 0.5  \rm pF$        | 1.3 | 3.1 | 5.5 | ns    |

| t <sub>SKD1</sub> (t <sub>sk(p)</sub> ) | Pulse Skew It <sub>PLHD</sub> – t <sub>PHLD</sub> I (Notes 5, 9) | Figure 6 and Figure 7            |     | 300 | 420 | ps    |

| t <sub>SKD3</sub>                       | Part-to-Part Skew (Notes 6, 9)                                   |                                  |     |     | 2.2 | ps    |

| t <sub>TLH</sub> (t <sub>r</sub> )      | Rise Time (Note 9)                                               |                                  | 1.0 | 1.8 | 3.0 | ns    |

| t <sub>THL</sub> (t <sub>f</sub> )      | Fall Time (Note 9)                                               |                                  | 1.0 | 1.8 | 3.0 | ns    |

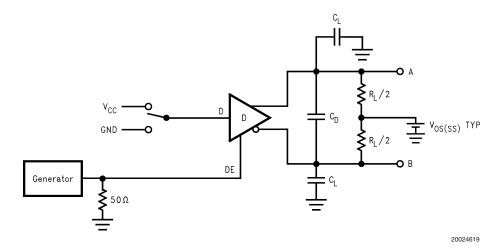

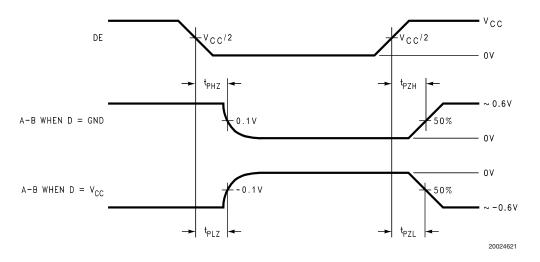

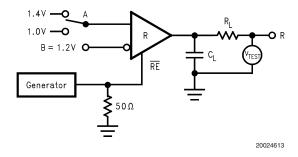

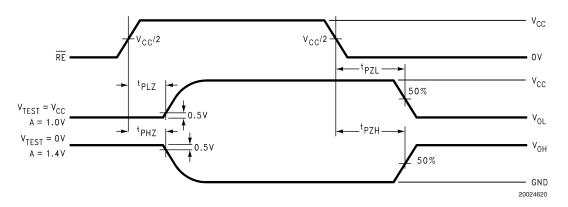

| t <sub>PZH</sub>                        | Enable Time (Z to Active High)                                   | $R_L = 50\Omega$ , $C_L = 5$ pF, |     |     | 8   | ns    |

| t <sub>PZL</sub>                        | Enable Time (Z to Active Low)                                    | $C_D = 0.5 \text{ pF}$           |     |     | 8   | ns    |

| t <sub>PLZ</sub>                        | Disable Time (Active Low to Z)                                   | Figure 8 and Figure 9            |     |     | 8   | ns    |

| t <sub>PHZ</sub>                        | Disable Time (Active High to Z)                                  |                                  |     |     | 8   | ns    |

| t <sub>JIT</sub>                        | Random Jitter, RJ (Note 9) 100 MHz Clock Pattern (Note 7)        |                                  |     | 2.5 | 5.5 | psrms |

| f <sub>MAX</sub>                        | Maximum Data Rate                                                |                                  | 200 |     |     | Mbps  |

| RECEIVER AC                             | SPECIFICATION                                                    |                                  |     |     |     |       |

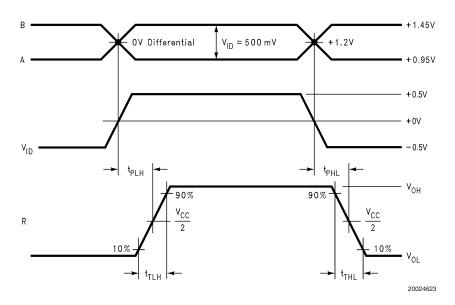

| t <sub>PLH</sub>                        | Propagation Delay Low to High                                    | $C_L = 15 pF$                    | 2.0 | 4.7 | 8.5 | ns    |

| t <sub>PHL</sub>                        | Propagation Delay High to Low                                    | Figures 10, 11 and Figure 12     | 2.0 | 5.3 | 8.5 | ns    |

| t <sub>SKD1</sub> (t <sub>sk(p)</sub> ) | Pulse Skew It <sub>PLHD</sub> – t <sub>PHLD</sub> I (Notes 5, 9) |                                  |     | 0.6 | 1.7 | ns    |

| t <sub>SKD3</sub>                       | Part-to-Part Skew (Notes 6, 9)                                   |                                  |     |     | 3.3 | ns    |

| t <sub>TLH</sub> (t <sub>r</sub> )      | Rise Time (Note 9)                                               |                                  | 0.5 | 1.2 | 2.5 | ns    |

| $t_{THL}$ $(t_f)$                       | Fall Time (Note 9)                                               |                                  | 0.5 | 1.2 | 2.5 | ns    |

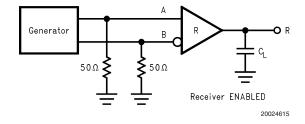

| t <sub>PZH</sub>                        | Enable Time (Z to Active High)                                   | $R_L = 500\Omega, C_L = 15 pF$   |     |     | 10  | ns    |

| t <sub>PZL</sub>                        | Enable Time (Z to Active Low)                                    | Figure 13 and Figure 14          |     |     | 10  | ns    |

| t <sub>PLZ</sub>                        | Disable Time (Active Low to Z)                                   |                                  |     |     | 10  | ns    |

| t <sub>PHZ</sub>                        | Disable Time (Active High to Z)                                  |                                  |     |     | 10  | ns    |

| f <sub>MAX</sub>                        | Maximum Data Rate                                                |                                  | 200 |     |     | Mbps  |

Note 1: "Absolute Maximum Ratings" are those beyond which the safety of the device cannot be guaranteed. They are not meant to imply that the device should be operated at these limits. The tables of "Electrical Characteristics" provide conditions for actual device operation.

- Note 2: All currents into device pins are positive; all currents out of device pins are negative. All voltages are referenced to device ground unless otherwise specified.

- Note 3: All typicals are given for  $V_{CC}=3.3V$  and  $T_A=25^{\circ}C$ .

- Note 4: The algebraic convention, in which the least positive (most negative) limit is designated as minimum, is used in this datasheet.

- Note 5: t<sub>SKD1</sub>, lt<sub>PLHD</sub> t<sub>PHLD</sub>l, is the magnitude difference in differential propagation delay time between the positive going edge and the negative going edge of the same channel

- Note 6:  $t_{SKD3}$ , Part-to-Part Skew, is defined as the difference between the minimum and maximum specified differential propagation delays. This specification applies to devices at the same  $V_{CC}$  and within 5°C of each other within the operating temperature range.

- Note 7: Stimulus and fixture Jitter has been subtracted.

- Note 8:  $C_L$  includes fixture capacitance and  $C_D$  includes probe capacitance.

- Note 9: Not production tested. Guaranteed by a statistical analysis on a sample basis at the time of characterization.

# **Test Circuits and Waveforms**

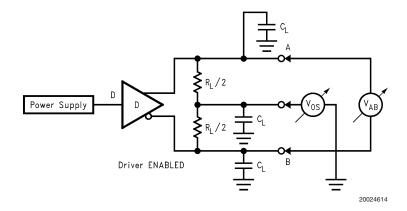

FIGURE 1. Differential Driver Test Circuit

FIGURE 2. Differential Driver Waveforms

FIGURE 3. Differential Driver Full Load Test Circuit

FIGURE 4. Differential Driver DC Open Test Circuit

FIGURE 5. Differential Driver Short-Circuit Test Circuit

FIGURE 6. Driver Propagation Delay and Transition Time Test Circuit

FIGURE 7. Driver Propagation Delays and Transition Time Waveforms

FIGURE 8. Driver TRI-STATE Delay Test Circuit

FIGURE 9. Driver TRI-STATE Delay Waveforms

FIGURE 10. Receiver Propagation Delay and Transition Time Test Circuit

FIGURE 11. Type 1 Receiver Propagation Delay and Transition Time Waveforms

FIGURE 12. Type 2 Receiver Propagation Delay and Transition Time Waveforms

FIGURE 13. Receiver TRI-STATE Delay Test Circuit

FIGURE 14. Receiver TRI-STATE Delay Waveforms

# **Function Tables**

#### DS91D176/DS91C176 Transmitting

| Inputs |      |      | Out | puts |

|--------|------|------|-----|------|

| RE     | DE   | D    | В   | Α    |

| Х      | 2.0V | 2.0V | L   | Н    |

| X      | 2.0V | 0.8V | Н   | L    |

| X      | 0.8V | Х    | Z   | Z    |

#### DS91D176 Receiving

|      | Inputs |          |   |

|------|--------|----------|---|

| RE   | DE     | A – B    | R |

| 0.8V | 0.8V   | ≥ +0.05V | Н |

| 0.8V | 0.8V   | ≤ -0.05V | L |

| 0.8V | 0.8V   | 0V       | Х |

| 2.0V | 0.8V   | Х        | Z |

X — Don't care condition

#### DS91C176 Receiving

|      | Output |          |   |

|------|--------|----------|---|

| RE   | DE     | A – B    | R |

| 0.8V | 0.8V   | ≥ +0.15V | Н |

| 0.8V | 0.8V   | ≤ +0.05V | L |

| 0.8V | 0.8V   | 0V       | L |

| 2.0V | 0.8V   | Х        | Z |

X — Don't care condition

#### DS91D176 Receiver Input Threshold Test Voltages

| Applied Voltages |                 | Resulting Differential Input<br>Voltage | Resulting Common-Mode<br>Input Voltage | Receiver<br>Output |

|------------------|-----------------|-----------------------------------------|----------------------------------------|--------------------|

| VIA              | V <sub>IB</sub> | V <sub>ID</sub>                         | V <sub>IC</sub>                        | R                  |

| 2.400V           | 0.000V          | 2.400V                                  | 1.200V                                 | Н                  |

| 0.000V           | 2.400V          | -2.400V                                 | 1.200V                                 | L                  |

| 3.800V           | 3.750V          | 0.050V                                  | 3.775V                                 | Н                  |

| 3.750V           | 3.800V          | -0.050V                                 | 3.775V                                 | L                  |

| -1.400V          | -1.350V         | -0.050V                                 | -1.375V                                | Н                  |

| -1.350V          | -1.400V         | 0.050V                                  | -1.375V                                | L                  |

#### **DS91C176 Receiver Input Threshold Test Voltages**

| Applied Voltages |                 | Resulting Differential Input<br>Voltage | Resulting Common-Mode<br>Input Voltage | Receiver<br>Output |

|------------------|-----------------|-----------------------------------------|----------------------------------------|--------------------|

| VIA              | V <sub>IB</sub> | V <sub>ID</sub>                         | V <sub>IC</sub>                        | R                  |

| 2.400V           | 0.000V          | 2.400V                                  | 1.200V                                 | Н                  |

| 0.000V           | 2.400V          | -2.400V                                 | 1.200V                                 | L                  |

| 3.800V           | 3.650V          | 0.150V                                  | 3.725V                                 | Н                  |

| 3.800V           | 3.750V          | 0.050V                                  | 3.775V                                 | L                  |

| -1.250V          | -1.400V         | 0.150V                                  | -1.325V                                | Н                  |

| -1.350V          | -1.400V         | 0.050V                                  | -1.375V                                | L                  |

H — High Level L — Low Level

X — Don't care conditionZ — High impedance state

Z — High impedance state

Z — High impedance state

H — High Level

L — Low Level

Output state assumes that the receiver is enabled (RE = L)

Output state assumes that the receiver is enabled  $(\overline{RE} = L)$

# **Pin Descriptions**

| Pin No. | Name            | Description                                                                                                                                |

|---------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | R               | Receiver output pin                                                                                                                        |

| 2       | RE              | Receiver enable pin: When $\overline{RE}$ is high, the receiver is disabled. When $\overline{RE}$ is low or open, the receiver is enabled. |

| 3       | DE              | Driver enable pin: When DE is low, the driver is disabled. When DE is high, the driver is enabled.                                         |

| 4       | D               | Driver input pin                                                                                                                           |

| 5       | GND             | Ground pin                                                                                                                                 |

| 6       | А               | Non-inverting driver output pin/Non-inverting receiver input pin                                                                           |

| 7       | В               | Inverting driver output pin/Inverting receiver input pin                                                                                   |

| 8       | V <sub>CC</sub> | Power supply pin, +3.3V ± 0.3V                                                                                                             |

# **Application Information**

#### STUB LENGTH

Stub lengths should be kept to a minimum. For a general approximation, if the electrical length of a trace is greater than 1/5 of the transition edge, then the trace is considered a transmission line. If the velocity equals 160 ps per inch for

a typical loaded backplane, then the maximum stub length is 312 ps/160 ps/inch or 1.95 inches (approximately 2 inches). To determine the maximum stub for your backplane, the propagation velocity for the backplane is required (refer to application notes AN-905 and AN-808).

**Output VOD vs. Load Resistance**

# **Typical Performance Characteristics**

Supply Current measured using a clock pattern with driver terminated to 50ohms . V $_{CC}$  = 3.3V, T $_{A}$  = +25  $^{\circ}C.$

#

60

OUTPUT LOAD  $(\Omega)$

20024663

120

100

$V_{CC} = 3.3V, T_A = +25^{\circ}C$

0

0

1000

FIGURE 15. SOIC performance Characteristics

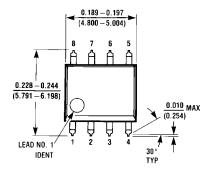

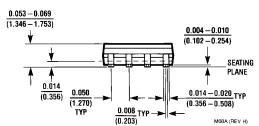

#### Physical Dimensions inches (millimeters) unless otherwise noted

Order Number DS91D176TMA, DS91C176TMA See NS package Number M08A

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.

For the most current product information visit us at www.national.com.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### BANNED SUBSTANCE COMPLIANCE

National Semiconductor manufactures products and uses packing materials that meet the provisions of the Customer Products Stewardship Specification (CSP-9-111C2) and the Banned Substances and Materials of Interest Specification (CSP-9-111S2) and contain no "Banned Substances" as defined in CSP-9-111S2.

Leadfree products are RoHS compliant.

**National Semiconductor Americas Customer** Support Center

Email: new.feedback@nsc.com Tel: 1-800-272-9959

**Europe Customer Support Center** Fax: +49 (0) 180-530 85 86 Email: europe.support@nsc.com Deutsch Tel: +49 (0) 69 9508 6208 English Tel: +44 (0) 870 24 0 2171

Français Tel: +33 (0) 1 41 91 8790

**National Semiconductor**

**National Semiconductor** Asia Pacific Customer Support Center Email: ap.support@nsc.com **National Semiconductor** Japan Customer Support Center Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560