# TMS370 Microcontroller Family Extract

# Data Book

1997

8-Bit Microcontroller Family

| General Information                | 1 |

|------------------------------------|---|

| Quality and Reliability            | 2 |

| Electrostatic Discharge Guidelines | 3 |

| Mechanical Data                    | 4 |

| I |  |

|---|--|

# TMS370 Microcontroller Family Data Book

# **Extract**

SPND005 March 1997

#### **IMPORTANT NOTICE**

Texas Instruments (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

TI warrants performance of its semiconductor products and related software to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Certain applications using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage ("Critical Applications").

TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

Inclusion of TI products in such applications is understood to be fully at the risk of the customer. Use of TI products in such applications requires the written approval of an appropriate TI officer. Questions concerning potential risk applications should be directed to TI through a local SC sales office.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

#### INTRODUCTION

The TMS370 Microcontroller Family Data Book from Texas Instruments includes complete detailed specifications on the TMS370 8-Bit Microcontroller Family product line to include the following subfamilies TMS370Cx0x, TMS370Cx1x, TMS370Cx2x, TMS370Cx32, TMS370Cx36, TMS370Cx4x, TMS370Cx5x, TMS370Cx6x, TMS370Cx7x, TMS370Cx8x, TMS370Cx9x, TMS370CxAx, TMS370CxBx, and TMS370CxCx.

The objective of this manual is to provide the user with complete information on all the subfamilies contained within the TMS370 Family, enabling selection of a particular device to suit the user's needs and application much easier.

The data book is divided into the following sections, each of which is described briefly below:

**Section 1. General Information** – Introduces the TMS370 Family of devices, discusses the key features and major components of the device family, provides a functional-block-diagram generalization, and contains an ordering guide showing the device-numbering convention for all 14 subfamilies. This section also provides a selection reference guide; a listing of the development system support tools; defines: acronyms, key terms and signal names; operating conditions and characteristics; and timing conventions.

**Section 2. Quality and Reliability** – Details the selected processes, standards and philosophies that Texas Instruments uses to ensure the production of high quality products.

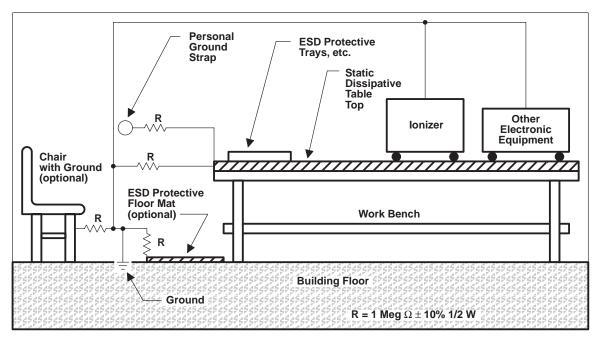

Section 3. Guidelines for Handling Electrostatic-Discharge-Sensitive Devices and Assemblies – Because the devices included in the TMS370 8-Bit Microcontroller Family are categorized as Class 2 ESD-sensitive, this section includes the guidelines for the handling of ESD-sensitive devices.

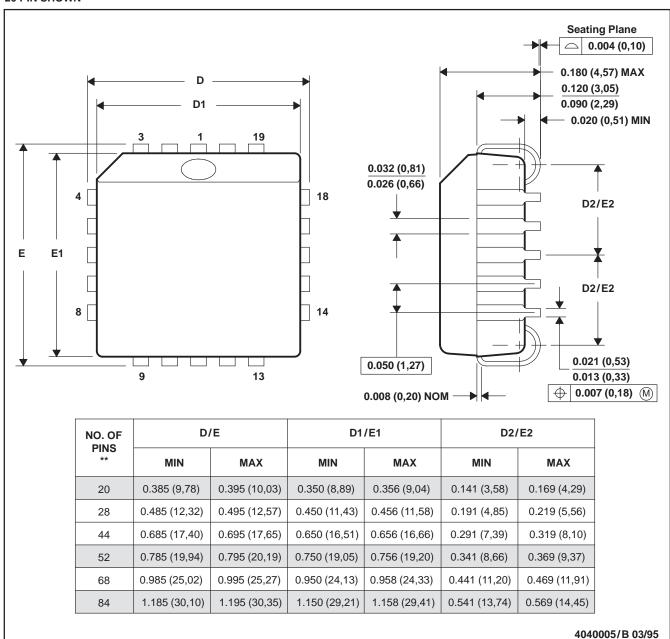

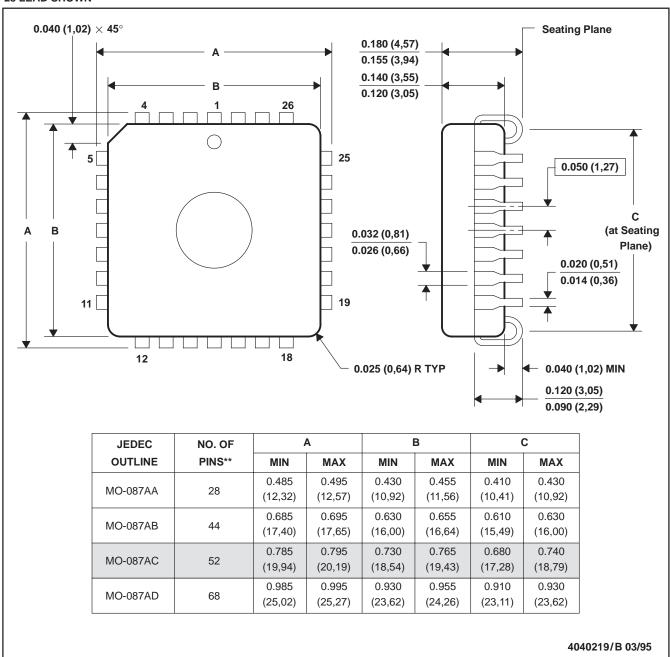

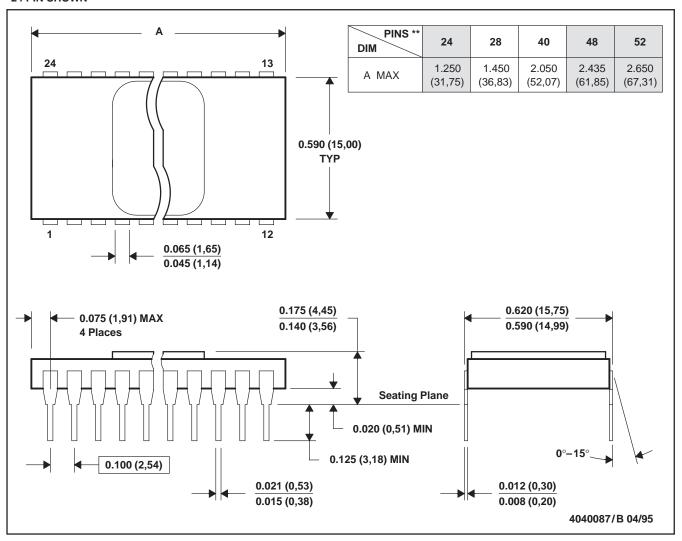

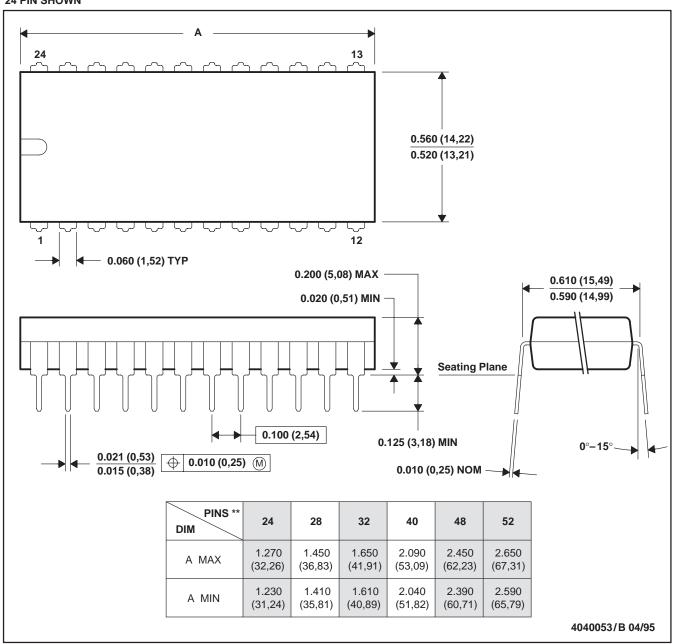

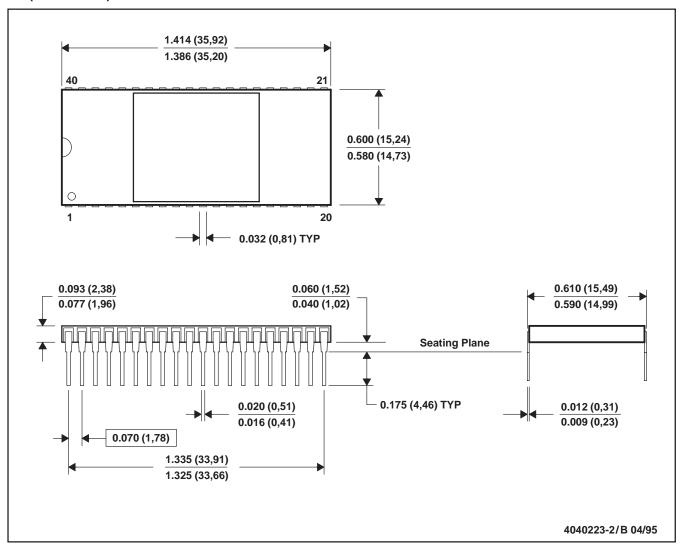

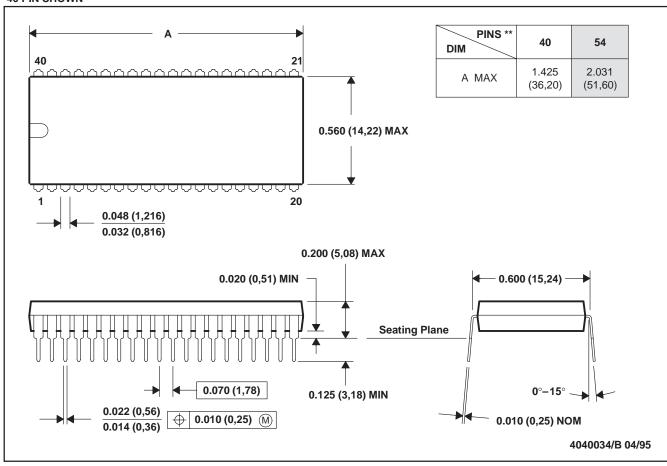

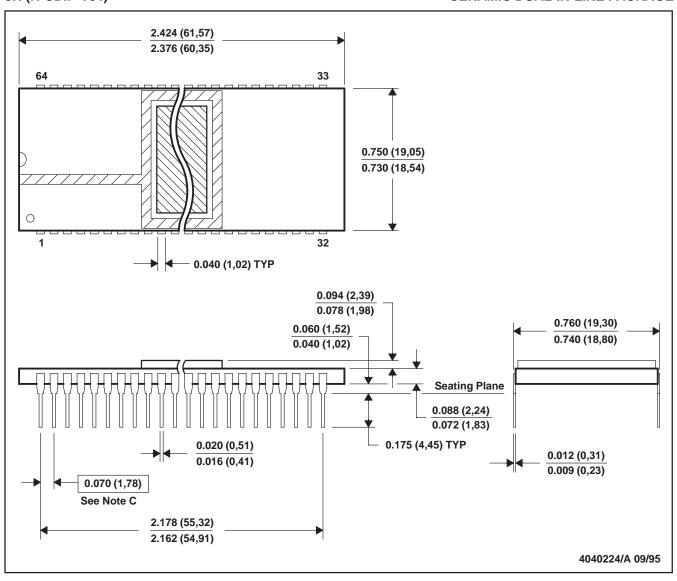

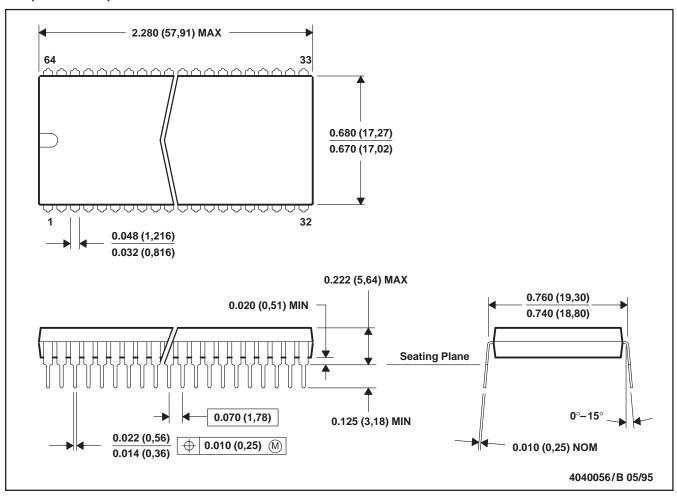

**Section 4. Mechanical Data** – Shows the detailed mechanical drawing packages and the associated specifications for each package type utilized in the TMS370 family. This section also provides a cross-reference table to identify the mechanical package type(s) to a specific device family.

For ordering information or further assistance, please contact your nearest Texas Instruments sales office or distributor as listed on the back page of this book.

#### PRODUCT STAGE STATEMENTS

Product stage statements are used on Texas Instruments data sheets to indicate the development stage(s) of the product(s) specified in the data sheets.

If all products specified in a data sheet are at the same development stage, the appropriate statement from the following list is placed in the lower left corner of the first page of the data sheet.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

ADVANCE INFORMATION concerns new products in the sampling or preproduction phase of development. Characteristic data and other specifications are subject to change without notice.

PRODUCT PREVIEW information concerns products in the formative or design phase of development. Characteristic data and other specifications are design goals. Texas Instruments reserves the right to change or discontinue these products without notice.

If not all products specified in a data sheet are at the PRODUCTION DATA stage, then the first statement below is placed in the lower left corner of the first page of the data sheet. Subsequent pages of the data sheet containing PRODUCT PREVIEW information or ADVANCE INFORMATION are then marked in the lower left-hand corner with the appropriate statement given below:

UNLESS OTHERWISE NOTED this document contains PRODUCTION DATA information current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

ADVANCE INFORMATION concerns new products in the sampling or preproduction phase of development. Characteristic data and other specifications are subject to change without notice.

PRODUCT PREVIEW information concerns products in the formative or design phase of development. Characteristic data and other specifications are design goals. Texas Instruments reserves the right to change or discontinue these products without notice.

| General Information                | 1 |

|------------------------------------|---|

| Quality and Reliability            | 2 |

| Electrostatic Discharge Guidelines | 3 |

| Mechanical Data                    | 4 |

# Contents

|                                              | Page |

|----------------------------------------------|------|

| Introduction to the TMS370 Family of Devices | 1–3  |

| Overview                                     | 1–4  |

| Typical Applications                         | 1–4  |

| Device Categories                            | 1–5  |

| Key Features                                 | 1–6  |

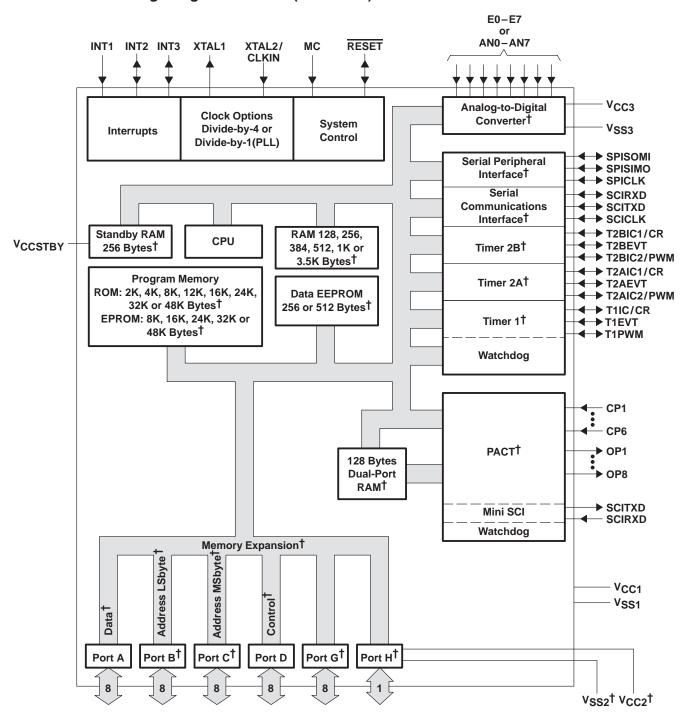

| TMS370 Major Components Architecture         | 1–7  |

| Functional-Block-Diagram Generalization      | 1–11 |

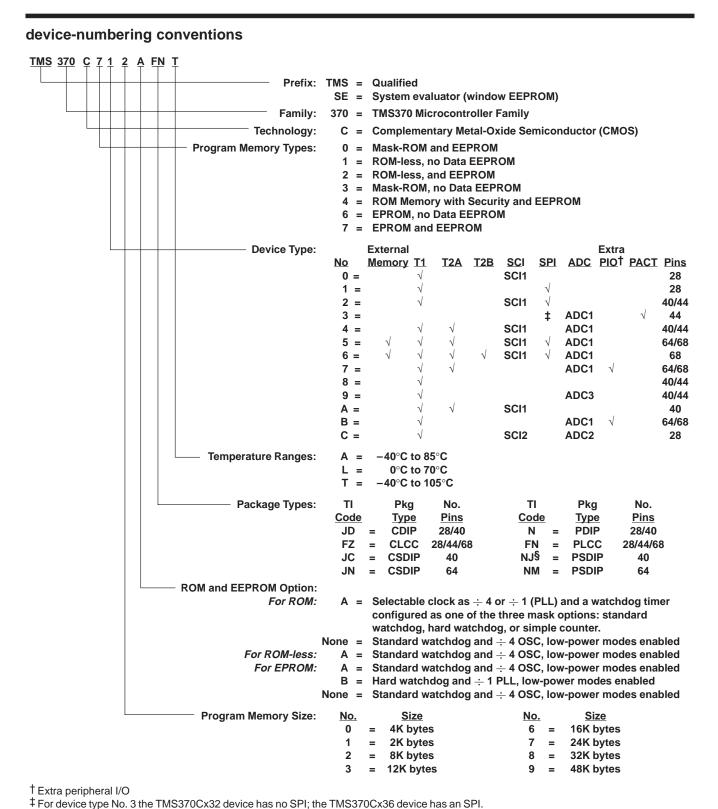

| Device-Numbering Conventions                 | 1–13 |

| Available Development System Support Tools   | 1–14 |

| Selection Reference Guide                    | 1–15 |

| Development Systems Support Tools            | 1–15 |

| Third-Party Support                          | 1–21 |

| Operating Conditions and Characteristics     | 1–22 |

| Timing Conventions                           | 1–23 |

| Related Documentation From Texas Instruments | 1–27 |

| For Further Assistance                       | 1–28 |

| Glossary/Symbols, Terms, and Definitions     | 1-29 |

#### INTRODUCTION TO THE TMS370 FAMILY OF DEVICES

#### introduction to the TMS370 family of devices

This section discusses the key features and major components of the TMS370 8-Bit Microcontroller subfamilies ('x0x, 'x1x, 'x2x, 'x32, 'x36, 'x4x, ..., 'xCx) and includes a functional-block-diagram generalization that depicts all available modules, noting that no one device contains all the available modules. The section concludes with the device-numbering convention and a list of other Texas Instruments related documents.

This section covers the following topics:

- Overview

- Typical Applications

- Device Categories

- Key Features

- TMS370 Major Components Architecture

- CPU

- Register File (RF)

- RAM

- Data EEPROM

- Program Memory (ROM/EPROM)

- Input/Output Ports

- Timer 1

- Timer 2n (A and B)

- Watchdog Timer

- Programmable Acquisition and Control Timer (PACT)

- Serial Communications Interface (SCI1 or SCI2)

- Serial Peripheral Interface (SPI)

- Analog-to-Digital Converter (ADC1, ADC2 or ADC3) Modules

- Functional-Block-Diagram Generalization

- Device-Numbering Conventions

- Available Development-System-Support Tools

- Section Reference Guide

- Development-System-Support Tools

- Operating Conditions and Characteristics

- Timing Conventions

- Related Documentation from Texas Instruments

- For Further Assistance

- Glossary/Symbols, Terms, and Definitions

#### overview

The TMS370 family consists of very large scaled integration (VLSI), 8-bit, complementary metal oxide semiconductor (CMOS) microcontrollers with on-chip EEPROM storage and peripheral-support functions. These devices offer superior performance in complex, real-time control applications in demanding environments and are available in mask-programmable ROM and EPROM.

In a continual effort to improve its products, Texas Instruments has added new, more robust features to the TMS370 family of devices that are designed to enhance performance and enable new application technologies. These added features include new watchdog modes and low-power modes for mask-ROM devices. All family members are software compatible, so that many existing applications can be run on the improved devices without modification of software. (Refer to the associated data sheets for more information on compatibility.)

In expanding its powerful TMS370 family of microcontrollers, TI™ offers many new configurable devices for specific applications. As microcontrollers have evolved, TI has added multiple peripheral functions to chips that originally had only a central processing unit (CPU), memory, and I/O blocks. Now, with the high-performance, software-compatible TMS370 microcontrollers, over 130 standard products are available. Also, up to 27 function modules can be used to configure a new device quickly, easily, and cost-effectively for any applications.

The TMS370 family is supported fully by TI development tools that facilitate simplified software development for prompt market introduction of new products. These tools include an assembler, an optimizing C compiler, a linker, a C source debugger, a design kit, a starter kit, and a third-party microcontroller programmer from BP Microsystems. All of these tools work together by using an IBM™-compatible personal computer (PC) as the host and the central control element. This allows the user to select the host computer and text management as well as editing tools according to system requirements.

Additionally, the TMS370 in-circuit emulator [XDS™—extended development support, and CDT370 compact development tool (CDT™)] allows the user to immediately begin designing, testing, and debugging the system upon specification. The reason for this is straightforward: the emulator itself is modular and configurable, thereby eliminating the need to produce a new emulator for each TMS370 configuration.

#### typical applications

The TMS370 family of devices is the ideal choice for the applications shown in Table 1 because the newly added features (like the addition of multiple peripheral functions per device) have expanded the TMS370 family of microcontrollers, enhanced its performance, and opened up new application technologies.

Table 1. Typical Applications for TMS370 Family of Microcontroller Devices

| APPLICATION AREA   | APP                                                                          | LICATIONS                                                  |

|--------------------|------------------------------------------------------------------------------|------------------------------------------------------------|

| Automotive         | Climate control systems Cruise control Entertainment systems Instrumentation | Navigational systems<br>Engine control<br>Antilock braking |

| Computer           | Keyboards<br>Peripheral interface control                                    | Disk controllers<br>Terminals                              |

| Industrial         | Motor control Temperature controllers Process control                        | Meter control Medical instrumentation Security systems     |

| Telecommunications | Modems Intelligent phones Intelligent line card control                      | Telecopiers<br>Debit cards                                 |

#### device categories

The TMS370 category of devices is divided into 14 subfamilies (see Table 2). All the subfamilies are supported by a full complement of development support tools, which are listed in Table 5.

Table 2. TMS370 Family Categories and Their Corresponding Devices

| FAMILY     | DEVICES INCLUDED                                                                    |                                                                                     |                                                                         |                                                                                     |                                                          |  |  |  |  |  |  |  |  |

|------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------|-------------------------------------------------------------------------------------|----------------------------------------------------------|--|--|--|--|--|--|--|--|

| TMS370Cx0x | TMS370C002A                                                                         | TMS370C302A                                                                         | TMS370C702 <sup>†</sup>                                                 | SE370C702 <sup>†</sup>                                                              |                                                          |  |  |  |  |  |  |  |  |

| TMS370Cx1x | TMS370C010A<br>TMS370C712A                                                          | TMS370C012A<br>TMS370C712B                                                          | TMS370C310A<br>SE370C712A <sup>†</sup>                                  | TMS370C311A<br>SE370C712B <sup>†</sup>                                              | TMS370C312A                                              |  |  |  |  |  |  |  |  |

| TMS370Cx2x | TMS370C020A<br>SE370C722 <sup>†</sup>                                               | TMS370C022A                                                                         | TMS370C320A                                                             | TMS370C322A                                                                         | TMS370C722                                               |  |  |  |  |  |  |  |  |

| TMS370Cx32 | TMS370C032A                                                                         | TMS370C732A                                                                         | TMS370C332A                                                             | SE370C732A <sup>†</sup>                                                             |                                                          |  |  |  |  |  |  |  |  |

| TMS370Cx36 | TMS370C036A                                                                         | TMS370C736A                                                                         | SE370C736A <sup>†</sup>                                                 |                                                                                     |                                                          |  |  |  |  |  |  |  |  |

| TMS370Cx4x | TMS370C040A<br>SE370C742A <sup>†</sup>                                              | TMS370C042A                                                                         | TMS370C340A                                                             | TMS370C342A                                                                         | TMS370C742A                                              |  |  |  |  |  |  |  |  |

| TMS370Cx5x | TMS370C050A<br>TMS370C150A<br>TMS370C352A<br>TMS370C456A<br>SE370C756A <sup>†</sup> | TMS370C052A<br>TMS370C156A<br>TMS370C353A<br>TMS370C756A<br>SE370C758A <sup>†</sup> | TMS370C056A<br>TMS370C250A<br>TMS370C356A<br>TMS370C758A<br>SE370C758B† | TMS370C058A<br>TMS370C256A<br>TMS370C358A<br>TMS370C758B<br>SE370C759A <sup>†</sup> | TMS370C059A<br>TMS370C350A<br>TMS370C452A<br>TMS370C759A |  |  |  |  |  |  |  |  |

| TMS370Cx6x | TMS370C067A<br>SE370C768A <sup>†</sup>                                              | TMS370C068A<br>SE370C769A <sup>†</sup>                                              | TMS370C069A                                                             | TMS370C768A                                                                         | TMS370C769A                                              |  |  |  |  |  |  |  |  |

| TMS370Cx7x | TMS370C077A                                                                         | TMS370C777A                                                                         | SE370C777A <sup>†</sup>                                                 |                                                                                     |                                                          |  |  |  |  |  |  |  |  |

| TMS370Cx8x | TMS370C080                                                                          | TMS370C380A                                                                         | TMS370C686A                                                             | SE370C686A <sup>†</sup>                                                             |                                                          |  |  |  |  |  |  |  |  |

| TMS370Cx9x | TMS370C090A                                                                         | TMS370C792                                                                          | SE370C792 <sup>†</sup>                                                  |                                                                                     |                                                          |  |  |  |  |  |  |  |  |

| TMS370CxAx | TMS370C3A7A                                                                         |                                                                                     |                                                                         |                                                                                     |                                                          |  |  |  |  |  |  |  |  |

| TMS370CxBx | TMS370C0B6A                                                                         |                                                                                     |                                                                         |                                                                                     |                                                          |  |  |  |  |  |  |  |  |

| TMS370CxCx | TMS370C3C0A                                                                         | TMS370C6C2A                                                                         | SE370C6C2A†                                                             |                                                                                     |                                                          |  |  |  |  |  |  |  |  |

<sup>†</sup> These system evaluators are used only in a prototype environment. Their reliability has not been characterized.

#### **KEY FEATURES**

#### key features

The TMS370 family is based on a register-to-register architecture that allows access to a register file (up to 256 bytes) in a single bus cycle. On-chip memory includes program memory (mask ROM or EPROM), static RAM, standby RAM, and data EEPROM.

The versatile on-chip peripheral functions include an analog-to-digital converter (ADC1, ADC2, or ADC3), a serial communications interface (SCI1 or SCI2), a serial peripheral interface (SPI), three different timer modules (T1, T2A, and T2B), and up to 55 digital input/output (I/O) pins. The number and type of peripheral functions (modules) is dependent on the TMS370 subfamily.

The following are key features of the TMS370 device family (not all features are available for all devices):

- Compatibility for supporting software migration between current and future microcontrollers

- CMOS EPROM technology for providing reprogrammable EPROM and one-time programmable (OTP) program memory for prototypes and for small-volume or quick-turn production

- CMOS EEPROM technology for providing EEPROM programming with a single 5-V supply

- ADC technology for converting analog signals to digital values

- Static RAM/register file registers that offer numerous memory options

- Standby RAM that offers data protection in power-off condition

- Programmable (asynchronous and isosynchronous<sup>†</sup>) built-in serial communications interface for control of timing, data format, and protocol

- Serial peripheral interface for providing single-mode synchronous data transmission from the CPUs to any external peripheral devices

- Flexible operating features:

- Power-reduction-standby and halt modes

- Temperature options:

- 0°C to 70°C operating temperature (L)

- -40°C to 85°C operating temperature (A)

- -40°C to 105°C operating temperature (T)

- Input clock frequency options:

- Divide-by-4 (0.5 MHz to 5 MHz SYSCLK) standard oscillator

- Divide-by-1 ( 2 MHz to 5 MHz SYSCLK) phase-locked loop (PLL)

- Operating voltage range: 5 V +10%

- Flexible interrupt handling for design flexibility:

- Two programmable interrupt levels

- Programmable rising-edge or falling-edge detect

- System integrity features that increase flexibility during the software development phase:

- Oscillator fault detection

- Privileged mode lockout

- Watchdog timer

- Memory security (for ROM)

#### key features (continued)

- Memory-mapped ports for easy addressing

- An optimizing C compiler that translates ANSI C programs into TMS370 assembly language source

- A high-level language debugger that lets the user refine and correct code

- A modular library for quickly changing the device configurations

- 18 addressing modes that use eight formats, including:

- Implied

- Register-to-register arithmetic

- Indirect addressing

- Indexed and indirect branches and calls

- PC relative

- 250-mA typical latch-up immunity at 25°C

- Electrostatic discharge (ESD) protection that exceeds 2,000 V per MIL-STD-883C method 3015, making the TMS370 families Class 2 ESD-sensitive devices

#### TMS370 major components architecture

In addition to the features listed in the key features section, the TMS370 family members have the following architectural features. Not all features (key or architectural) are applicable to all devices. The selection reference guide (see Table 4) summarizes the following features and identifies the applicable devices associated with those features.

#### CPU

The TMS370 8-bit CPU has a status register, program-counter register, and stack pointer. The CPU uses the register file as working registers that are accessed on the internal bus in one bus cycle. The 8-bit internal bus also allows access to memory and to the peripheral interfaces. TMS370Cx5x and TMS370Cx6x devices all allow external memory expansion through ports A, B, C, and D.

#### register file (RF)

The register file is located at the beginning of the TMS370 memory map. Register-access instructions in the TMS370 instruction set allow access to any of the first 256 registers (if available) in one bus cycle. This segment of the memory map is used as general-purpose RAM and as the stack.

#### **RAM**

RAM modules, other than those contained in the register file, are mapped after the register file. The TMS370 accesses this RAM in two cycles.

#### data EEPROM

With the exception of the TMS370CxAx and TMS370CxCx device groups, certain devices in the TMS370 family have EEPROM. The data EEPROM modules provide in-circuit programmability and data retention in power-off mode. The modules contain 256 or 512 bytes of EEPROM. This memory is useful for storing constants and infrequently changed variables that are required by the application program. The EEPROM can be programmed and erased by using available EEPROM programmers or by the TMS370 device under program control.

#### program memory (ROM/EPROM)

The program memory provides alternatives to meet the needs of different applications. The program memory modules presently contain 2K, 4K, 8K, 16K, 24K, 32K, or 48K bytes of memory. The program memory in TMS370C6xx, SE370C6xx, TMS370C7xx, and SE370C7xx devices is EPROM. EPROM devices in a windowed ceramic package can be programmed, erased, and reprogrammed for prototyping. EPROM devices in a non-windowed plastic package are one-time programmable (OTP) devices that are used for small production runs. In the TMS370C0xx, TMS370C3xx, and TMS370C4xx devices, the program memory is mask-ROM that is programmed at the factory. ROM devices are appropriate for large-volume production.

#### input/output ports

The TMS370 family of devices has a varying number of I/O ports that have various port widths. Table 3 lists the available I/O port widths, by the number of bits, for each of the TMS370 subfamilies.

| 0.105.1111.150.  | BITS FOR PORTS A-H |    |    |    |   |   |  |  |  |  |  |  |  |  |

|------------------|--------------------|----|----|----|---|---|--|--|--|--|--|--|--|--|

| SUBFAMILIEST     | Α                  | В  | С  | D  | G | Н |  |  |  |  |  |  |  |  |

| 'x0x, 'x1x       | 8                  |    |    | 5  |   |   |  |  |  |  |  |  |  |  |

| 'x2x             | 8                  | 8  | 1  | 5  |   |   |  |  |  |  |  |  |  |  |

| 'x32             | 8                  |    |    | 4  |   |   |  |  |  |  |  |  |  |  |

| 'x36             | 8                  |    |    | 5  |   |   |  |  |  |  |  |  |  |  |

| 'x4x             | 8                  | 3  |    | 5  |   |   |  |  |  |  |  |  |  |  |

| 'x5x - (64 pins) | 8‡                 | 8‡ | 8‡ | 6‡ |   |   |  |  |  |  |  |  |  |  |

| 'x5x - (68 pins) | 8‡                 | 8‡ | 8‡ | 8‡ |   |   |  |  |  |  |  |  |  |  |

| 'x6x             | 8‡                 | 8‡ | 8‡ | 5‡ |   |   |  |  |  |  |  |  |  |  |

| 'x7x - (64 pins) | 8                  | 8  | 8  | 6  | 6 |   |  |  |  |  |  |  |  |  |

| 'x7x - (68 pins) | 8                  | 8  | 8  | 8  | 6 |   |  |  |  |  |  |  |  |  |

| 'x8x - (40 pins) | 8                  | 8  | 6  | 5  |   |   |  |  |  |  |  |  |  |  |

| 'x8x – (44 pins) | 8                  | 8  | 8  | 5  |   |   |  |  |  |  |  |  |  |  |

| 'x9x             | 8                  |    |    | 5  |   |   |  |  |  |  |  |  |  |  |

| 'xAx             | 8                  | 8  | 1  | 5  |   |   |  |  |  |  |  |  |  |  |

| 'xBx - (64 pins) | 8                  | 8  | 8  | 6  | 8 | 1 |  |  |  |  |  |  |  |  |

| 'xBx – (68 pins) | 8                  | 8  | 8  | 8  | 8 | 1 |  |  |  |  |  |  |  |  |

| 'xCx             | 8                  |    |    | 4  |   |   |  |  |  |  |  |  |  |  |

Table 3. Bits Per Port for TMS370 Devices

#### timer 1

Timer 1 is a 16-bit timer that can be configured in the following ways:

- A programmable 8-bit prescaler (provides a 24-bit real-time timer) that determines the independent clock sources for the general-purpose timer and the watchdog (WD) timer

- A 16-bit event timer to keep a cumulative total of the transitions

- A 16-bit pulse accumulator to measure the pulse-input width

- A 16-bit input-capture function that latches the counter value on the occurrence of an external input

- Two 16-bit compare registers that trigger when the counter matches the contents of a compare register

- A self-contained pulse-width modulated (PWM) output control function

<sup>†</sup> For all subfamilies, the ports for these microcontrollers can be programmed, bit by bit, to function as either digital input or digital output.

<sup>&</sup>lt;sup>‡</sup> These ports can be configured by the software as the data, control, and address buses for external memory. Any bits not needed for external memory can be programmed to be either digital input or digital output.

#### timer 1 (continued)

The results of these operations can generate an interrupt to the CPU, set flag bits, reset the timer counter, toggle an I/O line, or generate PWM outputs. Timer 1 can provide up to 200 ns of resolution with a 5-MHz system clock (SYSCLK).

#### timer 2n (A and B)

Timer 2A and 2B are 16-bit timers that can be configured in the following ways:

- Four independent clock sources for the general-purpose timer

- A 16-bit event timer, to keep a cumulative total of the transitions

- A16-bit pulse accumulator, to measure the pulse-input width

- Two 16-bit input-capture devices that change a counter value on the occurrence of an external input

- Two 16-bit compare registers that trigger when a counter matches the contents of a compare register

- A self-contained PWM output controller

The results of the timer 2A and 2B operations can generate an interrupt to the CPU, set flag bits, reset the timer counter, toggle an I/O line, or generate PWM outputs. Timers 2A and 2B can provide up to 200 ns of resolution with a 5-MHz system clock (SYSCLK).

#### watchdog timer

The watchdog (WD) timer helps ensure system integrity. The WD timer can be programmed to generate a hardware reset upon a time-out condition. The WD function provides a hardware monitor over the software to help avoid losing a program. If not needed as a WD, this timer can be used as a general-purpose timer.

#### programmable acquisition and control timer (PACT)

The PACT module in the 'x32 and 'x36 subfamilies is a programmable timing module that uses some of the on-chip RAM to store its commands and the timer values. Only the TMS370Cx36 device offers the 256-byte standby RAM that protects stored data against power failures. The PACT module offers the following:

- Input capture on up to six pins, four of which may have a programmable prescaler

- One input-capture pin that can drive an 8-bit event counter

- Up to eight timer-driven outputs

- Timer capability of up to 20 bits

- Interaction between event counter and timer activity

- 18 independent interrupt vectors to allow better servicing of events

- Watchdog with selectable time-out period

- Mini-SCI (serial communications interface) that works as a full duplex UART (universal asynchronous receiver transmitter)

Once set up, the PACT requires no CPU overhead except to service interrupts.

#### serial communications interface (SCI1 or SCI2)

The term SCI is used frequently to refer to SCI1 and SCI2. The SCI1 and SCI2 modules are built-in serial interfaces. The SCI1 has a 3-pin configuration and SCI2 has a 2-pin configuration. Both offer the following features:

- Programmable to be asynchronous (up to 156 Kbps)

- Full duplex, double-buffered receive (Rx) and transmit (Tx)

- Programmable format with error-checking capabilities

The following feature is available only on the SCI1 module:

Programmable to be isosynchronous (up to 2.5 Mbps)

The SCI1 and SCI2 modules program and control all timing, data format, and protocol factors. The CPU takes part in the serial communications only:

- To write data transmitted to the registers in the SCI

- To read received data from the registers in the SCI when interrupted

#### serial peripheral interface (SPI)

The SPI module is a built-in serial interface that facilitates communication between the network master, slave CPUs, and the external peripheral devices. The SPI module provides synchronous data transmission of up to 2.5 Mbps. Like the SCI, the SPI is set up by software. Once setup, the CPU takes no part in timing, data format, or protocol. Also, like the SCI, the CPU reads and writes to memory-mapped registers to receive and transmit data. An SPI interrupt alerts the CPU when received data is ready.

#### analog-to-digital converter (ADC1, ADC2, ADC3) modules

The 8-bit ADC modules perform successive approximation conversion. The term ADC is a general term used for ADC1, ADC2, and ADC3 modules. The ADCs offer the following number of input channels for each of the specified microcontroller families:

- ADC1 offers the following:

- Four channels in the 40-pin devices of the 'x4x subfamily,

- Eight channels in the 44-pin devices of the 'x4x, 'x32, and 'x36 subfamilies

- Eight channels in the 64-pin and 68-pin devices of the 'x5x, 'x6x, 'x7x, and 'xBx subfamilies

- ADC2 offers four channels in the 28-pin devices of the 'xCx subfamily

- ADC3 offers 15 channels in the 40-pin and 44-pin devices of the 'x9x subfamily

The reference source and input channel are selectable. The user can program the conversion result to be the ratio of the input voltage to the reference voltage or the ratio of one analog input to another. Input lines that are not required for analog-to-digital conversion can be programmed to be digital input lines.

For a detailed explanation on any of the major components of the TMS370 device family, see the *TMS370 8-Bit Microcontroller User's Guide* (literature number SPNU127) or to the specific subfamily data sheet.

For more details on the programming of the TMS370 family or for further expansion on the applications of these devices, see the paragraph in this section on related documentation from Texas Instruments.

#### FUNCTIONAL-BLOCK-DIAGRAM GENERALIZATION

#### functional-block-diagram generalization

This section contains a functional-block-diagram generalization for the TMS370 microcontroller subfamilies (that is, 'x0x, 'x1x, 'x2x, 'x32, 'x36, 'x4x, ..., 'xCx). Because this diagram is a generalization, it depicts all the modules available for the TMS370 families, noting that no one TMS370 device contains all available options. The diagram also shows the basic internal connections among the major architectural features that are identified in the selection guide (see Table 4). For a functional block diagram of a specific TM370 subfamily, the pinouts, the descriptions of the pinouts, and descriptions of the external connection names, refer to the applicable data sheet.

#### FUNCTIONAL-BLOCK-DIAGRAM GENERALIZATION

#### functional-block-diagram generalization (continued)

<sup>&</sup>lt;sup>†</sup> Not available on all devices; see the selection reference guide (Table 4).

§ NJ package was formerly known as N2.

Figure 1. TMS370C Family Nomenclature

#### AVAILABLE DEVELOPMENT SYSTEM SUPPORT TOOLS

#### available development system support tools

The TMS370 family is fully supported by TI development tools that facilitate simplified software development for prompt market introduction of new products. These tools include an assembler, an optimizing C compiler, a linker, a C source debugger, a design kit, a starter kit, and a third-party microcontroller programmer from BP Microsystems. All of these tools work together by using an IBM-compatible PC as the host and central control element. This allows the user to select the host computer and text management as well as editing tools according to system requirements.

Additionally, the TMS370 in-circuit emulator (XDS and CDT370) allows the user to immediately begin designing, testing, and debugging the system upon specification. The reason for this is straightforward: the emulator itself is modular and configurable, thereby eliminating the need to produce a new emulator for each TMS370 configuration.

For a list of the available development system support tools, identified by device category, refer to the TMS370 Development System Support Tools table (see Table 5) or to the specific TMS370 subfamily data sheet.

For more detailed information on the development system support tools, refer to the *TMS370 8-Bit Microcontroller User's Guide* (literature number SPNU127) or to the documents listed in the section titled related documentation from Texas Instruments.

#### SELECTION REFERENCE GUIDE

#### selection reference guide

The TMS370 8-Bit Microcontroller Product Selection Guide Configurations Table, commonly called the Selection Reference Guide (see Table 4), provides the user with an easy-to-use guide that includes the following specific device information by subfamilies: product family description (device type, part number, package and temperature options, and pin count); memory [program memory (ROM, EPROM), data memory (EEPROM, RAM) and any capability of off-chip memory expansion]; and peripherals (timers, serial interfaces, A/D channels, I/O, clock generators, and OTP and reprogrammable devices). The following symbol footnotes are used in Table 4:

- † Packages: FN = PLCC, FZ = CLCC, N = PDIP, JD = CDIP, NJ = PSDIP (formerly N2), JC = CSDIP, NM = PSDIP, JN = CSDIP

- ‡ Temperatures: ROM device types have L = 0°C to +70°C, A = -40°C to +85°C, and T = -40°C to +105°C temperature options; ROM-less, OTP and UV-EPROM device types only have T.

- § PACT SCI: PACT includes a mini-SCI. SCI1 module has 3-pin configuration while SCI2 module has 2-pin configuration.

- ¶ RAM: Includes 256 bytes of standby RAM

- # Memory: Includes secured memory feature

- Max Freq: Supports maximum operating frequency of 3 MHz SYSCLK

- \*PACT WDOG: PACT includes a watchdog timer

- □ADC1 Channels: 8 channels A/D for 44 pin package, 4 channels A/D for 40 pin package

- ◊ Timers: Timer 1 (T1) includes a watchdog timer programmable as a general purpose 16-bit timer

- Ψ44/40 Packages: 44 pins for FN, FZ packages. 40 pins for N, JD, NJ (formerly N2), JC packages.

- Φ68/64 Packages: 68 pins for FN, FZ packages. 64 pins for NM, JN packages

- ¥ TMS370CxCx SCI: Operable in asynchronous mode only

- △ Converter Socket: Requires a TMDS37788OTP converter socket

- \*Requires software modification (see the TMS370CxBx Data Sheet (literature number SPNS038))

Table 4 is a continuous table and only the applicable symbol footnotes are listed on each page.

#### development systems support tools

The TMS370 development system support tools listing shown in Table 5 identifies the available development support tools (by tool description and part number) for each of the TMS370 subfamilies ('x0x, 'x1x, 'x2x, 'x32, 'x36, ..., 'xCx).

## **SELECTION REFERENCE GUIDE**

Table 4. TMS370 8-Bit Microcontroller Product Configurations

| ABLE                         |            |            |                |                |               |              |            |                |                |                |                |                |                |                |               |               |            |                    |                    |                    |                    |                |           |

|------------------------------|------------|------------|----------------|----------------|---------------|--------------|------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|---------------|---------------|------------|--------------------|--------------------|--------------------|--------------------|----------------|-----------|

| OTP AND REPROGRAMMABLE       | DEVICES    |            | C702           | C702           | I             | I            |            | C712           | C712           | C712           | C712           | C712           | ı              | I              | ı             | ı             |            | C722               | C722               | C722               | C722               | I              | I         |

| CLOCK                        |            |            | ÷4 or PLL      | ÷4 or PLL      | ÷4            | ÷4           |            | ÷4 or PLL      | ÷4             | PLL            | ÷4            | PLL           |            | ÷4 or PLL          | ÷4 or PLL          | ÷4 or PLL          | ÷4 or PLL          | ÷4             | 7.7       |

| O/I                          |            |            | 22             | 22             | 22            | 22           |            | 22             | 22             | 22             | 22             | 22             | 22             | 22             | 22            | 22            |            | 34                 | 34                 | 34                 | 34                 | 34             | 3.4       |

| A/D<br>CHANNELS              |            |            |                |                |               |              |            |                |                |                |                |                |                |                |               |               |            |                    |                    |                    |                    |                |           |

| SERIAL<br>INTERFACE§         |            |            | SCI1           | SCI1           | SCI1          | SCI1         |            | SPI            | SPI           | SPI           |            | SPI/SCI1           | SPI/SCI1           | SPI/SCI1           | SPI/SCI1           | SPI/SCI1       | 100/100   |

| TIMERS                       |            |            | T1             | T1             | T1            | 11           |            | 11             | 11             | T1             | 11             | T1             | T1             | T1             | T1            | T1            |            | T1                 | T1                 | T1                 | 11                 | 11             | +         |

| OFF-CHIP<br>MEM EXP          | (BY1ES)    | TMS370Cx0x |                |                |               |              | TMS370Cx1x |                |                |                |                |                |                |                |               |               | TMS370Cx2x |                    |                    |                    |                    |                |           |

| MORY<br>S)                   | RAM        | TMS3       | 256            | 256            | 256           | 256          | TMS3       | 128            | 128            | 128            | 128            | 256            | 256            | 256            | 256           | 256           | TMS3       | 256                | 256                | 256                | 256                | 256            | 010       |

| DATA MEMORY<br>(BYTES)       | EEPROM     |            |                | 256            | 256           | 256          |            |                |                | 256            |                | 256            | 256            | 256            | 256           | 256           |            |                    |                    | 256                | 256                | 256            | 250       |

| PROGRAM<br>MEMORY<br>(BYTES) | EPROM      |            |                |                | ₩<br>Ж        | ₩<br>Ж       |            |                |                |                |                |                | %              | ₩<br>Ж         | æ             | ₩<br>Ж        |            |                    |                    |                    |                    | 8K             | 70        |

| PRO<br>MEI<br>(B)            | ROM        |            | 8K             | 8K             |               |              |            | 2K             | 4K             | 4K             | 8K             | 8K             |                |                |               |               |            | ¥                  | 8K                 | 4K                 | 8K                 |                |           |

| PACKAGE<br>PIN COUNT         |            |            | 28             | 28             | 28            | 28           |            | 28             | 28             | 28             | 28             | 28             | 28             | 28             | 28            | 28            |            | 44/40 <sup>Ψ</sup> | 44/40 <sup>Ψ</sup> | 44/40 <sup>Ψ</sup> | 44/40 <sup>Ψ</sup> | $44/40^{\Psi}$ | WON/ NA   |

| PACKAGE<br>OPTIONS           |            |            | Ę              | Ę              | ĸ             | FZ           |            | FN/N           | FN/N           | FN/N           | FN/N           | N/NH           | N/NH           | N/NH           | FZ/JD         | FZ/JD         |            | FN/N/NJ            | FN/N/NJ            | FN/N/NJ            | FN/N/NJ            | FN/N/NJ        | 01/01/22  |

| PART NUMBER "yy" = PACKAGE   | .z. = 1EMP |            | TMS370C302Ayyz | TMS370C002Ayyz | TMS370C702yyz | SE370C702yyz |            | TMS370C311Ayyz | TMS370C310Ayyz | TMS370C010Ayyz | TMS370C312Ayyz | TMS370C012Ayyz | TMS370C712Ayyz | TMS370C712Byyz | SE370C712Ayyz | SE370C712Byyz |            | TMS370C320Ayyz     | TMS370C322Ayyz     | TMS370C020Ayyz     | TMS370C022Ayyz     | TMS370C722yyz  | - CCTOCTO |

| DEVICE<br>TYPE‡              |            |            | ROM            | ROM            | OTP           | UV-EPROM     |            | ROM            | ROM            | ROM            | ROM            | ROM            | OTP            | OTP            | UV-EPROM      | UV-EPROM      |            | ROM                | ROM                | ROM                | ROM                | OTP            | MO007 /1- |

† Packages: FN = PLCC, FZ = CLCC, N = PDIP, JD = CDIP, NJ = PSDIP (formerly N2), JC = CSDIP, NM = PSDIP, JN = CSDIP

<sup>‡</sup> Temperatures: ROM device types have L = 0°C to +70°C, A = -40°C to +85°C, and T = -40°C to +105°C temperature options; ROM-less, OTP and UV-EPROM device types only have T. § PACT SCI: PACT includes a mini-SCI. SCI1 module has 3-pin configuration while SCI2 module has 2-pin configuration.

◊ Timers: Timer 1 (T1) includes a watchdog timer programmable as a general purpose 16-bit timer Ψ44/40 Packages: 44 pins for FN, FZ packages. 40 pins for N, JD, NJ (formerly N2), JC packages.

| _                             |

|-------------------------------|

| ned                           |

| ontin                         |

| <u>ပ</u>                      |

| <i><b><u>Irations</u></b></i> |

| Configu                       |

| oduct                         |

| <u>.</u>                      |

| Microcontroller               |

| 3370 8-Bit                    |

| 읟                             |

| Table 4. TN                   |

|                                                               | OTP AND REPROGRAMMABLE       | DEVICES  |            | C732           | C732           | C736           | ı              | ı              | ı             | I             |            | C742               | C742               | C742               | C742               | ı                  | I                  |            | C756           | C756           | C756           | C756           | C756                 | C756           | C756           | C756                 | C756           | C759           |                                         |

|---------------------------------------------------------------|------------------------------|----------|------------|----------------|----------------|----------------|----------------|----------------|---------------|---------------|------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|------------|----------------|----------------|----------------|----------------|----------------------|----------------|----------------|----------------------|----------------|----------------|-----------------------------------------|

|                                                               | CLOCK<br>GENERATOR           |          |            | ÷4 or PLL      | ÷4 or PLL      | ÷4 or PLL      | ÷4             | ÷4             | ÷4            | ÷4            |            | ÷4 or PLL          | ÷4 or PLL          | ÷4 or PLL          | ÷4 or PLL          | ÷4                 | ÷4                 |            | ÷4             | ÷4             | ÷4             | ÷4             | ÷4 or PLL            | ÷4 or PLL      | ÷4 or PLL      | ÷4 or PLL            | ÷4 or PLL      | ÷4 or PLL      |                                         |

| ea)                                                           | 0/                           |          |            | 23             | 23             | 25             | 23             | 25             | 23            | 25            |            | 36/32              | 36/32              | 36/32              | 36/32              | 36/32              | 36/32              |            | 22             | 22             | 55             | 22             | 55/53                | 55/53          | 55/53          | 55/53                | 22             | 22             |                                         |

| พรร/บ ช-ธน microcontroller Product Configurations (Continued) | A/D<br>CHANNELS              |          |            | ADC1/8         | ADC1/8         | ADC1/8         | ADC1/8         | ADC1/8         | ADC1/8        | ADC1/8        |            | ADC1/8, 4□         |            | ADC1/8         | ADC1/8         | ADC1/8         | ADC1/8         | ADC1/8               | ADC1/8         | ADC1/8         | ADC1/8               | ADC1/8         | ADC1/8         |                                         |

| riguration                                                    | SERIAL<br>INTERFACE§         |          |            | PACT           | PACT           | SPI/PACT       | PACT           | SPI/PACT       | PACT          | SPI/PACT      |            | SCI1               | SCI1               | SCI1               | SCI1               | SCI1               | SCI1               |            | SPI/SCI1       | SPI/SCI1       | SPI/SCI1       | SPI/SCI1       | SPI/SC11             | SPI/SCI1       | SPI/SCI1       | SPI/SCI1             | SPI/SCI1       | SPI/SCI1       | 1.10                                    |

| noo 13r                                                       | TIMERS                       |          |            | PACT☆          | PACT☆          | PACT☆          | PACT☆          | PACT☆          | PACT☆         | PACT☆         |            | T1/T2a             | T1/T2a             | T1/T2a             | T1/T2a             | T1/T2a             | T1/T2a             |            | T1/T2a         | T1/T2a         | T1/T2a         | T1/T2a         | T1/T2a               | T1/T2a         | T1/T2a         | T1/T2a               | T1/T2a         | T1/T2a         | 1.11                                    |

| er Produ                                                      | OFF-CHIP<br>MEM EXP          | (BYTES)  | TMS370Cx3x |                |                |                |                |                |               |               | TMS370Cx4x |                    |                    |                    |                    |                    |                    | TMS370Cx5x | 56K            | 56K            | 56K            | 56K            | 112K                 | 112K           | 112K           | 112K                 | 112K           | 112K           |                                         |

| ntrolle                                                       | MORY<br>S)                   | RAM      | TMS        | 256            | 256            | 512¶           | 256            | 512¶           | 256           | 1212          | TMS        | 256                | 256                | 256                | 256                | 256                | 256                | TMS        | 256            | 256            | 512            | 512            | 256                  | 256            | 256            | 256                  | 256            | 1536           |                                         |

| MICLOCO                                                       | DATA MEMORY<br>(BYTES)       | EEPROM   |            |                | 256            | 256            | 256            | 256            | 256           | 256           |            |                    |                    | 256                | 256                | 256                | 256                |            |                | 256            |                | 512            |                      | 256            |                | 256                  | 256            |                |                                         |

| 0-DIL                                                         | PROGRAM<br>MEMORY<br>(BYTES) | EPROM    |            |                |                |                | 8K             | 16K            | 8K            | 16K           |            |                    |                    |                    |                    | 9K                 | 8K                 |            |                |                |                |                |                      |                |                |                      |                |                | 1.1                                     |

| M3570                                                         | PROC<br>MEN<br>(BY           | ROM      |            | 8K             | %<br>X         | 16K            |                |                |               |               |            | 4 <sub>X</sub>     | 8K                 | 4K                 | 3K                 |                    |                    |            |                |                |                |                | 4K                   | 4K             | 8K             | 8K                   | 8K#            | 12K            |                                         |

| lable 4. II                                                   | PACKAGE<br>PIN               | COON     |            | 44             | 44             | 44             | 44             | 44             | 44            | 44            |            | 44/40 <sup>Ψ</sup> |            | 68             | 68             | 68             | 68             | 68 / 64 <sup>Φ</sup> | $68/64^{\Phi}$ | $68/64^{\Phi}$ | 68 / 64 <sup>Φ</sup> | 68             | 89             | !!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!! |

| 18                                                            | PACKAGE<br>OPTIONS           | - XX     |            | ΝH             | N.             | ΝΉ             | В              | ИN             | FZ            | FZ            |            | FN/N/NJ            | FN/N/NJ            | FN/N/NJ            | FN/N/NJ            | FN/N/NJ            | FZ/JD/JC           |            | ВN             | FN             | FN             | FN             | FN/NM                | FN/NM          | FN/NM          | FN/NM                | FN             | N.             |                                         |

|                                                               | PART NUMBER<br>"yy"= PACKAGE | z =1 EMP |            | TMS370C332Ayyz | TMS370C032Ayyz | TMS370C036Ayyz | TMS370C732Ayyz | TMS370C736Ayyz | SE370C732Ayyz | SE370C736Ayyz |            | TMS370C340Ayyz     | TMS370C342Ayyz     | TMS370C040Ayyz     | TMS370C042Ayyz     | TMS370C742Ayyz     | SE370C742Ayyz      |            | TMS370C150Ayyz | TMS370C250Ayyz | TMS370C156Ayyz | TMS370C256Ayyz | TMS370C350Ayyz       | TMS370C050Ayyz | TMS370C352Ayyz | TMS370C052Ayyz       | TMS370C452Ayyz | TMS370C353Ayyz |                                         |

|                                                               | DEVICE<br>TYPE‡              |          |            | ROM            | ROM            | ROM            | ОТР            | OTP            | UV-EPROM      | UV-EPROM      |            | ROM                | ROM                | ROM                | ROM                | ОТР                | UV-EPROM           |            | ROM-less       | ROM-less       | ROM-less       | ROM-less       | ROM                  | ROM            | ROM            | ROM                  | ROM            | ROM            |                                         |

† Packages: FN = PLCC, FZ = CLCC, N = PDIP, JD = CDIP, NJ = PSDIP (formerly N2), JC = CSDIP, NM = PSDIP, JN = CSDIP

<sup>‡</sup> Temperatures: ROM device types have L = 0°C to +70°C, A = -40°C to +85°C, and T = -40°C to +105°C temperature options; ROM-less, OTP and UV-EPROM device types only have T. § PACT SCI: PACT includes a mini-SCI. SCI1 module has 3-pin configuration while SCI2 module has 2-pin configuration.

¶ RAM: Includes 256 bytes of standby RAM

# Memory: Includes secured memory feature

★PACT WDOG: PACT includes a watchdog timer

□ADC1 Channels: 8 channels A/D for 44 pin package, 4 channels A/D for 40 pin package

◊ Timers: Timer 1 (T1) includes a watchdog timer programmable as a general purpose 16-bit timer

Ψ44/40 Packages: 44 pins for FN, FZ packages. 40 pins for N, JD, NJ (formerly N2), JC packages. Φ68/64 Packages: 68 pins for FN, FZ packages. 64 pins for NM, JN packages

## **SELECTION REFERENCE GUIDE**

|                                                                          |                              |           |                        |                    |                |                    |                    |                    |                |                    |                    |                    |                |                    |                    |                    |               |            |                |                |                |                |                |               | _             |

|--------------------------------------------------------------------------|------------------------------|-----------|------------------------|--------------------|----------------|--------------------|--------------------|--------------------|----------------|--------------------|--------------------|--------------------|----------------|--------------------|--------------------|--------------------|---------------|------------|----------------|----------------|----------------|----------------|----------------|---------------|---------------|

|                                                                          | OTP AND<br>REPROGRAMMABLE    | DEVICES   |                        | C756               | C756           | C756               | C758               | C758               | C759           | I                  | I                  | I                  | I              | I                  | I                  | I                  | I             |            | C768           | C768           | C769           | _              | _              | I             | I             |

|                                                                          | CLOCK<br>GENERATOR           |           |                        | ÷4 or PLL          | ÷4 or PLL      | ÷4 or PLL          | ÷4 or PLL          | ÷4 or PLL          | ÷4 or PLL      | ÷4                 | ÷4                 | PLL                | ÷4             | ÷4                 | ÷4                 | PLL                | ÷4            |            | ÷4 or PLL      | ÷4 or PLL      | ÷4 or PLL      | ÷4             | ÷4             | ÷4            | ÷4            |

| (F                                                                       | 0/1                          |           |                        | 55/53              | 22             | 55/53              | 55/53              | 55/53              | 55             | 55/53              | 55/53              | 55/53              | 55             | 55/53              | 22/23              | 55/53              | 22            |            | 22             | 22             | 55             | 22             | 99             | 99            | 55            |

| Sontinue                                                                 | A/D<br>CHANNELS              |           |                        | ADC1/8             | ADC1/8         | ADC1/8             | ADC1/8             | ADC1/8             | ADC1/8         | ADC1/8             | ADC1/8             | ADC1/8             | ADC1/8         | ADC1/8             | ADC1/8             | ADC1/8             | ADC1/8        |            | ADC1/8         | ADC1/8         | ADC1/8         | ADC1/8         | ADC1/8         | ADC1/8        | ADC1/8        |

| ırations ((                                                              | SERIAL<br>INTERFACE§         |           |                        | SPI/SCI1           | SPI/SC11       | SPI/SCI1           | SPI/SCI1           | SPI/SCI1           | SPI/SCI1       | SPI/SCI1           | SPI/SC11           | SPI/SC11           | SPI/SCI1       | SPI/SCI1           | SPI/SCI1           | SPI/SCI1           | SPI/SCI1      |            | SPI/SC11       | SPI/SCI1       | SPI/SCI1       | SPI/SCI1       | SPI/SCI1       | SPI/SCI1      | SPI/SCI1      |

| Table 4. TMS370 8-Bit Microcontroller Product Configurations (Continued) | TIMERS                       |           | (a)                    | T1/T2a             | T1/T2a         | T1/T2a             | T1/T2a             | T1/T2a             | T1/T2a         | T1/T2a             | T1/T2a             | T1/T2a             | T1/T2a         | T1/T2a             | T1/T2a             | T1/T2a             | T1/T2a        |            | T1/T2a/T2b     | T1/T2a/T2b     | T1/T2a/T2b     | T1/T2a/T2b     | T1/T2a/T2b     | T1/T2a/T2b    | T1/T2a/T2b    |

| r Produ                                                                  | OFF-<br>CHIP<br>MEM EXP      | (BYTES)   | TMS370Cx5x (CONTINUED) | 112K               | 112K           | 112K               | 64K                | 64K                | 20K            | 112K               | 64K                | 64K                | 20K            | 112K               | 64K                | 64K                | 20K           | TMS370Cx6x | 24K            | 24K            | 8K             | 24K            | 8K             | 24K           | 8K            |

| ntrolle                                                                  |                              | RAM       | 370Cx5x                | 512                | 512            | 512                | 1 024              | 1 024              | 3 584          | 512                | 1 024              | 1 024              | 3 584          | 512                | 1 024              | 1 024              | 3 584         | TMS3       | 1 024          | 1 024          | 3 584          | 1 024          | 3 584          | 1 024         | 3 584         |

| <b>licrocor</b>                                                          | DATA MEMORY<br>(BYTES)       | EEPROM    | TMS                    |                    | 512            | 512                |                    | 256                | 256            | 512                | 256                | 256                | 256            | 512                | 256                | 256                | 256           |            | 256            | 256            | 256            | 256            | 256            | 256           | 256           |

| 8-Bit N                                                                  | PROGRAM<br>MEMORY<br>(BYTES) | EPROM     |                        |                    |                |                    |                    |                    |                | 16K                | 32K                | 32K                | 48K            | 16K                | 32K                | 32K                | 48K           |            |                |                |                | 32K            | 48K            | 32K           | 48K           |

| <b>AS370</b>                                                             | PRO<br>MEN<br>(BY            | ROM       |                        | 16K                | 16K#           | 16K                | 32K                | 32K                | 48K            |                    |                    |                    |                |                    |                    |                    |               |            | 24K            | 32K            | 48K            |                |                |               |               |

| ble 4. TN                                                                | PACKAGE<br>PIN               | COUNT     |                        | 68/64 <sup>Ф</sup> | 89             | 68/64 <sup>Ф</sup> | 68/64 <sup>Ф</sup> | 68/64 <sup>Ф</sup> | 89             | 68/64 <sup>Ф</sup> | 68/64 <sup>Ф</sup> | 68/64 <sup>Ф</sup> | 89             | 68/64 <sup>Ф</sup> | 68/64 <sup>Ф</sup> | 68/64 <sup>Ф</sup> | 89            |            | 89             | 89             | 89             | 89             | 89             | 89            | 89            |

| Ta                                                                       | PACKAGE<br>OPTIONS           |           |                        | FN/NM              | Ę              | FN/NM              | FN/NM              | FN/NM              | Ę              | FN/NM              | MN/NH              | MN/NH              | Æ              | FZ/JN              | FZ/JN              | FZ/JN              | FZ            |            | Ä.             | Ä              | Æ              | ΝΉ             | FN             | FZ            | FZ            |

|                                                                          | PART NUMBER "yy"= PACKAGE    | .z. =TEMP |                        | TMS370C356Ayyz     | TMS370C456Ayyz | TMS370C056Ayyz     | TMS370C358Ayyz     | TMS370C058Ayyz     | TMS370C059Ayyz | TMS370C756Ayyz     | TMS370C758Ayyz     | TMS370C758Byyz     | TMS370C759Ayyz | SE370C756Ayyz      | SE370C758Ayyz      | SE370C758Byyz      | SE370C759Ayyz |            | TMS370C067Ayyz | TMS370C068Ayyz | TMS370C069Ayyz | TMS370C768Ayyz | TMS370C769Ayyz | SE370C768Ayyz | SE370C769Ayyz |

|                                                                          | DEVICE<br>TYPE‡              |           |                        | ROM                | ROM            | ROM                | ROM                | ROM                | ROM            | OTP                | - OTP              | OTP .              | . OTP          | UV-EPROM           | UV-EPROM           | UV-EPROM           | UV-EPROM      |            | ROM            | ROM .          | ROM            | OTP .          | OTP -          | UV-EPROM      | UV-EPROM      |

<sup>‡</sup> Temperatures: ROM device types have L = 0°C to +70°C, A = - 40°C to +85°C, and T = - 40°C to +105°C temperature options; ROM-less, OTP and UV-EPROM device types only have T.

<sup>§</sup> PACT SCI: PACT includes a mini-SCI. SCI1 module has 3-pin configuration while SCI2 module has 2-pin configuration.

II Max Freq: Supports maximum operating frequency of 3 MHz SYSCLK ♦ Timers: Timer 1 (T1) includes a watchdog timer programmable as a general purpose 16-bit timer Ф 68/64 Packages: 68 pins for FN, FZ packages. 64 pins for NM, JN packages

| (Continued)         |

|---------------------|

| Configurations (    |

| <b>ller Product</b> |

| crocontro           |

| 4. TMS370 8-Bit Mic |

| Table 4             |

| OTP AND REPROGRAMMABLE       | DEVICES   |            | C777               | I               |                 |            | C686           | C758 <sup>∆</sup> |                | I             |            | C792               | _                  |                     |            | C758 <sup>∆</sup> |            | C758*          |            | C6C2           | _              | _             |

|------------------------------|-----------|------------|--------------------|-----------------|-----------------|------------|----------------|-------------------|----------------|---------------|------------|--------------------|--------------------|---------------------|------------|-------------------|------------|----------------|------------|----------------|----------------|---------------|

| CLOCK                        |           |            | ÷4 or PLL          | ÷4              | ÷4              |            | ÷4 or PLL      | ÷4                | ÷4             | ÷4            |            | ÷4 or PLL          | ÷4                 | ÷4                  |            | ÷4 or PLL         |            | ÷4 or PLL      |            | ÷4 or PLL      | ÷4             | ÷4            |

| 8                            |           |            | 55/53              | 55/53           | 55/53           |            | 35             | 33                | 35             | 35            |            | 25                 | 25                 | 25                  |            | 34                |            | 55/53          |            | 22             | 22             | 22            |

| A/D<br>CHANNELS              |           |            | ADC1/8             | ADC1/8          | ADC1/8          |            |                |                   |                |               |            | ADC3/15            | ADC3/15            | ADC3/15             |            |                   |            | ADC1/8         |            | ADC2/4         | ADC2/4         | ADC2/4        |

| SERIAL<br>INTERFACES         |           |            |                    |                 |                 |            |                |                   |                |               |            |                    |                    |                     |            | SC11              |            |                |            | SCI2¥          | SCI2¥          | SCI2¥         |

| TIMERS                       |           |            | T1/T2a             | T1/T2a          | T1/T2a          |            | T1             | Τ1                | Τ1             | 11            |            | T1                 | T1                 | Τ1                  |            | T1/T2a            |            | T1             |            | T1             | T1             | T1            |

| OFF-CHIP<br>MEM EXP          | (BYIES)   | TMS370Cx7x |                    |                 |                 | TMS370Cx8x |                |                   |                |               | TMS370Cx9x |                    |                    |                     | TMS370CxAx |                   | TMS370CxBx |                | TMS370CxCx |                |                |               |

| MORY<br>S)                   | RAM       | TMS3       | 512                | 512             | 512             | TMS3       | 128            | 128               | 256            | 256           | TMS3       | 128                | 128                | 128                 | TMS3       | 512               | TMS3       | 384            | TMS3       | 128            | 128            | 128           |

| DATA MEMORY<br>(BYTES)       | EEPROM    |            | 256                | 256             | 256             |            |                | 256               |                |               |            | 256                | 256                | 256                 |            |                   |            | 256            |            |                |                |               |

| PROGRAM<br>MEMORY<br>(BYTES) | EPROM     |            |                    | 24K             | 24K             |            |                |                   | 16K            | 16K           |            |                    | 8K                 | 8K                  |            |                   |            |                |            |                | 8K             | 9K            |

| PRO(<br>MEN                  | ROM       |            | 24K                |                 |                 |            | ¥              | ¥                 |                |               |            | ¥                  |                    |                     |            | 24K               |            | 16K            |            | 4K             |                |               |

| PACKAGE<br>PIN COUNT         |           |            | 68/64 <sup>Ф</sup> | $_{\Phi}$ 49/89 | $_{\Phi}$ 49/89 |            | 44             | 40                | 44             | 44            |            | 44/40 <sup>Ψ</sup> | 44/40 <sup>Ψ</sup> | 44/40 <sup>\P</sup> |            | 40                |            | $68/64^{\Phi}$ |            | 28             | 28             | 28            |

| PACKAGE<br>OPTIONS           |           |            | FN/NM              | FN/NM           | FZ/JN           |            | FN             | z                 | ΝΉ             | FZ            |            | FN/NJ              | FN/NJ              | FZ/JC               |            | z                 |            | FN/NM          |            | FN/N           | FN/N           | FZ/JD         |

| PART NUMBER "yy" = PACKAGE   | .z. =1EMP |            | TMS370C077Ayyz     | TMS370C777Ayyz  | SE370C777Ayyz   |            | TMS370C380Ayyz | TMS370C080yyz     | TMS370C686Ayyz | SE370C686Ayyz |            | TMS370C090Ayyz     | TMS370C792yyz      | SE370C792yyz        |            | TMS370C3A7Ayyz    |            | TMS370C0B6Ayyz |            | TMS370C3C0Ayyz | TMS370C6C2Ayyz | SE370C6C2Ayyz |

| DEVICE<br>TYPE‡              |           |            | ROM                | ОТР             | UV-EPROM        |            | ROM            | ROM               | OTP            | UV-EPROM      |            | ROM                | OTP                | UV-EPROM            |            | ROM               |            | ROM            |            | ROM            | OTP            | UV-EPROM      |

† Packages: FN = PLCC, FZ = CLCC, N = PDIP, JD = CDIP, NJ = PSDIP (formerly N2), JC = CSDIP, NM = PSDIP, JN = CSDIP 1 = CSDIP 1 = CSDIP 1 = CSDIP 1 = CSDIP 2 = CSDIP 1 = CSDIP 2 = CSDIP 3 = CSDIP

§ PACT SCI: PACT includes a mini-SCI. SCI1 module has 3-pin configuration while SCI2 module has 2-pin configuration.

◊ Timers: Timer 1 (T1) includes a watchdog timer programmable as a general purpose 16-bit timer Ψ44/40 Packages: 44 pins for FN, FZ packages. 40 pins for N, JD, NJ (formerly N2), JC packages.

Φ68/64 Packages: 68 pins for FN, FZ packages. 64 pins for NM, JN packages

¥ TMS370CxCx SCI: Operable in asynchronous mode only

△ Converter Socket: Requires a TMDS37788OTP converter socket

\* Requires software modification [see the TMS370CxBx Data Sheet (literature number SPNS038)]

Template Release Date: 7-11-94

# **DEVELOPMENT SYSTEMS SUPPORT TOOLS**

|                                  | Table 5. TMS370 Development System Support Tools | <b>AS370</b> | Deve | lopme | nt Sys   | stem S | oddn       | t Tool   | S   |     |     |     |          |     |     |

|----------------------------------|--------------------------------------------------|--------------|------|-------|----------|--------|------------|----------|-----|-----|-----|-----|----------|-----|-----|

| DEVELOPMENT TOOL<br>DESCRIPTION  | PART NUMBER                                      | ×0×          | x1x  | x2x   | x32      | x36    | ×4×        | x5x      | ×9× | x7x | x8x | х6х | хАх      | xBx | ×CX |

| Assembler/Linker (PC)            | TMDS3740850-02                                   | ٧            | ٧    | Λ     | ^        | Λ      | $\nearrow$ | Λ        | ^   | ٧   | ٧   | Λ   | Λ        | Λ   | Λ   |

| C-Compiler, Assem/Link (PC)      | TMDS3740855-02                                   | ٨            | ٨    | Λ     | Λ        | Λ      | Λ          | Λ        | ^   | ٨   | Λ   | Λ   | Λ        | Λ   | Λ   |

| C-Compiler, Assem/Link (WS)      | TMDS3740555-09                                   | ٧            | ٧    | Λ     | $\wedge$ | Λ      | $\nearrow$ | $\wedge$ | Λ   | ٧   | ٧   | Λ   | $\wedge$ | ^   | ^   |

| TMS370 Starter Kit               | TMDS37000                                        | ٧            | ٧    | Λ     | Λ        | -      | Λ          | Λ        | Λ   | ٧   | -   | 1   | Λ        | Λ   | ı   |

| TMS370 Design Kit                | TMDS3770110                                      | ٨            | ٨    |       | I        | _      | 1          | Λ        | Ι   | -   | _   | -   | 1        | -   | 1   |

| TMS370 Compact Development Tool  |                                                  |              |      |       |          |        |            |          |     |     |     |     |          |     |     |

| CDT370                           | EDSCDT370                                        | >            | >    | >     | I        | I      | >          | >        | ı   | ı   | >   | I   | >        | ı   | >   |

| CDT370 PACT                      | EDSCDT37P                                        | I            | I    | I     | >        | >      | I          | I        | I   | I   | I   | >   | I        | ı   | I   |