**ESS Technology, Inc.****ES7020**

## Vantage-II Audio/Video Codec Product Brief

### DESCRIPTION

The ES7020 Vantage™-II codec is a highly integrated superior performance chip that combines an advanced MPEG-2 decoder with a sophisticated MPEG-2 encoder and an NTSC/PAL encoder. The ES7020 provides time base correction (TBC) for recording from VCR videocassette tapes with weak signals without loss of synchronization, low delay monitoring of decoded video output signal, ATAPI interface, built-in CPRM encode/decode, state-of-the-art progressive-scan video, and S/PDIF input and output support.

The MPEG encoder portion does flexible NTSC or PAL encoding on a YUV 4:2:2 stream in response to firmware control of the internal CPU. The internal CPU, in conjunction with an additional hardware accelerator, allows for very flexible encoding and allows for additional functionality to be easily added. An audio DSP engine facilitates the encoding of MPEG-1 layer 2 audio while the host CPU interface unit allows for easy reading of close caption data. In addition, the ES7020 has inverse 3:2 pull-down capability, allowing it to dynamically analyze incoming fields and compress from 60 fields to 24 frames in the case of film material.

The MPEG decoder portion is built on the ESS proprietary dual CPU Programmable Multimedia Processor (PMP), consisting of a 32-bit RISC processor and a 64-bit vector engine. This architecture is extremely programmable and allows for the best DVD feature set. The RISC processor performs bit stream parsing, transfers data to the vector engine, and manages the chip as a whole.

The vector engine performs all the computationally intensive tasks required by applications such as Dolby® Digital, DTS Surround™, and MPEG and JPEG imaging. These tasks include video motion compensation and estimation, loop filtering, discrete and inverse discrete cosine transforms (DCT/IDCT), quantization, and inverse quantization.

The ES7020 with DTS support is offered with the ES7020D, which has the same pinout as the standard ES7020. The ES7020 and ES7020D are available in an industry-standard 388-pin BGA package.

### FEATURES

- MPEG-2 video encoding up to MP@ML.

- Constant and variable bit rate (CBR/VBR) encoding.

- Inverse 3:2 pull-down.

- Built-in time base corrector (TBC).

- Frame mode and field mode encoding.

- Vertical blanking interval (VBI) data slicer.

- CPRM encryption.

- ATAPI Interface with control for up to two storage media devices, such as hard disk drives, A/V recordable loaders, and Flash memory cards.

- 4x-8x high speed archiving over ATAPI interface to storage media, such as a hard disk drive to DVD+RW or DVD-RW disc.

- Real time clock.

- On-chip modem with integrated low voltage DAA.

- Integrated NTSC/PAL encoder with pixel-adaptive de-interlacer and five 10-bit 54MHz video DACs.

- High-quality progressive scan video output for flicker-free video display.

- DVD-Video, DVD-VR, VCD and SVCD playback.

- Media playback with CD-ROM, CD-R/RW, DVD-R/RW, DVD+R/RW, and DVD-RAM.

- Up to 7.1 channel audio outputs.

- Bass management.

- Direct 8/16-bit SDRAM interface up to 16 MB capacity.

- Macrovision 7.1 for NTSC/PAL interlaced video or progressive (480p/576p) video.

- Composite, S-video, and CCIR656 video outputs.

- OSD graphics plane with 256 colors and eight levels of transparency.

- ESS Music Slideshow™

- S/PDIF digital audio input and output.

- MP3, MPEG AAC, and WMA digital audio decoding.

- Dolby Digital, Dolby Pro Logic™, Pro Logic II digital audio decoding.

- DTS Surround and DTS ES digital audio decoding (ES7020D only).

- Lead-free leads using 98%-Sn/2%-Cu or 98%-Sn/2%-Bi.

## PINOUT (A1 TO N13)

The pinout diagram for the decoder TDM interface, and for part of the decoder SDRAM, clock, and decoder RISC interfaces of the ES7020, appears in Figure 1.

The pound symbol (#) denotes an active-low signal. The rest of the ES7020 device pinout appears in Figure 2, Figure 3 and Figure 4.

|   | 1      | 2      | 3      | 4       | 5    | 6      | 7   | 8   | 9    | 10       | 11       | 12       | 13       |

|---|--------|--------|--------|---------|------|--------|-----|-----|------|----------|----------|----------|----------|

| A | VSS    | VSS    | LD6    | LD8     | LD11 | LD15   | LA1 | LA5 | LA9  | LA12     | LA14     | LA16     | LA18     |

| B | LD5    | VSS    | LD7    | LD9     | LD13 | LOE#   | LA2 | LA6 | LA10 | LA13     | LA15     | LA17     | LA19     |

| C | LD4    | LD3    | VSS    | LD10    | LD12 | LA0    | LA3 | LA7 | LA11 | AVDD_PLL | AVDD_PLL | AVSS_PLL | AVDD_PLL |

| D | LD0    | LD1    | LD2    | VSS     | LD14 | VDD1.5 | LA4 | LA8 | VSS  | AVSS_PLL | VDD3.3   | VDD1.5   | AVDD_PLL |

| E | TDMFS  | TDMMDR | TDMDX  | TDMTSC# |      |        |     |     |      |          |          |          |          |

| F | TBCK   | MCLK   | TDMCLK | VDD3.3  |      |        |     |     |      |          |          |          |          |

| G | DCS0#  | DSCK   | NC     | CLK     |      |        |     |     |      |          |          |          |          |

| H | DRAS1# | DRAS0# | DCS1#  | VSS     |      |        |     |     |      |          |          |          |          |

| J | DOE#   | DWE#   | DCAS#  | DRAS2#  |      |        |     |     |      |          |          |          |          |

| K | DB13   | DB14   | DB15   | DQM     |      |        |     |     |      |          |          |          |          |

| L | DB10   | DB11   | DB12   | VDD1.5  |      |        |     |     |      |          |          |          |          |

| M | DB6    | DB7    | DB8    | DB9     |      |        |     |     |      |          |          |          |          |

| N | DB2    | DB3    | DB4    | VSS     |      |        |     |     |      |          |          |          |          |

|   |        |        |        |         |      |        |     |     |      | 11       | 12       | 13       |          |

| L |        |        |        |         |      |        |     |     |      | VSS      | VSS      | VSS      |          |

| M |        |        |        |         |      |        |     |     |      | VSS      | VSS      | VSS      |          |

| N |        |        |        |         |      |        |     |     |      | VSS      | VSS      | VSS      |          |

Figure 1 ES7020 Device Pinout (A1 to N13)

## PINOUT (P1 TO AF13)

The pinout diagram for the auxiliary port interface, and for part of the decoder audio and video, decoder SDRAM, decoder host, modem, and decoder S/PDIF audio interfaces of the ES7020, appears in Figure 2.

The pound symbol (#) denotes an active-low signal. The rest of the ES7020 device pinout appears in Figure 1, Figure 3 and Figure 4.

|    |          |          |            |        |      |        |      |       |      |      |        |     |

|----|----------|----------|------------|--------|------|--------|------|-------|------|------|--------|-----|

| P  | DMA11    | DB0      | DB1        | DB5    |      |        |      |       |      |      |        |     |

| R  | DMA8     | DMA9     | DMA10      | VDD1.5 |      |        |      |       |      |      |        |     |

| T  | DMA5     | DMA6     | DMA7       | VDD1.5 |      |        |      |       |      |      |        |     |

| U  | DMA1     | DMA2     | DMA3       | DMA4   |      |        |      |       |      |      |        |     |

| V  | TSD0     | TWS      | DMA0       | VSS    |      |        |      |       |      |      |        |     |

| W  | RBCK     | TSD3     | TSD2       | TSD1   |      |        |      |       |      |      |        |     |

| Y  | MODEM_CS | SPDIF_IN | RSD        | RWS    |      |        |      |       |      |      |        |     |

| AA | CAMIN1   | CAMINO   | PCLK_2XSCN | VDD3.3 |      |        |      |       |      |      |        |     |

| AB | YUV2     | YUV1     | YUV0       | CAMIN3 |      |        |      |       |      |      |        |     |

| AC | YUV5     | YUV4     | YUV3       | VSS    | YDAC | VDD1.5 | UDAC | VSS   | AUX7 | AUX6 | VDD3.3 | HD0 |

| AD | YUV7     | YUV6     | VSS        | AVSS   | AVDD | AVSS   | AVDD | AVDD  | AUX5 | AUX2 | HD1    | HD4 |

| AE | VSS      | VSS      | VDAC       | AVDD   | AVDD | RSET2  | VREF | RSET1 | AVSS | AUX4 | AUX1   | HD2 |

| AF | VSS      | FDAC     | AVSS       | CDAC   | AVSS | AVDD   | AVSS | AVDD  | AVSS | AUX3 | AUX0   | HD3 |

|    | 1        | 2        | 3          | 4      | 5    | 6      | 7    | 8     | 9    | 10   | 11     | 12  |

|    |          |          |            |        |      |        |      |       |      |      |        | 13  |

Figure 2 ES7020 Device Pinout (P1 to AF13)

## PINOUT (A14 TO N26)

The pinout diagram for the clock and JTAG interfaces, and for part of the decoder video, encoder input, PLL, RISC, and encoder SDRAM interfaces of the ES7020, appears in Figure 3.

The pound symbol (#) denotes an active-low signal. The rest of the ES7020 device pinout appears in Figure 1, Figure 2 and Figure 4.

| 14       | 15       | 16     | 17       | 18        | 19     | 20        | 21     | 22       | 23     | 24     | 25        | 26        |   |

|----------|----------|--------|----------|-----------|--------|-----------|--------|----------|--------|--------|-----------|-----------|---|

| LA20     | LWRHL#   | LCS3#  | LCS1#    | PCLK QSCN | HSYNC# | TMS       | TMC1   | AIMCLK   | RSVD   | AILRCK | VIFLD     | VSS       | A |

| LA21     | LWRLL#   | LCS2#  | LCS0#    | VSYNC#    | TRST   | TDO       | TDI    | TMC2     | AIBD   | AIBCK  | VSS       | VSS       | B |

| AVSS_PLL | AVSS_PLL | VID_XO | AVDD_PLL | AVDD_PLL  | TCK    | PSTOP     | RSVD   | CS2      | VBAT   | VSS    | VI VSYNC# | VI HSYNC# | C |

| VSS      | VID_XI   | VDD1.5 | AVSS_PLL | AVSS_PLL  | VSS    | OSC32 OUT | VDD3.3 | OSC32 IN | VSS    | RESET# | VIN0      | VIN1      | D |

|          |          |        |          |           |        |           |        |          | VIN2   | VIN3   | VIN4      | VIN5      | E |

|          |          |        |          |           |        |           |        |          | VDD3.3 | VIN6   | VIN7      | VICLK     | F |

|          |          |        |          |           |        |           |        |          | MDQM   | MWE#   | MCAS#     | MRAS#     | G |

|          |          |        |          |           |        |           |        |          | MCS#   | MCKE   | MEMCLK    | MD0       | H |

|          |          |        |          |           |        |           |        |          | VSS    | MD1    | MD2       | MD3       | J |

|          |          |        |          |           |        |           |        |          | MD4    | MD5    | MD6       | MD7       | K |

| 14       | 15       | 16     |          |           |        |           |        |          | VDD1.5 | MD8    | MD9       | MD10      | L |

| VSS      | VSS      | VSS    | L        |           |        |           |        |          | VDD1.5 | MD11   | MD12      | MD13      | M |

| VSS      | VSS      | VSS    | M        |           |        |           |        |          | MD14   | MD15   | MD16      | MD17      | N |

| VSS      | VSS      | VSS    | N        |           |        |           |        |          |        |        |           |           |   |

Figure 3 ES7020 Device Pinout (A14 to N26)

## PINOUT (P14 TO AF26)

The pinout diagram for the decoder ATAPI, decoder GPIO and test interfaces, and for part of the encoder SDRAM, decoder host, and decoder S/PDIF audio interfaces of the ES7020, appears in Figure 4.

The pound symbol (#) denotes an active-low signal. The rest of the ES7020 device pinout appears in Figure 1, Figure 2 and Figure 3.

|      |      |         |         |          |          |       |           |         |           |        |       |       |    |

|------|------|---------|---------|----------|----------|-------|-----------|---------|-----------|--------|-------|-------|----|

| VSS  | VSS  | VSS     | P       | VSS      | MD18     | MD19  | MD20      | P       |           |        |       |       |    |

| VSS  | VSS  | VSS     | R       | MD21     | MD22     | MD23  | MD24      | R       |           |        |       |       |    |

| VSS  | VSS  | VSS     | T       | VDD1.5   | MD25     | MD26  | MD27      | T       |           |        |       |       |    |

| 14   | 15   | 16      |         | MD28     | MD29     | MD30  | MD31      | U       |           |        |       |       |    |

|      |      |         |         | MA0      | MA1      | MA2   | MA3       | V       |           |        |       |       |    |

|      |      |         |         | VSS      | MA4      | MA5   | MA6       | W       |           |        |       |       |    |

|      |      |         |         | MA7      | MA8      | MA9   | MA10      | Y       |           |        |       |       |    |

|      |      |         |         | VDD3.3   | MA11     | MA12  | MA13      | AA      |           |        |       |       |    |

|      |      |         |         | GPIO0    | GPIO1    | GPIO2 | GPIO3     | AB      |           |        |       |       |    |

| HD7  | HD11 | VDD1.5  | HDD_IRQ | VSS      | HDD_CS#  | HRST# | VDD3.3    | HCS1FX# | VSS       | GPIO4  | GPIO5 | GPIO6 | AC |

| HD8  | HD12 | HD15    | HDD_DRQ | DVD_WR#  | HDD_WR#  | HRD#  | RSVD      | HCS3FX# | HA1       | VSS    | GPIO7 | GPIO8 | AD |

| HD9  | HD13 | DVD_IRQ | HIORDY  | DVD_RD#  | HDD_RD#  | HWR#  | HWRQ#     | HIRQ    | HA2       | GPIO11 | VSS   | GPIO9 | AE |

| HD10 | HD14 | DVD_DRQ | DVD_CS# | DVD_ACK# | HDD_ACK# | HRRQ# | HIO_CS16# | HA0     | SPDIF_OUT | GPIO10 | VSS   | VSS   | AF |

| 14   | 15   | 16      | 17      | 18       | 19       | 20    | 21        | 22      | 23        | 24     | 25    | 26    |    |

Figure 4 ES7020 Device Pinout (P14 to AF26)

## SYSTEM BLOCK DIAGRAM

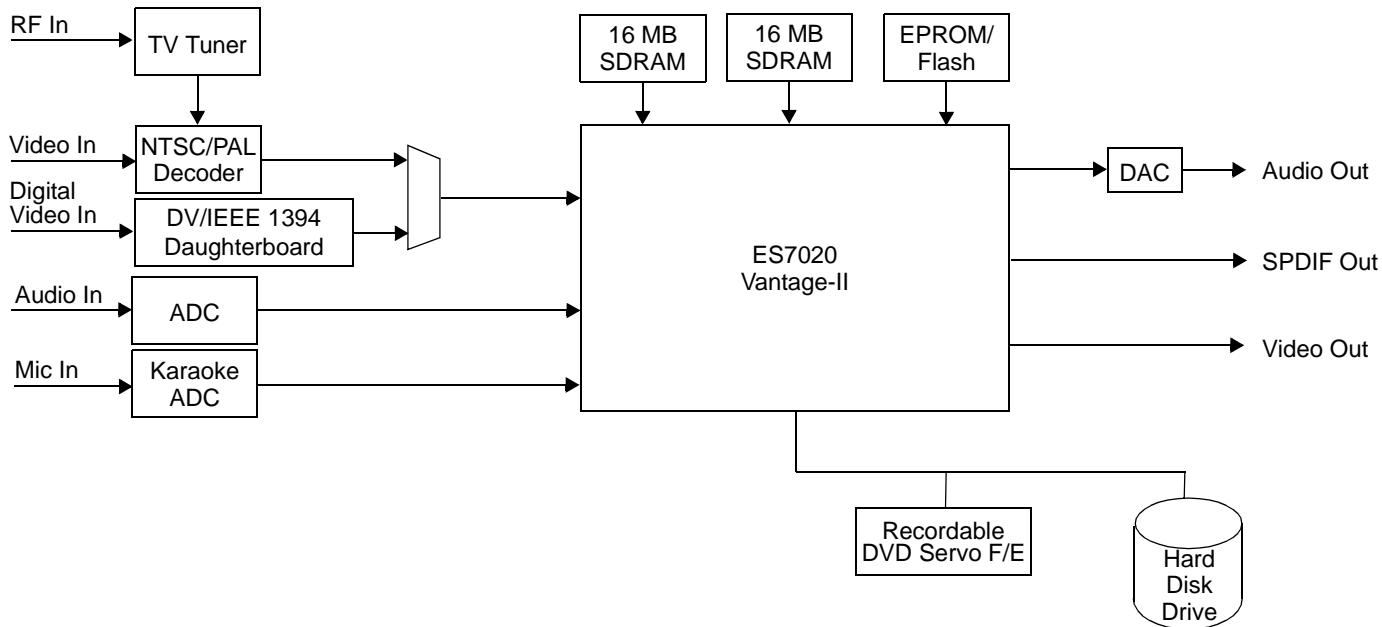

Figure 5 depicts a sample ES7020-based system block diagram.

Figure 5 ES7020 System Block Diagram

## ORDERING INFORMATION

| Part Number | Description                                                 | Package     |

|-------------|-------------------------------------------------------------|-------------|

| ES7020BF    | Vantage-II A/V Codec with lead-free leads.                  | 388-pin BGA |

| ES7020BDF   | Vantage-II Audio/Video Codec with DTS with lead-free leads. | 388-pin BGA |

The letter B at the end of the part number identifies the package type BGA. The letter F indicates lead-free leads.

**ESS Technology, Inc.**

**48401 Fremont Blvd.**

**Fremont, CA 94538**

**Tel: (510) 492-1088**

**Fax: (510) 492-1898**

No part of this publication may be reproduced, stored in a retrieval system, transmitted, or translated in any form or by any means, electronic, mechanical, manual, optical, or otherwise, without the prior written permission of ESS Technology, Inc.

ESS Technology, Inc. makes no representations or warranties regarding the content of this document.

All specifications are subject to change without prior notice.

ESS Technology, Inc. assumes no responsibility for any errors contained herein.

(P) U.S. Patent pending.

All other trademarks are owned by their respective holders and are used for identification purposes only.