October 2003 Revised March 2005

FIN1217 • FIN1218 • FIN1215 • FIN1216

### LVDS 21-Bit Serializers/De-Serializers

### **General Description**

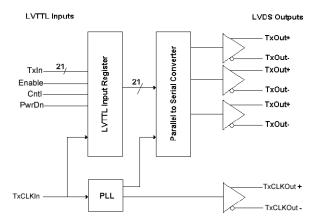

The FIN1217 and FIN1215 transform 21-bit wide parallel LVTTL (Low Voltage TTL) data into 3 serial LVDS (Low Voltage Differential Signaling) data streams. A phase-locked transmit clock is transmitted in parallel with the data stream over a separate LVDS link. Every cycle of transmit clock 21 bits of input LVTTL data are sampled and transmitted.

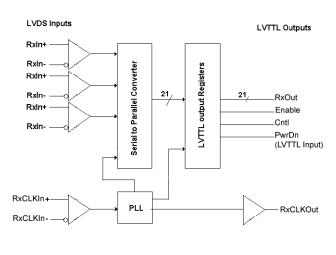

The FIN1218 and FIN1216 receive and convert the 3 serial LVDS data streams back into 21 bits of LVTTL data. Refer to Table 1 for a matrix summary of the Serializers and Deserializers available. For the FIN1217, at a transmit clock frequency of 85 MHz, 21 bits of LVTTL data are transmitted at a rate of 595 Mbps per LVDS channel.

These chipsets are an ideal solution to solve EMI and cable size problems associated with wide and high-speed TTL interfaces.

#### **Features**

- Low power consumption

- 20 MHz to 85 MHz shift clock support

- 50% duty cycle on the clock output of receiver

- ±1V common-mode range around 1.2V

- Narrow bus reduces cable size and cost

- High throughput (up to 1.785 Gbps throughput)

- Up to 595 Mbps per channel

- Internal PLL with no external component

- Compatible with TIA/EIA-644 specification

- Devices are offered in 48-lead TSSOP packages

#### **Ordering Code:**

| Order Number               | Package<br>Number | Package Description                                                                 |

|----------------------------|-------------------|-------------------------------------------------------------------------------------|

| FIN1215MTD                 | MTD48             | 48-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 6.1mm Wide         |

| FIN1215MTDX_NL<br>(Note 1) | MTD48             | Pb-Free 48-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 6.1mm Wide |

| FIN1216MTD                 | MTD48             | 48-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 6.1mm Wide         |

| FIN1216MTDX_NL<br>(Note 1) | MTD48             | Pb-Free 48-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 6.1mm Wide |

| FIN1217MTD                 | MTD48             | 48-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 6.1mm Wide         |

| FIN1218MTD                 | MTD48             | 48-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 6.1mm Wide         |

Devices also available in Tape and Reel. Specify by appending suffix letter "X" to the ordering code.

Note 1: "\_NL" indicates Pb-Free package (per JEDEC J-STD-020B). Device available in Tape and Reel only.

TABLE 1. Serializers/De-Serializers Chip Matrix

| Part    | CLK Frequency | LVTTL IN | LVDS OUT | LVDS IN | LVTTL OUT | Package  |

|---------|---------------|----------|----------|---------|-----------|----------|

| FIN1217 | 85            | 21       | 3        |         |           | 48 TSSOP |

| FIN1218 | 85            |          |          | 3       | 21        | 48 TSSOP |

| FIN1215 | 66            | 21       | 3        |         |           | 48 TSSOP |

| FIN1216 | 66            |          |          | 3       | 21        | 48 TSSOP |

# **Block Diagrams**

#### Transmitter Functional Diagram for FIN1217 and FIN1215

Receiver Functional Diagram for FIN1218 and FIN1216

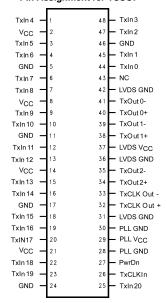

#### **Transmitters**

#### **Pin Descriptions**

| Pin Names            | I/O Type | Number of Pins | Description of Signals                                    |

|----------------------|----------|----------------|-----------------------------------------------------------|

| TxIn                 | I        | 21             | LVTTL Level Inputs                                        |

| TxCLKIn              | I        | 1              | LVTTL Level Clock Input                                   |

|                      |          |                | The rising edge is for data strobe.                       |

| TxOut+               | 0        | 3              | Positive LVDS Differential Data Output                    |

| TxOut-               | 0        | 3              | Negative LVDS Differential Data Output                    |

| TxCLKOut+            | 0        | 1              | Positive LVDS Differential Clock Output                   |

| TxCLKOut-            | 0        | 1              | Negative LVDS Differential Clock Output                   |

| PwrDn                | I        | 1              | LVTTL Level Power-Down Input                              |

|                      |          |                | Assertion (LOW) puts the outputs in high-impedance state. |

| PLL V <sub>CC</sub>  | I        | 1              | Power Supply Pin for PLL                                  |

| PLL GND              | I        | 2              | Ground Pins for PLL                                       |

| LVDS V <sub>CC</sub> | I        | 1              | Power Supply Pin for LVDS Outputs                         |

| LVDS GND             | I        | 3              | Ground Pins for LVDS Outputs                              |

| V <sub>CC</sub>      | I        | 4              | Power Supply Pins for LVTTL Inputs                        |

| GND                  | I        | 5              | Ground pins for LVTTL Inputs                              |

| NC                   |          |                | No Connect                                                |

# **Connection Diagram**

# FIN1217 and FIN1215 (21:3 Transmitter) Pin Assignment for TSSOP

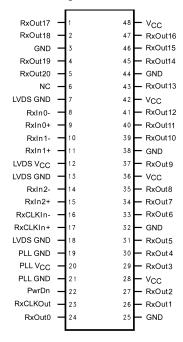

#### **Receivers**

#### **Pin Descriptions**

| Pin Names            | I/O Type | Number<br>of<br>Pins | Description of Signals                                                                               |

|----------------------|----------|----------------------|------------------------------------------------------------------------------------------------------|

| RxIn                 | I        | 3                    | Negative LVDS Differential Data Inputs                                                               |

| RxIn+                | I        | 3                    | Positive LVDS Differential Data Inputs                                                               |

| RxCLKIn-             | ı        | 1                    | Negative LVDS Differential Clock Input                                                               |

| RxCLKIn+             | I        | 1                    | Positive LVDS Differential Clock Input                                                               |

| RxOut                | 0        | 21                   | LVTTL Level Data Outputs<br>Goes HIGH for PwrDn LOW                                                  |

| RxCLKOut             | 0        | 1                    | LVTTL Clock Output                                                                                   |

| PwrDn                | I        | 1                    | LVTTL Level Input<br>Refer to Transmitter and Receiver Power-Up and Power-Down Operation Truth Table |

| PLL V <sub>CC</sub>  | I        | 1                    | Power Supply Pin for PLL                                                                             |

| PLL GND              | I        | 2                    | Ground Pins for PLL                                                                                  |

| LVDS V <sub>CC</sub> | I        | 1                    | Power Supply Pin for LVDS Inputs                                                                     |

| LVDS GND             | I        | 3                    | Ground Pins for LVDS Inputs                                                                          |

| V <sub>CC</sub>      | I        | 4                    | Power Supply for LVTTL Outputs                                                                       |

| GND                  | I        | 5                    | Ground Pins for LVTTL Outputs                                                                        |

| NC                   |          |                      | No Connect                                                                                           |

### **Connection Diagram**

#### FIN1218 and FIN1216 (3:21 Receiver) Pin Assignment for TSSOP

### **Truth Tables**

#### **Transmitter Truth Table**

|        | Inputs  | Outputs        |        |            |

|--------|---------|----------------|--------|------------|

| TxIn   | TxCLKIn | PwrDn (Note 2) | TxOut± | TxCLKOut±  |

| Active | Active  | Н              | L/H    | L/H        |

| Active | L/H/Z   | Н              | L/H    | X (Note 3) |

| F      | Active  | Н              | L      | L/H        |

| F      | F       | Н              | L      | X (Note 3) |

| Х      | Х       | L              | Z      | Z          |

H = HIGH Logic Level

- L = LOW Logic Level

- X = Don't Care

- Z = High Impedance

- F = Floating

$\textbf{Note 2:} \ \text{The outputs of the transmitter or receiver will remain in a High Impedance state until V}_{\text{CC}} \ \text{reaches 2V}.$

Note 3: TxCLKOut± will settle at a free running frequency when the part is powered up, PwrDn is HIGH and the TxCLKIn is a steady logic level (L/H/Z).

#### **Receiver Truth Table**

|            | Inputs     | Outputs        |            |          |

|------------|------------|----------------|------------|----------|

| RxIn±      | RxCLKIn±   | PwrDn (Note 4) | RxOut      | RxCLKOut |

| Active     | Active     | Н              | L/H        | L/H      |

| Active     | F (Note 5) | Н              | Р          | Н        |

| F (Note 5) | Active     | Н              | Н          | L/H      |

| F (Note 5) | F (Note 5) | Н              | P (Note 6) | Н        |

| Х          | Х          | L              | L          | Н        |

H = HIGH Logic Level

- L = LOW Logic Level

- P = Last Valid State

- X = Don't Care

- Z = High Impedance F = Failsafe Condition

$\textbf{Note 4:} \ \ \text{The outputs of the transmitter or receiver will remain in a High Impedance state until V_{CC}\ reaches\ 2V.$

Note 5: Failsafe condition is defined as the input being terminated and un-driven (Z) or shorted or open.

Note 6: If RxCLKIn± is removed prior to the RxIn± data being removed, RxOut will be the last valid state. If RxIn± data is removed prior to RxCLKIn± being removed, RxOut will be HIGH.

#### **Absolute Maximum Ratings**(Note 7)

#### **Recommended Operating Conditions**

Power Supply Voltage (V<sub>CC</sub>) -0.3V to +4.6V TTL/CMOS Input/Output Voltage -0.5V to +4.6VLVDS Input/Output Voltage -0.3V to +4.6V LVDS Output Short Circuit Current (I<sub>OSD</sub>) Continuous

Storage Temperature Range (T<sub>STG</sub>) -65°C to +150°C Maximum Junction Temperature (T<sub>1</sub>) 150°C

Lead Temperature (T<sub>L</sub>) (Soldering, 4 seconds)

ESD Rating (HBM, 1.5 k $\Omega$ , 100 pF)

LVDS I/O to GND >10.0 kV All Pins (FIN1215, FIN1217 only) >6.5 kV

(FIN1215, FIN1217 only)

ESD Rating (MM, 0Ω, 200 pF) >400V Supply Voltage (V<sub>CC</sub>) 3.0V to 3.6V Operating Temperature (T<sub>A</sub>)(Note 7) -40°C to +85°C

Maximum Supply Noise Voltage

(V<sub>CCNPP</sub>) 100 mV<sub>P-P</sub> (Note 8)

Note 7: Absolute maximum ratings are DC values beyond which the device may be damaged or have its useful life impaired. The datasheet specifications should be met, without exception, to ensure that the system design is reliable over its power supply, temperature, and output/input loading variables. Fairchild does not recommend operation outside datasheet specifi-

Note 8: 100mV  $V_{CC}$  noise should be tested for frequency at least up to 2 MHz. All the specification below should be met under such a noise.

#### **Transmitter DC Electrical Characteristics**

Over supply voltage and operating temperature ranges, unless otherwise specified. (Note 9)

260°C

| Symbol             | Parameter                                                      | Test Conditions                   |          | Min   | Тур   | Max             | Units |

|--------------------|----------------------------------------------------------------|-----------------------------------|----------|-------|-------|-----------------|-------|

| Transmitt          | er LVTTL Input Characteristics                                 |                                   | •        |       |       |                 |       |

| V <sub>IH</sub>    | Input High Voltage                                             |                                   |          | 2.0   |       | V <sub>CC</sub> | V     |

| V <sub>IL</sub>    | Input Low Voltage                                              |                                   |          | GND   |       | 0.8             | V     |

| V <sub>IK</sub>    | Input Clamp Voltage                                            | I <sub>IK</sub> = -18 mA          |          |       | -0.79 | -1.5            | V     |

| I <sub>IN</sub>    | Input Current                                                  | $V_{IN} = 0.4V$ to 4.6V           |          |       | 1.8   | 10.0            | ^     |

|                    |                                                                | V <sub>IN</sub> = GND             |          | -10.0 | 0     |                 | μА    |

| Transmitt          | er LVDS Output Characteristics (Note 10)                       | •                                 |          |       | •     | •               |       |

| V <sub>OD</sub>    | Output Differential Voltage                                    |                                   |          | 250   |       | 450             | mV    |

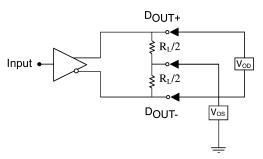

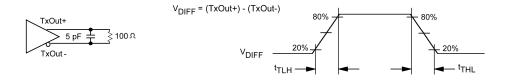

| $\Delta V_{OD}$    | V <sub>OD</sub> Magnitude Change from Differential LOW-to-HIGH | $R_L = 100 \Omega$ , See Figure 1 |          |       |       | 35.0            | mV    |

| Vos                | Offset Voltage                                                 |                                   |          | 1.125 | 1.25  | 1.375           | V     |

| ΔV <sub>OS</sub>   | Offset Magnitude Change from Differential LOW-to-HIGH          |                                   |          |       |       |                 | mV    |

| Ios                | Short Circuit Output Current                                   | V <sub>OUT</sub> = 0V             |          |       | -3.5  | -5.0            | mA    |

| I <sub>OZ</sub>    | Disabled Output Leakage Current                                | DO = 0V to 4.6V, Pwr              | Dn = 0V  |       | ±1.0  | ±10.0           | μА    |

| Transmitt          | er Supply Current                                              |                                   | •        |       |       |                 |       |

| I <sub>CCWT</sub>  | 21:3 Transmitter Power Supply Current                          |                                   | 33.0 MHz |       | 28.0  | 46.2            |       |

|                    | for Worst Case Pattern (With Load)                             | $R_L = 100 \Omega$ , $40.0 MHz$   |          |       | 29.0  | 51.7            | mA    |

|                    | (Note 11), (Note 12)                                           | See Figure 3 65.0 MHz             |          |       | 34.0  | 57.2            | IIIA  |

|                    | (85.0 MHz Specification for FIN1217 only)                      |                                   | 85.0 MHz |       | 39.0  | 62.7            |       |

| I <sub>CCPDT</sub> | Powered Down Supply Current                                    | PwrDn = 0.8V                      |          |       | 10.0  | 55.0            | μА    |

Note 9: All Typical values are at  $T_A = 25$  °C and with  $V_{CC} = 3.3$ V.

Note 10: Positive current values refer to the current flowing into device and negative values means current flowing out of pins. Voltage are referenced to ground unless otherwise specified (except  $\Delta V_{OD}$  and  $V_{OD}$ ).

Note 11: The power supply current for both transmitter and receiver can be different with the number of active I/O channels.

Note 12: The 16-grayscale test pattern tests device power consumption for a "typical" LCD display pattern. The test pattern approximates signal switching needed to produce groups of 16 vertical strips across the display.

#### **Transmitter AC Electrical Characteristics**

Over supply voltage and operating temperature ranges, unless otherwise specified.

| Symbol             | Parameter                                            | Test Conditions                                       | Min     | Тур  | Max     | Units |

|--------------------|------------------------------------------------------|-------------------------------------------------------|---------|------|---------|-------|

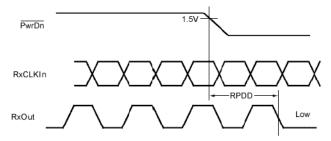

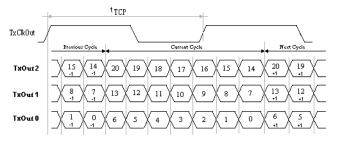

| t <sub>TCP</sub>   | Transmit Clock Period                                |                                                       | 11.76   | T    | 50.0    | ns    |

| t <sub>TCH</sub>   | Transmit Clock (TxCLKIn) HIGH Time                   | See Figure 6                                          | 0.35    | 0.5  | 0.65    | Т     |

| t <sub>TCL</sub>   | Transmit Clock Low Time                              |                                                       | 0.35    | 0.5  | 0.65    | Т     |

| t <sub>CLKT</sub>  | TxCLKIn Transition Time (Rising and Failing)         | (10% to 90%) See Figure 7                             | 1.0     |      | 6.0     | ns    |

| t <sub>JIT</sub>   | TxCLKIn Cycle-to-Cycle Jitter                        |                                                       |         |      | 3.0     | ns    |

| t <sub>XIT</sub>   | TxIn Transition Time                                 |                                                       | 1.5     |      | 6.0     | ns    |

| LVDS Trans         | mitter Timing Characteristics                        | •                                                     |         |      |         |       |

| t <sub>TLH</sub>   | Differential Output Rise Time (20% to 80%)           | See Figure 4                                          |         | 0.75 | 1.5     | ns    |

| t <sub>THL</sub>   | Differential Output Fall Time (80% to 20%)           | See Figure 4                                          |         | 0.75 | 1.5     | ns    |

| t <sub>STC</sub>   | TxIn Setup to TxCLNIn                                | See Figure 6                                          | 2.5     |      |         | ns    |

| t <sub>HTC</sub>   | TxIn Holds to TCLKIn                                 | (f = 85 MHz) (FIN1217 only)                           | 0       |      |         | ns    |

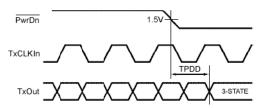

| t <sub>TPDD</sub>  | Transmitter Power-Down Delay                         | See Figure 13, (Note 13)                              |         |      | 100     | ns    |

| t <sub>TCCD</sub>  | Transmitter Clock Input to Clock Output Delay        | See Figure 9                                          |         |      | 5.5     |       |

|                    | Transmitter Clock Input to Clock Output Delay        | $(T_A = 25^{\circ}C \text{ and with } V_{CC} = 3.3V)$ | 2.8     |      | 6.8     | ns    |

| Transmitter        | Output Data Jitter (f = 40 MHz) (Note 14)            | 1                                                     |         |      |         |       |

| t <sub>TPPB0</sub> | Transmitter Output Pulse Position of Bit 0           |                                                       | -0.25   | 0    | 0.25    | ns    |

| t <sub>TPPB1</sub> | Transmitter Output Pulse Position of Bit 1           | See Figure 16                                         | a-0.25  | а    | a+0.25  | ns    |

| t <sub>TPPB2</sub> | Transmitter Output Pulse Position of Bit 2           | a = 1                                                 | 2a-0.25 | 2a   | 2a+0.25 | ns    |

| t <sub>TPPB3</sub> | Transmitter Output Pulse Position of Bit 3           | $a = {f \times 7}$                                    | 3a-0.25 | 3a   | 3a+0.25 | ns    |

| t <sub>TPPB4</sub> | Transmitter Output Pulse Position of Bit 4           |                                                       | 4a-0.25 | 4a   | 4a+0.25 | ns    |

| t <sub>TPPB5</sub> | Transmitter Output Pulse Position of Bit 5           |                                                       | 5a-0.25 | 5a   | 5a+0.25 | ns    |

| t <sub>TPPB6</sub> | Transmitter Output Pulse Position of Bit 6           |                                                       | 6a-0.25 | 6a   | 6a+0.25 | ns    |

| Transmitte         | Output Data Jitter (f = 65 MHz) (Note 14)            |                                                       | •       | •    | •       | •     |

| t <sub>TPPB0</sub> | Transmitter Output Pulse Position of Bit 0           |                                                       | -0.2    | 0    | 0.2     | ns    |

| t <sub>TPPB1</sub> | Transmitter Output Pulse Position of Bit 1           | See Figure 16                                         | a-0.2   | а    | a+0.2   | ns    |

| t <sub>TPPB2</sub> | Transmitter Output Pulse Position of Bit 2           | a = 1                                                 | 2a-0.2  | 2a   | 2a+0.2  | ns    |

| t <sub>TPPB3</sub> | Transmitter Output Pulse Position of Bit 3           | a – f x 7                                             | 3a-0.2  | 3a   | 3a+0.2  | ns    |

| t <sub>TPPB4</sub> | Transmitter Output Pulse Position of Bit 4           |                                                       | 4a-0.2  | 4a   | 4a+0.2  | ns    |

| t <sub>TPPB5</sub> | Transmitter Output Pulse Position of Bit 5           |                                                       | 5a-0.2  | 5a   | 5a+0.2  | ns    |

| t <sub>TPPB6</sub> | Transmitter Output Pulse Position of Bit 6           |                                                       | 6a-0.2  | 6a   | 6a+0.2  | ns    |

| Transmitte         | Output Data Jitter (f = 85 MHz) (FIN1217 only) (Note | 14)                                                   | •       | •    | •       | •     |

| t <sub>TPPB0</sub> | Transmitter Output Pulse Position of Bit 0           |                                                       | -0.2    | 0    | 0.2     | ns    |

| t <sub>TPPB1</sub> | Transmitter Output Pulse Position of Bit 1           | See Figure 16                                         | a-0.2   | а    | a+0.2   | ns    |

| t <sub>TPPB2</sub> | Transmitter Output Pulse Position of Bit 2           | $a = \frac{1}{f \times 7}$                            | 2a-0.2  | 2a   | 2a+0.2  | ns    |

| t <sub>TPPB3</sub> | Transmitter Output Pulse Position of Bit 3           | a =f x 7                                              | 3a-0.2  | За   | 3a+0.2  | ns    |

| t <sub>TPPB4</sub> | Transmitter Output Pulse Position of Bit 4           |                                                       | 4a-0.2  | 4a   | 4a+0.2  | ns    |

| t <sub>TPPB5</sub> | Transmitter Output Pulse Position of Bit 5           |                                                       | 5a-0.2  | 5a   | 5a+0.2  | ns    |

| t <sub>TPPB6</sub> | Transmitter Output Pulse Position of Bit 6           |                                                       | 6a-0.2  | 6a   | 6a+0.2  | ns    |

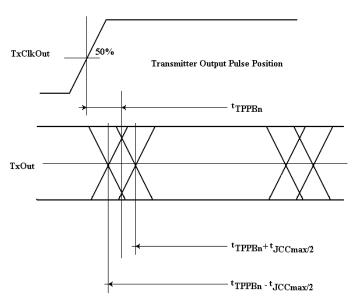

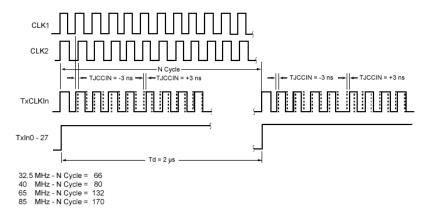

| t <sub>JCC</sub>   | FIN1217 Transmitter Clock Out Jitter                 | f = 40 MHz                                            |         | 350  | 370     |       |

|                    | (Cycle-to-Cycle)                                     | f = 65 MHz                                            |         | 210  | 230     | ps    |

|                    | See Figure 19                                        | f = 85 MHz (FIN1217 only)                             |         | 110  | 150     |       |

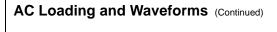

| t <sub>TPLLS</sub> | Transmitter Phase Lock Loop Set Time (Note 15)       | See Figure 11, (Note 14)                              |         |      | 10.0    | ms    |

Note 13: Outputs of all transmitters stay in 3-STATE until power reaches 2V. Both clock and data output begins to toggle 10ms after V<sub>CC</sub> reaches 3V and Power-Down pin is above 1.5V.

Note 14: This output data pulse position works for both transmitter with 21 TTL inputs except the LVDS output bit mapping difference (see Figure 15). Figure 16 shows the skew between the first data bit and clock output. Also 2-bit cycle delay is guaranteed when the MSB is output from transmitter.

Note 15: This jitter specification is based on the assumption that PLL has a ref clock with cycle-to-cycle input jitter less than 2ns.

### **Receiver DC Electrical Characteristics**

Over supply voltage and operating temperature ranges, unless otherwise specified. (Note 16)

| Symbol             | Parameter                                 | Test Conditions                            |            | Min   | Тур   | Max             | Units |

|--------------------|-------------------------------------------|--------------------------------------------|------------|-------|-------|-----------------|-------|

| LVTTL/CN           | MOS DC Characteristics                    | •                                          |            | •     | •     |                 | •     |

| V <sub>IH</sub>    | Input High Voltage                        |                                            |            | 2.0   |       | V <sub>CC</sub> | V     |

| V <sub>IL</sub>    | Input Low Voltage                         |                                            |            | GND   |       | 0.8             | V     |

| V <sub>OH</sub>    | Output High Voltage                       | $I_{OH} = -0.4 \text{ mA}$                 |            | 2.7   | 3.3   |                 | V     |

| V <sub>OL</sub>    | Output Low Voltage                        | I <sub>OL</sub> = 2 mA                     |            |       |       | 0.3             | V     |

| V <sub>IK</sub>    | Input Clamp Voltage                       | I <sub>IK</sub> = -18 mA                   |            |       |       | -1.5            | V     |

| I <sub>IN</sub>    | Input Current                             | V <sub>IN</sub> = 0V to 4.6V               |            | -10.0 |       | 10.0            | μА    |

| I <sub>OFF</sub>   | Input/Output Power Off Leakage Current    | $V_{CC} = 0V$ ,                            |            |       |       | 140.0           | _     |

|                    |                                           | All LVTTL Inputs/Outputs                   | 0V to 4.6V |       |       | ±10.0           | μА    |

| Ios                | Output Short Circuit Current              | V <sub>OUT</sub> = 0V                      |            |       | -60.0 | -120            | mA    |

| Receiver           | LVDS Input Characteristics                | Į.                                         |            |       |       | ı               |       |

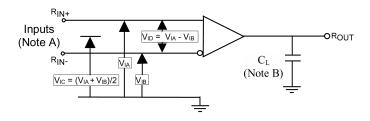

| V <sub>TH</sub>    | Differential Input Threshold HIGH         | Figure 2, Table 2                          |            |       |       | 100             | mV    |

| V <sub>TL</sub>    | Differential Input Threshold LOW          | Figure 2, Table 2                          |            | -100  |       |                 | mV    |

| V <sub>ICM</sub>   | Input Common Mode Range                   | Figure 2, Table 2                          |            | 0.05  |       | 2.35            | V     |

| I <sub>IN</sub>    | Input Current                             | $V_{IN} = 2.4V, V_{CC} = 3.6V$ or          | r 0V       |       |       | ±10.0           | μА    |

|                    |                                           | $V_{IN} = 0V, V_{CC} = 3.6V \text{ or } 0$ | V          |       |       | ±10.0           | μА    |

| Receiver           | Supply Current                            | Į.                                         |            |       |       | ı               |       |

| I <sub>CCWR</sub>  | 3:21 Receiver Power Supply Current        |                                            | 33.0 MHz   |       |       | 66.0            |       |

|                    | for Worst Case Pattern (With Load)        | C <sub>L</sub> = 8 pF,                     | 40.0 MHz   |       | 56.0  | 74.0            | 4     |

|                    | (Note 17)                                 | See Figure 3                               | 65.0 MHz   |       | 75.0  | 102             | mA    |

|                    | (85.0 MHz Specification for FIN1218 only) |                                            | 85.0 MHz   |       | 92.0  | 125             |       |

| I <sub>CCPDR</sub> | Powered Down Supply Current               | PwrDn = 0.8V (RxOut stays LOW)             |            |       | NA    | 400             | μА    |

Note 16: All Typical Values are at T<sub>A</sub> = 25°C and with V<sub>CC</sub> = 3.3V. Positive current values refer to the current flowing into device and negative values means current flowing out of pins. Voltage are referenced to ground unless otherwise specified (except ΔV<sub>OD</sub> and V<sub>OD</sub>).

Note 17: The power supply current for the receiver can be different with the number of active I/O channels.

### **Receiver AC Electrical Characteristics**

Over supply voltage and operating temperatures, unless otherwise specified

| Symbol             | Parameter                                                | Test Conditions                            | Min           | Тур         | Max          | Units    |

|--------------------|----------------------------------------------------------|--------------------------------------------|---------------|-------------|--------------|----------|

| t <sub>RCOL</sub>  | RxCLKOut LOW Time                                        |                                            | 10.0          | 11.0        |              | ns       |

| t <sub>RCOH</sub>  | RxCLKOut HIGH Time                                       | See Figure 8                               | 10.0          | 12.2        |              | ns       |

| t <sub>RSRC</sub>  | RxOut Valid Prior to RxCLKOut                            | (Rising Edge Strobe)                       | 6.5           | 11.6        |              | ns       |

| t <sub>RHRC</sub>  | RxOut Valid After RxCLKOut                               | (f = 40 MHz)                               | 6.0           | 11.6        |              | ns       |

| t <sub>RCOP</sub>  | Receiver Clock Output (RxCLKOut) Period                  |                                            | 15.0          | Т           | 50.0         | ns       |

| t <sub>RCOL</sub>  | RxCLKOut LOW Time                                        | See Figure 8                               | 5.0           | 7.8         | 9.0          | ns       |

| t <sub>RCOH</sub>  | RxCLKOut HIGH Time                                       | (Rising Edge Strobe)                       | 5.0           | 7.3         | 9.0          | ns       |

| t <sub>RSRC</sub>  | RxOut Valid Prior to RxCLKOut                            | (f = 65 MHz)                               | 4.5           | 7.7         |              | ns       |

| t <sub>RHRC</sub>  | RxOut Valid After RxCLKOut                               |                                            | 4.0           | 8.4         |              | ns       |

| t <sub>RCOP</sub>  | Receiver Clock Output (RxCLKOut) Period                  |                                            | 11.76         | Т           | 50.0         | ns       |

| t <sub>RCOL</sub>  | RxCLKOut LOW Time                                        | See Figure 8                               | 4.0           | 6.3         | 6.0          | ns       |

| t <sub>RCOH</sub>  | RxCLKOut HIGH Time                                       | (Rising Edge Strobe)                       | 4.5           | 5.4         | 6.5          | ns       |

| t <sub>RSRC</sub>  | RxOut Valid Prior to RxCLKOut                            | (f = 85 MHz) (FIN1218 only)                | 3.5           | 6.3         |              | ns       |

| t <sub>RHRC</sub>  | RxOut Valid After RxCLKOut                               |                                            | 3.5           | 6.5         |              | ns       |

| t <sub>ROLH</sub>  | Output Rise Time (20% to 80%)                            | C <sub>L</sub> = 8 pF                      |               | 2.2         | 5.0          | ns       |

| t <sub>ROHL</sub>  | Output Fall Time (80% to 20%)                            | See Figure 5                               |               | 2.1         | 5.0          | ns       |

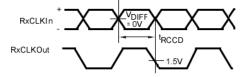

| t <sub>RCCD</sub>  | Receiver Clock Input to Clock Output Delay               | See Figure 10 (Note 19)                    | 3.5           | 6.9         | 7.5          | ns       |

|                    |                                                          | $T_A=25^{\circ}C$ and $V_{CC}=3.3V$        | 3.3           | 6.9         | 7.5          | 115      |

| t <sub>RPDD</sub>  | Receiver Power-Down Delay                                | See Figure 14                              |               |             | 1.0          | μS       |

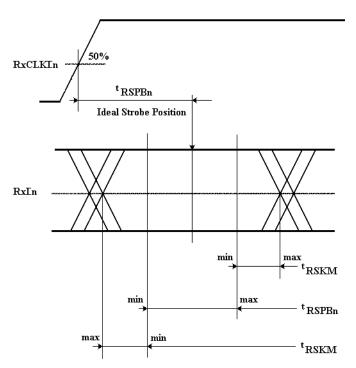

| t <sub>RSPB0</sub> | Receiver Input Strobe Position of Bit 0                  |                                            | 1.0           |             | 2.15         | ns       |

| t <sub>RSPB1</sub> | Receiver Input Strobe Position of Bit 1                  |                                            | 4.5           |             | 5.8          | ns       |

| t <sub>RSPB2</sub> | Receiver Input Strobe Position of Bit 2                  | See Figure 17                              | 8.1           |             | 9.15         | ns       |

| t <sub>RSPB3</sub> | Receiver Input Strobe Position of Bit 3                  | (f = 40 MHz)                               | 11.6          |             | 12.6         | ns       |

| t <sub>RSPB4</sub> | Receiver Input Strobe Position of Bit 4                  |                                            | 15.1          |             | 16.3         | ns       |

| t <sub>RSPB5</sub> | Receiver Input Strobe Position of Bit 5                  |                                            | 18.8          |             | 19.9         | ns       |

| t <sub>RSPB6</sub> | Receiver Input Strobe Position of Bit 6                  |                                            | 22.5          |             | 23.6         | ns       |

| t <sub>RSPB0</sub> | Receiver Input Strobe Position of Bit 0                  |                                            | 0.7           |             | 1.4          | ns       |

| t <sub>RSPB1</sub> | Receiver Input Strobe Position of Bit 1                  |                                            | 2.9           |             | 3.6          | ns       |

| t <sub>RSPB2</sub> | Receiver Input Strobe Position of Bit 2                  | See Figure 17                              | 5.1           |             | 5.8          | ns       |

| t <sub>RSPB3</sub> | Receiver Input Strobe Position of Bit 3                  | (f = 65 MHz)                               | 7.3           |             | 8.0          | ns       |

| t <sub>RSPB4</sub> | Receiver Input Strobe Position of Bit 4                  |                                            | 9.5           |             | 10.2         | ns       |

| t <sub>RSPB5</sub> | Receiver Input Strobe Position of Bit 5                  |                                            | 11.7          |             | 12.4         | ns       |

| t <sub>RSPB6</sub> | Receiver Input Strobe Position of Bit 6                  |                                            | 13.9          |             | 14.6         | ns       |

| t <sub>RSPB0</sub> | Receiver Input Strobe Position of Bit 0                  |                                            | 0.49          |             | 1.19         | ns       |

| t <sub>RSPB1</sub> | Receiver Input Strobe Position of Bit 1                  |                                            | 2.17          |             | 2.87         | ns       |

| t <sub>RSPB2</sub> | Receiver Input Strobe Position of Bit 2                  |                                            | 3.85          |             | 4.55         | ns       |

| t <sub>RSPB3</sub> | Receiver Input Strobe Position of Bit 3                  | See Figure 17                              | 5.53          |             | 6.23         | ns       |

| t <sub>RSPB4</sub> | Receiver Input Strobe Position of Bit 4                  | (f = 85 MHz) (FIN1218 only)                | 7.21          |             | 7.91         | ns       |

| t <sub>RSPB5</sub> | Receiver Input Strobe Position of Bit 5                  |                                            | 8.89          |             | 9.59         | ns       |

| t <sub>RSPB6</sub> | Receiver Input Strobe Position of Bit 6                  |                                            | 10.57         |             | 11.27        | ns       |

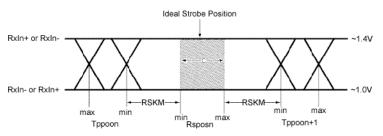

| t <sub>RSKM</sub>  | RxIn Skew Margin                                         | f = 40 MHz; See Figure 18                  | 490           |             |              |          |

|                    | (Note 18)                                                | f = 65 MHz; See Figure 18                  | 400           |             |              | ps       |

|                    |                                                          | f = 85 MHz (FIN1218 only);                 | 252           |             |              | PS       |

|                    |                                                          | See Figure 18                              | 232           | <u></u>     | <u> </u>     | <u> </u> |

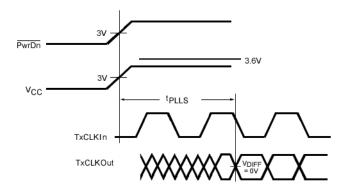

| t <sub>RPLLS</sub> | Receiver Phase Lock Loop Set Time                        | See Figure 12                              |               |             | 10.0         | ms       |

| Note 18: Pa        | aceiver skew margin is defined as the valid sampling win | dow after considering notantial actua/hole | d time and mi | nimum/movir | num hit naci | tion     |

Note 18: Receiver skew margin is defined as the valid sampling window after considering potential setup/hold time and minimum/maximum bit position.

Note 19: Total channel latency from serializer to deserializer is  $(T + t_{TCCD}) + (2*T + t_{RCCD})$ . There is the clock period.

FIGURE 1. Differential LVDS Output DC Test Circuit

$\label{eq:Note A: For all input pulses, $t_R$ or $t_F<=1$ ns.}$  Note B:  $C_L$  includes all probe and jig capacitance.

FIGURE 2. Differential Receiver Voltage Definitions and Propagation Delay and Transition Time Test Circuit TABLE 2. Receiver Minimum and Maximum Input Threshold Test Voltages

| Applied         | Voltages        | Resulting Differential Input Voltage | Resulting Common Mode Input Voltage |

|-----------------|-----------------|--------------------------------------|-------------------------------------|

| (               | (V) (mV)        |                                      | (V)                                 |

| V <sub>IA</sub> | V <sub>IB</sub> | V <sub>ID</sub>                      | V <sub>IC</sub>                     |

| 1.25            | 1.15            | 100                                  | 1.2                                 |

| 1.15            | 1.25            | -100                                 | 1.2                                 |

| 2.4             | 2.3             | 100                                  | 2.35                                |

| 2.3             | 2.4             | -100                                 | 2.35                                |

| 0.1             | 0               | 100                                  | 0.05                                |

| 0               | 0.1             | -100                                 | 0.05                                |

| 1.5             | 0.9             | 600                                  | 1.2                                 |

| 0.9             | 1.5             | -600                                 | 1.2                                 |

| 2.4             | 1.8             | 600                                  | 2.1                                 |

| 1.8             | 2.4             | -600                                 | 2.1                                 |

| 0.6             | 0               | 600                                  | 0.3                                 |

| 0               | 0.6             | -600                                 | 0.3                                 |

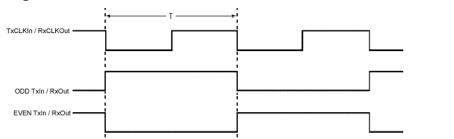

# **AC Loading and Waveforms**

Note: The worst case test pattern produces a maximum toggling of digital circuits, LVDS I/O and LVTTL/CMOS I/O. Depending on the valid strobe edge of transmitter, the TxCLKIn can be either rising or falling edge data strobe.

FIGURE 3. "Worst Case" Test Pattern

FIGURE 4. Transmitter LVDS Output Load and Transition Times

FIGURE 5. Receiver LVTTL/CMOS Output Load and Transition Times

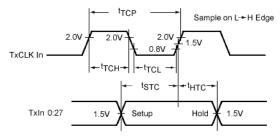

FIGURE 6. Transmitter Setup/Hold and HIGH/LOW Times (Rising Edge Strobe)

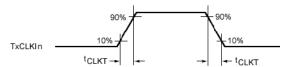

FIGURE 7. Transmitter Input Clock Transition Time

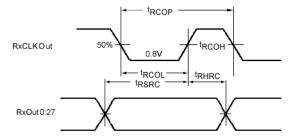

FIGURE 8. Receiver Setup/Hold and HIGH/LOW Times

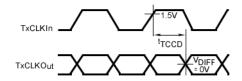

FIGURE 9. Transmitter Clock In to Clock Out Delay (Rising Edge Strobe)

FIGURE 10. Receiver Clock In to Clock Out Delay (Falling Edge Strobe)

FIGURE 11. Transmitter Phase Lock Loop Set Time

FIGURE 12. Receiver Phase Lock Loop Set Time

FIGURE 13. Transmitter Power-Down Delay

FIGURE 14. Receiver Power-Down Delay

Note: This output data pulse position works for both transmitter with 21 TTL inputs except the LVDS output bit mapping difference. All the information in this diagram tells that the skew between the first data bit and clock output. Also 2-bit cycle delay is guaranteed when the MSB is output from transmitter.

FIGURE 15. 21 Parallel LVTTL Inputs Mapped to 3 Serial LVDS Outputs

FIGURE 16. Transmitter Output Pulse Bit Position

FIGURE 17. Receiver Input Strobe Bit Position

$\textbf{Note:} \ t_{\text{RSKM}} \ \text{is the budget for the cable skew and source clock skew plus ISI (Inter-Symbol Interference)}.$

**Note:** The minimum and maximum pulse position values are based on the bit position of each of the 7 bits within the LVDS data stream across PVT (Process, Voltage Supply, and Temperature).

FIGURE 18. Receiver LVDS Input Skew Margin

Note: This jitter pattern is used to test the jitter response (Clock Out) of the device over the power supply range with worst jitter ±3ns (cycle-to-cycle) clock input. The specific test methodology is as follows:

- Switching input data TxIn0 to TxIn20 at 0.5 MHz, and the input clock is shifted to left –3ns and to the right +when data is HIGH (by switching between CLK1 and CLK2 in Figure 11)

- The ±3ns cycle-to-cycle input jitter is the static phase error between the two clock sources. Jumping between two clock sources to simulate the worst

case of clock edge jump (3 ns) from graphical controllers. Cycle-to-cycle jitter at TxCLK out pin should be measured cross V<sub>CC</sub> range with 100mV noise

(V<sub>CC</sub> noise frequency <2 MHz).</li>

FIGURE 19.

### Physical Dimensions inches (millimeters) unless otherwise noted 0.40 TYF -B-8 9.20 8.10 4.05 O.2 C B A ALL LEAD TIPS - 0.30 0.50 LAND PATTERN RECOMMENDATION □ 0.1 C SEE DETAIL A 1.2 MAX 0.90+0.15 0.09-0.20 0.10±0.05 ♦ 0.13@ A BS CS DIMENSIONS ARE IN MILLIMETERS R0.16 GAGE PLANE 0.25 NOTES: A. CONFORMS TO JEDEC REGISTRATION MO-153, VARIATION ED. DATE 4/97. SEATING PLANE 0.60±0.10 B. DIMENSIONS ARE IN MILLIMETERS. C. DIMENSIONS ARE EXCLUSIVE OF BURRS, MOLD FLASH, AND TIE BAR EXTRUSIONS. D. DIMENSIONS AND TOLERANCES PER ANSI Y14.5M. 1982. DETAIL A MTD48REVC

48-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 6.1mm Wide Package Number MTD48

Fairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com