# 捷多邦,专业PCB打样工厂,24小时加急出货

September 2005 Revised December 2005

# FIN24AC µSerDes™ 22-Bit Bi-Directional Serializer/Deserializer

#### **General Description**

The FIN24AC µSerDes<sup>™</sup> is a low power Serializer/Deserializer (SerDes) that can help minimize the cost and power of transferring wide signal paths. Through the use of serialization, the number of signals transferred from one point to another can be significantly reduced. Typical reduction is 4:1 to 6:1 for unidirectional paths. For bi-directional operation, using half duplex for multiple sources, it is possible to increase the signal reduction to close to 10:1. Through the use of differential signaling, shielding and EMI filters can also be minimized, further reducing the cost of serialization. The differential signaling is also important for providing a noise-insensitive signal that can withstand radio and electrical noise sources. Major reduction in power consumption allows minimal impact on battery life in ultra-portable applications. A unique word boundary technique assures that the actual word boundary is identified when the data is deserialized. This guarantees that each word is correctly aligned at the deserializer on a word by word basis through a unique sequence of clock and data that is not repeated except at the word boundary. It is possible to use a single PLL for most applications including bi-directional operation.

#### Features

- Low power for minimum impact on battery life

- Multiple power-down modes

- AC coupling with DC balance

- 100nA in standby mode 5mA typical operating conditions

- Cable reduction: 25:4 or greater

- Bi-directional operation 50:7 reduction or greater

- Differential signaling:

- -90dBm EMI when using CTL in lab conditions using a near field probe

- Minimized shielding

- Minimized EMI filter

- Minimum susceptibility to external interference

- Up to 22 bits in either direction

- Up to 20MHz parallel interface operation

- Voltage translation from 1.65V to 3.6V

- Ultra-small and cost-effective packaging

- High ESD protection: >8kV HBM

- Parallel I/O power supply (V<sub>DDP</sub>) range between 1.65V to 3.6V

#### Applications

- Micro-controller or Pixel interfaces

- Image sensors

- Small displays

- LCD, cell phone, digital camera, portable gaming, printer, PDA, video camera, automotive

#### **Ordering Code:**

| Order<br>Number | Package<br>Number | Package Description                                                                   |

|-----------------|-------------------|---------------------------------------------------------------------------------------|

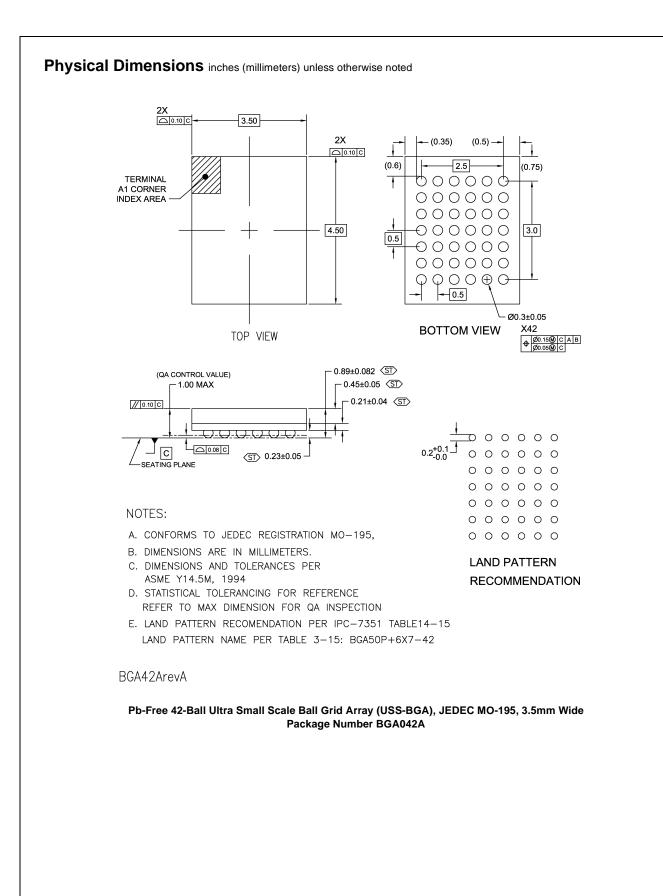

| FIN24ACGFX      | BGA042A           | Pb-Free 42-Ball Ultra Small Scale Ball Grid Array (USS-BGA), JEDEC MO-195, 3.5mm Wide |

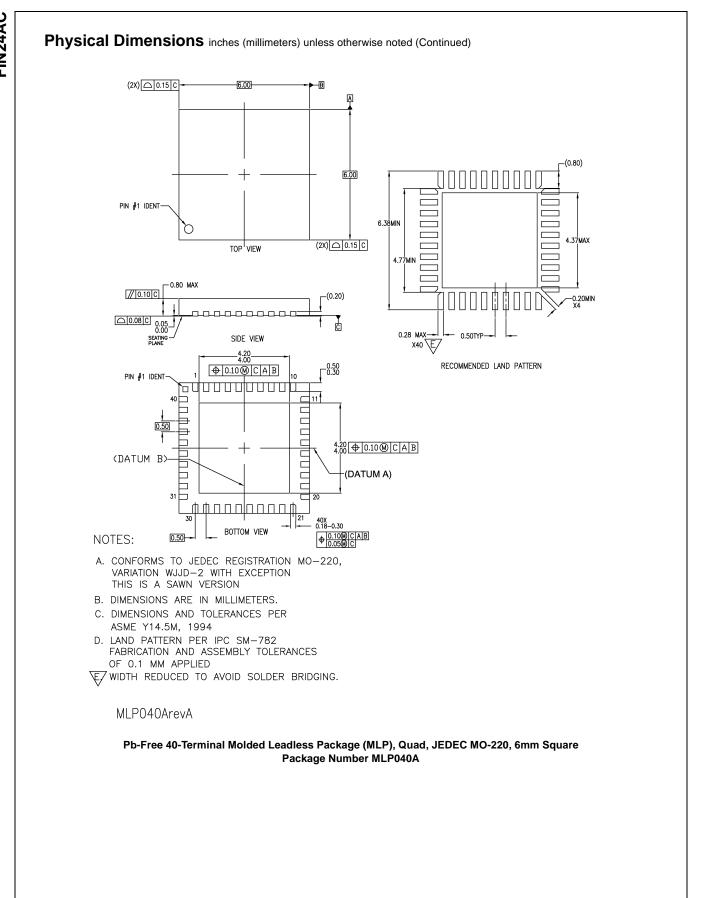

| FIN24ACMLX      | MLP040A           | Pb-Free 40-Terminal Molded Leadless Package (MLP), Quad, JEDEC MO-220, 6mm Square     |

Pb-Free package per JEDEC J-STD-020B. BGA and MLP packages available in Tape and Reel only.

Destris a trademark of Fairchild Semiconductor Corporation.

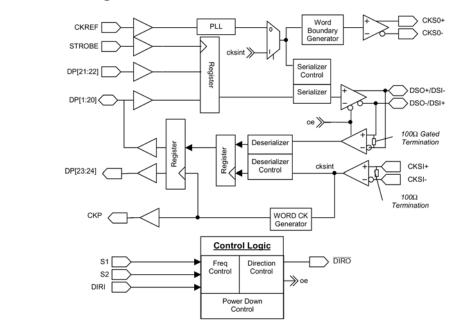

#### **Functional Block Diagram**

# **Connection Diagrams**

Terminal Assignments for MLP DP[8] DP[7] DP[6] DP[5] DP[3] DP[3] DP[3] DP[3] STROBE STROBE <u> 3553333333349</u> 30 DIRO 29 CKSO+ 28 CKSO-DP[9] 1 DP[10] 2 DP[11] 3) 27 DSO+ / DSI-DP[12] 4 DSO- / DSI+ 26 VDDP 5 25 CKSI-CKP 6) 24 CKSI+ DP[13] 7) 23DIRI 22S2 21VDDS DP[14] 8 DP[15] 9) DP[16]10 P ÊÊ ାର୍ଲ F 印 Ê ₫ P DP[23] DP[24] DP[17] DP[18] DP[19] DP[20] DP[21] DP[22] VDDA S1 (Top View)

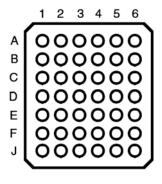

Terminal Assignments for  $\mu$ BGA

(Top View)

# **Terminal Description**

| Terminal<br>Name           | I/О Туре | Number<br>of<br>Terminals | Description of Signals                                                                                                                                                                                           |

|----------------------------|----------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DP[1:20]                   | I/O      | 20                        | LVCMOS Parallel I/O. Direction controlled by DIRI pin                                                                                                                                                            |

| DP[21:22]                  | I        | 2                         | LVCMOS Parallel Unidirectional Inputs                                                                                                                                                                            |

| DP[23:24]                  | 0        | 2                         | LVCMOS Unidirectional Parallel Outputs                                                                                                                                                                           |

| CKREF                      | IN       | 1                         | LVCMOS Clock Input and PLL Reference                                                                                                                                                                             |

| STROBE                     | IN       | 1                         | LVCMOS Strobe Signal for Latching Data into the Serializer                                                                                                                                                       |

| СКР                        | OUT      | 1                         | LVCMOS Word Clock Output                                                                                                                                                                                         |

| DSO+ / DSI-<br>DSO- / DSI+ | DIFF-I/O | 2                         | CTL Differential Serial I/O Data Signals (Note 1)<br>DSO: Refers to output signal pair<br>DSI: Refers to input signal pair<br>DSO(I)+: Positive signal of DSO(I) pair<br>DSO(I)-: Negative signal of DSO(I) pair |

| CKSI+, CKSI-               | DIFF-IN  | 2                         | CTL Differential Deserializer Input Bit Clock<br>CKSI: Refers to signal pair<br>CKSI+: Positive signal of CKSI pair<br>CKSI-: Negative signal of CKSI pair                                                       |

| CKSO+, CKSO-               | DIFF-OUT | 2                         | CTL Differential Serializer Output Bit Clock<br>CKSO: Refers to signal pair<br>CKSO+: Positive signal of CKSO pair<br>CKSO-: Negative signal of CKSO pair                                                        |

| S1                         | IN       | 1                         | LVCMOS Mode Selection terminals used to select                                                                                                                                                                   |

| \$2                        | IN       | 1                         | Frequency Range for the RefClock, CKREF                                                                                                                                                                          |

| DIRI                       | IN       | 1                         | LVCMOS Control Input<br>Used to control direction of Data Flow:<br>DIRI = "1" Serializer, DIRI = "0" Deserializer                                                                                                |

| DIRO                       | OUT      | 1                         | LVCMOS Control Output<br>Inversion of DIRI                                                                                                                                                                       |

| V <sub>DDP</sub>           | Supply   | 1                         | Power Supply for Parallel I/O and Translation Circuitry                                                                                                                                                          |

| V <sub>DDS</sub>           | Supply   | 1                         | Power Supply for Core and Serial I/O                                                                                                                                                                             |

| V <sub>DDA</sub>           | Supply   | 1                         | Power Supply for Analog PLL Circuitry                                                                                                                                                                            |

| GND                        | Supply   | 0                         | Use Bottom Ground Plane for Ground Signals                                                                                                                                                                       |

Note 1: The DSO/DSI serial port pins have been arranged such that when one device is rotated 180 degrees with respect to the other device the serial connections will properly align without the need for any traces or cable signals to cross. Other layout orientations may require that traces or cables cross.

# $\mu$ BGA Terminal Assignments

|   | 1      | 2      | 3                | 4                | 5           | 6           |

|---|--------|--------|------------------|------------------|-------------|-------------|

| А | DP[9]  | DP[7]  | DP[5]            | DP[3]            | DP[1]       | CKREF       |

| В | DP[11] | DP[10] | DP[6]            | DP[2]            | STROBE      | DIRO        |

| С | CKP    | DP[12] | DP[8]            | DP[4]            | CKSO+       | CKSO-       |

| D | DP[13] | DP[14] | V <sub>DDP</sub> | GND              | DSO- / DSI+ | DSO+ / DSI- |

| Е | DP[15] | DP[16] | GND              | V <sub>DDS</sub> | CKSI+       | CKSI–       |

| F | DP[17] | DP[18] | DP[21]           | V <sub>DDA</sub> | S2          | DIRI        |

| J | DP[19] | DP[20] | DP[22]           | DP[23]           | DP[24]      | S1          |

#### **Control Logic Circuitry**

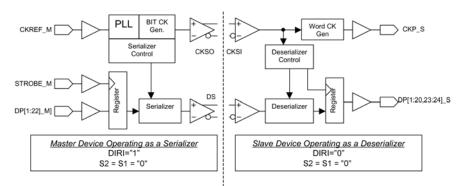

The FIN24AC has the ability to be used as a 24-bit Serializer or a 24-bit Deserializer. Pins S1 and S2 must be set to accommodate the clock reference input frequency range of the serializer. The table below shows the pin programming of these options based on the S1 and S2 control pins. The DIRI pin controls whether the device is a serializer or a deserializer. When DIRI is asserted LOW, the device is configured as a deserializer. When the DIRI pin is asserted HIGH, the device will be configured as a serializer. Changing the state on the DIRI signal will reverse the direction of the I/O signals and generate the opposite state signal on DIRO. For unidirectional operation the DIRI pin should be hardwired to the HIGH or LOW state and the DIRO pin should be left floating. For bi-directional operation the DIRI of the master device will be driven by the system and the DIRO signal of the master will be used to drive the DIRI of the slave device.

#### Serializer/Deserializer with Dedicated I/O Variation

The serialization and deserialization circuitry is setup for 24 bits. Because of the dedicated inputs and outputs only 22 bits of data are ever serialized or deserialized. Regardless of the mode of operation the serializer is always sending 24 bits of data plus 2 boundary bits and the deserializer is always receiving 24 bits of data and 2 word boundary bits. Bits 23 and 24 of the serializer will always contain the value of zero and will be discarded by the deserializer. DP[21:22] input to the serializer will be deserialized to DP[23:24] respectively.

#### **Turn-Around Functionality**

The device passes and inverts the DIRI signal through the device asynchronously to the DIRO signal. Care must be taken by the system designer to insure that no contention occurs between the deserializer outputs and the other devices on this port. Optimally the peripheral device driving the serializer should be put into a HIGH Impedance state prior to the DIRI signal being asserted.

When a device with dedicated data outputs turns from a deserializer to a serializer the dedicated outputs will remain at the last logical value asserted. This value will only change if the device is once again turned around into a deserializer and the values are overwritten.

| Mode<br>Number | S2 | S1                                        | DIRI | Description                               |

|----------------|----|-------------------------------------------|------|-------------------------------------------|

| 0              | 0  | 0                                         | х    | Power-Down Mode                           |

| 1              | 0  | 1                                         | 1    | 24-Bit Serializer<br>2MHz to 5MHz CKREF   |

|                | 0  | 1                                         | 0    | 24-Bit Deserializer                       |

| 2              | 1  | 0                                         | 1    | 24-Bit Serializer<br>5MHz to 15MHz CKREF  |

|                | 1  | 0                                         | 0    | 24-Bit Deserializer                       |

| 3              | 1  | 1 1 24-Bit Serializer<br>10MHz to 20MHz ( |      | 24-Bit Serializer<br>10MHz to 20MHz CKREF |

|                | 1  | 1                                         | 0    | 24-Bit Deserializer                       |

**TABLE 1. Control Logic Circuitry**

# Power-Down Mode: (Mode 0)

Mode 0 is used for powering down and resetting the device. When both of the mode signals are driven to a LOW state the PLL and references will be disabled, differential input buffers will be shut off, differential output buffers will be placed into a HIGH impedance state, LVCMOS outputs will be placed into a HIGH impedance state and LVCMOS inputs will be driven to a valid level internally. Additionally all internal circuitry will be reset. The loss of CKREF state is also enabled to insure that the PLL will only power-up if there is a valid CKREF signal.

In a typical application mode signals of the device will typically not change states other than between the desired frequency range and the power-down mode. This allows for system level power-down functionality to be implemented via a single wire for a SerDes pair. The S1 and S2 selection signals that have their operating mode driven to a "logic 0" should be hardwired to GND. The S1 and S2 signals that have their operating mode driven to a "logic 1" should be connected to a system level power-down signal.

# **Serializer Operation Mode**

The serializer configurations are described in the following sections. The basic serialization circuitry works essentially identically in these modes, but the actual data and clock streams will differ depending on if CKREF is the same as the STROBE signal or not. When it is stated that CKREF = STROBE this means that the CKREF and STROBE signals have an identical frequency of operation but may or may not be phase aligned. When it is stated that CKREF does not equal STROBE then each signal is distinct and CKREF must be running at a frequency high enough to avoid any loss of data condition. CKREF must never be a lower frequency than STROBE.

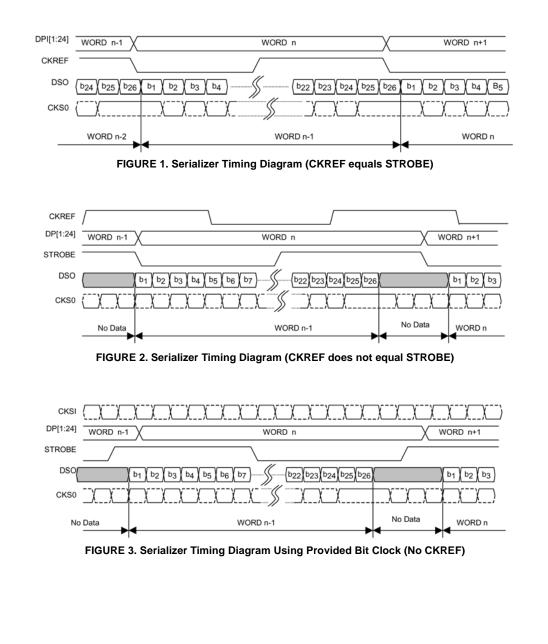

#### Serializer Operation: (Figure 1) Modes 1, 2, or 3 DIRI equals 1 CKREF equals STROBE

The PLL must receive a stable CKREF signal in order to achieve lock prior to any valid data being sent. The CKREF signal can be used as the data STROBE signal provided that data can be ignored during the PLL lock phase.

Once the PLL is stable and locked the device can begin to capture and serialize data. Data will be captured on the rising edge of the STROBE signal and then serialized. The serialized data stream is synchronized and sent source synchronously with a bit clock with an embedded word boundary. When operating in this mode the internal deserializer circuitry is disabled including the serial clock, serial data input buffers, the bi-directional parallel outputs and the CKP word clock. The CKP word clock will be driven HIGH.

#### Serializer Operation: (Figure 2) DIRI equals 1 CKREF does not equal STROBE

If the same signal is not used for CKREF and STROBE, then the CKREF signal must be run at a higher frequency than the STROBE rate in order to serialize the data correctly. The actual serial transfer rate will remain at 26 times the CKREF frequency. A data bit value of zero will be sent when no valid data is present in the serial bit stream. The operation of the serializer will otherwise remain the same.

The exact frequency that the reference clock needs to run at will be dependent upon the stability of the CKREF and STROBE signal. If the source of the CKREF signal implements spread spectrum technology then the maximum frequency of this spread spectrum clock should be used in calculating the ratio of STROBE frequency to the CKREF frequency. Similarly if the STROBE signal has significant cycle-to-cycle variation then the maximum cycle-to-cycle time needs to be factored into the selection of the CKREF frequency.

#### Serializer Operation: (Figure 3) DIRI equals 1 No CKREF

A third method of serialization can be done by providing a free running bit clock on the CKSI signal. This mode is enabled by grounding the CKREF signal and driving the DIRI signal HIGH.

At power-up the device is configured to accept a serialization clock from CKSI. If a CKREF is received then this device will enable the CKREF serialization mode. The device will remain in this mode even if CKREF is stopped. To re-enable this mode the device must be powered down and then powered back up with a "logic 0" on CKREF.

### **Deserializer Operation Mode**

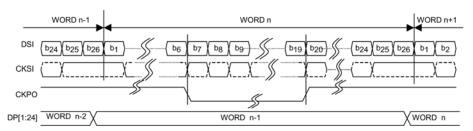

The operation of the deserializer is only dependent upon the data received on the DSI data signal pair and the CKSI clock signal pair. The following two sections describe the operation of the deserializer under two distinct serializer source conditions. References to the CKREF and STROBE signals refer to the signals associated with the serializer device used in generating the serial data and clock signals that are inputs to the deserializer.

When operating in this mode the internal serializer circuitry is disabled including the parallel data input buffers. If there is a CKREF signal provided then the CKSO serial clock will continue to transmit bit clocks. Upon device power-up (S1 or S2 = 1) all deserializer output data pins will be driven low until valid data is passed through the deserializer.

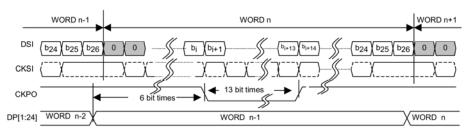

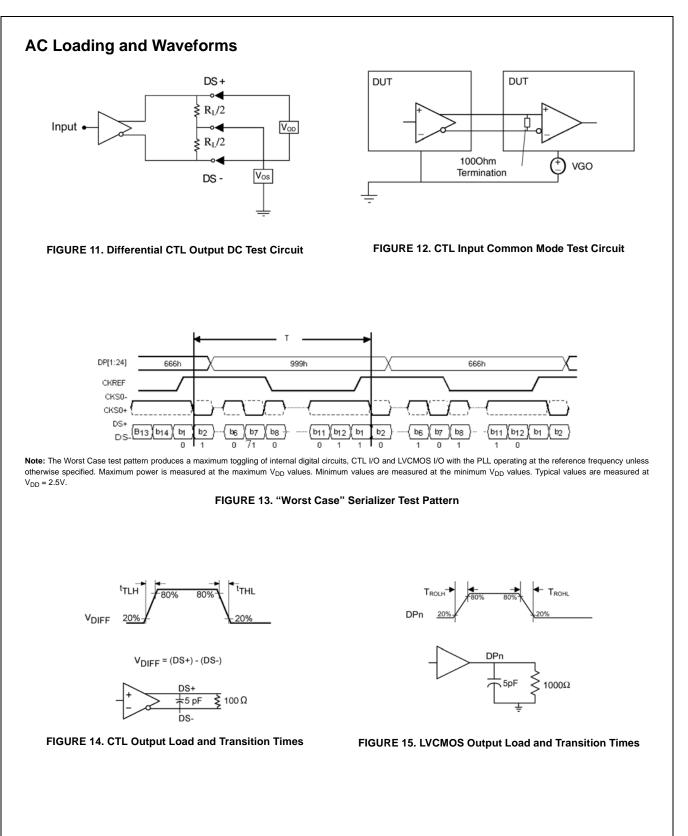

#### Deserializer Operation: DIRI equals 0 (Serializer Source: CKREF equals STROBE)

When the DIRI signal is asserted LOW the device will be configured as a deserializer. Data will be captured on the serial port and deserialized through use of the bit clock sent with the data. The word boundary is defined in the actual clock and data signal. Parallel data will be generated at the time the word boundary is detected. The falling edge of CKP will occur approximately 6 bit times after the falling edge of CKSI. The rising edge of CKP will go high approximately 13 bit times after CKP goes LOW. The rising edge of CKP will be generated approximately 13 bit times later. When no embedded word boundary occurs then no pulse on CKP will be generated and CKP will remain HIGH.

#### Deserializer Operation: DIRI equals 0 (Serializer Source: CKREF does not equal STROBE)

The logical operation of the deserializer remains the same regardless of if the CKREF is equal in frequency to the STOBE or at a higher frequency than the STROBE. The actual serial data stream presented to the deserializer will however be different because it will have non-valid data bits sent between words. The duty cycle of CKP will vary based on the ratio of the frequency of the CKREF signal to the STROBE signal. The frequency of the CKP signal will be equal to the STROBE frequency. The falling edge of CKP will occur 6 bit times after the data transition. The LOW time of the CKP signal will be equal to 1/2 (13 bit times) of the CKREF period. The CKP HIGH time will be equal to STROBE period –  $\frac{1}{2}$  of the CKREF period. Figure 5 is representative of a waveform that could be seen when CKREF is not equal to STROBE. If CKREF was significantly faster then additional non-valid data bits would occur between data words.

FIGURE 4. Deserializer Timing Diagram (Serializer Source: CKREF equals STROBE)

FIGURE 5. Deserializer Timing Diagram (Serializer Source: CKREF does not equal STROBE)

#### **Embedded Word Clock Operation**

The FIN24AC sends and receives serial data source synchronously with a bit clock. The bit clock has been modified to create a word boundary at the end of each data word. The word boundary has been implemented by skipping a low clock pulse. This appears in the serial clock stream as 3 consecutive bit times where signal CKSO remains HIGH. In order to implement this sort of scheme two extra data bits are required. During the word boundary phase the data will toggle either HIGH-then-LOW or LOW-then-HIGH dependent upon the last bit of the actual data word. Table 2 provides some examples showing the actual data word and the data word with the word boundary bits added. Note that a 24-bit word will be extended to 26-bits during serial transmission. Bit 25 and Bit 26 are defined with-respect-to Bit 24. Bit 25 will always be the inverse of Bit 24, and Bit 26 will always be the same as Bit 24. This insures that a "0"  $\rightarrow$  "1" and a "1"  $\rightarrow$  "0" transition will always occur during the embedded word phase where CKSO is HIGH.

The serializer generates the word boundary data bits and the boundary clock condition and embeds them into the serial data stream. The deserializer looks for the end of the word boundary condition to capture and transfer the data to the parallel port. The deserializer only uses the embedded word boundary information to find and capture the data. These boundary bits are then stripped prior to the word being sent out of the parallel port.

|         | 24-Bit Data Words               | 24-Bit Data Word with Word Boundar |                                   |  |  |  |  |

|---------|---------------------------------|------------------------------------|-----------------------------------|--|--|--|--|

| Hex     | Binary                          | Hex                                | Binary                            |  |  |  |  |

| 3FFFFFh | 0011 1111 1111 1111 1111 1111b  | 1FFFFFFh                           | 01 1111 1111 1111 1111 1111 1111b |  |  |  |  |

| 155555h | 0101 0101 0101 0101 01010 0101b | 1155555h                           | 01 0101 0101 0101 0101 0101 0101b |  |  |  |  |

| xxxxxxh | 0xxx xxxx xxxx xxxx xxxx xxxxb  | 1xxxxxxh                           | 01 0xxx xxxx xxxx xxxx xxxx xxxxb |  |  |  |  |

**TABLE 2. Word Boundary Data Bits**

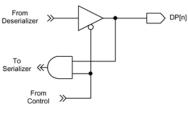

#### LVCMOS Data I/O

The LVCMOS input buffers have a nominal threshold value equal to  $\frac{1}{2}$  of V\_{DDP}. The input buffers are only operational when the device is operating as a serializer. When the device is operating as a deserializer the inputs are gated off to conserve power.

The LVCMOS 3-STATE output buffers are rated for a source/ sink current of 2 mAs at 1.8V. The outputs are active when the DIRI signal is asserted LOW. When the DIRI signal is asserted HIGH the bi-directional LVCMOS I/Os will be in a HIGH-Z state. Under purely capacitive load conditions the output will swing between GND and V<sub>DDP</sub>.

Unused LVCMOS input buffers must be tied off to either a valid logic LOW or a valid logic HIGH level to prevent static current draw due to a floating input. Unused LVCMOS output should be left floating. Unused bi-directional pins should be connected to GND through a high value resistor. If a FIN24AC device is configured as an unidirectional serializer then unused data I/O can be treated as unused inputs. If the FIN24AC is hardwired as a deserializer then unused data I/O can be treated as unused outputs.

FIGURE 6. LVCMOS I/O

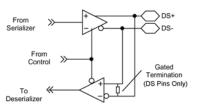

#### **Differential I/O Circuitry**

The FIN24AC employs FSC proprietary CTL I/O technology. CTL is a low power, low EMI differential swing I/O technology. The CTL output driver generates a constant output source and sink current. The CTL input receiver senses the current difference and direction from the corresponding output buffer to which it is connected. This differs from LVDS which uses a constant current source output but a voltage sense receiver. Like LVDS an input source termination resistor is required to properly terminate the transmission line. The FIN24AC device incorporates an internal termination resistor on the CKSI receiver and a gated internal termination resistor on the DS input receiver. The gated termination resistor insures proper termination regardless of direction of data flow. The relative greater sensitivity of the current sense receiver of CTL allows it to work at much lower current drive and correspondingly a much lower voltage.

During power-down mode the differential inputs will be disabled and powered down and the differential outputs will be placed in a HIGH-Z state. CTL inputs have an inherent failsafe capability that supports floating inputs. When the CKSI input pair of the serializer is unused it can reliably be left floating. Alternately both of the inputs can be connected to ground. CTL inputs should never be connected to  $V_{DD}$ . When the CKSO output of the deserializer is unused it should be allowed to float.

FIGURE 7. Bi-Directional Differential I/O Circuitry

### **PLL Circuitry**

The CKREF input signal is used to provide a reference to the PLL. The PLL will generate internal timing signals capable of transferring data at 26 times the incoming CKREF signal. The output of the PLL is a Bit Clock that is used to serialize the data. The bit clock is also sent source synchronously with the serial data stream.

There are two ways to disable the PLL. The PLL can be disabled by entering the Mode 0 state (S1 = S2 = 0). The PLL will disable immediately upon detecting a LOW on both the S1 and S2 signals. When any of the other modes are entered by asserting either S1 or S2 HIGH and by providing a CKREF signal the PLL will power-up and goes through a lock sequence. One must

wait the specified number of clock cycles prior to capturing valid data into the parallel port. When the  $\mu$ SerDes chipset transitions from a power down state (S1, S2 = 0, 0) to a powered state (example S1, S2 = 1, 1), CKP on the deserializer will transition LOW for a short duration, and will return HIGH. Following this, the signal level of the deserializer at CKP will correspond to the serializer signal levels.

An alternate way of powering down the PLL is by stopping the CKREF signal either HIGH or LOW. Internal circuitry detects the lack of transitions and shuts the PLL and serial I/O down. Internal references will not however be disabled allowing for the PLL to power-up and re-lock in a lesser number of clock cycles than when exiting Mode 0. When a transition is seen on the CKREF signal the PLL will once again be reactivated.

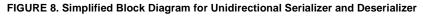

#### Application Mode Diagrams Unidirectional Data Transfer

Figure 8 shows the basic operation diagram when a pair of Ser-Des is configured in an unidirectional operation mode.

Master Operation: The device will... (Please refer to Figure 8)

- 1. Be configured as a serializer at power-up based on the value of the DIRI signal.

- Accept CKREF\_M word clock and generate a bit clock with embedded word boundary. This bit clock will be sent to the slave device through the CKSO port.

- 3. Receive parallel data on the rising edge of STROBE\_M.

- 4. Generate and transmit serialized data on the DS signals which is source synchronous with CKSO.

- 5. Generate an embedded word clock for each strobe signal.

Slave Operation: The device will...

- 1. Be configured as a deserializer at power-up based on the value of the DIRI signal.

- 2. Accept an embedded word boundary bit clock on CKSI.

- 3. Deserialize the DS Data stream using the CKSI input clock.

- Write parallel data onto the DP\_S port and generate the CKP\_S. CKP\_S will only be generated when a valid data word occurs.

Note: Data on serializer pins DP[21:22] will be output on pins DP[23:24] of the deserializer as shown REFCK FIN24AC Sending FIN24AC Receiving Unit Unit CKREF CKSO CKSI CKP STROBE CNTLIO CNTL [0-1] DP[21:22] DS DP[23:24] DS DP[1:20] DP[1:20] VDD DĪRO DIR DIRO DIRI S1 S1 S2 S2 PwrDwr

FIGURE 9. Unidirectional Serializer and Deserializer

FIGURE 10. Multiple Units, Unidirectional Signals in Each Direction

Figure 10 shows a half duplex connectivity diagram. This connectivity allows for two unidirectional data streams to be sent across a single pair of SerDes devices. Data will be sent on a frame by frame basis. For this mode of operation to work there needs to be some synchronization between when the Camera sends its data frame and when the LCD sends its data. One option for this is to have the LCD send data during the camera blanking period. External logic may need to be provided in order for this mode of operation to work.

Devices will alternate frames of data controlled by a direction control and a direction sense. When DIRI, on the right-hand FIN24AC is HIGH, data will be sent from the Camera to the Camera interface at the base. When DIRI, on the right-hand FIN24AC goes LOW data will be sent from the baseband process to the LCD. The direction is then changed at DIRO on the right-hand FIN24AC indicating to the left-hand FIN24AC to change direction. Data will be sent from the Base LCD Unit to the LCD. The DIRO pin on the left-hand FIN24AC is used to indicate to the base control unit that the signals are changing direction and the LCD is now available to be sent data. DIRI on the right-hand FIN24AC could typically use a timing reference signal such as VSYNC from the camera interface to indicate direction change. A derivative of this signal may be required in order to make sure that no data is lost on the final data transfer.

#### Absolute Maximum Ratings(Note 2)

| Supply Voltage (V <sub>DD</sub> )              | -0.5V to +4.6V                    |

|------------------------------------------------|-----------------------------------|

| ALL Input/Output Voltage                       | -0.5V to +4.6V                    |

| LVDS Output Short Circuit Duration             | Continuous                        |

| Storage Temperature Range (T <sub>STG</sub> )  | $-65^{\circ}C$ to $+150^{\circ}C$ |

| Maximum Junction Temperature (T <sub>J</sub> ) | +150°C                            |

| Lead Temperature (T <sub>L</sub> )             |                                   |

| (Soldering, 4 seconds)                         | +260°C                            |

| ESD Rating                                     |                                   |

| Human Body Model, 1.5K $\Omega$ , 100pF        |                                   |

| All Pins                                       | >2kV                              |

| CKSO, CKSI, DSO to GND                         | >7.5kV                            |

|                                                |                                   |

# **Recommended Operating Conditions**

| Supply Voltage (V <sub>DDA</sub> , V <sub>DDS</sub> ) | 2.5V to 2.9V                         |

|-------------------------------------------------------|--------------------------------------|

| Supply Voltage (V <sub>DDP</sub> )                    | 1.65V to 3.6V                        |

| Operating Temperature (T <sub>A</sub> ) (Note 2)      | $-30^{\circ}C$ to $+$ 70 $^{\circ}C$ |

| Supply Noise Voltage (V <sub>DDA-PP</sub> )           | 100 mV <sub>P-P</sub>                |

Note 2: Absolute maximum ratings are DC values beyond which the device may be damaged or have its useful life impaired. The datasheet specifications should be met, without exception, to ensure that the system design is reliable over its power supply, temperature, and output/input loading variables. Fairchild does not recommend operation outside datasheet specifications.

#### DC Electrical Characteristics Over supply voltage and operating temperature ranges, unless otherwise specified.

| Symbol           | Parameter                       | Test C                                                    | conditions                                                                            | Min                     | Typ<br>(Note 3) | Мах                     | Unit |

|------------------|---------------------------------|-----------------------------------------------------------|---------------------------------------------------------------------------------------|-------------------------|-----------------|-------------------------|------|

| LVCMOS I/O       | ·                               | •                                                         |                                                                                       |                         |                 |                         |      |

| V <sub>IH</sub>  | Input High Voltage              |                                                           |                                                                                       | 0.65 x V <sub>DDP</sub> |                 | V <sub>DDP</sub>        |      |

| V <sub>IL</sub>  | Input Low Voltage               |                                                           |                                                                                       | GND                     |                 | 0.35 x V <sub>DDP</sub> | V    |

| V <sub>OH</sub>  | Output High Voltage             |                                                           | $V_{DDP}=3.3\pm0.3$                                                                   |                         |                 |                         |      |

|                  |                                 | I <sub>OH</sub> = -2.0 mA                                 | $V_{DDP} = 2.5 \pm 0.2$                                                               | 0.75 x V <sub>DDP</sub> |                 |                         | V    |

|                  |                                 |                                                           | $V_{DDP}=1.8\pm0.15$                                                                  |                         |                 |                         |      |

| V <sub>OL</sub>  | Output Low Voltage              |                                                           | $V_{DDP}=3.3\pm0.3$                                                                   |                         |                 |                         |      |

|                  | I <sub>OL</sub> = 2.0 mA        | I <sub>OL</sub> = 2.0 mA                                  | $V_{DDP} = 2.5 \pm 0.2$                                                               |                         |                 | 0.25 x V <sub>DDP</sub> | V    |

|                  |                                 |                                                           | $V_{DDP}=1.8\pm0.15$                                                                  |                         |                 |                         |      |

| I <sub>IN</sub>  | Input Current                   | V <sub>IN</sub> = 0V to 3.6V                              |                                                                                       | -5.0                    |                 | 5.0                     | μA   |

| DIFFERENTIAL     | 1/0                             | •                                                         |                                                                                       |                         |                 |                         |      |

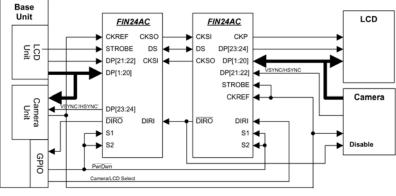

| I <sub>ODH</sub> | Output HIGH Source Current      | V <sub>OS</sub> = 1.0V, Figure                            | 11                                                                                    |                         | -1.75           |                         | mA   |

| I <sub>ODL</sub> | Output LOW Sink Current         | V <sub>OS</sub> = 1.0V, Figure                            | $V_{OS}$ = 1.0V, Figure 11<br>$V_{OS}$ = 1.0V, Figure 11                              |                         | 0.950           |                         | mA   |

| I <sub>OZ</sub>  | Disabled Output Leakage Current | CKSO, DSO = 0V to                                         | V <sub>OS</sub> = 1.0V, Figure 11   CKSO, DSO = 0V to V <sub>DDS</sub> , S2 = S1 = 0V |                         | ±0.1            | ±5.0                    | μA   |

| I <sub>IZ</sub>  | Disabled Input Leakage Current  | CKSI, DSI = 0V to V                                       | / <sub>DDS</sub> , S2 = S1 = 0V                                                       |                         | ±0.1            | ±5.0                    | μA   |

| VICM             | Input Common Mode Range         | $V_{DDS}$ = 2.775 ± 5%                                    |                                                                                       |                         | $V_{GO} + 0.80$ |                         | V    |

| V <sub>GO</sub>  | Input Voltage Ground Off-set    | see Figure 12                                             |                                                                                       |                         |                 |                         |      |

|                  | Relative to Driver (Note 4)     |                                                           |                                                                                       |                         | 0               |                         | V    |

| R <sub>TRM</sub> | CKSI Internal Receiver          | V <sub>ID</sub> = 50mV, V <sub>IC</sub> = 9               | 25mV, DIRI = 0                                                                        | 80.0                    | 400             | 400                     |      |

|                  | Termination Resistor            | CKSI <sup>+</sup> - CKSI <sup>−</sup>   = V <sub>ID</sub> |                                                                                       |                         | 100             | 120                     | Ω    |

| R <sub>TRM</sub> | DSI Internal Receiver           | V <sub>ID</sub> = 50mV, V <sub>IC</sub> = 9               | $V_{ID} = 50$ mV, $V_{IC} = 925$ mV, DIRI = 0<br>  DSI+ - DSI-   = $V_{ID}$           |                         |                 |                         |      |

|                  | Termination Resistor            | DSI+ - DSI-   = V <sub>II</sub>                           |                                                                                       |                         |                 | 120                     | Ω    |

Note 3: Typical Values are given for  $V_{DD}$  = 2.775V and  $T_A$  = 25°C. Positive current values refer to the current flowing into device and negative values means current flowing out of pins. Voltage are referenced to GROUND unless otherwise specified (except  $\Delta V_{OD}$  and  $V_{OD}$ ).

Note 4:  $V_{GO}$  is the difference in device ground levels between the CTL Driver and the CTL Receiver.

# Power Supply Currents

| Symbol             | Parameter                                     | Test Co                 | nditions                             |                 | Min | Тур  | Max | Units |

|--------------------|-----------------------------------------------|-------------------------|--------------------------------------|-----------------|-----|------|-----|-------|

| I <sub>DDA1</sub>  | V <sub>DDA</sub> Serializer Static            | All DP and Control Inpu | uts at 0V or \                       | / <sub>DD</sub> |     | 450  |     |       |

|                    | Supply Current                                | NOCKREF, S2 = 0, S1     | NOCKREF, S2 = 0, S1 = 1, DIR = 1     |                 |     | 450  |     | μΑ    |

| I <sub>DDA2</sub>  | V <sub>DDA</sub> Deserializer Static          | All DP and Control Inpu | uts at 0V or \                       | / <sub>DD</sub> |     | 550  |     |       |

|                    | Supply Current                                | NOCKREF, S2 = 0, S1     | = 1, DIR = 0                         | 1               |     | 550  |     | μA    |

| I <sub>DDS1</sub>  | V <sub>DDS</sub> Serializer Static            | All DP and Control Inpu | uts at 0V or \                       | / <sub>DD</sub> |     | 4.0  |     |       |

|                    | Supply Current                                | NOCKREF, S2 = 0, S1     | = 1, DIR = 1                         |                 |     | 4.0  |     | mA    |

| I <sub>DDS2</sub>  | V <sub>DDS</sub> Deserializer Static          | All DP and Control Inpu | uts at 0V or \                       | / <sub>DD</sub> |     | 4.5  |     |       |

|                    | Supply Current                                | NOCKREF, S2 = 0, S1     | = 1, DIR = 0                         | 1               |     | 4.0  |     | mA    |

| I <sub>DD_PD</sub> | V <sub>DD</sub> Power-Down Supply Current     | S1 = S2 = 0,            |                                      |                 |     | 0.1  |     |       |

|                    | $I_{DD\_PD} = I_{DDA} + I_{DDS} + I_{DDP}$    | All Inputs at GND or V  | All Inputs at GND or V <sub>DD</sub> |                 |     | 0.1  |     | μA    |

| IDD_SER1           | 26:1 Dynamic Serializer                       |                         | S2 = L                               | 2 MHz           |     | 9.0  |     |       |

|                    | Power Supply Current                          | CKREF = STROBE          | S1 = H                               | 5 MHz           |     | 14.0 |     |       |

|                    | $I_{DD\_SER1} = I_{DDA} + I_{DDS} + I_{DDP}$  | DIRI = H                | S2 = H                               | 5 MHz           |     | 9.5  |     |       |

|                    |                                               | See Figure 13           | S1 = L                               | 15 MHz          |     | 17.0 |     | mA    |

|                    |                                               |                         | S2 = H                               | 10 MHz          |     | 11.0 |     |       |

|                    |                                               |                         | S1 = H                               | 20 MHz          |     | 15.5 |     |       |

| IDD_DES1           | 1:26 Dynamic Deserializer                     |                         | S2 = L                               | 2 MHz           |     | 5.5  |     |       |

|                    | Power Supply Current                          | CKREF = STROBE          | S1 = H                               | 5 MHz           |     | 6.0  |     |       |

|                    | $I_{DD_{DES1}} = I_{DDA} + I_{DDS} + I_{DDP}$ | DIRI = L                | S2 = H                               | 5 MHz           |     | 4.0  |     | mA    |

|                    |                                               | See Figure 13           | S1 = L                               | 15 MHz          |     | 5.5  |     | ma    |

|                    |                                               |                         | S2 = H                               | 10 MHz          |     | 7.5  |     |       |

|                    |                                               |                         | S1 = H                               | 20 MHz          |     | 10.0 |     |       |

| IDD_SER2           | 26:1 Dynamic Serializer Power                 | NO CKREF                | NO CKREF 2 M                         |                 |     | 8.0  |     |       |

|                    | Supply Current                                | $STROBE \to Active$     |                                      | 5 MHz           |     | 8.5  |     | ~^^   |

|                    | $I_{DD\_SER2} = I_{DDA} + I_{DDS} + I_{DDP}$  | CKSI = 15X Strobe       |                                      | 10 MHz          |     | 10.0 |     | mA    |

|                    |                                               | DIRI = H See Figure 13  | 3                                    | 15 MHz          |     | 12.0 |     |       |

#### AC Electrical Characteristics Over supply voltage and operating temperature ranges, unless otherwise specified.

| Symbol              | Parameter                                     | Test Conditions                                                 |                           | Min                  | Typ<br>(Note 5) | Max         | Units |

|---------------------|-----------------------------------------------|-----------------------------------------------------------------|---------------------------|----------------------|-----------------|-------------|-------|

| Serializer Input    | Operating Conditions                          |                                                                 |                           |                      |                 |             |       |

| t <sub>TCP</sub>    | CKREF Clock Period                            | See Figure 17                                                   | S2 = 0 S1 = 1             | 200                  |                 | 500         |       |

|                     | (2 MHz - 20 MHz)                              | CKREF = STROBE                                                  | S2 = 1 S1 = 0             | 66.0                 | т               | 200         | ns    |

|                     |                                               |                                                                 | S2 = 1 S1 = 1             | 50.0                 |                 | 100         |       |

| f <sub>REF</sub>    | CKREF Frequency Relative                      | CKREF                                                           | S2 = 0 S1 = 1             |                      |                 | 5.0         |       |

|                     | to Strobe Frequency                           | does not equal                                                  | S2 = 1 S1 = 0             | 1.1 *f <sub>ST</sub> |                 | 15.0        | MHz   |

|                     |                                               | STROBE                                                          | S2 = 1 S1 = 1             |                      |                 | 20.0        |       |

| t <sub>CPWH</sub>   | CKREF Clock High Time                         |                                                                 | -                         | 0.2                  | 0.5             |             | Т     |

| t <sub>CPWL</sub>   | CKREF Clock Low Time                          |                                                                 |                           | 0.2                  | 0.5             |             | т     |

| t <sub>CLKT</sub>   | LVCMOS Input Transition Time                  | See Figure 17                                                   |                           |                      |                 | 90.0        | ns    |

| t <sub>SPWH</sub>   | STROBE Pulse Width HIGH/LOW                   | See Figure 17                                                   |                           | (T x 4)/26           |                 | (T x 22)/26 | ns    |

| f <sub>MAX</sub>    | Maximum Serial Data Rate                      | CKREF x 26                                                      | S2 = 0 S1 = 1             | 52.0                 |                 | 130         |       |

|                     |                                               |                                                                 | S2 = 1 S1 = 0             | 130                  |                 | 390         | Mb/s  |

|                     |                                               |                                                                 | S2 = 1 S1 = 1             | 260                  |                 | 520         |       |

| t <sub>STC</sub>    | DP <sub>(n)</sub> Setup to STROBE             | DIRI = 1                                                        | 2.5                       |                      |                 | ns          |       |

| t <sub>нтс</sub>    | DP <sub>(n)</sub> Hold to STROBE              | see Figure 6 (f = 5MH:                                          | 2.0                       |                      |                 | ns          |       |

| f <sub>REF</sub>    | CKREF Frequency Relative to Strobe Frequency  | CKREF Does Not Equ                                              | 1.1 x f <sub>STROBE</sub> |                      | 20.0            | MHz         |       |

| Serializer AC El    | ectrical Characteristics                      |                                                                 |                           |                      |                 |             |       |

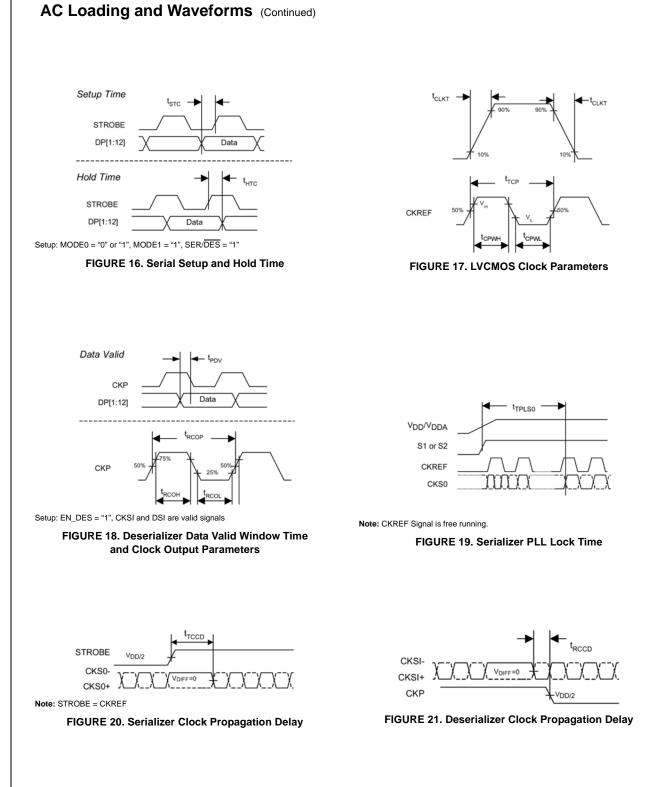

| t <sub>TCCD</sub>   | Transmitter Clock Input to                    | See Figure 20, DIRI =                                           | 222 4 5                   |                      | 250 . 0.5       |             |       |

|                     | Clock Output Delay                            | CKREF = STROBE                                                  |                           | 33a + 1.5            |                 | 35a + 6.5   | ns    |

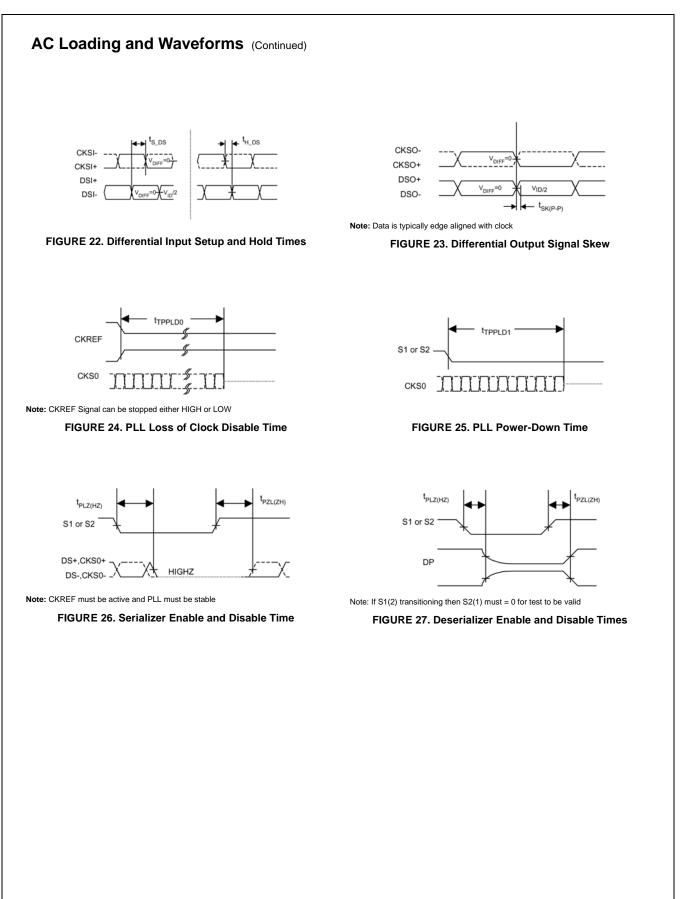

| t <sub>SPOS</sub>   | CKSO Position Relative to DS                  | See Figure 23, (Note 6                                          | i)                        | -50.0                |                 | 250         | ps    |

| PLL AC Electric     | al Characteristics                            |                                                                 |                           |                      |                 |             |       |

| t <sub>TPLLS0</sub> | Serializer Phase Lock Loop Stabilization Time | See Figure 19                                                   |                           |                      |                 | 200         | μS    |

| t <sub>TPLLD0</sub> | PLL Disable Time Loss of Clock                | See Figure 24                                                   |                           |                      |                 | 30.0        | μS    |

| t <sub>TPLLD1</sub> | PLL Power-Down Time                           | See Figure 25, (Note 7                                          | )                         |                      |                 | 20.0        | ns    |

| Deserializer Inp    | ut Operation Conditions                       |                                                                 |                           |                      |                 |             |       |

| ts_DS               | Serial Port Setup Time, DS-to-CKSI            | Figure 22, (Note 8)                                             |                           | 1.4                  |                 |             | ns    |

| t <sub>H_DS</sub>   | Serial Port Hold Time, DS-to-CKS              | Figure 22, (Note 8)                                             |                           | -250                 |                 |             | ps    |

| Deserializer AC     | Electrical Characteristics                    |                                                                 |                           |                      |                 |             |       |

| t <sub>RCOP</sub>   | Deserializer Clock Output (CKP OUT) Period    | Figure 18                                                       |                           | 50.0                 | Т               | 500         | ns    |

| t <sub>RCOL</sub>   | CKP OUT Low Time                              | Figure 18 (Rising Edge Strobe)                                  |                           | 13a-3                |                 | 13a+3       | ns    |

| t <sub>RCOH</sub>   | CKP OUT High Time                             | Serializer Source STROBE = CKREF<br>Where a = (1/f)/26 (Note 9) |                           | 13a-3                |                 | 13a+3       | ns    |

| t <sub>PDV</sub>    | Data Valid to CKP LOW                         | Figure 18 (Rising Edge                                          | e Strobe)                 | 8a-6                 |                 | 8a+1        | ns    |

|                     |                                               | Where a = (1/f)/26 (No                                          | te 9)                     |                      |                 |             |       |

| t <sub>ROLH</sub>   | Output Rise Time (20% to 80%)                 | C <sub>L</sub> = 5 pF                                           |                           |                      | 2.5             |             | ns    |

| tROHL               | Output Fall time (80% to 20%)                 | Figure 15                                                       |                           |                      | 2.5             |             | ns    |

Note 5: Typical Values are given for  $V_{DD}$  = 2.775V and  $T_A$  = 25°C. Positive current values refer to the current flowing into device and negative values means current flowing out of pins. Voltage are referenced to GROUND unless otherwise specified (except  $\Delta V_{OD}$  and  $V_{OD}$ ).

Note 6: Skew is measured form either the rising or falling edge of CKSO clock to the rising or falling edge of data (DSO). Signals are edge aligned. Both outputs should have identical load conditions for this test to be valid.

Note 7: The power-down time is a function of the CKREF frequency prior to CKREF being stopped HIGH or LOW and the state of the S1/S2 mode pins. The specific number of clock cycles required for the PLL to be disabled will vary dependent upon the operating mode of the device.

Note 8: Signals are transmitted from the serializer source synchronously. Note that in some cases data is transmitted when the clock remains at a high state. Skew should only be measured when data and clock are transitioning at the same time. Total measured input skew would be a combination of output skew from the serializer, load variations and ISI and jitter effects.

Note 9: Rising edge of CKP will appear approximately 13 bit times after the falling edge of the CKP output. Falling edge of CKP will occur approximately 8 bit times after a data transition or 6 bit times after the falling edge of CKSO. Variation of the data with respect of the CKP signal is due to internal propagation delay differences of the data and CKP path and propagation delay differences on the various data pins. Note that if the CKREF is not equal to STROBE for the serializer then the CKP signal will not maintain a 50% duty cycle. The low time of CKP will remain 13 bit times.

# **Control Logic Timing Controls**

| Symbol                 | Parameter                  | Test Conditions                             | Min | Тур | Max  | Units |

|------------------------|----------------------------|---------------------------------------------|-----|-----|------|-------|

| t <sub>PHL_DIR</sub> , | Propagation Delay          | DIRI LOW-to-HIGH or HIGH-to-LOW             |     |     | 17.0 |       |

| t <sub>PLH_DIR</sub>   | DIRI-to-DIRO               | DIRI LOW-IO-HIGH OF HIGH-IO-LOW             |     |     | 17.0 | ns    |

| t <sub>PLZ</sub> ,     | Propagation Delay          |                                             |     |     | 25.0 |       |

| t <sub>PHZ</sub>       | DIRI-to-DP                 | DIRI LOW-to-HIGH                            |     |     | 25.0 | ns    |

| t <sub>PZL</sub> ,     | Propagation Delay          |                                             |     |     | 05.0 |       |

| t <sub>PZH</sub>       | DIRI-to-DP                 | DIRI HIGH-to-LOW                            |     |     | 25.0 | ns    |

| t <sub>PLZ</sub> ,     | Deserializer Disable Time: | DIRI = 0,                                   |     |     | 05.0 |       |

| t <sub>PHZ</sub>       | S0 or S1 to DP             | S1(2) = 0 and S2(1) = LOW-to-HIGH Figure 26 |     |     | 25.0 | ns    |

| t <sub>PZL</sub> ,     | Deserializer Enable Time:  | DIRI = 0, (Note 10)                         |     |     |      | _     |

| t <sub>PZH</sub>       | S0 or S1 to DP             | S1(2) = 0 and S2(1) = LOW-to-HIGH Figure 26 |     |     | 2.0  | μS    |

| t <sub>PLZ</sub> ,     | Serializer Disable Time:   | DIRI = 1,                                   |     |     | 05.0 |       |

| t <sub>PHZ</sub>       | S0 or S1 to CKSO, DS       | S1(2) = 0 and S2(1) = HIGH-to-LOW Figure 25 |     |     | 25.0 | ns    |

| t <sub>PZL</sub> ,     | Serializer Enable Time:    | DIRI = 1,                                   |     |     | 05.0 |       |

| t <sub>PZH</sub>       | S0 or S1 to CKSO, DS       | S1(2) and S2(1) = LOW-to-HIGH Figure 25     |     |     | 65.0 | ns    |

Note 10: Deserializer Enable Time includes the amount of time required for internal voltage and current references to stabilize. This time is significantly less than the PLL Lock Time and therefore will not limit overall system startup time.

# Capacitance

| Symbol               | Parameter                               | Test Conditions          | Min | Тур | Max | Units |  |    |

|----------------------|-----------------------------------------|--------------------------|-----|-----|-----|-------|--|----|

| C <sub>IN</sub>      | Capacitance of Input Only Signals,      | DIRI = 1, S1 = S2 = 0,   |     | 2.0 |     | pF    |  |    |

|                      | CKREF, STROBE, S1, S2, DIRI             | V <sub>DD</sub> = 2.5V   |     | 2.0 |     | рн    |  |    |

| C <sub>IO</sub>      | Capacitance of Parallel Port Pins       | DIRI = 1, S1 = S2 = 0,   |     | 2.0 |     | - 5   |  |    |

|                      | DP <sub>1:12</sub>                      | V <sub>DD</sub> = 2.5V   |     | 2.0 |     | pF    |  |    |

| C <sub>IO-DIFF</sub> | Capacitance of Differential I/O Signals | DIRI = 0, S1 = S2 = 0,   |     | 2.0 |     |       |  | pF |

|                      |                                         | V <sub>DD</sub> = 2.775V | 2.0 |     |     | рн    |  |    |

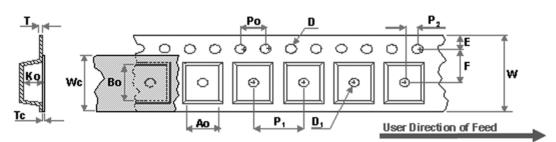

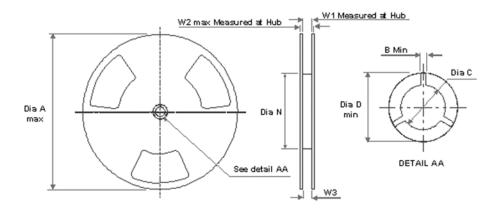

### **Tape and Reel Specification**

#### **Dimensions are in millimeters**

| Package   | A <sub>0</sub> | B <sub>0</sub> | D     | D <sub>1</sub> | Е            | F            | K <sub>0</sub> | <b>P</b> <sub>1</sub> | P <sub>0</sub> | P <sub>2</sub> | Т   | т <sub>с</sub> | W    | W <sub>C</sub> |

|-----------|----------------|----------------|-------|----------------|--------------|--------------|----------------|-----------------------|----------------|----------------|-----|----------------|------|----------------|

| I denage  | ±0.10          | ±0.10          | ±0.05 | min            | ± <b>0.1</b> | ± <b>0.1</b> | ± <b>0.1</b>   | TYP                   | TYP            | ±0/05          | TYP | ±0.005         | ±0.3 | TYP            |

| 3.5 x 4.5 | TBD            | TBD            | 1.55  | 1.5            | 1.75         | 5.5          | 1.1            | 8.0                   | 4.0            | 2.0            | 0.3 | 0.07           | 12.0 | 9.3            |

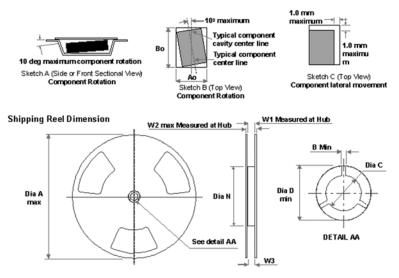

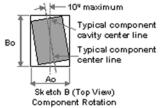

Note: A0, B0, and K0 dimensions are determined with respect to the EIA/JEDEC RS-481 rotational and lateral movement requirements (see sketches A, B, and C).

#### **Dimensions are in millimeters**

| Таре  | Dia A | Dim B | Dia C     | Dia D | Dim N | Dim W1           | Dim W2 | Dim W3      |

|-------|-------|-------|-----------|-------|-------|------------------|--------|-------------|

| Width | max   | min   | +0.5/-0.2 | min   | min   | + <b>2.0/</b> -0 | max    | (LSL - USL) |

| 8     | 330   | 1.5   | 13.0      | 20.2  | 178   | 8.4              | 14.4   | 7.9 ~ 10.4  |

| 12    | 330   | 1.5   | 13.0      | 20.2  | 178   | 12.4             | 18.4   | 11.9 ~ 15.4 |

| 16    | 330   | 1.5   | 13.0      | 20.2  | 178   | 16.4             | 22.4   | 15.9 ~ 19.4 |

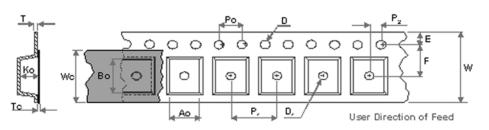

#### Tape and Reel Specification (continued)

Dimensions are in millimeters

| Package | Ao<br>±0.10 | Во<br>±0.10 | D<br>±0.05 | D <sub>1</sub><br>min | Е<br>±0.1 | F<br>±0.1 | Ко<br>±0.1 | P <sub>1</sub><br>TYP | Po<br>TYP | P <sub>2</sub><br>±0/05 | T<br>TYP | Тс<br>±0.005 | W<br>±0.3 | Wc<br>TYP |

|---------|-------------|-------------|------------|-----------------------|-----------|-----------|------------|-----------------------|-----------|-------------------------|----------|--------------|-----------|-----------|

| 5 x 5   | 5.35        | 5.35        | 1.55       | 1.5                   | 1.75      | 5.5       | 1.4        | 8                     | 4         | 2.0                     | 0.3      | 0.07         | 12        | 9.3       |

| 6 x 6   | 6.30        | 6.30        | 1.55       | 1.5                   | 1.75      | 5.5       | 1.4        | 8                     | 4         | 2.0                     | 0.3      | 0.07         | 12        | 9.3       |

Note: Ao, Bo, and Ko dimensions are determined with respect to the EIA / JEDEC RS-481 rotational and lateral movement requirements (see sketches A, B, and C).

10 deg maximum component rotation Sketch A (Side or Front Sectional View)

**Component Rotation**

Sk etch C (Top View) Component lateral movement

#### **Dimensions are in millimeters**

| Tape Width | Dia A<br>max | Dim B<br>min | Dia C<br>+.5/–.2 | Dia D<br>min | Dim N<br>min | Dim W1<br>+.2/-0 | Dim W2<br>max | Dim W3<br>(LSL - USL) |

|------------|--------------|--------------|------------------|--------------|--------------|------------------|---------------|-----------------------|

| 8          | 330          | 1.5          | 13               | 20.2         | 178          | 8.4              | 14.4          | 7.9 ~10.4             |

| 12         | 330          | 1.5          | 13               | 20.2         | 178          | 12.4             | 18.4          | 11.9 ~ 15.4           |

| 16         | 330          | 1.5          | 13               | 20.2         | 178          | 16.4             | 22.4          | 15.9 ~ 19.4           |

#### DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION

#### As used herein:

1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, or (c) whose failure to perform when properly used in accordance with instructions for use

provided in the labeling, can be reasonably expected to result in significant injury to the user.

2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### **PRODUCT STATUS DEFINITIONS**

| <b>Datasheet Identification</b> | Product Status         | Definition                                                                                                                                                                                                                  |  |  |  |  |  |

|---------------------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Advance Information             | Formative or In Design | This datasheet contains the design specifications for product develop-<br>ment. Specifications may change in any manner without notice.                                                                                     |  |  |  |  |  |

| Preliminary                     | First Production       | This datasheet contains preliminary data, and supplementary data will<br>be published at a later date. Fairchild Semiconductor reserves the right<br>to make changes at any time without notice in order to improve design. |  |  |  |  |  |

| No Identification Needed        | Full Production        | This datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice in order to improve design.                                                             |  |  |  |  |  |

| Obsolete                        | Not In Production      | This datasheet contains specifications on a product that has been dis-<br>continued by Fairchild Semiconductor. The datasheet is printed for ref-<br>erence information only.                                               |  |  |  |  |  |