October 2006

# FSB32560 Smart Power Module

## **Features**

- UL Certified No.E209204(SPM27-BC package)

- 600V-25A 3-phase IGBT inverter bridge including control ICs for gate driving and protection

- Divided negative dc-link terminals for inverter current sensing applications

- Single-grounded power supply due to built-in HVIC

- Isolation rating of 2500Vrms/min.

- Very low leakage current due to using ceramic substrate

## **Applications**

- AC 100V ~ 253V three-phase inverter drive for small power ac motor drives

- Home appliances applications like air conditioner and washing machine

## **General Description**

It is an advanced smart power module (SPM™) that Fairchild has newly developed and designed to provide very compact and high performance ac motor drives mainly targeting low-power inverter-driven application like air conditioner and washing machine. It combines optimized circuit protection and drive matched to low-loss IGBTs. System reliability is further enhanced by the integrated under-voltage lock-out and short-circuit protection. The high speed built-in HVIC provides opto-coupler-less single-supply IGBT gate driving capability that further reduce the overall size of the inverter system design. Each phase current of inverter can be monitored separately due to the divided negative dc terminals.

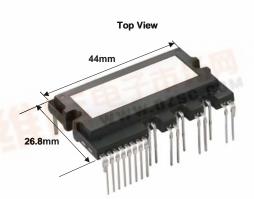

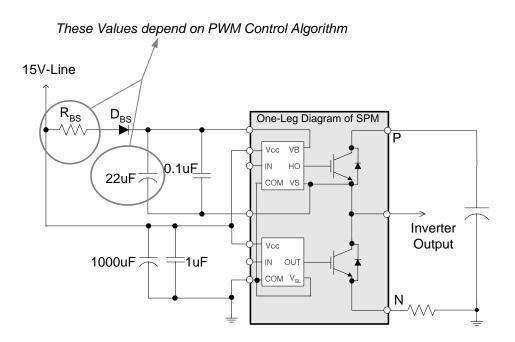

Figure 1.

## **Integrated Power Functions**

• 600V-25A IGBT inverter for three-phase DC/AC power conversion (Please refer to Figure 3)

## Integrated Drive, Protection and System Control Functions

- For inverter high-side IGBTs: Gate drive circuit, High voltage isolated high-speed level shifting

Control circuit under-voltage (UV) protection

Note) Available bootstrap circuit example is given in Figures 10 and 11.

- For inverter low-side IGBTs: Gate drive circuit, Short circuit protection (SC)

Control supply circuit under-voltage (UV) protection

- Fault signaling: Corresponding to UV (Low-side supply) and SC faults

- Input interface: 3.3/5V CMOS/LSTTL compatible, Schmitt trigger input

## **Pin Configuration**

### **Top View** 13.3 (1) V<sub>CC(L)</sub> (2) COM (21) $N_U$ 0 0 (3) IN<sub>(UL)</sub> (4) IN<sub>(VL)</sub> (5) IN<sub>(WL)</sub> (22) $N_V$ 19.1 (6) V<sub>FO</sub> (23) $N_W$ (7) C<sub>FOD</sub> (8) C<sub>SC</sub> (9) IN<sub>(UH)</sub> (24) U Case Temperature (T<sub>C</sub>) (10) V<sub>CC(UH)</sub> Detecting Point (11) $V_{B(U)} =$ (12) V<sub>S(U)</sub> □ (25) V (13) IN<sub>(VH)</sub> (14) V<sub>CC(VH)</sub> (15) V<sub>B(V)</sub> = (16) V<sub>S(V)</sub> (26) W (17) IN<sub>(WH)</sub> Ceramic Substrate (18) V<sub>CC(WH)</sub> (19) V<sub>B(W)</sub> <sup>-</sup> (27) P (20) V<sub>S(W)</sub> 5

Figure 2.

# **Pin Descriptions**

| Pin Number | Pin Name            | Pin Description                                               |

|------------|---------------------|---------------------------------------------------------------|

| 1          | V <sub>CC(L)</sub>  | Low-side Common Bias Voltage for IC and IGBTs Driving         |

| 2          | COM                 | Common Supply Ground                                          |

| 3          | IN <sub>(UL)</sub>  | Signal Input for Low-side U Phase                             |

| 4          | IN <sub>(VL)</sub>  | Signal Input for Low-side V Phase                             |

| 5          | IN <sub>(WL)</sub>  | Signal Input for Low-side W Phase                             |

| 6          | V <sub>FO</sub>     | Fault Output                                                  |

| 7          | C <sub>FOD</sub>    | Capacitor for Fault Output Duration Time Selection            |

| 8          | C <sub>SC</sub>     | Capacitor (Low-pass Filter) for Short-Current Detection Input |

| 9          | IN <sub>(UH)</sub>  | Signal Input for High-side U Phase                            |

| 10         | V <sub>CC(UH)</sub> | High-side Bias Voltage for U Phase IC                         |

| 11         | V <sub>B(U)</sub>   | High-side Bias Voltage for U Phase IGBT Driving               |

| 12         | V <sub>S(U)</sub>   | High-side Bias Voltage Ground for U Phase IGBT Driving        |

| 13         | IN <sub>(VH)</sub>  | Signal Input for High-side V Phase                            |

| 14         | V <sub>CC(VH)</sub> | High-side Bias Voltage for V Phase IC                         |

| 15         | V <sub>B(V)</sub>   | High-side Bias Voltage for V Phase IGBT Driving               |

| 16         | V <sub>S(V)</sub>   | High-side Bias Voltage Ground for V Phase IGBT Driving        |

| 17         | IN <sub>(WH)</sub>  | Signal Input for High-side W Phase                            |

| 18         | V <sub>CC(WH)</sub> | High-side Bias Voltage for W Phase IC                         |

| 19         | V <sub>B(W)</sub>   | High-side Bias Voltage for W Phase IGBT Driving               |

| 20         | V <sub>S(W)</sub>   | High-side Bias Voltage Ground for W Phase IGBT Driving        |

| 21         | N <sub>U</sub>      | Negative DC-Link Input for U Phase                            |

| 22         | N <sub>V</sub>      | Negative DC-Link Input for V Phase                            |

| 23         | N <sub>W</sub>      | Negative DC-Link Input for W Phase                            |

| 24         | U                   | Output for U Phase                                            |

| 25         | V                   | Output for V Phase                                            |

| 26         | W                   | Output for W Phase                                            |

| 27         | Р                   | Positive DC–Link Input                                        |

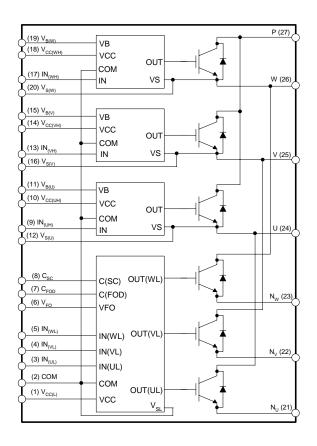

## **Internal Equivalent Circuit and Input/Output Pins**

### Note

- 1. Inverter low-side is composed of three IGBTs, freewheeling diodes for each IGBT and one control IC. It has gate drive and protection functions.

- 2. Inverter power side is composed of four inverter dc-link input terminals and three inverter output terminals.

- 3. Inverter high-side is composed of three IGBTs, freewheeling diodes and three drive ICs for each IGBT.

Figure 3.

## **Absolute Maximum Ratings** (T<sub>J</sub> = 25°C, Unless Otherwise Specified)

## **Inverter Part**

| Symbol                 | Parameter Conditions           |                                                                     | Rating    | Units |

|------------------------|--------------------------------|---------------------------------------------------------------------|-----------|-------|

| V <sub>PN</sub>        | Supply Voltage                 | Applied between P- $N_U$ , $N_V$ , $N_W$                            | 450       | V     |

| V <sub>PN(Surge)</sub> | Supply Voltage (Surge)         | Applied between P- N <sub>U</sub> , N <sub>V</sub> , N <sub>W</sub> | 500       | V     |

| V <sub>CES</sub>       | Collector-emitter Voltage      |                                                                     | 600       | V     |

| ± I <sub>C</sub>       | Each IGBT Collector Current    | $T_C = 25^{\circ}C$                                                 | 25        | Α     |

|                        |                                | T <sub>C</sub> = 100°C                                              | 12        | Α     |

| P <sub>C</sub>         | Collector Dissipation          | T <sub>C</sub> = 25°C per One Chip                                  | 29        | W     |

| T <sub>J</sub>         | Operating Junction Temperature | (Note 1)                                                            | -20 ~ 125 | °C    |

#### Note

## **Control Part**

| Symbol          | Parameter                         | Conditions                                                                                              | Rating                    | Units |

|-----------------|-----------------------------------|---------------------------------------------------------------------------------------------------------|---------------------------|-------|

| V <sub>CC</sub> | Control Supply Voltage            | Applied between $V_{CC(UH)}$ , $V_{CC(VH)}$ , $V_{CC(WH)}$ , $V_{CC(L)}$ - COM                          | 20                        | V     |

| V <sub>BS</sub> | High-side Control Bias<br>Voltage | Applied between $V_{B(U)}$ - $V_{S(U)}$ , $V_{B(V)}$ - $V_{S(V)}$ , $V_{B(W)}$ - $V_{S(W)}$             | 20                        | V     |

| V <sub>IN</sub> | Input Signal Voltage              | Applied between $IN_{(UH)}$ , $IN_{(VH)}$ , $IN_{(WH)}$ , $IN_{(UL)}$ , $IN_{(VL)}$ , $IN_{(WL)}$ - COM | -0.3~17                   | V     |

| V <sub>FO</sub> | Fault Output Supply Voltage       | Applied between V <sub>FO</sub> - COM                                                                   | -0.3~V <sub>CC</sub> +0.3 | V     |

| I <sub>FO</sub> | Fault Output Current              | Sink Current at V <sub>FO</sub> Pin                                                                     | 5                         | mA    |

| V <sub>SC</sub> | Current Sensing Input Voltage     | Applied between C <sub>SC</sub> - COM                                                                   | -0.3~V <sub>CC</sub> +0.3 | V     |

## **Total System**

| Symbol                | Parameter                                                                  | Conditions                                                                                        | Rating    | Units     |

|-----------------------|----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|-----------|-----------|

| V <sub>PN(PROT)</sub> | Self Protection Supply Voltage Limit (Short Circuit Protection Capability) | $V_{CC} = V_{BS} = 13.5 \sim 16.5 V$<br>$T_J = 125^{\circ}C$ , Non-repetitive, less than $2\mu s$ | 400       | V         |

| T <sub>C</sub>        | Module Case Operation Temperature                                          | -20°C≤ T <sub>J</sub> ≤ 125°C, See Figure 2                                                       | -20 ~ 100 | °C        |

| T <sub>STG</sub>      | Storage Temperature                                                        |                                                                                                   | -40 ~ 125 | °C        |

| V <sub>ISO</sub>      | Isolation Voltage                                                          | 60Hz, Sinusoidal, AC 1 minute, Connection<br>Pins to ceramic substrate                            | 2500      | $V_{rms}$ |

## **Thermal Resistance**

| Symbol                | Parameter                | Conditions                          | Min. | Тур. | Max. | Units |

|-----------------------|--------------------------|-------------------------------------|------|------|------|-------|

| R <sub>th(j-c)Q</sub> | Junction to Case Thermal | Inverter IGBT part (per 1/6 module) | -    | -    | 3.5  | °C/W  |

| R <sub>th(j-c)F</sub> | Resistance               | Inverter FWD part (per 1/6 module)  | -    | -    | 4.7  | °C/W  |

### Note:

## **Package Marking and Ordering Information**

| Device Marking | Device   | Package  | Reel Size | Tape Width | Quantity |

|----------------|----------|----------|-----------|------------|----------|

| FSB32560       | FSB32560 | SPM27-BC | -         | -          | 10       |

5

<sup>1.</sup> The maximum junction temperature rating of the power chips integrated within the SPM is  $150^{\circ}C(@T_{C} \le 100^{\circ}C)$ . However, to insure safe operation of the SPM, the average junction temperature should be limited to  $T_{J(ave)} \le 125^{\circ}C$  ( $@T_{C} \le 100^{\circ}C$ )

<sup>2.</sup> For the measurement point of case temperature( $T_{\mbox{\scriptsize C}}$ ), please refer to Figure 2.

## $\textbf{Electrical Characteristics} \ \, (T_J = 25^{\circ}C, \, \text{Unless Otherwise Specified})$

## **Inverter Part**

| S  | ymbol               | Parameter                            | Condi                                                                      | tions                          | Min. | Тур. | Max. | Units |

|----|---------------------|--------------------------------------|----------------------------------------------------------------------------|--------------------------------|------|------|------|-------|

| V  | CE(SAT)             | Collector-Emitter Saturation Voltage | $V_{CC} = V_{BS} = 15V$ $I_{C} = 25A, T_{J} = 25^{\circ}$<br>$V_{IN} = 5V$ |                                | -    | 2.15 | 2.85 | V     |

|    | V <sub>F</sub>      | FWD Forward Voltage                  | V <sub>IN</sub> = 0V                                                       | $I_C = 25A, T_J = 25^{\circ}C$ | -    | 2.20 | 2.90 | V     |

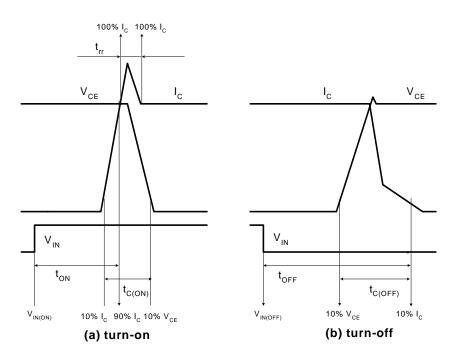

| HS | t <sub>ON</sub>     | Switching Times                      | $V_{PN} = 300V, V_{CC} = V_{BS}$                                           | <sub>S</sub> = 15V             | -    | 0.31 | -    | μS    |

|    | t <sub>C(ON)</sub>  |                                      | $I_C = 12A$<br>$V_{IN} = 0V \leftrightarrow 5V$ , Inducti                  | ve Load                        | -    | 0.15 | -    | μS    |

|    | t <sub>OFF</sub>    |                                      | (Note 3)                                                                   |                                | -    | 0.90 | -    | μS    |

|    | t <sub>C(OFF)</sub> |                                      |                                                                            |                                | -    | 0.34 | -    | μS    |

|    | t <sub>rr</sub>     |                                      |                                                                            |                                | -    | 0.10 | -    | μS    |

| LS | t <sub>ON</sub>     |                                      | $V_{PN} = 300V, V_{CC} = V_{BS}$                                           | <sub>S</sub> = 15V             | -    | 0.58 | -    | μS    |

|    | t <sub>C(ON)</sub>  |                                      | $I_C = 12A$<br>$V_{IN} = 0V \leftrightarrow 5V$ , Inducti                  | ve I nad                       | -    | 0.30 | -    | μS    |

|    | t <sub>OFF</sub>    |                                      | (Note 3)                                                                   | ve Load                        | -    | 0.96 | -    | μS    |

|    | t <sub>C(OFF)</sub> |                                      |                                                                            |                                | -    | 0.37 | -    | μS    |

|    | t <sub>rr</sub>     |                                      |                                                                            |                                | -    | 0.10 | -    | μS    |

|    | I <sub>CES</sub>    | Collector-Emitter<br>Leakage Current | V <sub>CE</sub> = V <sub>CES</sub>                                         |                                | -    | -    | 250  | μА    |

#### Note

<sup>3.</sup>  $t_{ON}$  and  $t_{OFF}$  include the propagation delay time of the internal drive IC.  $t_{C(ON)}$  and  $t_{C(OFF)}$  are the switching time of IGBT itself under the given gate driving condition internally. For the detailed information, please see Figure 4.

Figure 4. Switching Time Definition

# $\textbf{Electrical Characteristics} \ \, (T_J = 25^{\circ}C, \, \text{Unless Otherwise Specified})$

## **Control Part**

| Symbol               | Parameter                                   | Co                                                                                                  | nditions                                                                                       | Min. | Тур. | Max. | Units |

|----------------------|---------------------------------------------|-----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|------|------|------|-------|

| I <sub>QCCL</sub>    | Quiescent V <sub>CC</sub> Supply<br>Current | V <sub>CC</sub> = 15V<br>IN <sub>(UL, VL, WL)</sub> = 0V                                            | V <sub>CC(L)</sub> - COM                                                                       | -    | -    | 23   | mA    |

| Ідссн                |                                             | V <sub>CC</sub> = 15V<br>IN <sub>(UH, VH, WH)</sub> = 0V                                            | V <sub>CC(UH)</sub> , V <sub>CC(VH)</sub> ,<br>V <sub>CC(WH)</sub> - COM                       | -    | -    | 200  | μΑ    |

| I <sub>QBS</sub>     | Quiescent V <sub>BS</sub> Supply<br>Current | $V_{BS} = 15V$<br>$IN_{(UH, VH, WH)} = 0V$                                                          | $egin{array}{c} V_{B(U)} - V_{S(U)}, \ V_{B(V)} - V_{S(V)}, \ V_{B(W)} - V_{S(W)} \end{array}$ | i    | -    | 500  | μА    |

| V <sub>FOH</sub>     | Fault Output Voltage                        | V <sub>SC</sub> = 0V, V <sub>FO</sub> Circu                                                         | it: 4.7kΩ to 5V Pull-up                                                                        | 4.5  | -    | -    | V     |

| V <sub>FOL</sub>     |                                             | V <sub>SC</sub> = 1V, V <sub>FO</sub> Circu                                                         | $V_{SC}$ = 1V, $V_{FO}$ Circuit: 4.7k $\Omega$ to 5V Pull-up                                   |      | -    | 0.8  | V     |

| V <sub>SC(ref)</sub> | Short Circuit Trip Level                    | V <sub>CC</sub> = 15V (Note 4)                                                                      | V <sub>CC</sub> = 15V (Note 4)                                                                 |      | 0.5  | 0.55 | V     |

| UV <sub>CCD</sub>    | Supply Circuit Under-                       | Detection Level                                                                                     |                                                                                                | 10.7 | 11.9 | 13.0 | V     |

| UV <sub>CCR</sub>    | Voltage Protection                          | Reset Level                                                                                         |                                                                                                | 11.2 | 12.4 | 13.2 | V     |

| UV <sub>BSD</sub>    |                                             | Detection Level                                                                                     |                                                                                                | 10   | 11   | 12   | V     |

| UV <sub>BSR</sub>    |                                             | Reset Level                                                                                         | Reset Level                                                                                    |      | 11.5 | 12.5 | V     |

| t <sub>FOD</sub>     | Fault-out Pulse Width                       | C <sub>FOD</sub> = 33nF (Note 5)                                                                    |                                                                                                | 1.0  | 1.8  | -    | ms    |

| V <sub>IN(ON)</sub>  | ON Threshold Voltage                        | Applied between IN <sub>(UH)</sub> , IN <sub>(VH)</sub> , IN <sub>(WH)</sub> , IN <sub>(UL)</sub> , |                                                                                                | 3.0  | -    | -    | V     |

| V <sub>IN(OFF)</sub> | OFF Threshold Voltage                       | $IN_{(VL)}$ , $IN_{(WL)}$ - COM                                                                     |                                                                                                | Ī    | -    | 0.8  | V     |

#### Note

# **Recommended Operating Conditions**

| Symbol                                        | Parameter                              | Conditions                                                                                  | Value |      |      | Units |

|-----------------------------------------------|----------------------------------------|---------------------------------------------------------------------------------------------|-------|------|------|-------|

| Symbol                                        | Parameter                              | Conditions                                                                                  | Min.  | Тур. | Max. | Units |

| V <sub>PN</sub>                               | Supply Voltage                         | Applied between P - N <sub>U</sub> , N <sub>V</sub> , N <sub>W</sub>                        | -     | 300  | 400  | V     |

| V <sub>CC</sub>                               | Control Supply Voltage                 | Applied between $V_{CC(UH)}$ , $V_{CC(VH)}$ , $V_{CC(WH)}$ , $V_{CC(WH)}$ ,                 | 13.5  | 15   | 16.5 | V     |

| V <sub>BS</sub>                               | High-side Bias Voltage                 | Applied between $V_{B(U)}$ - $V_{S(U)}$ , $V_{B(V)}$ - $V_{S(V)}$ , $V_{B(W)}$ - $V_{S(W)}$ | 13.0  | 15   | 18.5 | V     |

| dV <sub>CC</sub> /dt,<br>dV <sub>BS</sub> /dt | Control supply variation               |                                                                                             | -1    | ı    | 1    | V/μs  |

| t <sub>dead</sub>                             | Blanking Time for Preventing Arm-short | For Each Input Signal                                                                       | 2.0   | -    | -    | μ\$   |

| f <sub>PWM</sub>                              | PWM Input Signal                       | $-20^{\circ}C \leq T_{C} \leq 100^{\circ}C, \ -20^{\circ}C \leq T_{J} \leq 125^{\circ}C$    | -     | i    | 20   | kHz   |

| V <sub>SEN</sub>                              | Voltage for Current Sensing            | Applied between $N_U$ , $N_V$ , $N_W$ - COM (Including surge voltage)                       | -4    |      | 4    | V     |

<sup>4.</sup> Short-circuit current protection is functioning only at the low-sides.

<sup>5.</sup> The fault-out pulse width  $t_{FOD}$  depends on the capacitance value of  $C_{FOD}$  according to the following approximate equation:  $C_{FOD} = 18.3 \times 10^{-6} \times t_{FOD}[F]$

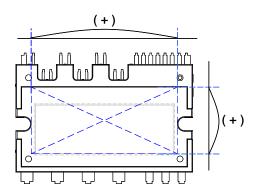

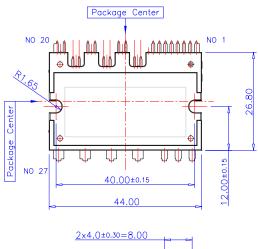

# **Mechanical Characteristics and Ratings**

| Parameter       | Cor                  | Limits              |      |      | Units  |            |

|-----------------|----------------------|---------------------|------|------|--------|------------|

| Farameter       | Col                  | Min.                | Тур. | Max. | Ullits |            |

| Mounting Torque | Mounting Screw: - M3 | Recommended 0.62N•m | 0.51 | 0.62 | 0.72   | N•m        |

| Device Flatness |                      | Note Figure 5       | 0    | -    | +120   | μ <b>m</b> |

| Weight          |                      |                     | -    | 15.4 | -      | g          |

Figure 5. Flatness Measurement Position

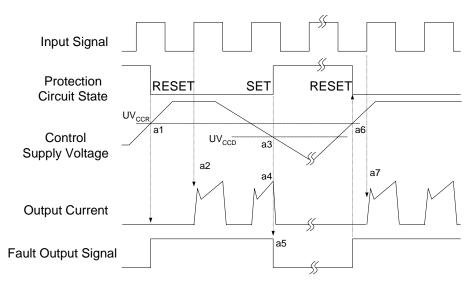

## **Time Charts of SPMs Protective Function**

- a1 : Control supply voltage rises: After the voltage rises  $UV_{CCR}$ , the circuits start to operate when next input is applied.

- a2: Normal operation: IGBT ON and carrying current.

- a3 : Under voltage detection (UV<sub>CCD</sub>).

- a4: IGBT OFF in spite of control input condition.

- a5 : Fault output operation starts.

- a6 : Under voltage reset ( $UV_{CCR}$ ).

- a7: Normal operation: IGBT ON and carrying current.

Figure 6. Under-Voltage Protection (Low-side)

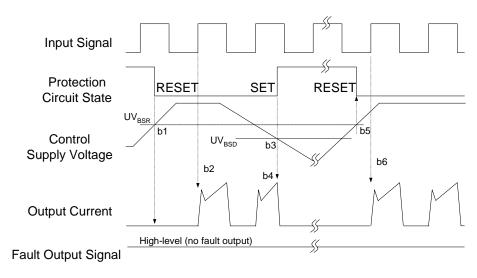

- b1 : Control supply voltage rises: After the voltage reaches UV<sub>BSR</sub>, the circuits start to operate when next input is applied.

- b2: Normal operation: IGBT ON and carrying current.

- b3: Under voltage detection (UV<sub>BSD</sub>).

- b4: IGBT OFF in spite of control input condition, but there is no fault output signal.

- b5 : Under voltage reset ( $UV_{BSR}$ )

- b6: Normal operation: IGBT ON and carrying current

Figure 7. Under-Voltage Protection (High-side)

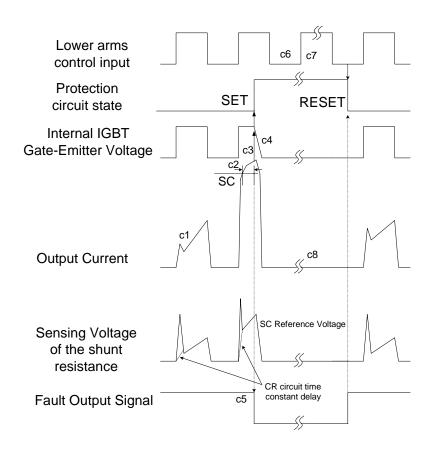

(with the external shunt resistance and CR connection)

- c1 : Normal operation: IGBT ON and carrying current.

- c2 : Short circuit current detection (SC trigger).

- c3: Hard IGBT gate interrupt.

- c4: IGBT turns OFF.

- c5 : Fault output timer operation starts: The pulse width of the fault output signal is set by the external capacitor  $C_{FO}$ .

- c6 : Input "L" : IGBT OFF state.

- c7: Input "H": IGBT ON state, but during the active period of fault output the IGBT doesn't turn ON.

- c8: IGBT OFF state

Figure 8. Short-Circuit Current Protection (Low-side Operation only)

#### Note

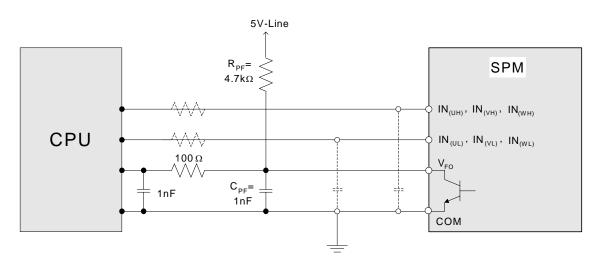

- 1) RC coupling at each input (parts shown dotted) might change depending on the PWM control scheme used in the application and the wiring impedance of the application's printed circuit board. The SPM input signal section integrates 3.3kΩ (typ.) pull-down resistor. Therefore, when using an external filtering resistor, please pay attention to the signal voltage drop at input terminal.

- 2) The logic input is compatible with standard CMOS or LSTTL outputs.

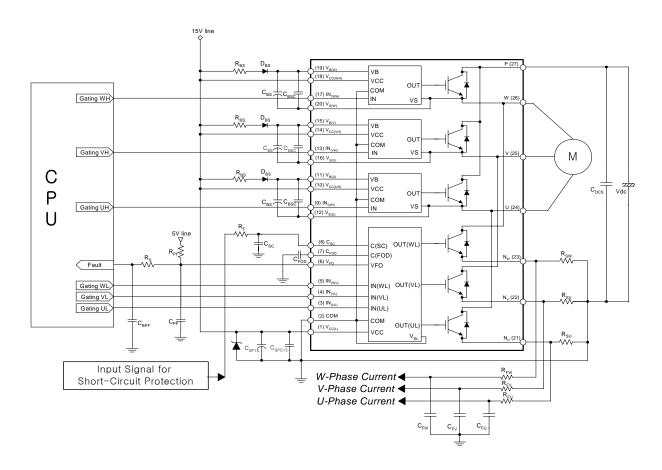

Figure 9. Recommended CPU I/O Interface Circuit

### Note:

- 1) It would be recommended that the bootstrap diode,  $D_{BS}$ , has soft and fast recovery characteristics.

- 2) The ceramic capacitor placed between V<sub>CC</sub>-COM should be over 1uF and mounted as close to the pins of the SPM as possible.

Figure 10. Recommended Bootstrap Operation Circuit and Parameters

### Note:

- 1) To avoid malfunction, the wiring of each input should be as short as possible. (less than 2-3cm)

- 2) By virtue of integrating an application specific type HVIC inside the SPM, direct coupling to CPU terminals without any opto-coupler or transformer isolation is possible.

- 3)  $V_{FO}$  output is open collector type. This signal line should be pulled up to the positive side of the 5V power supply with approximately  $4.7k\Omega$  resistance. Please refer to Figure 9.

- 4)  $C_{SP15}$  of around 7 times larger than bootstrap capacitor  $C_{BS}$  is recommended.

- 5)  $V_{FO}$  output pulse width should be determined by connecting an external capacitor( $C_{FOD}$ ) between  $C_{FOD}$ (pin7) and COM(pin2). (Example : if  $C_{FOD}$  = 33 nF, then  $t_{FO}$  = 1.8ms (typ.)) Please refer to the note 5 for calculation method.

- 6) Input signal is High-Active type. There is a 3.3kΩ resistor inside the IC to pull down each input signal line to GND. When employing RC coupling circuits, set up such RC couple that input signal agree with turn-off/turn-on threshold voltage.

- 7) To prevent errors of the protection function, the wiring around  $R_{\text{F}}$  and  $C_{\text{SC}}$  should be as short as possible.

- 8) In the short-circuit protection circuit, please select the  $R_F C_{SC}$  time constant in the range 1.5~2  $\mu s$  .

- 9) Each capacitor should be mounted as close to the pins of the SPM as possible.

- 10) To prevent surge destruction, the wiring between the smoothing capacitor and the P&GND pins should be as short as possible. The use of a high frequency non-inductive capacitor of around 0.1~0.22µF between the P&GND pins is recommended.

- 11) Relays are used at almost every systems of electrical equipments of home appliances. In these cases, there should be sufficient distance between the CPU and the relays.

- 12)  $C_{SPC15}$  should be over  $1\mu F$  and mounted as close to the pins of the SPM as possible.

Figure 11. Typical Application Circuit

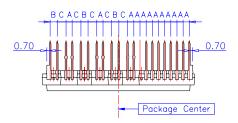

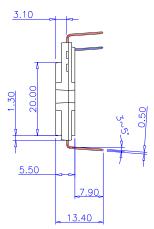

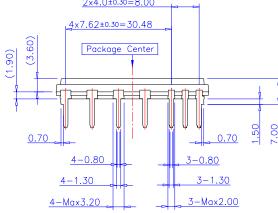

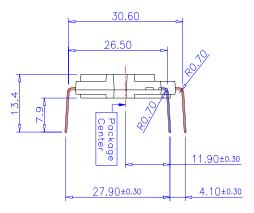

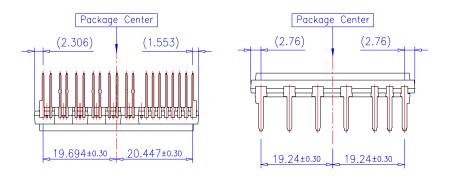

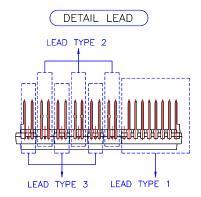

# **Detailed Package Outline Drawings**

Lead Pitch : ±0.30

A: 1.778 B: 2.050 C: 2.531

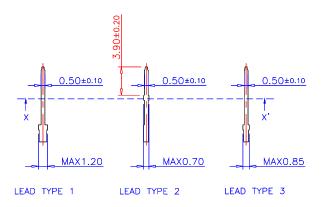

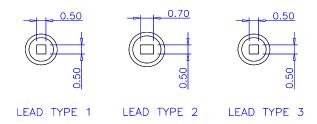

# **Detailed Package Outline Drawings (Continued)**

Lead Forming Dimension

PKG Center to Lead Distance

# **Detailed Package Outline Drawings (Continued)**

LEAD SECTION X-X'

## **TRADEMARKS**

The following are registered and unregistered trademarks Fairchild Semiconductor owns or is authorized to use and is not intended to be an exhaustive list of all such trademarks.

## **DISCLAIMER**

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

## LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, or (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in significant injury to the user.

2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

## PRODUCT STATUS DEFINITIONS

## **Definition of Terms**

| Datasheet Identification | Product Status            | Definition                                                                                                                                                                                                            |

|--------------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advance Information      | Formative or In<br>Design | This datasheet contains the design specifications for product development. Specifications may change in any manner without notice.                                                                                    |

| Preliminary              | First Production          | This datasheet contains preliminary data, and supplementary data will be published at a later date. Fairchild Semiconductor reserves the right to make changes at any time without notice in order to improve design. |

| No Identification Needed | Full Production           | This datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice in order to improve design.                                                       |

| Obsolete                 | Not In Production         | This datasheet contains specifications on a product that has been discontinued by Fairchild semiconductor. The datasheet is printed for reference information only.                                                   |

Rev. I15