February 2006

## **FSB50325T**

### **Smart Power Module (SPM)**

#### **Features**

- 250V 3.0A 3-phase FRFET inverter including high voltage integrated circuit (HVIC)

- 3 divided negative dc-link terminals for inverter current sensing applications

- HVIC for gate driving and undervoltage protection

- 3/5V CMOS/TTL compatible, active-high interface

- Optimized for low electromagnetic interference

- Isolation voltage rating of 1500Vrms for 1min.

- Extended VB pin for PCB isolation

### **General Description**

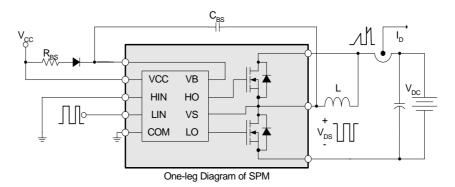

FSB50325T is a tiny smart power module (SPM) based on FRFET technology as a compact inverter solution for small power motor drive applications such as fan motors and water suppliers. It is composed of 6 fast-recovery MOSFET (FRFET), and 3 half-bridge HVICs for FRFET gate driving. FSB50325T provides low electromagnetic interference (EMI) characteristics with optimized switching speed. Moreover, since it employs FRFET as a power switch, it has much better ruggedness and larger safe operation area (SOA) than that of an IGBT-based power module or one-chip solution. The package is optimized for the thermal performance and compactness for the use in the built-in motor application and any other application where the assembly space is concerned. FSB50325T is the most solution for the compact inverter providing the energy efficiency, compactness, and low electromagnetic interference.

### **Absolute Maximum Ratings**

| Symbol           | Parameter                                                 | Conditions                                                                                    | Rating         | Units            |  |

|------------------|-----------------------------------------------------------|-----------------------------------------------------------------------------------------------|----------------|------------------|--|

| V <sub>PN</sub>  | DC Link Input Voltage, Drain-source Voltage of each FRFET |                                                                                               | 250            | V                |  |

| I <sub>D25</sub> | Each FRFET Drain Current, Continuous                      | T <sub>C</sub> = 25°C                                                                         | 1.5            | Α                |  |

| I <sub>D80</sub> | Each FRFET Drain Current, Continuous                      | $T_C = 80$ °C                                                                                 | 1.0            | Α                |  |

| I <sub>DP</sub>  | Each FRFET Drain Current, Peak                            | T <sub>C</sub> = 25°C, PW < 100μs                                                             | 3.0            | Α                |  |

| P <sub>D</sub>   | Maximum Power Dissipation                                 | T <sub>C</sub> = 25°C, Each FRFET                                                             | 10             | W                |  |

| V <sub>CC</sub>  | Control Supply Voltage                                    | Applied between V <sub>CC</sub> and COM                                                       | 20             | V                |  |

| V <sub>BS</sub>  | High-side Bias Voltage                                    | Bias Voltage Applied between V <sub>B(U)</sub> -U, V <sub>B(V)</sub> -V, V <sub>B(W)</sub> -W |                | V                |  |

| V <sub>IN</sub>  | Input Signal Voltage                                      | Applied between IN and COM                                                                    | -0.3 ~ VCC+0.3 | V                |  |

| TJ               | Operating Junction Temperature                            | COM                                                                                           | -20 ~ 125      | °C               |  |

| T <sub>STG</sub> | Storage Temperature                                       |                                                                                               | -50 ~ 150      | °C               |  |

| R <sub>θJC</sub> | Junction to Case Thermal Resistance                       | Each FRFET under inverter operating condition (Note 1)                                        | 10.2           | °C/W             |  |

| V <sub>ISO</sub> | Isolation Voltage                                         | 60Hz, Sinusoidal, 1 minute, Connection pins to heatsink                                       | 1500           | V <sub>rms</sub> |  |

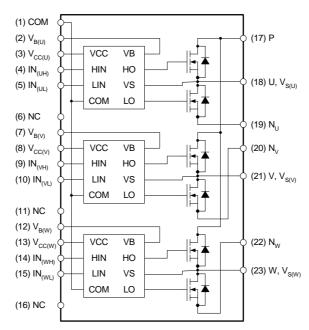

# **Pin Descriptions**

| Pin Number | Pin Name             | Pin Description                                                      |  |

|------------|----------------------|----------------------------------------------------------------------|--|

| 1          | COM                  | IC Common Supply Ground                                              |  |

| 2          | V <sub>B(U)</sub>    | Bias Voltage for U Phase High Side FRFET Driving                     |  |

| 3          | V <sub>CC(U)</sub>   | Bias Voltage for U Phase IC and Low Side FRFET Driving               |  |

| 4          | IN <sub>(UH)</sub>   | Signal Input for U Phase High-side                                   |  |

| 5          | IN <sub>(UL)</sub>   | Signal Input for U Phase Low-side                                    |  |

| 6          | NC                   | No Connection                                                        |  |

| 7          | V <sub>B(V)</sub>    | Bias Voltage for V Phase High Side FRFET Driving                     |  |

| 8          | V <sub>CC(V)</sub>   | Bias Voltage for V Phase IC and Low Side FRFET Driving               |  |

| 9          | IN <sub>(VH)</sub>   | Signal Input for V Phase High-side                                   |  |

| 10         | IN <sub>(VL)</sub>   | Signal Input for V Phase Low-side                                    |  |

| 11         | NC                   | No Connection                                                        |  |

| 12         | V <sub>B(W)</sub>    | Bias Voltage for W Phase High Side FRFET Driving                     |  |

| 13         | V <sub>CC(W)</sub>   | Bias Voltage for W Phase IC and Low Side FRFET Driving               |  |

| 14         | IN <sub>(WH)</sub>   | Signal Input for W Phase High-side                                   |  |

| 15         | IN <sub>(WL)</sub>   | Signal Input for W Phase Low-side                                    |  |

| 16         | NC                   | No Connection                                                        |  |

| 17         | Р                    | Positive DC-Link Input                                               |  |

| 18         | U, V <sub>S(U)</sub> | Output for U Phase & Bias Voltage Ground for High Side FRFET Driving |  |

| 19         | N <sub>U</sub>       | Negative DC-Link Input for U Phase                                   |  |

| 20         | N <sub>V</sub>       | Negative DC-Link Input for V Phase                                   |  |

| 21         | V, V <sub>S(V)</sub> | Output for V Phase & Bias Voltage Ground for High Side FRFET Driving |  |

| 22         | N <sub>W</sub>       | Negative DC–Link Input for W Phase                                   |  |

| 23         | W, V <sub>S(W)</sub> | Output for W Phase & Bias Voltage Ground for High Side FRFET Driving |  |

Note:

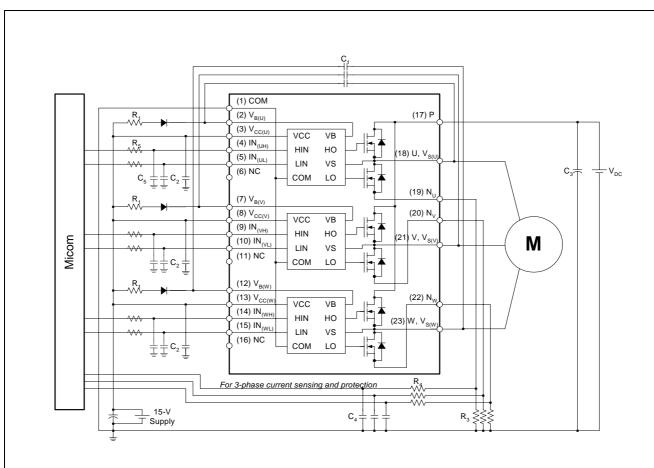

Source terminal of each low-side MOSFET is not connected to supply ground or bias voltage ground inside SPM. External connections should be made as indicated in Figure 2 and 5.

Figure 1. Pin Configuration and Internal Block Diagram (Bottom View)

### **Electrical Characteristics** (T<sub>J</sub> = 25°C, V<sub>CC</sub>=V<sub>BS</sub>=15V Unless Otherwise Specified)

Inverter Part (Each FRFET Unless Otherwise Specified)

| Symbol                          | Parameter                                 | Conditions                                                                                                                                | Min | Тур    | Max | Units |

|---------------------------------|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-----|--------|-----|-------|

| BV <sub>DSS</sub>               | Drain-Source Breakdown<br>Voltage         | V <sub>IN</sub> = 0V, I <sub>D</sub> = 250μA (Note 2)                                                                                     |     | -      | -   | V     |

| $\Delta BV_{DSS}/ \Delta T_{J}$ | Breakdown Voltage Temperature Coefficient | I <sub>D</sub> = 250μA, Referenced to 25°C                                                                                                | -   | 0.31   | -   | V     |

| I <sub>DSS</sub>                | Zero Gate Voltage<br>Drain Current        | V <sub>IN</sub> = 0V, V <sub>DS</sub> = 250V                                                                                              | -   | -      | 250 | μΑ    |

| R <sub>DS(on)</sub>             | Static Drain-Source<br>On-Resistance      | V <sub>CC</sub> = V <sub>BS</sub> = 15V, V <sub>IN</sub> = 5V, I <sub>D</sub> = 1.0A                                                      |     | 1.4    | 1.8 | Ω     |

| V <sub>SD</sub>                 | Drain-Source Diode<br>Forward Voltage     | V <sub>CC</sub> = V <sub>BS</sub> = 15V, V <sub>IN</sub> = 0V, I <sub>D</sub> = -1.0A                                                     |     | -      | 1.2 | V     |

| t <sub>ON</sub>                 |                                           | V <sub>PN</sub> = 150V, V <sub>CC</sub> = V <sub>BS</sub> = 15V, I <sub>D</sub> = 1.0A                                                    |     | 1076   | -   | ns    |

| t <sub>OFF</sub>                |                                           | $V_{IN} = 0V \leftrightarrow 5V$                                                                                                          | -   | 660    | -   | ns    |

| t <sub>rr</sub>                 | Switching Times                           | Inductive load L=3mH High- and low-side FRFET switching                                                                                   | -   | 108    | -   | ns    |

| E <sub>ON</sub>                 |                                           |                                                                                                                                           | -   | 47     | -   | μJ    |

| E <sub>OFF</sub>                |                                           | (Note 3)                                                                                                                                  |     | 3.1    | -   | μJ    |

| RBSOA                           | Reverse-bias Safe Operating Area          | $V_{PN} = 200V$ , $V_{CC} = V_{BS} = 15V$ , $I_D = I_{DP}$ , $V_{DS} = BV_{DSS}$ , $V_{DS} = 125^{\circ}C$ Full Signard Industry (Note 4) |     | Square |     |       |

### Control Part (Each HVIC Unless Otherwise Specified)

| Symbol            | Parameter                         | Conditions                                              |                                                             | Min | Тур | Max | Units |

|-------------------|-----------------------------------|---------------------------------------------------------|-------------------------------------------------------------|-----|-----|-----|-------|

| I <sub>QCC</sub>  | Quiescent V <sub>CC</sub> Current | $V_{CC}$ =15V, $V_{IN}$ =0V                             | Applied between V <sub>CC</sub> and COM                     | -   | -   | 160 | μΑ    |

| I <sub>QBS</sub>  | Quiescent V <sub>BS</sub> Current | V <sub>BS</sub> =15V, V <sub>IN</sub> =0V               | Applied between $V_{B(U)}$ -U, $V_{B(V)}$ -V, $V_{B(W)}$ -W | -   | -   | 100 | μА    |

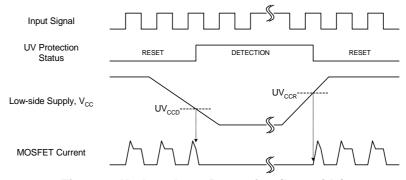

| UV <sub>CCD</sub> | Low-side Undervoltage             | V <sub>CC</sub> Undervoltage Protection Detection Level |                                                             | 7.4 | 8.0 | 9.4 | V     |

| UV <sub>CCR</sub> | Protection (Figure 6)             | V <sub>CC</sub> Undervoltage Protection Reset Level     |                                                             | 8.0 | 8.9 | 9.8 | V     |

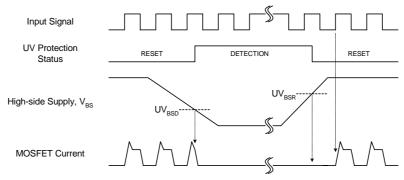

| UV <sub>BSD</sub> | High-side Undervoltage            | V <sub>BS</sub> Undervoltage F                          | Protection Detection Level                                  | 7.4 | 8.0 | 9.4 | V     |

| UV <sub>BSR</sub> | Protection (Figure 7)             | V <sub>BS</sub> Undervoltage F                          | Undervoltage Protection Reset Level                         |     | 8.9 | 9.8 | V     |

| V <sub>IH</sub>   | ON Threshold Voltage              | Logic High Level                                        | Applied between IN and COM                                  | 2.9 | -   | -   | V     |

| V <sub>IL</sub>   | OFF Threshold Voltage             | Logic Low Level                                         | Applied between IN and COM                                  | -   | -   | 0.8 | V     |

| I <sub>IH</sub>   | Input Bias Current                | V <sub>IN</sub> = 5V                                    | Applied between IN and COM                                  | -   | 10  | 20  | μΑ    |

| I <sub>IL</sub>   | input bias current                | V <sub>IN</sub> = 0V                                    | Applied between IN and COM                                  | -   | -   | 2   | μΑ    |

#### Note

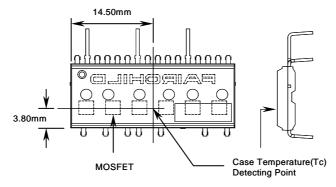

- 1. For the measurement point of case temperature  $\mathsf{T}_\mathsf{C},$  please refer to Figure 3 in page 4.

- 2. BV<sub>DSS</sub> is the absolute maximum voltage rating between drain and source terminal of each FRFET inside SPM. V<sub>PN</sub> should be sufficiently less than this value considering the effect of the stray inductance so that V<sub>DS</sub> should not exceed BV<sub>DSS</sub> in any case.

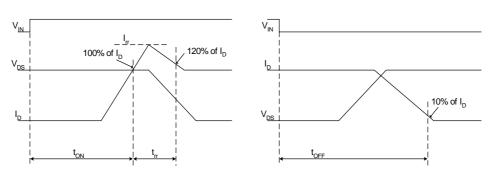

- 3. t<sub>ON</sub> and t<sub>OFF</sub> include the propagation delay time of the internal drive IC. Listed values are measured at the laboratory test condition, and they can be different according to the field applications due to the effect of different printed circuit boards and wirings. Please see Figure 4 for the switching time definition with the switching test circuit of Figure 5.

- 4. The peak current and voltage of each FRFET during the switching operation should be included in the safe operating area (SOA). Please see Figure 5 for the RBSOA test circuit that is same as the switching test circuit.

### **Recommended Operating Conditions**

| Symbol               | Parameter                              | Conditions                                                                  | Value |      |          | Units  |

|----------------------|----------------------------------------|-----------------------------------------------------------------------------|-------|------|----------|--------|

| Symbol               | raiailletei                            | Conditions                                                                  | Min.  | Тур. | Max.     | Oiilla |

| V <sub>PN</sub>      | Supply Voltage                         | Applied between P and N                                                     | -     | 150  | 200      | V      |

| V <sub>CC</sub>      | Control Supply Voltage                 | Applied between V <sub>CC</sub> and COM                                     | 13.5  | 15   | 16.5     | V      |

| V <sub>BS</sub>      | High-side Bias Voltage                 | Applied between $V_B$ and output(U, V, W)                                   | 13.5  | 15   | 16.5     | V      |

| V <sub>IN(ON)</sub>  | Input ON Threshold Voltage             | Applied between IN and COM                                                  | 3.0   | -    | $V_{CC}$ | V      |

| V <sub>IN(OFF)</sub> | Input OFF Threshold Voltage            | Applied between IV and Gold                                                 | 0     | -    | 0.6      | V      |

| t <sub>dead</sub>    | Blanking Time for Preventing Arm-short | $V_{CC} = V_{BS} = 13.5 \sim 16.5 \text{V}, T_{J} \le 125 ^{\circ}\text{C}$ | 1.0   | -    | -        | μS     |

| f <sub>PWM</sub>     | PWM Switching Frequency                | $T_{J} \leq 125^{\circ}C$                                                   | -     | 15   | i        | kHz    |

| T <sub>C</sub>       | Case Temperature                       | $T_J \le 125^{\circ}C$                                                      | -20   | =    | 100      | °C     |

| HIN  | LIN  | Output          | Note               |

|------|------|-----------------|--------------------|

| 0    | 0    | Z               | Both FRFET Off     |

| 0    | 1    | 0               | Low-side FRFET On  |

| 1    | 0    | V <sub>DC</sub> | High-side FRFET On |

| 1    | 1    | Forbidden       | Shoot-through      |

| Open | Open | Z               | Same as (0, 0)     |

#### Note:

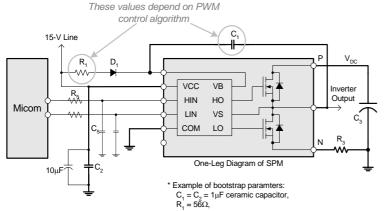

- (1) It is recommended the bootstrap diode  $D_1$  to have soft and fast recovery characteristics with 400-V rating

- (2) Parameters for bootsrap circuit elements are dependent on PWM algorithm. For 15 kHz of switching frequency, typical example of parameters is shown above.

- (3) RC coupling(R<sub>5</sub> and C<sub>5</sub>) at each input (indicated as dotted lines) may be used to prevent improper input signal due to surge noise. Signal input of SPM is compatible with standard CMOS or LSTTL outptus.

- (4) Bold lines should be short and thick in PCB pattern to have small stray inductance of circuit, which results in the reduction of surge voltage. Bypass capacitors such as C<sub>1</sub>, C<sub>2</sub> and C<sub>3</sub> should have good high-frequency characteristics to absorb high-frequency ripple current.

Figure 2. Recommended CPU Interface and Bootstrap Circuit with Parameters

#### Note:

Attach the thermocouple on top of the heatsink-side of SPM (between SPM and heatsink if applied) to get the correct temperature measurement.

**Figure 3. Case Temperature Measurement**

(a) Turn-on (b) Turn-off Figure 4. Switching Time Definition

Figure 5. Switching and RBSOA(Single-pulse) Test Circuit (Low-side)

Figure 6. Undervoltage Protection (Low-side)

Figure 7. Undervoltage Protection (High-side)

Figure 8. Example of Application Circuit

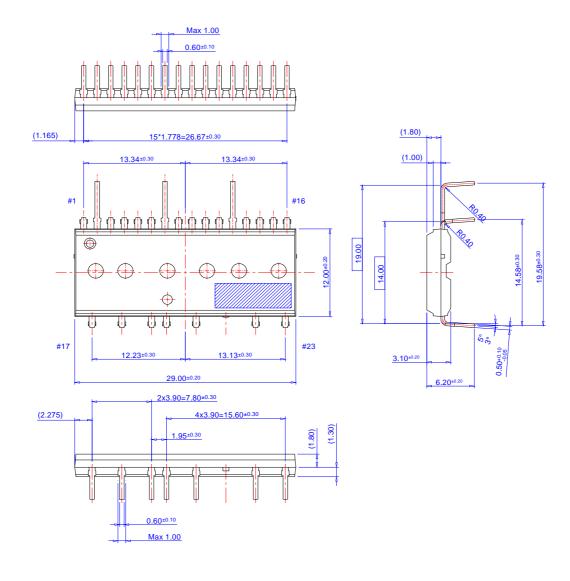

# **Detailed Package Outline Drawings**

#### **TRADEMARKS**

The following are registered and unregistered trademarks Fairchild Semiconductor owns or is authorized to use and is not intended to be an exhaustive list of all such trademarks.

| ACEx™                                                                                  | FAST <sup>®</sup>              | ISOPLANAR™             | PowerSaver™              | SuperSOT™-6            |

|----------------------------------------------------------------------------------------|--------------------------------|------------------------|--------------------------|------------------------|

| ActiveArray™                                                                           | FASTr™                         | LittleFET™             | PowerTrench <sup>®</sup> | SuperSOT™-8            |

| Bottomless™                                                                            | FPS™                           | MICROCOUPLER™          | QFET <sup>®</sup>        | SyncFET™               |

| Build it Now™                                                                          | FRFET™                         | MicroFET™              | QS™                      | TCM™ _                 |

| CoolFET™                                                                               | GlobalOptoisolator™            | MicroPak™              | QT Optoelectronics™      | TinyLogic <sup>®</sup> |

| CROSSVOLT™                                                                             | GTO™ .                         | MICROWIRE™             | Quiet Series™            | TINYOPTO™              |

| DOME™                                                                                  | HiSeC™                         | MSX™                   | RapidConfigure™          | TruTranslation™        |

| EcoSPARK™                                                                              | I <sup>2</sup> C <sup>TM</sup> | MSXPro™                | RapidConnect™            | UHC™                   |

| E <sup>2</sup> CMOS <sup>TM</sup>                                                      | i-Lo™                          | $OCX^{TM}$             | μSerDes™                 | UltraFET <sup>®</sup>  |

| EnSigna™                                                                               | ImpliedDisconnect™             | OCXPro™                | ScalarPump™              | UniFET™                |

| FACT™                                                                                  | IntelliMAX™                    | OPTOLOGIC <sup>®</sup> | SILENT SWITCHER®         | VCX™                   |

| FACT Quiet Serie                                                                       |                                | OPTOPLANAR™            | SMART START™             | Wire™                  |

| A th h                                                                                 |                                | PACMAN™                | SPM™                     |                        |

| Across the board. Around the world.™ The Power Franchise®  Programmable Active Program |                                | POPTM                  | Stealth™                 |                        |

|                                                                                        |                                | Power247™              | SuperFET™                |                        |

| Programmable P                                                                         | Programmable Active Droop™     |                        | SuperSOT™-3              |                        |

### **DISCLAIMER**

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTENAPPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.

As used berein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, or (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### PRODUCT STATUS DEFINITIONS

#### **Definition of Terms**

| Datasheet Identification | Product Status            | Definition                                                                                                                                                                                                            |

|--------------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advance Information      | Formative or<br>In Design | This datasheet contains the design specifications for product development. Specifications may change in any manner without notice.                                                                                    |

| Preliminary              | First Production          | This datasheet contains preliminary data, and supplementary data will be published at a later date. Fairchild Semiconductor reserves the right to make changes at any time without notice in order to improve design. |

| No Identification Needed | Full Production           | This datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice in order to improve design.                                                       |

| Obsolete                 | Not In Production         | This datasheet contains specifications on a product that has been discontinued by Fairchild semiconductor. The datasheet is printed for reference information only.                                                   |