### FS8170 2.5 GHz Low Power Phase-locked Loop IC

HiMARK Technology, Inc. reserves the right to change the product described in this datasheet. All information contained in this datasheet is subject to change without prior notice. HiMARK Technology, Inc. assumes no responsibility for the use of any circuits shown in this datasheet.

### **Description**

The FS8170 IC is a serial data input, fully programmable phase-locked loop with a 2.5 GHz prescaler for use in the local oscillator subsystem of radio transceivers. Multi-modulus division ratios of 32/33 and 64/65 are selectable thru serial programming to enable pulse swallowing operation. When combined with an external VCO, the FS8170 becomes the core of a very low power frequency synthesizer well-suited for mobile communication applications, such as 2.4 GHz ISM-band wireless data links and cellular GSM and PCS. The FS8170 is also pin compatible with Fujitsu's MB15E07SL IC.

#### **Features**

- Maximum input frequency: 2.5 GHz

- ◆ Supply voltage range from 2.4 V to 3.6 V

- Low current consumption in locked state: 3.5 mA typ. ( $V_{CC} = V_p = 2.7 \text{ V}, T_A = +25 \text{ °C}$ )

4.0 mA typ.  $(V_{CC} = V_P = 3.0 \text{ V}, T_A = +25 \text{ °C})$

10 μA max. in asynchronous power-down mode

- Digitally-filtered lock detect output

- ◆ 18-bit programmable input frequency divider using ÷ 32/33/64/65 multi-modulus prescaler with divide ratio range from 992 to 65631 for ÷ 32/33 mode and from 4032 to 131135 for ÷ 64/65 mode

- ◆ 14-bit programmable reference frequency divider with divide ratio range from 3 to 16383

- Programmable charge pump current: 1.5 mA or 6 mA

- ◆ Pin compatible with Fujitsu MB15E07, MB15E07L, MB15E07SL

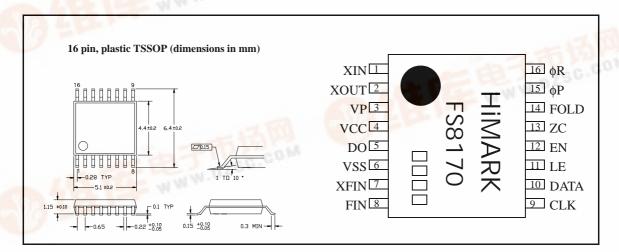

- ◆ 16 pin, plastic TSSOP (0.65 mm pitch)

## Package and Pin Assignment

Page 1 May 2003

# **Pin Descriptions**

| Number | Name | I/O | Description                                                                                    |

|--------|------|-----|------------------------------------------------------------------------------------------------|

| 1      | XIN  | I   | Reference crystal oscillator or external clock input with internally biased amplifier          |

| 2      | XOUT | О   | Reference crystal oscillator output                                                            |

| 3      | VP   | _   | Power supply voltage for the charge pump                                                       |

| 4      | VCC  | _   | Power supply voltage                                                                           |

| 5      | DO   | О   | Single-ended charge pump output                                                                |

| 6      | VSS  | _   | Ground                                                                                         |

| 7      | XFIN | I   | Complementary input for prescaler (normally ac-bypassed via a capacitor)                       |

| 8      | FIN  | I   | VCO frequency input with internally biased input amplifier                                     |

| 9      | CLK  | I   | Shift register clock input                                                                     |

| 10     | DATA | I   | Serial data input                                                                              |

| 11     | LE   | I   | Load enable signal input                                                                       |

| 12     | EN   | I   | Power-down control                                                                             |

| 13     | ZC   | I   | Forced high-impedance control for the charge pump                                              |

| 14     | FOLD | О   | Multiplexed CMOS level output (see Functional Description section for programming information) |

| 15     | φP   | О   | Phase comparator N-channel open drain output for an external charge pump                       |

| 16     | φR   | О   | Phase comparator CMOS inverter output for an external charge pump                              |

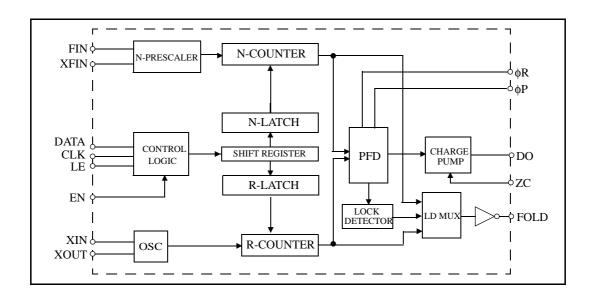

# **Functional Block Diagram**

Page 2 May 2003

# **Absolute Maximum Ratings**

$$V_{SS} = 0 V$$

| Parameter                    | Symbol           | Rating                             | Unit |

|------------------------------|------------------|------------------------------------|------|

| Cumply voltage senge         | V <sub>CC</sub>  | $V_{SS} - 0.3$ to $V_{SS} + 4.0$   | V    |

| Supply voltage range         | $V_{p}$          | V <sub>CC</sub> to 6.0             | V    |

| Input voltage range          | V <sub>FIN</sub> | $V_{SS} - 0.5$ to $V_{DD} + 0.5$   | V    |

| Outmut violtogo rongo        | V <sub>o</sub>   | V <sub>SS</sub> to V <sub>CC</sub> | V    |

| Output voltage range         | V <sub>DO</sub>  | V <sub>SS</sub> to V <sub>P</sub>  | V    |

| Storage temperature range    | $T_{STG}$        | -55 to 125                         | °C   |

| Soldering temperature range  | $T_{SLD}$        | 260                                | °C   |

| Soldering time range         | $t_{\rm SLD}$    | 4                                  | S    |

| ESD rating (human body mode) |                  | 3500                               | eV   |

# **Recommended Operating Conditions**

$$V_{SS} = 0 V$$

| Parameter             | Cymh ol         |      | Unit |      |       |  |

|-----------------------|-----------------|------|------|------|-------|--|

| r ai ametei           | Symbol          | min. | typ. | max. | Oiiit |  |

| Supply voltage range  | V <sub>CC</sub> | 2.4  | 3.0  | 3.6  | V     |  |

| Supply voltage range  | V <sub>P</sub>  | Vcc  | _    | 5.5  | V     |  |

| Operating temperature | $T_A$           | -40  | 25   | 80   | °C    |  |

## **Electrical Characteristics**

(V $_{\rm CC}$  = V $_{\rm P}$  = 3.0 V, V $_{\rm SS}$  = 0 V,  $T_{\rm A}$  = –40 to 85 °C unless otherwise noted)

| Parameter                        | Symbol                  | Condition                                              |                          | Value |                     | Unit               |  |

|----------------------------------|-------------------------|--------------------------------------------------------|--------------------------|-------|---------------------|--------------------|--|

| rarameter                        | Symbol                  | Condition                                              | min.                     | typ.  | max.                | Oint               |  |

| GENERAL                          |                         |                                                        |                          |       |                     |                    |  |

| Power supply current consumption | I <sub>CC,total</sub>   | fin = 2.5 GHz                                          |                          | 4     |                     | mA                 |  |

| Standby current consumption      | I <sub>CC,standby</sub> | ZC = "H" or open                                       |                          |       | 10                  | μΑ                 |  |

| FIN operating frequency          | $f_{FIN}$               | $V_{FIN} = 0.3 V_{pk-pk} $ sinusoid                    | 50                       |       | 2500                | MHz                |  |

| XIN operating frequency          | $f_{XIN}$               |                                                        | 3                        |       | 40                  | MHz                |  |

| Input sensitivity                | $P_{FIN}$               | 50 Ω measurement system                                | -15                      |       | +2                  | dBm                |  |

| XIN input voltage swing          | V <sub>XIN</sub>        |                                                        | 0.5                      |       | V <sub>CC</sub>     | V <sub>pk-pk</sub> |  |

| CHARGE PUMP                      |                         |                                                        |                          |       |                     |                    |  |

|                                  | IDO <sub>source</sub>   | $V_{DO} = V_P/2$ , CS bit = "H"                        |                          | -6    |                     | mA                 |  |

| RF charge pump output current    | IDO <sub>sink</sub>     | $V_{DO} = V_P/2$ , CS bit = "H"                        |                          | 6     |                     | mA                 |  |

| Kr charge pump output current    | IDO <sub>source</sub>   | $V_{DO} = V_p/2$ , CS bit = "L"                        |                          | -1.5  |                     | mA                 |  |

|                                  | IDO <sub>sink</sub>     | $V_{DO} = V_p/2$ , CS bit = "L"                        |                          | 1.5   |                     | mA                 |  |

| DIGITAL INTERFACE (DATA,         | CLK, LE,                | PS, ZC)                                                |                          |       |                     |                    |  |

| High-level input voltage         | V <sub>IH</sub>         |                                                        | $0.8 \times V_{CC}$      |       |                     | V                  |  |

| Low-level input voltage          | $V_{\rm IL}$            |                                                        |                          |       | $0.2 \times V_{CC}$ | V                  |  |

| High-level input current         | I <sub>IH</sub>         | $V_{IH} = V_{CC} = 3.6V$                               | -1                       |       | 1                   | μΑ                 |  |

| Low-level input current          | $I_{\rm IL}$            | $V_{IL} = 0 \text{ V}, V_{CC} = 3.6 \text{V}$          | -1                       |       | 1                   | μΑ                 |  |

| XIN logic HIGH input current     | $I_{IH,XIN}$            | $V_{IH} = V_{DD}$                                      |                          |       | 100                 | μΑ                 |  |

| XIN logic LOW input current      | $I_{\rm IL,XIN}$        | $V_{IL} = 0 V$                                         | -100                     |       |                     | μΑ                 |  |

| φP logic LOW output voltage      | V <sub>OL</sub>         | Open drain output                                      |                          |       | 0.4                 | V                  |  |

| φP logic LOW output current      | $I_{OL}$                | Open drain output                                      | 1                        |       |                     | mA                 |  |

| φR logic HIGH output voltage     | V <sub>OH</sub>         | $V_{CC} = V_P = 3.0 \text{ V}, I_{OH} = -1 \text{ mA}$ | V <sub>CC</sub> -<br>0.4 |       |                     | V                  |  |

| φR logic LOW output voltage      | V <sub>OL</sub>         | $V_{CC} = V_P = 3.0 \text{ V}, I_{OL} = 1 \text{ mA}$  |                          |       | 0.4                 | V                  |  |

| φR logic HIGH output current     | $I_{OH}$                | $V_{CC} = V_P = 3.0 \text{ V}$                         |                          |       | -1                  | mA                 |  |

| φR logic LOW output current      | $I_{OL}$                | $V_{CC} = V_p = 3.0 \text{ V}$                         | 1                        |       |                     | mA                 |  |

FS8170

# **Electrical Characteristics**

(V $_{CC}$  = V $_{P}$  = 3.0 V, V $_{SS}$  = 0 V,  $T_{A}$  = –40 to 85  $^{\circ}C$  unless otherwise noted)

| Parameter                      | Symbol             | Condition                                              |                          | - Unit |      |       |

|--------------------------------|--------------------|--------------------------------------------------------|--------------------------|--------|------|-------|

| r arameter                     | Symbol             | Condition                                              | min.                     | typ.   | max. | Oilit |

| FOLD logic HIGH output voltage | $V_{OH}$           | $V_{CC} = V_P = 3.0 \text{ V}, I_{OH} = -1 \text{ mA}$ | V <sub>CC</sub> -<br>0.4 |        |      | V     |

| FOLD logic LOW output voltage  | V <sub>OL</sub>    | $V_{CC} = V_P = 3.0 \text{ V}, I_{OL} = 1 \text{ mA}$  |                          |        | 0.4  | V     |

| FOLD logic HIGH output current | V <sub>OH</sub>    | $V_{CC} = V_P = 3.0 \text{ V}$                         |                          |        | -1   | mA    |

| FOLD logic LOW output current  | V <sub>OL</sub>    | $V_{CC} = V_P = 3.0 \text{ V}$                         | 1                        |        |      | mA    |

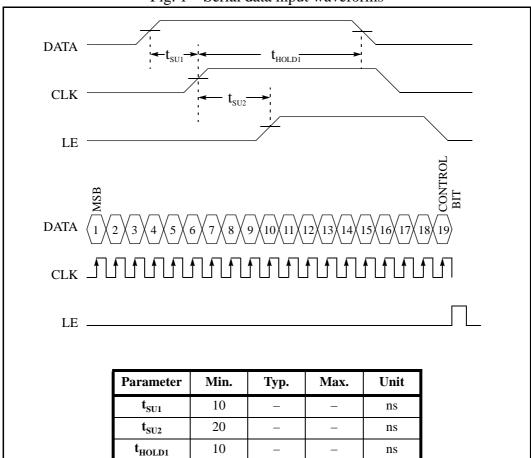

| MICROWIRE TIMING               |                    |                                                        |                          |        |      |       |

| DATA to CLK setup time         | $t_{SU1}$          |                                                        | 10                       |        |      | ns    |

| DATA to CLK hold time          | $t_{HOLD1}$        |                                                        | 10                       |        |      | ns    |

| CLK to LE setup time           | t <sub>SU2</sub>   |                                                        | 20                       |        |      | ns    |

| CLK to LE hold time            | t <sub>HOLD2</sub> |                                                        | 30                       |        |      | ns    |

| LE Pulse width                 | $t_{\rm EW}$       |                                                        | 50                       |        |      | ns    |

### **Functional Description**

#### **Programmable Input Frequency Divider**

The VCO output to the FIN pin is divided by the programmable divider and then internally output to the phase/frequency detector (PFD) as  $f_{\rm V}$ . The programmable input frequency divider consists of a multi-modulus (selectable  $\div$  32/33 or  $\div$  64/65 (M/M+1)) prescaler and a 18-bit N-counter, which is further comprised of a 7-bit swallow A-counter, and a 11-bit main B-counter. The total divide ratio, N, is related to values for M, A, and B through the relation

$$N = (M+1) \times A + M \times (B-A) = M \times B + A,$$

with  $B \ge A$ . The minimum programmable divisor for continuous counting is given by  $M \times (M-1)$ , and is  $32 \times (32-1) = 992$  for the  $\div 32/33$  prescaler mode, and is  $64 \times (64-1) = 4032$  for the  $\div 64/65$  mode. Hence, the valid total divide ratio range for the input divider is N = 992 to 65631 for the  $\div 32/33$  mode and N = 4032 to 131135 for the  $\div 64/65$  mode.

#### **Programmable Reference Frequency Divider**

The crystal oscillator output is divided by the programmable reference divider and then internally output to the PFD as  $f_R$ . The programmable reference frequency divider consists of a 14-bit reference R-counter. Becasue of its specific design, the minimum acceptable divisor for R is 3, and hence the total divide ratio, R, ranges from 3 to 16383.

#### **Shift Register Configuration**

The divide ratios for the input and reference dividers are input using a 19-bit serial interface consisting of separate clock (CLK), data (DATA), and load enable (LE) lines. The format of the serial data is shown in Table 1. The data on the DATA line is written to the shift register on the rising edge of the CLK signal and is input with MSB first, and the last bit is used as the latch select control bit. The data on the DATA line should be changed on the falling edge of CLK, and LE should be held LOW while data is being written to the shift register. Data is transferred from the shift register to one of the frequency divider latches when LE is set HIGH. When the latch select control bit is set LOW, data is loaded to the 18-bit *N*-counter latch, and when the latch select control bit is set HIGH, the 4 MSBs are recognized as CS, LDS, FC, SW, respectively, and the next 14 data bits are loaded to the 14-bit *R*-counter latch. The definition of the 4 MSBs will be described in Table 5 and 6. Note that LDS should be set LOW for normal operation.

Also, serial input data timing waveforms are shown in Fig. 1.

Fig. 1 – Serial data input waveforms

LSB MSB Data Flow — Table 1: Serial data input format 5 11 12 14 15 16 19 N N A A A A A A A N N N N N N N N N 2 3 4 5 6 7 2 3 4 5 7 8 9 10 11 1 1 6 C L В C R R R R R R R R R R R S F R R R D 14 10 13 W  $\mathbf{C}$  $\mathbf{S}$ 11 12

CB Control bit for selecting the N or R latch

A1 to A7 Control bits for setting the divide ratio of the programmable swallow counter (0 to 127)

B1 to B11 Control bits for setting the divide ratio of the programmable main counter (3 to 2047)

R1 to R14 Control bits for setting the divide ratio of the programmable reference counter (3 to 16383)

SW Control bit for setting the divide ratio of the prescaler (32/33 or 64/65) FC Control bit for setting the polarity of the phase/frequency detector

LDS Control bit for selecting the output for the FOLD pin CS Control bit for setting the charge pump current level

Page 7 May 2003

Table 2: Binary 7-bit data format for swallow counter

| Divide<br>ratio<br>(A) | A<br>7 | A<br>6 | A<br>5 | A<br>4 | A<br>3 | A<br>2 | A<br>1 |

|------------------------|--------|--------|--------|--------|--------|--------|--------|

| 0                      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

| 1                      | 0      | 0      | 0      | 0      | 0      | 0      | 1      |

|                        |        |        |        |        |        |        |        |

| 127                    | 1      | 1      | 1      | 1      | 1      | 1      | 1      |

Table 3: Binary 11-bit data format for main counter

| Divide ratio (B) | N<br>11 | N<br>10 | N<br>9 | N<br>8 | N<br>7 | N<br>6 | N<br>5 | N<br>4 | N<br>3 | N<br>2 | N<br>1 |

|------------------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| 3                | 0       | 0       | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 1      | 1      |

| 4                | 0       | 0       | 0      | 0      | 0      | 0      | 0      | 0      | 1      | 0      | 0      |

|                  |         |         |        |        |        |        |        |        |        |        |        |

| 2047             | 1       | 1       | 1      | 1      | 1      | 1      | 1      | 1      | 1      | 1      | 1      |

Table 4: Binary 14-bit data format for reference counter

| Divide<br>ratio<br>(R) | R<br>14 | R<br>13 | R<br>12 | R<br>11 | R<br>10 | R<br>9 | R<br>8 | R<br>7 | R<br>6 | R<br>5 | R<br>4 | R<br>3 | R<br>2 | R<br>1 |

|------------------------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| 3                      | 0       | 0       | 0       | 0       | 0       | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 1      | 1      |

| 4                      | 0       | 0       | 0       | 0       | 0       | 0      | 0      | 0      | 0      | 0      | 0      | 1      | 0      | 0      |

|                        |         |         |         |         |         |        |        |        |        |        |        |        |        |        |

| 16383                  | 1       | 1       | 1       | 1       | 1       | 1      | 1      | 1      | 1      | 1      | 1      | 1      | 1      | 1      |

Table 5: Data format for 3 optional bits

| Bit | Н             | L               | Description                          |

|-----|---------------|-----------------|--------------------------------------|

| SW  | 32/33         | 64/65           | Prescaler dual-modulus ratio setting |

| CS  | <u>+</u> 6 mA | <u>+</u> 1.5 mA | Charge pump current setting          |

| LDS | FO signal     | LD signal       | FOLD output select setting           |

Page 8 May 2003

|                         |    | FC = | HIGH |              | FC = LOW |    |                           |              |  |

|-------------------------|----|------|------|--------------|----------|----|---------------------------|--------------|--|

|                         | DO | φR   | φР   | FOLD         | DO       | φR | φР                        | FOLD         |  |

| $f_{\rm R} > f_{\rm V}$ | Н  | L    | L    |              | L        | Н  | $\mathbf{Z}^{\mathrm{a}}$ |              |  |

| $f_{\rm R} < f_{ m V}$  | L  | Н    | Z    | $FOLD = f_R$ | Н        | L  | L                         | $FOLD = f_V$ |  |

| $f_{\rm R} = f_{\rm V}$ | Z  | L    | Z    |              | Z        | L  | Z                         |              |  |

Table 6: Data format for FC bit (LDS = HIGH)

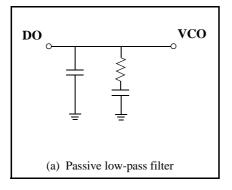

### **Phase/Frequency Detector (PFD)**

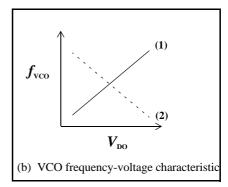

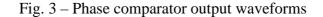

The PFD compares an internal input frequency divider output signal,  $f_V$ , with an internal reference frequency divider output signal,  $f_R$ , and generates an error signal, DO, which is proportional to the phase error between  $f_V$  and  $f_R$ . The DO output is intended for use with a passive filter as shown in Fig. 2 (a). The polarity of DO is selectable by setting the bit FC to high or low. The setting should depend on the frequency-voltage characteristic of external VCO as depicted in Fig. 2 (b).

The input/output waveforms for the PFD are shown in Fig. 3.

Fig. 2 – Low-pass filter and external VCO frequency-voltage characteristic

Note: If VCO has a positive tuning curve similiar to trace (1), set FC = "H," otherwise if the VCO has a negative tuning curve similar to trace (2), set FC = "L."

Page 9 May 2003

a. Z denotes high impedance state

- 1. Pulses of finite width on DO output are generated during locked state to prevent dead zone.

- 2. A "locked" condition (LD is HIGH) is indicated when the phase error is less than t1 or t2 at least for 3 consecutive comparison cycles, otherwise an "unlocked" condition (LD is LOW) is indicated.

- 3. The values of  $t_1$  and  $t_2$  depend on the XIN input frequency:  $t_1 \ge 2/\text{fosc}$  (e.g.  $t_1 \ge 250$  ns, if  $f_{XIN} = 8$  MHz)

- $t_2 \ge 2/\text{fosc}$  (e.g.  $t_2 \ge 250$  ns, if  $f_{XIN} = 8$  MHz)

- 4. LD becomes HIGH during power-down mode (when EN is set LOW).

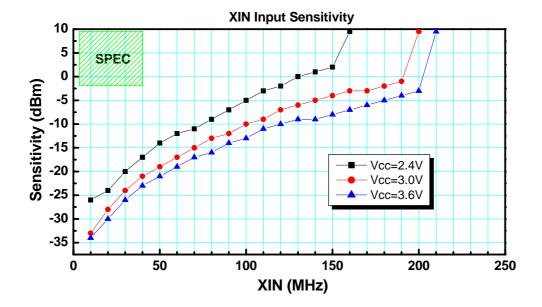

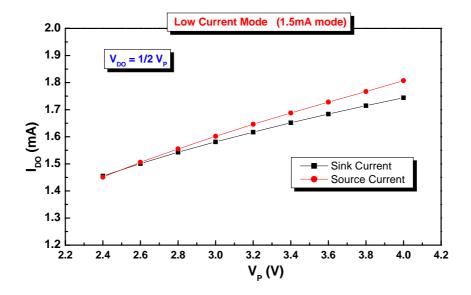

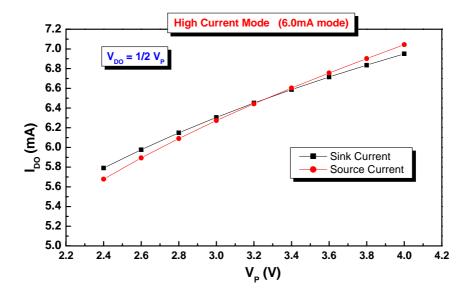

#### **Charge Pump (CP)**

The phase error signal, DO, generated from the PFD will pump charge into an external loop filter, which then converts the charge to produce the VCO's tuning voltage. With a constant pumping rate, the shift of the VCO's tuning voltage will be directly proportional to the phase error signal DO. Two pumping rates, 1.5 mA and 6 mA, are provided by the chip and are selectable through the bit CS as defined previously in Table 5. Also, the charge pump characteristics corresponding to both modes are shown in the Typical Characteristics section. The internal charge pump may be turned off by the pin ZC. When ZC is set low, the internal charge pump will stay in its high-impedance state and will not pump any charge into the external LPF. In this case, the user is allowed to utilize one's own charge pump by two control pins  $\phi P$  and  $\phi R$  which are defined in Table 6.  $\phi P$  and  $\phi R$  are the error signals directly proportional to the positive/negative phase error when FC = "H." When FC = "L," the relation becomes negative/positive.

Table 7: Setting for the pin ZC

| ZC | Do Output      |

|----|----------------|

| Н  | Normal output  |

| L  | High impedance |

Page 10 May 2003

FS8170

#### **Multi-function Lock Detect Output (FOLD)**

A digital lock detect function is included with the phase detector through an internal digital filter to produce a logic level output which is available on the FOLD output pin. The criterion of lock indication depends on the period of the crystal oscillator reference. The lock dectect output is HIGH whenever the phase error between phase detector inputs is less than 2 times of the crystal period for more than three consecutive comparison cycles, otherwise is low. Note that LD becomes HIGH during the power saving mode. The LD output is depicted in Fig. 3 as well.

#### **Power-down Control (EN)**

By setting the pin EN to LOW, the chip enters into power-down mode, reducing the current consumption. During the power-down mode, the phase detector output, DO, is set to its high impedance. Normal operation mode resumes when EN is switched to HIGH. To prove a smooth start-up condition, an intermittent control circuit is activated when the device returns to normal operation. Due to the unknown relationship between  $f_{\rm V}$  and  $f_{\rm R}$  after returning from power-down, the PFD output is unpredictable and may give rise to a significant jump in the VCO's frequency which will result in an increased lock-up time. To prevent this, the FS8170 employs an intermittent control circuit to limit the magnitude of the error signal generated by the phase detector when it returns to normal operation, thus ensuring a much quicker return to the fully phase-locked condition.

Table 8: Setting for the pin EN

| EN | Status                |

|----|-----------------------|

| Н  | Normal operation mode |

| L  | Power-down mode       |

Page 11 May 2003

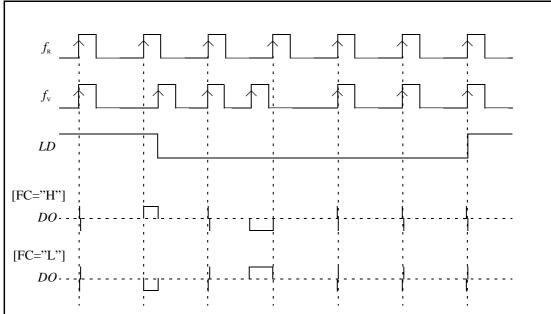

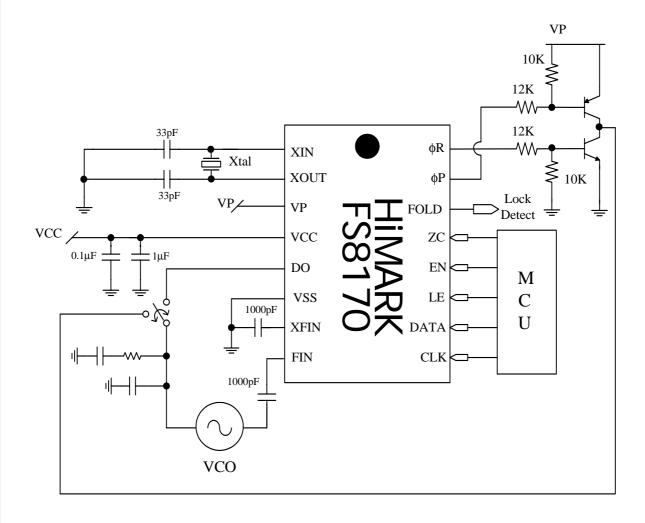

# **Measurement Circuit Setup**

The circuit shown in Fig. 4 is used for measuring the input sensitivity of the FIN input of the PLL.

Fig. 4 – FIN input sensitivity test circuit

Page 12 May 2003

# **Typical Characteristics**

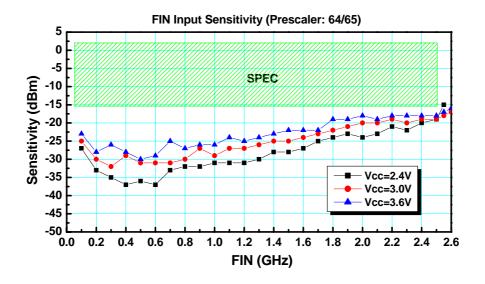

### **FIN Input Sensitivity**

Fig. 5 – Input sensitivity vs. frequency

Page 13 May 2003

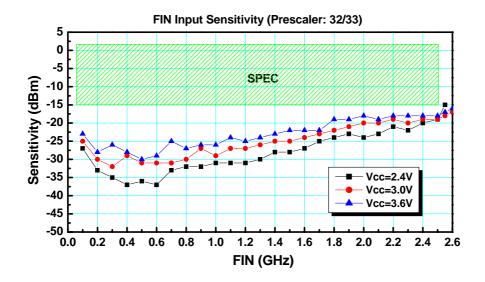

# **XIN Input Sensitivity**

Fig. 6 – XIN input sensitivity vs. frequency

Page 14 May 2003

## **Charge Pump Characteristic**

Fig. 7 – Charge pump current vs.  $V_{DO}$

Page 15 May 2003

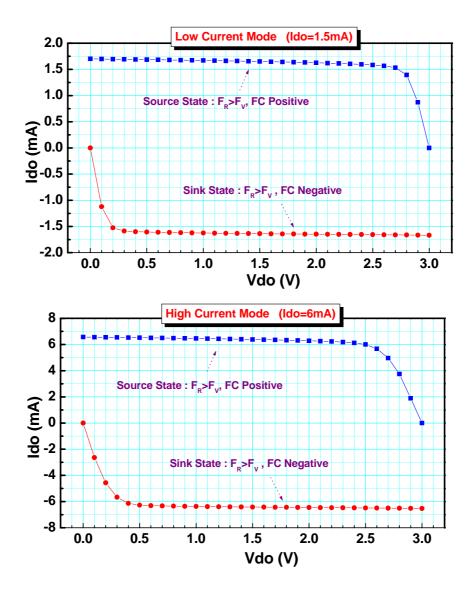

## **Supply Voltage Dependence of Charge Pump Current**

Fig. 8 – Charge pump current vs. supply voltage at  $V_{DO} = V_P/2$

Page 16 May 2003

# **Appication Circuit**

Page 17 May 2003